A Cell Matrix Merging Method in Physical Verification of Flat Panel Display Layout

A cell matrix, physical verification technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as non-coverage, low inspection efficiency, and great impact, and achieve improved execution efficiency and result level optimization. , reduce the effect of overlapping areas

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The preferred embodiments of the present invention will be described below with reference to the accompanying drawings. It should be understood that the preferred embodiments described herein are only used to illustrate and explain the present invention, but not to limit the present invention.

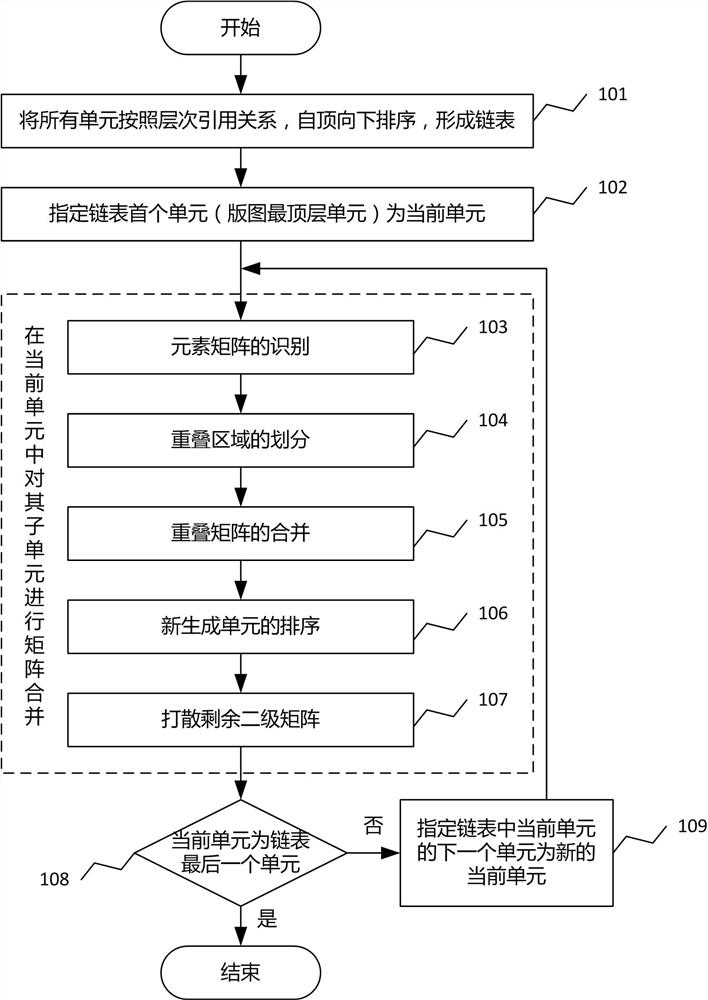

[0053] figure 1 It is a flow chart of the unit matrix merging method in the physical verification of the flat panel display layout according to the present invention, which will be referred to below. figure 1 , the unit matrix combining method in the physical verification of the flat panel display layout of the present invention is described in detail.

[0054] First, in step 101, all units are sorted from top to bottom according to the hierarchical reference relationship, that is, topological sorting, to form a linked list.

[0055] After that, it will try to do matrix merging of sub-units in it, from top to bottom, taking each unit as the current unit in turn.

[0056] The n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More