Correlation Between Resistive Read Disturb And MTJ Design

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

MTJ Technology Background and Objectives

Magnetic Tunnel Junction (MTJ) technology has evolved significantly over the past two decades, emerging as a cornerstone for next-generation non-volatile memory applications. The fundamental structure of an MTJ consists of two ferromagnetic layers separated by a thin insulating barrier, typically made of magnesium oxide (MgO). The resistance of this junction varies depending on the relative magnetization directions of the ferromagnetic layers, creating the basis for data storage through the tunnel magnetoresistance (TMR) effect.

The development trajectory of MTJ technology has progressed through several critical phases. Initially, in-plane magnetic anisotropy (IMA) designs dominated the field, but these were limited by scalability and power efficiency concerns. The breakthrough came with the introduction of perpendicular magnetic anisotropy (PMA) MTJs around 2010, which offered superior thermal stability and reduced switching current requirements, enabling higher density memory arrays.

Recent advancements have focused on enhancing the reliability and performance characteristics of MTJs, particularly addressing challenges related to read disturb phenomena. Read disturb occurs when the current used to sense the MTJ state inadvertently alters the stored information, compromising data integrity. This issue becomes increasingly critical as device dimensions shrink to accommodate higher storage densities.

The correlation between resistive read disturb and MTJ design represents a crucial area of investigation. Various design parameters—including the thickness of the tunnel barrier, composition of the free and reference layers, and interface engineering—significantly impact read disturb susceptibility. Understanding these relationships is essential for developing robust MTJ devices capable of maintaining data integrity over extended operational lifetimes.

The primary technical objectives in this domain include: quantifying the impact of design variations on read disturb thresholds; establishing predictive models that correlate MTJ structural parameters with read disturb vulnerability; and developing innovative design approaches that enhance read disturb immunity without compromising other performance metrics such as TMR ratio, switching speed, and endurance.

Industry trends indicate a growing emphasis on materials engineering and interface optimization to address these challenges. Techniques such as synthetic antiferromagnetic (SAF) structures, dual MgO interfaces, and incorporation of novel materials like Heusler alloys are being explored to enhance both performance and reliability.

The ultimate goal of current research efforts is to establish design guidelines that enable the development of MTJ devices with optimal resistance to read disturb effects while maintaining compatibility with advanced manufacturing processes and meeting the stringent requirements of emerging applications in data storage, IoT devices, and neuromorphic computing systems.

The development trajectory of MTJ technology has progressed through several critical phases. Initially, in-plane magnetic anisotropy (IMA) designs dominated the field, but these were limited by scalability and power efficiency concerns. The breakthrough came with the introduction of perpendicular magnetic anisotropy (PMA) MTJs around 2010, which offered superior thermal stability and reduced switching current requirements, enabling higher density memory arrays.

Recent advancements have focused on enhancing the reliability and performance characteristics of MTJs, particularly addressing challenges related to read disturb phenomena. Read disturb occurs when the current used to sense the MTJ state inadvertently alters the stored information, compromising data integrity. This issue becomes increasingly critical as device dimensions shrink to accommodate higher storage densities.

The correlation between resistive read disturb and MTJ design represents a crucial area of investigation. Various design parameters—including the thickness of the tunnel barrier, composition of the free and reference layers, and interface engineering—significantly impact read disturb susceptibility. Understanding these relationships is essential for developing robust MTJ devices capable of maintaining data integrity over extended operational lifetimes.

The primary technical objectives in this domain include: quantifying the impact of design variations on read disturb thresholds; establishing predictive models that correlate MTJ structural parameters with read disturb vulnerability; and developing innovative design approaches that enhance read disturb immunity without compromising other performance metrics such as TMR ratio, switching speed, and endurance.

Industry trends indicate a growing emphasis on materials engineering and interface optimization to address these challenges. Techniques such as synthetic antiferromagnetic (SAF) structures, dual MgO interfaces, and incorporation of novel materials like Heusler alloys are being explored to enhance both performance and reliability.

The ultimate goal of current research efforts is to establish design guidelines that enable the development of MTJ devices with optimal resistance to read disturb effects while maintaining compatibility with advanced manufacturing processes and meeting the stringent requirements of emerging applications in data storage, IoT devices, and neuromorphic computing systems.

Market Analysis for MTJ-based Memory Solutions

The global market for MTJ-based memory solutions continues to experience robust growth, driven primarily by increasing demand for high-performance, non-volatile memory technologies across various sectors. The current market valuation stands at approximately $2.1 billion as of 2023, with projections indicating a compound annual growth rate (CAGR) of 29% through 2028, potentially reaching $7.5 billion by that time.

The demand for MTJ-based memory solutions is particularly strong in data centers and enterprise storage systems, where the need for fast, reliable, and energy-efficient memory solutions is paramount. These sectors currently account for roughly 42% of the total market share. The automotive industry represents another significant growth area, with advanced driver-assistance systems (ADAS) and autonomous vehicles requiring robust memory solutions capable of withstanding harsh operating conditions.

Consumer electronics manufacturers are increasingly incorporating MTJ-based memory solutions into smartphones, tablets, and wearable devices, leveraging their low power consumption and non-volatility characteristics. This segment currently represents approximately 28% of the market and is expected to grow substantially as device manufacturers seek to extend battery life while maintaining performance.

Geographically, North America leads the market with approximately 38% share, followed closely by Asia-Pacific at 35%, with particularly strong growth in China, Japan, and South Korea. European markets account for about 22% of global demand, with the remaining 5% distributed across other regions.

The correlation between resistive read disturb and MTJ design has significant market implications. As manufacturers strive to increase memory density and reduce power consumption, the susceptibility to read disturb effects becomes a critical factor in product differentiation. Companies that can effectively mitigate these effects while maintaining performance metrics stand to gain substantial market advantage.

Market research indicates that customers are willing to pay a premium of 15-20% for MTJ-based memory solutions that demonstrate superior read disturb resistance, particularly in applications where data integrity is mission-critical. This represents a significant opportunity for manufacturers investing in advanced MTJ designs that address this specific challenge.

The competitive landscape is characterized by both established semiconductor manufacturers and specialized memory technology companies. Recent market consolidation through mergers and acquisitions suggests that industry players recognize the strategic importance of MTJ technology in the broader memory ecosystem. Venture capital investment in startups focusing on novel MTJ designs has reached $780 million in the past 18 months, underscoring the market's growth potential and technological significance.

The demand for MTJ-based memory solutions is particularly strong in data centers and enterprise storage systems, where the need for fast, reliable, and energy-efficient memory solutions is paramount. These sectors currently account for roughly 42% of the total market share. The automotive industry represents another significant growth area, with advanced driver-assistance systems (ADAS) and autonomous vehicles requiring robust memory solutions capable of withstanding harsh operating conditions.

Consumer electronics manufacturers are increasingly incorporating MTJ-based memory solutions into smartphones, tablets, and wearable devices, leveraging their low power consumption and non-volatility characteristics. This segment currently represents approximately 28% of the market and is expected to grow substantially as device manufacturers seek to extend battery life while maintaining performance.

Geographically, North America leads the market with approximately 38% share, followed closely by Asia-Pacific at 35%, with particularly strong growth in China, Japan, and South Korea. European markets account for about 22% of global demand, with the remaining 5% distributed across other regions.

The correlation between resistive read disturb and MTJ design has significant market implications. As manufacturers strive to increase memory density and reduce power consumption, the susceptibility to read disturb effects becomes a critical factor in product differentiation. Companies that can effectively mitigate these effects while maintaining performance metrics stand to gain substantial market advantage.

Market research indicates that customers are willing to pay a premium of 15-20% for MTJ-based memory solutions that demonstrate superior read disturb resistance, particularly in applications where data integrity is mission-critical. This represents a significant opportunity for manufacturers investing in advanced MTJ designs that address this specific challenge.

The competitive landscape is characterized by both established semiconductor manufacturers and specialized memory technology companies. Recent market consolidation through mergers and acquisitions suggests that industry players recognize the strategic importance of MTJ technology in the broader memory ecosystem. Venture capital investment in startups focusing on novel MTJ designs has reached $780 million in the past 18 months, underscoring the market's growth potential and technological significance.

Resistive Read Disturb Challenges in MTJ Devices

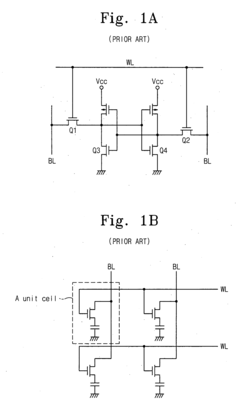

Resistive read disturb (RRD) represents a significant reliability challenge in Magnetic Tunnel Junction (MTJ) devices, particularly as these components become increasingly critical in emerging non-volatile memory technologies. The fundamental issue stems from the interaction between read currents and the magnetic stability of the MTJ structure. During read operations, current flowing through the MTJ can generate thermal effects and spin-transfer torque that may destabilize the magnetic state, potentially causing unintended switching or gradual degradation of the stored information.

The severity of RRD is heavily influenced by specific design parameters of the MTJ structure. Junction size plays a crucial role, with smaller dimensions generally exhibiting increased vulnerability to disturb effects due to higher current densities. The thickness ratio between the free and reference layers significantly impacts stability, as thinner free layers may be more susceptible to thermally-assisted switching during read operations.

Material composition presents another critical factor affecting RRD susceptibility. The choice of ferromagnetic materials, tunnel barrier composition, and interface engineering all contribute to the overall resilience against read disturb phenomena. For instance, MgO-based barriers with specific crystalline orientations have demonstrated superior performance compared to earlier amorphous barriers, though they still face challenges at advanced technology nodes.

The shape anisotropy and thermal stability factor (Δ) of the MTJ directly correlate with read disturb immunity. Devices designed with higher Δ values offer greater resistance to thermal fluctuations but may require higher switching currents for write operations, creating a fundamental design trade-off between read stability and write efficiency.

Process variations during manufacturing further complicate the RRD landscape. Minute variations in layer thicknesses, interface quality, or material properties can significantly alter the disturb characteristics across a memory array, leading to reliability concerns and potential yield issues in high-volume production scenarios.

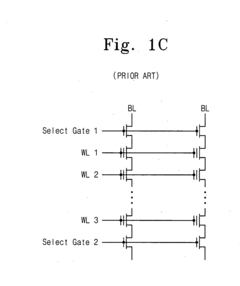

Reading schemes and circuit-level considerations also influence RRD behavior. The amplitude and duration of read pulses, sensing margin design, and reference schemes all contribute to the overall system-level resilience against read disturb effects. Advanced reading techniques incorporating error correction, disturb-aware reading algorithms, and optimized pulse shaping have been proposed to mitigate these challenges.

As MTJ technology scales to smaller dimensions for higher density applications, the correlation between design parameters and read disturb becomes increasingly critical. The industry faces a complex optimization problem balancing multiple factors including thermal stability, switching efficiency, read disturb immunity, and manufacturing feasibility to create commercially viable MTJ-based memory solutions.

The severity of RRD is heavily influenced by specific design parameters of the MTJ structure. Junction size plays a crucial role, with smaller dimensions generally exhibiting increased vulnerability to disturb effects due to higher current densities. The thickness ratio between the free and reference layers significantly impacts stability, as thinner free layers may be more susceptible to thermally-assisted switching during read operations.

Material composition presents another critical factor affecting RRD susceptibility. The choice of ferromagnetic materials, tunnel barrier composition, and interface engineering all contribute to the overall resilience against read disturb phenomena. For instance, MgO-based barriers with specific crystalline orientations have demonstrated superior performance compared to earlier amorphous barriers, though they still face challenges at advanced technology nodes.

The shape anisotropy and thermal stability factor (Δ) of the MTJ directly correlate with read disturb immunity. Devices designed with higher Δ values offer greater resistance to thermal fluctuations but may require higher switching currents for write operations, creating a fundamental design trade-off between read stability and write efficiency.

Process variations during manufacturing further complicate the RRD landscape. Minute variations in layer thicknesses, interface quality, or material properties can significantly alter the disturb characteristics across a memory array, leading to reliability concerns and potential yield issues in high-volume production scenarios.

Reading schemes and circuit-level considerations also influence RRD behavior. The amplitude and duration of read pulses, sensing margin design, and reference schemes all contribute to the overall system-level resilience against read disturb effects. Advanced reading techniques incorporating error correction, disturb-aware reading algorithms, and optimized pulse shaping have been proposed to mitigate these challenges.

As MTJ technology scales to smaller dimensions for higher density applications, the correlation between design parameters and read disturb becomes increasingly critical. The industry faces a complex optimization problem balancing multiple factors including thermal stability, switching efficiency, read disturb immunity, and manufacturing feasibility to create commercially viable MTJ-based memory solutions.

Current Approaches to Mitigate Read Disturb Effects

01 MTJ structure design to mitigate read disturb

Specific structural designs of Magnetic Tunnel Junctions can reduce read disturb effects. These designs include optimized free layer configurations, synthetic antiferromagnetic structures, and specialized barrier materials that maintain data integrity during read operations. By engineering the physical structure of MTJs, the resistance to read disturb can be significantly improved while maintaining reliable sensing margins.- MTJ structure design to mitigate read disturb: Specific structural designs of Magnetic Tunnel Junctions can reduce read disturb effects. These designs include optimized free layer configurations, synthetic antiferromagnetic (SAF) reference layers, and specialized tunnel barrier materials. By engineering the physical structure of MTJs, the stability during read operations can be improved while maintaining sufficient signal-to-noise ratio, thus reducing the probability of unintended state changes during reading.

- Read current optimization techniques: Controlling the magnitude, duration, and path of read currents is critical for minimizing read disturb in MTJ devices. Techniques include using lower read current amplitudes, shorter read pulses, and specialized sensing circuits that limit current exposure to the MTJ element. These approaches help maintain the integrity of stored data by reducing the thermal and spin-transfer torque effects that can destabilize the magnetic state during read operations.

- Reference layer stabilization methods: Enhancing the stability of the reference layer in MTJ structures helps prevent read disturb events. This can be achieved through pinning mechanisms, exchange coupling with antiferromagnetic materials, and optimized magnetic anisotropy. A more stable reference layer maintains consistent performance during repeated read operations and reduces the likelihood of state flipping due to thermal fluctuations or stray magnetic fields.

- Sensing circuit designs for read disturb mitigation: Advanced sensing circuit architectures can significantly reduce read disturb vulnerability in MTJ-based memory arrays. These designs include differential sensing schemes, reference cell configurations, and specialized amplifier circuits that minimize the stress on individual MTJ elements. By distributing read operations across multiple components or implementing error correction mechanisms, these circuits maintain data integrity while allowing for reliable state detection.

- Error detection and correction for read disturb events: Implementing error detection and correction mechanisms helps manage read disturb events in MTJ-based memory systems. These approaches include parity checking, error-correcting codes, and periodic refresh operations that can identify and rectify disturbed bits. Some systems also employ predictive algorithms to identify cells at risk of read disturb and proactively refresh their states before errors occur, thereby maintaining data integrity in high-density MTJ memory arrays.

02 Read current optimization techniques

Controlling the magnitude, duration, and pathway of read currents is crucial for minimizing read disturb in MTJ devices. Techniques include implementing current limiters, pulse shaping circuits, and optimized sensing schemes that reduce exposure of the free layer to potentially disturbing currents. These approaches balance the need for reliable readout with minimizing the probability of unintentional magnetization switching.Expand Specific Solutions03 Reference layer stabilization methods

Enhancing the stability of the reference layer in MTJ structures helps prevent read disturb events. This includes using materials with higher coercivity, implementing pinning structures, and designing reference layers that are less susceptible to thermal fluctuations and external magnetic fields. A stable reference layer provides a consistent comparison point for sensing the free layer state without contributing to read disturb issues.Expand Specific Solutions04 Compensation and error correction systems

Advanced error detection and correction mechanisms can be implemented to address read disturb events in MTJ-based memory arrays. These systems include disturb detection circuits, error correction codes, and compensation algorithms that can identify and mitigate the effects of read disturb. Some designs incorporate refresh operations that periodically rewrite potentially vulnerable cells before disturb effects accumulate to critical levels.Expand Specific Solutions05 Sensing circuit innovations

Novel sensing circuit designs can significantly reduce read disturb probability in MTJ devices. These include differential sensing techniques, self-referenced reading methods, and specialized amplifier designs that minimize the stress on the MTJ element during read operations. By improving the sensitivity of the sensing circuits, lower read currents can be used, directly reducing the likelihood of read disturb events while maintaining reliable data access.Expand Specific Solutions

Leading Companies in MTJ Technology Development

The correlation between resistive read disturb and MTJ design is currently in an early growth phase, with the market expanding as MRAM technology gains traction in embedded and standalone memory applications. The global MRAM market is projected to reach significant scale as companies address reliability challenges in MTJ designs. Technical maturity varies across players, with Everspin Technologies leading as a specialized MRAM provider, while major semiconductor companies like QUALCOMM, Samsung, and TSMC integrate MRAM into their portfolios. Research institutions including Chinese Academy of Sciences and CEA are advancing fundamental understanding, while emerging players like Shanghai Ciyu and Avalanche Technology focus on next-generation pSTT-MRAM solutions to mitigate read disturb issues through innovative MTJ designs.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung Electronics has developed comprehensive solutions addressing the correlation between resistive read disturb and MTJ design parameters in their MRAM technology. Their approach incorporates a sophisticated multi-layer MTJ stack with precisely engineered thickness ratios between the free layer, tunnel barrier, and reference layer to minimize read disturb vulnerability while maintaining high tunnel magnetoresistance (TMR) ratios. Samsung's design utilizes perpendicular magnetic anisotropy (PMA) materials with optimized interface properties that enhance thermal stability without increasing susceptibility to read disturb effects. Their technology includes specialized synthetic antiferromagnetic structures with enhanced coupling strength that resist field-induced disturbances during read operations. Samsung has also developed advanced sensing circuits that implement dynamic read current adjustment based on operating conditions and cell characteristics, maintaining the optimal balance between sensing margin and read disturb immunity. Their research has established quantitative models correlating MTJ geometric parameters (diameter, aspect ratio) with read disturb probability, enabling systematic design optimization across different technology nodes.

Strengths: Massive manufacturing infrastructure and integration capabilities; extensive experience in memory production and scaling; ability to optimize both MTJ design and peripheral circuitry. Weaknesses: Competing internal memory technologies (DRAM, NAND) may limit resource allocation to MRAM; challenges in achieving cost parity with established memory technologies; balancing read performance with disturb immunity.

International Business Machines Corp.

Technical Solution: IBM has developed advanced MTJ designs that specifically address the correlation between resistive read disturb and MTJ structural parameters. Their research focuses on optimizing the free layer thickness and composition to achieve an optimal balance between thermal stability and read disturb immunity. IBM's approach incorporates a dual MgO barrier design with engineered interfaces that reduces read current density while maintaining high tunnel magnetoresistance (TMR) ratios. Their MTJ stack includes specialized synthetic antiferromagnetic (SAF) structures with enhanced pinning strength to resist field-induced disturbances during read operations. IBM has also pioneered computational models that predict read disturb vulnerability based on MTJ geometric parameters, enabling design optimization before fabrication. Their latest designs incorporate perpendicular magnetic anisotropy (PMA) materials with carefully engineered damping factors to minimize susceptibility to spin-transfer torque effects during read operations while maintaining data retention capabilities.

Strengths: Extensive research infrastructure and materials expertise; strong patent portfolio in MTJ design; demonstrated ability to model and predict read disturb phenomena. Weaknesses: Limited commercial deployment of their MRAM technologies; research primarily focused on high-performance computing applications rather than broader consumer markets.

Key Patents on Read Disturb Reduction Techniques

Method of reading information in a magnetic memory by a reversible resistance change in a magnetic tunnel junction

PatentInactiveUS20040257849A1

Innovation

- Applying an electromagnetic field to the MTJ to change its electrical resistance, which is reversible upon field removal, allowing for non-destructive reading by measuring the initial and altered resistance states without the need for subsequent writing operations.

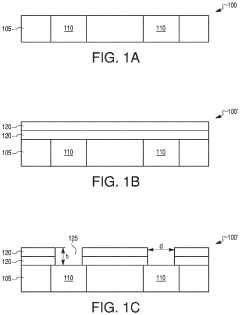

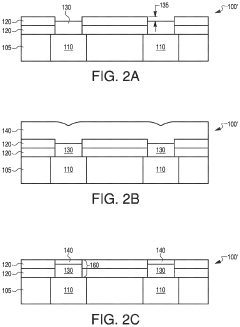

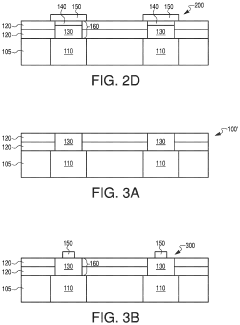

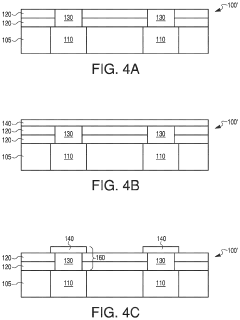

Methods for manufacturing magnetoresistive stack devices

PatentActiveUS12022738B2

Innovation

- The use of atomic layer deposition (ALD) for selectively depositing transition metal layers and tantalum-rich layers within trenches to form seamless vias, allowing for bidirectional current transfer between metal layers and magnetoresistive stacks, thereby improving electrical performance and structural integrity.

Reliability Testing Methodologies for MTJ Devices

Reliability testing methodologies for MTJ devices have evolved significantly to address the complex failure mechanisms inherent in spintronic technologies. Standard testing protocols now incorporate specialized procedures to evaluate read disturb phenomena, particularly focusing on the correlation between resistive read disturb and MTJ design parameters. These methodologies typically include accelerated lifetime testing under various operational conditions, where devices are subjected to millions of read cycles at different current densities and temperatures.

Time-dependent dielectric breakdown (TDDB) testing has been adapted specifically for MTJ structures, allowing researchers to characterize the gradual degradation of tunnel barriers under repeated read operations. This approach enables the extraction of critical reliability parameters such as mean time to failure (MTTF) and activation energy, providing insights into the fundamental relationship between device design and read disturb susceptibility.

Statistical analysis forms a crucial component of modern MTJ reliability assessment. Large sample sets are typically evaluated using Weibull distribution analysis to account for the inherent variability in MTJ performance and failure mechanisms. This statistical approach helps identify outliers and establish confidence intervals for reliability predictions, which is particularly important when correlating specific design features with read disturb resilience.

In-situ characterization techniques have emerged as powerful tools for understanding the progressive nature of read disturb effects. These methods include real-time resistance monitoring during stress testing, magnetic domain imaging via Kerr microscopy, and temperature-dependent transport measurements. Such techniques provide direct observation of failure progression and help establish causal relationships between specific design elements and reliability limitations.

Industry-standard qualification procedures have been established by organizations such as JEDEC, incorporating specific test conditions for MTJ-based devices. These standards typically mandate minimum endurance requirements under worst-case operating conditions, with particular attention to read disturb immunity. The qualification process generally includes both wafer-level reliability testing and packaged device assessment to capture process-induced variations that might affect read disturb susceptibility.

Advanced modeling approaches now complement physical testing, with physics-based simulation tools capable of predicting read disturb vulnerability based on MTJ design parameters. These models incorporate micromagnetic simulations coupled with electron transport calculations to establish theoretical correlations between design choices (such as free layer thickness, shape anisotropy, and tunnel barrier composition) and read disturb thresholds, accelerating the design optimization process.

Time-dependent dielectric breakdown (TDDB) testing has been adapted specifically for MTJ structures, allowing researchers to characterize the gradual degradation of tunnel barriers under repeated read operations. This approach enables the extraction of critical reliability parameters such as mean time to failure (MTTF) and activation energy, providing insights into the fundamental relationship between device design and read disturb susceptibility.

Statistical analysis forms a crucial component of modern MTJ reliability assessment. Large sample sets are typically evaluated using Weibull distribution analysis to account for the inherent variability in MTJ performance and failure mechanisms. This statistical approach helps identify outliers and establish confidence intervals for reliability predictions, which is particularly important when correlating specific design features with read disturb resilience.

In-situ characterization techniques have emerged as powerful tools for understanding the progressive nature of read disturb effects. These methods include real-time resistance monitoring during stress testing, magnetic domain imaging via Kerr microscopy, and temperature-dependent transport measurements. Such techniques provide direct observation of failure progression and help establish causal relationships between specific design elements and reliability limitations.

Industry-standard qualification procedures have been established by organizations such as JEDEC, incorporating specific test conditions for MTJ-based devices. These standards typically mandate minimum endurance requirements under worst-case operating conditions, with particular attention to read disturb immunity. The qualification process generally includes both wafer-level reliability testing and packaged device assessment to capture process-induced variations that might affect read disturb susceptibility.

Advanced modeling approaches now complement physical testing, with physics-based simulation tools capable of predicting read disturb vulnerability based on MTJ design parameters. These models incorporate micromagnetic simulations coupled with electron transport calculations to establish theoretical correlations between design choices (such as free layer thickness, shape anisotropy, and tunnel barrier composition) and read disturb thresholds, accelerating the design optimization process.

Material Science Advancements for MTJ Stability

Recent advancements in material science have significantly contributed to enhancing MTJ (Magnetic Tunnel Junction) stability, directly addressing the correlation between resistive read disturb and MTJ design. The development of novel materials with superior magnetic properties has been pivotal in mitigating read disturb effects while maintaining reliable resistance states.

Researchers have focused on optimizing the composition of ferromagnetic layers, exploring beyond traditional CoFeB to include materials with higher spin polarization and thermal stability. Heusler alloys, particularly Co-based compounds like Co2MnSi and Co2FeSi, have demonstrated promising results with their half-metallic properties, providing nearly 100% spin polarization and enhanced resistance to thermal fluctuations that contribute to read disturb phenomena.

The tunnel barrier material has undergone substantial refinement, moving beyond conventional MgO. Advanced deposition techniques now enable the creation of ultra-thin, defect-free barriers with precisely controlled crystalline orientation. The incorporation of dopants such as nitrogen or boron into MgO has shown remarkable improvements in barrier quality, reducing pinhole formation that often leads to resistance variability during repeated read operations.

Interface engineering between the ferromagnetic layers and the tunnel barrier represents another critical advancement. Atomic-level control of these interfaces through techniques like molecular beam epitaxy and atomic layer deposition has minimized interfacial roughness and interdiffusion, factors that significantly impact read disturb susceptibility. The introduction of insertion layers, only a few angstroms thick, has proven effective in optimizing the magnetic coupling across these interfaces.

Capping layer materials have evolved to provide enhanced protection against oxidation and degradation. Materials such as Ta, Ru, and their multilayer combinations offer superior diffusion barriers while maintaining the desired magnetic properties of the underlying MTJ structure. These advancements have extended device lifetime and stability under repeated read operations.

Perpendicular magnetic anisotropy (PMA) materials represent perhaps the most significant breakthrough in MTJ stability. By transitioning from in-plane to perpendicular magnetization, these materials enable higher thermal stability at smaller dimensions, directly addressing the scaling challenges of MTJ technology. Materials systems incorporating Co/Pt or Co/Pd multilayers, as well as CoFeB/MgO interfaces with enhanced PMA, have demonstrated remarkable resistance to read disturb effects while supporting higher storage densities.

Researchers have focused on optimizing the composition of ferromagnetic layers, exploring beyond traditional CoFeB to include materials with higher spin polarization and thermal stability. Heusler alloys, particularly Co-based compounds like Co2MnSi and Co2FeSi, have demonstrated promising results with their half-metallic properties, providing nearly 100% spin polarization and enhanced resistance to thermal fluctuations that contribute to read disturb phenomena.

The tunnel barrier material has undergone substantial refinement, moving beyond conventional MgO. Advanced deposition techniques now enable the creation of ultra-thin, defect-free barriers with precisely controlled crystalline orientation. The incorporation of dopants such as nitrogen or boron into MgO has shown remarkable improvements in barrier quality, reducing pinhole formation that often leads to resistance variability during repeated read operations.

Interface engineering between the ferromagnetic layers and the tunnel barrier represents another critical advancement. Atomic-level control of these interfaces through techniques like molecular beam epitaxy and atomic layer deposition has minimized interfacial roughness and interdiffusion, factors that significantly impact read disturb susceptibility. The introduction of insertion layers, only a few angstroms thick, has proven effective in optimizing the magnetic coupling across these interfaces.

Capping layer materials have evolved to provide enhanced protection against oxidation and degradation. Materials such as Ta, Ru, and their multilayer combinations offer superior diffusion barriers while maintaining the desired magnetic properties of the underlying MTJ structure. These advancements have extended device lifetime and stability under repeated read operations.

Perpendicular magnetic anisotropy (PMA) materials represent perhaps the most significant breakthrough in MTJ stability. By transitioning from in-plane to perpendicular magnetization, these materials enable higher thermal stability at smaller dimensions, directly addressing the scaling challenges of MTJ technology. Materials systems incorporating Co/Pt or Co/Pd multilayers, as well as CoFeB/MgO interfaces with enhanced PMA, have demonstrated remarkable resistance to read disturb effects while supporting higher storage densities.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!