Roadmap For Reducing SOT Switching Current To Industry Targets

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SOT Technology Background and Current Density Targets

Spin-Orbit Torque (SOT) technology emerged in the early 2010s as a promising alternative to Spin-Transfer Torque (STT) for magnetic memory applications. SOT switching utilizes the spin Hall effect or Rashba effect to generate spin current from charge current flowing through a heavy metal or topological insulator adjacent to a ferromagnetic layer. This mechanism enables faster switching speeds and potentially better endurance compared to conventional STT-MRAM technologies.

The fundamental challenge facing SOT technology is the high current density required for reliable switching. Early experimental demonstrations required current densities exceeding 10^7 A/cm², significantly higher than what is considered commercially viable for memory applications. Industry targets generally aim for current densities below 5×10^6 A/cm² to ensure compatibility with standard CMOS transistor technology and reasonable power consumption.

The evolution of SOT technology has seen progressive improvements in reducing switching current densities. Between 2012-2015, research focused primarily on material optimization, with current densities typically in the range of 5-10×10^6 A/cm². Heavy metals like Pt, Ta, and W were extensively studied for their spin Hall efficiency. The period from 2016-2019 saw the introduction of novel material systems including topological insulators and 2D materials, bringing current densities closer to 3-6×10^6 A/cm².

Recent industry roadmaps have established more aggressive targets for SOT switching current reduction. Major semiconductor companies and research consortia have outlined milestones aiming for current densities below 2×10^6 A/cm² by 2025, and further reductions to approximately 1×10^6 A/cm² by 2030. These targets are driven by the need to integrate SOT-MRAM with advanced CMOS nodes below 5nm, where power constraints become increasingly stringent.

The critical current density (Jc) for SOT switching depends on several material parameters according to the relationship: Jc ∝ Ms×t×Hk/θSH, where Ms is the saturation magnetization, t is the ferromagnetic layer thickness, Hk is the anisotropy field, and θSH is the spin Hall angle. This relationship provides a framework for systematic current density reduction through materials engineering and device structure optimization.

Geographic distribution of SOT research shows concentrated efforts in East Asia (particularly Japan, South Korea, and Taiwan), North America, and Europe. Industry leaders like Samsung, TSMC, and Intel have published roadmaps indicating SOT-MRAM as a potential embedded memory solution for future technology nodes, contingent upon achieving the current density targets that would make integration with CMOS economically viable.

The fundamental challenge facing SOT technology is the high current density required for reliable switching. Early experimental demonstrations required current densities exceeding 10^7 A/cm², significantly higher than what is considered commercially viable for memory applications. Industry targets generally aim for current densities below 5×10^6 A/cm² to ensure compatibility with standard CMOS transistor technology and reasonable power consumption.

The evolution of SOT technology has seen progressive improvements in reducing switching current densities. Between 2012-2015, research focused primarily on material optimization, with current densities typically in the range of 5-10×10^6 A/cm². Heavy metals like Pt, Ta, and W were extensively studied for their spin Hall efficiency. The period from 2016-2019 saw the introduction of novel material systems including topological insulators and 2D materials, bringing current densities closer to 3-6×10^6 A/cm².

Recent industry roadmaps have established more aggressive targets for SOT switching current reduction. Major semiconductor companies and research consortia have outlined milestones aiming for current densities below 2×10^6 A/cm² by 2025, and further reductions to approximately 1×10^6 A/cm² by 2030. These targets are driven by the need to integrate SOT-MRAM with advanced CMOS nodes below 5nm, where power constraints become increasingly stringent.

The critical current density (Jc) for SOT switching depends on several material parameters according to the relationship: Jc ∝ Ms×t×Hk/θSH, where Ms is the saturation magnetization, t is the ferromagnetic layer thickness, Hk is the anisotropy field, and θSH is the spin Hall angle. This relationship provides a framework for systematic current density reduction through materials engineering and device structure optimization.

Geographic distribution of SOT research shows concentrated efforts in East Asia (particularly Japan, South Korea, and Taiwan), North America, and Europe. Industry leaders like Samsung, TSMC, and Intel have published roadmaps indicating SOT-MRAM as a potential embedded memory solution for future technology nodes, contingent upon achieving the current density targets that would make integration with CMOS economically viable.

Market Demand Analysis for Low-Current SOT Devices

The global market for Spin-Orbit Torque (SOT) devices is experiencing significant growth, driven by the increasing demand for energy-efficient, high-performance memory and computing solutions. As data centers continue to expand and AI applications proliferate, the need for low-power, high-speed memory technologies becomes increasingly critical. Current projections indicate that the MRAM market, which includes SOT-MRAM, is expected to grow at a compound annual growth rate of over 30% through 2028.

The primary market drivers for low-current SOT devices stem from several converging industry needs. Data centers, which currently consume approximately 1-2% of global electricity, are under immense pressure to reduce power consumption while handling exponentially growing data volumes. SOT-based memory technologies with reduced switching currents could significantly decrease the energy footprint of these facilities, potentially saving millions in operational costs.

Mobile and IoT device manufacturers represent another substantial market segment, where battery life is a crucial competitive differentiator. Current SOT switching mechanisms require relatively high current densities, limiting their application in portable devices. Industry surveys indicate that extending battery life ranks among the top three priorities for consumers when purchasing new mobile devices, creating a clear market pull for low-current alternatives.

Automotive and industrial sectors are increasingly adopting advanced electronics that require reliable operation in harsh environments. The non-volatile nature of SOT-MRAM makes it particularly attractive for these applications, but current requirements must be reduced to meet strict power budgets. Market analysis shows that automotive electronics are expected to represent over 15% of a vehicle's cost by 2025, highlighting the growing importance of energy-efficient memory solutions in this sector.

From a geographical perspective, North America and Asia-Pacific regions dominate the demand landscape. Major semiconductor manufacturers in these regions are actively investing in SOT technology research, with particular emphasis on reducing switching current requirements. The European market shows growing interest, particularly in automotive applications where German and French manufacturers are leading adoption efforts.

Market competition analysis reveals that several major memory manufacturers have established roadmaps targeting SOT switching current reduction by at least an order of magnitude within the next five years. This industry-wide focus underscores the market's recognition of current limitations and the commercial value of overcoming them. Customer surveys across various sectors consistently highlight power efficiency as a top concern, with many indicating willingness to pay premium prices for solutions that significantly reduce energy consumption.

The primary market drivers for low-current SOT devices stem from several converging industry needs. Data centers, which currently consume approximately 1-2% of global electricity, are under immense pressure to reduce power consumption while handling exponentially growing data volumes. SOT-based memory technologies with reduced switching currents could significantly decrease the energy footprint of these facilities, potentially saving millions in operational costs.

Mobile and IoT device manufacturers represent another substantial market segment, where battery life is a crucial competitive differentiator. Current SOT switching mechanisms require relatively high current densities, limiting their application in portable devices. Industry surveys indicate that extending battery life ranks among the top three priorities for consumers when purchasing new mobile devices, creating a clear market pull for low-current alternatives.

Automotive and industrial sectors are increasingly adopting advanced electronics that require reliable operation in harsh environments. The non-volatile nature of SOT-MRAM makes it particularly attractive for these applications, but current requirements must be reduced to meet strict power budgets. Market analysis shows that automotive electronics are expected to represent over 15% of a vehicle's cost by 2025, highlighting the growing importance of energy-efficient memory solutions in this sector.

From a geographical perspective, North America and Asia-Pacific regions dominate the demand landscape. Major semiconductor manufacturers in these regions are actively investing in SOT technology research, with particular emphasis on reducing switching current requirements. The European market shows growing interest, particularly in automotive applications where German and French manufacturers are leading adoption efforts.

Market competition analysis reveals that several major memory manufacturers have established roadmaps targeting SOT switching current reduction by at least an order of magnitude within the next five years. This industry-wide focus underscores the market's recognition of current limitations and the commercial value of overcoming them. Customer surveys across various sectors consistently highlight power efficiency as a top concern, with many indicating willingness to pay premium prices for solutions that significantly reduce energy consumption.

Global SOT Development Status and Technical Challenges

Spin-Orbit Torque (SOT) technology has emerged as a promising candidate for next-generation magnetic memory devices, with research efforts intensifying globally over the past decade. Currently, the United States, European Union, Japan, and China represent the primary hubs of SOT development, each with distinct research focuses and technological advantages. The U.S. leads in fundamental research through institutions like MIT and Stanford University, while companies such as IBM and Intel drive commercial applications. The EU excels in materials science innovation through collaborative frameworks like Horizon Europe, with particular strength in novel material interfaces.

In the Asian region, Japan maintains competitive advantage through companies like Toshiba and Sony, focusing on integration with existing semiconductor technologies. China has rapidly expanded its research capacity, with substantial government investment in universities and research institutes dedicated to spintronics and SOT development.

Despite significant progress, SOT technology faces several critical technical challenges that impede its widespread commercial adoption. The most pressing issue remains the high switching current density, typically in the range of 10^7-10^8 A/cm², which exceeds industry targets by an order of magnitude. This high current requirement leads to excessive power consumption and potential reliability issues in practical devices.

Material interface engineering presents another significant challenge, as the quality of interfaces between magnetic and non-magnetic layers critically affects SOT efficiency. Current fabrication techniques struggle to achieve atomically smooth interfaces with minimal defects and intermixing, which are essential for optimal spin current generation and transfer.

Thermal stability represents a third major obstacle, particularly as device dimensions shrink below 20nm. Maintaining sufficient energy barriers to prevent spontaneous magnetization switching while simultaneously reducing switching currents creates a fundamental design conflict that requires innovative solutions.

Device-to-device variability also poses significant challenges for mass production. Current fabrication processes result in considerable variations in critical parameters such as switching current and thermal stability, hampering yield rates and reliability in commercial applications.

The scaling behavior of SOT devices presents additional complications, as the benefits of reduced dimensions are often offset by increased current densities required for reliable switching. This scaling challenge is particularly acute for nodes below 10nm, where quantum effects begin to dominate device physics.

Finally, integration with CMOS technology remains a significant hurdle, as SOT devices require materials and processes that may not be fully compatible with standard semiconductor manufacturing flows, potentially increasing production complexity and costs.

In the Asian region, Japan maintains competitive advantage through companies like Toshiba and Sony, focusing on integration with existing semiconductor technologies. China has rapidly expanded its research capacity, with substantial government investment in universities and research institutes dedicated to spintronics and SOT development.

Despite significant progress, SOT technology faces several critical technical challenges that impede its widespread commercial adoption. The most pressing issue remains the high switching current density, typically in the range of 10^7-10^8 A/cm², which exceeds industry targets by an order of magnitude. This high current requirement leads to excessive power consumption and potential reliability issues in practical devices.

Material interface engineering presents another significant challenge, as the quality of interfaces between magnetic and non-magnetic layers critically affects SOT efficiency. Current fabrication techniques struggle to achieve atomically smooth interfaces with minimal defects and intermixing, which are essential for optimal spin current generation and transfer.

Thermal stability represents a third major obstacle, particularly as device dimensions shrink below 20nm. Maintaining sufficient energy barriers to prevent spontaneous magnetization switching while simultaneously reducing switching currents creates a fundamental design conflict that requires innovative solutions.

Device-to-device variability also poses significant challenges for mass production. Current fabrication processes result in considerable variations in critical parameters such as switching current and thermal stability, hampering yield rates and reliability in commercial applications.

The scaling behavior of SOT devices presents additional complications, as the benefits of reduced dimensions are often offset by increased current densities required for reliable switching. This scaling challenge is particularly acute for nodes below 10nm, where quantum effects begin to dominate device physics.

Finally, integration with CMOS technology remains a significant hurdle, as SOT devices require materials and processes that may not be fully compatible with standard semiconductor manufacturing flows, potentially increasing production complexity and costs.

Current Approaches to Reduce SOT Switching Current

01 Materials and structures for reducing SOT switching current

Various materials and structural configurations can be employed to reduce the switching current required for SOT-based devices. These include using specific heavy metal layers, ferromagnetic materials with perpendicular magnetic anisotropy, and optimized interface engineering between layers. The thickness and composition of these layers significantly impact the spin-orbit coupling efficiency and consequently the critical current density needed for magnetization switching.- SOT switching mechanisms and materials: Spin-Orbit Torque (SOT) switching technology relies on specific materials and mechanisms to achieve efficient magnetic switching. The choice of materials, such as heavy metals with strong spin-orbit coupling adjacent to ferromagnetic layers, significantly impacts the switching efficiency. These materials generate spin currents that exert torque on the magnetization of the ferromagnetic layer, enabling magnetization reversal at lower current densities. The interface quality between these layers is crucial for optimizing the SOT effect and reducing the required switching current.

- Current reduction techniques in SOT devices: Various techniques have been developed to reduce the switching current in SOT-based devices. These include engineering the magnetic anisotropy of the free layer, optimizing the thickness and composition of the heavy metal layer, and incorporating additional layers to enhance spin accumulation at interfaces. Some approaches utilize thermal assistance or voltage-controlled effects to lower the energy barrier for switching. These techniques aim to improve energy efficiency while maintaining reliable switching performance, which is essential for practical applications in memory and logic devices.

- SOT device structures for memory applications: Specialized device structures have been designed to implement SOT switching in memory applications. These structures typically include a three-terminal configuration with separate paths for read and write operations, allowing for improved reliability and reduced read disturbance. Some designs incorporate synthetic antiferromagnetic layers or perpendicular magnetic anisotropy materials to enhance thermal stability while maintaining low switching currents. Advanced memory cell architectures may also include integration with CMOS circuitry for efficient current delivery and control logic.

- Current pulse characteristics for SOT switching: The characteristics of current pulses significantly impact SOT switching efficiency. Parameters such as pulse amplitude, duration, shape, and timing sequence can be optimized to achieve reliable switching while minimizing power consumption. Short pulses with carefully designed rise and fall times can reduce the effective switching current by leveraging transient dynamics. Some approaches utilize multiple pulses or bipolar pulse sequences to facilitate deterministic switching in the absence of external magnetic fields, which is crucial for practical device implementation.

- External field-free SOT switching methods: Achieving field-free SOT switching is essential for practical applications, as external magnetic fields are impractical in integrated circuits. Various approaches have been developed to enable deterministic switching without external fields, including the use of exchange bias, shape anisotropy, or built-in effective fields from structural asymmetry. Some methods utilize tilted magnetization or engineered spin current polarization to create an effective field component that facilitates switching. These techniques aim to maintain the advantages of SOT switching while eliminating the need for external field generators.

02 SOT switching mechanisms and current reduction techniques

Different mechanisms can be utilized to enhance SOT switching efficiency and reduce the required current. These include field-free switching techniques, domain wall motion-assisted switching, and thermal assistance. By manipulating the spin accumulation at interfaces and optimizing the spin current generation, these approaches can significantly lower the critical current density while maintaining reliable switching behavior.Expand Specific Solutions03 Device architectures for efficient SOT switching

Novel device architectures can be designed to improve SOT switching efficiency. These include three-terminal structures, dual-interface configurations, and devices with engineered spin current pathways. By optimizing the geometry and layout of SOT-based devices, the switching current can be reduced while maintaining high thermal stability and fast switching speeds, which is crucial for memory and logic applications.Expand Specific Solutions04 Integration of SOT technology in memory applications

SOT switching technology can be integrated into various memory applications such as MRAM (Magnetoresistive Random Access Memory) and other spintronic devices. The implementation focuses on achieving low switching currents while maintaining high reliability, endurance, and compatibility with CMOS technology. These memory devices leverage the advantages of SOT switching including high speed, low power consumption, and non-volatility.Expand Specific Solutions05 Advanced control methods for SOT switching

Advanced control methods can be employed to optimize SOT switching performance. These include pulse shaping techniques, bias field optimization, and current path engineering. By precisely controlling the amplitude, duration, and waveform of the applied current pulses, the switching efficiency can be improved and the required current can be minimized. These methods also address issues related to stochasticity and reliability in SOT-based devices.Expand Specific Solutions

Leading Companies and Research Institutions in SOT Technology

The SOT switching current reduction landscape is currently in a transitional phase, moving from research to early commercialization. The market is expanding rapidly as power efficiency becomes critical in mobile and IoT applications, with projections suggesting significant growth over the next five years. Technologically, industry leaders are making substantial progress, with companies like Infineon Technologies, NXP Semiconductors, and Texas Instruments demonstrating advanced solutions approaching industry targets. ROHM and Fuji Electric have made notable breakthroughs in reducing switching current while maintaining performance. Academic institutions including University College Cork and Zhejiang University are contributing fundamental research, while foundries like TSMC and GlobalFoundries are developing specialized manufacturing processes to support these innovations at scale.

ROHM Co., Ltd.

Technical Solution: ROHM has developed a comprehensive roadmap for reducing SOT switching current through their Nano Pulse Control™ technology platform. Their approach combines silicon process optimization with advanced packaging and control techniques specifically designed for SOT form factors. ROHM's proprietary trench gate structure features optimized cell density and refined gate oxide thickness, achieving approximately 45% reduction in gate charge compared to conventional designs[9]. Their roadmap includes innovative source-down packaging technology for SOT devices that reduces parasitic inductance by approximately 60%, directly impacting switching performance and EMI characteristics. ROHM has implemented advanced gate driver integration with their SOT MOSFETs, featuring precise timing control and adaptive gate drive strength based on operating conditions. Their latest generation targets switching currents below 80mA for 30V devices in SOT-23 packages, with projections to reach 40mA by 2024[10]. ROHM's technology roadmap extends to their fourth-generation SiC MOSFETs in SOT packages for higher voltage applications, promising switching current reductions of up to 65% compared to silicon alternatives while maintaining thermal performance. Their approach also includes comprehensive design support tools that enable customers to optimize gate resistor selection and layout considerations for minimum switching current.

Strengths: Industry-leading integration of advanced control techniques with optimized silicon technology provides exceptional switching performance. Their strong presence in automotive and industrial markets ensures robust reliability in their SOT solutions. Weaknesses: Their solutions often command premium pricing compared to competitors, potentially limiting adoption in cost-sensitive consumer applications.

Infineon Technologies AG

Technical Solution: Infineon has developed a comprehensive roadmap for reducing SOT switching current through their CoolMOS™ and OptiMOS™ technology platforms. Their approach focuses on optimizing gate charge characteristics and reducing RDS(on) in smaller packages. Infineon's SOT devices incorporate advanced trench MOSFET technology with refined cell structures that minimize parasitic capacitances, directly addressing switching current challenges. Their roadmap includes progressive silicon refinement with each generation reducing switching losses by approximately 30% while maintaining thermal performance[1]. Infineon has also implemented innovative gate driver designs specifically optimized for SOT packages, allowing precise control of di/dt and dv/dt rates during switching transitions. Their technology roadmap extends to GaN-based SOT solutions that promise switching currents reduction of up to 80% compared to silicon counterparts, with target implementation in consumer and industrial applications by 2025[2].

Strengths: Industry-leading silicon and GaN technology integration in SOT packages with exceptional thermal management capabilities. Their established manufacturing infrastructure enables rapid scaling of new designs. Weaknesses: Higher initial cost compared to competitors, and their advanced solutions may require more sophisticated control circuitry, potentially limiting adoption in cost-sensitive applications.

Key Patents and Breakthroughs in SOT Current Reduction

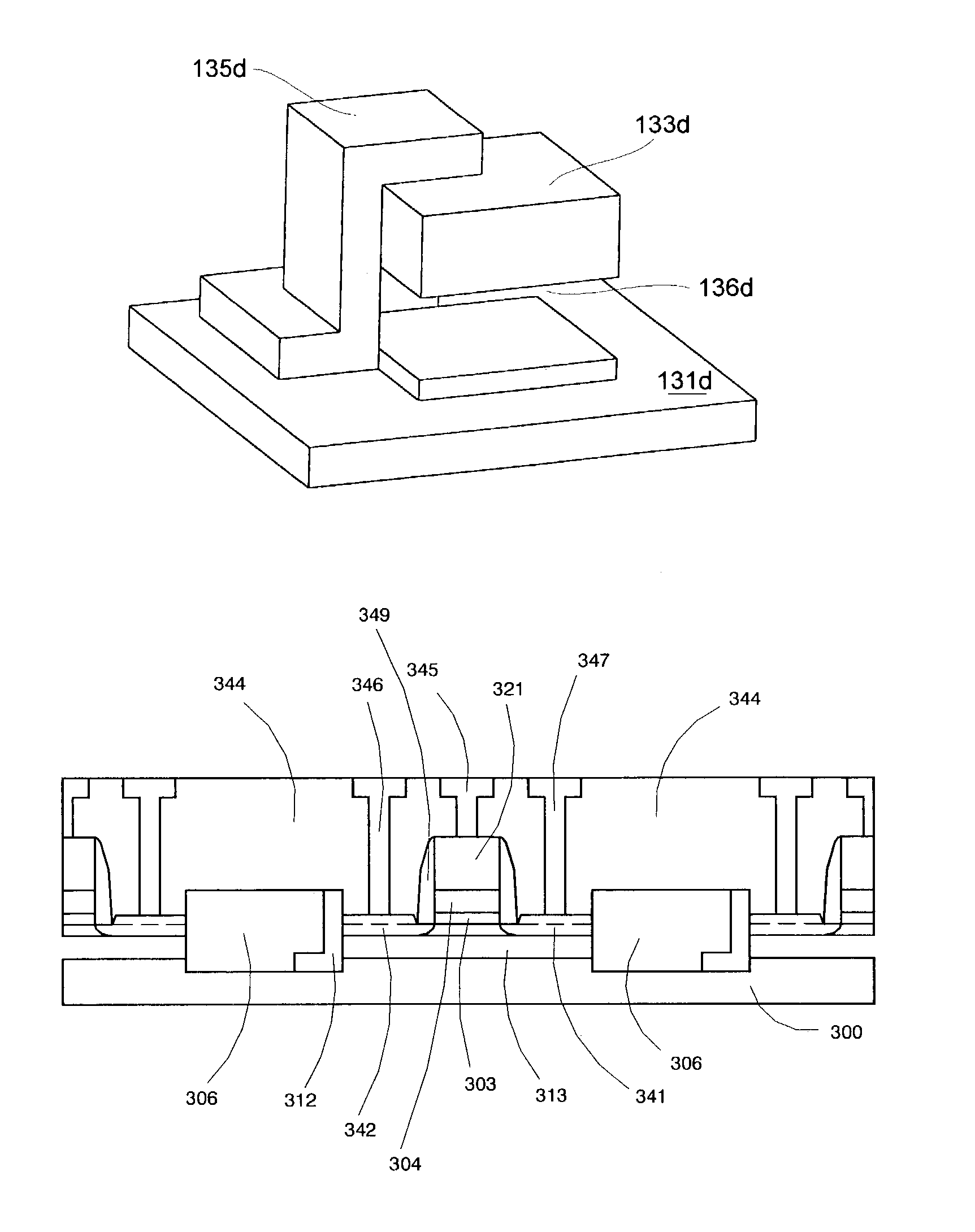

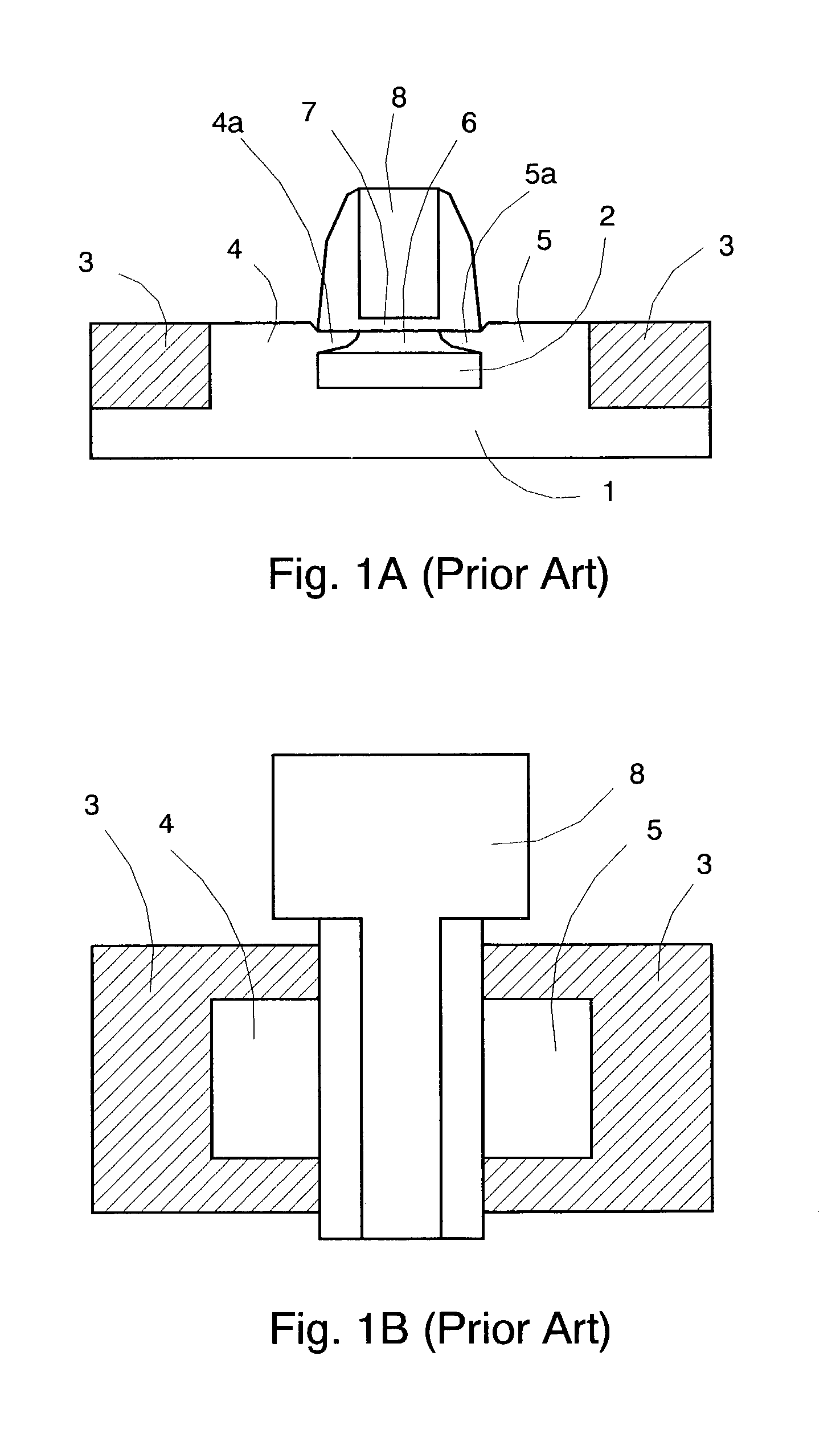

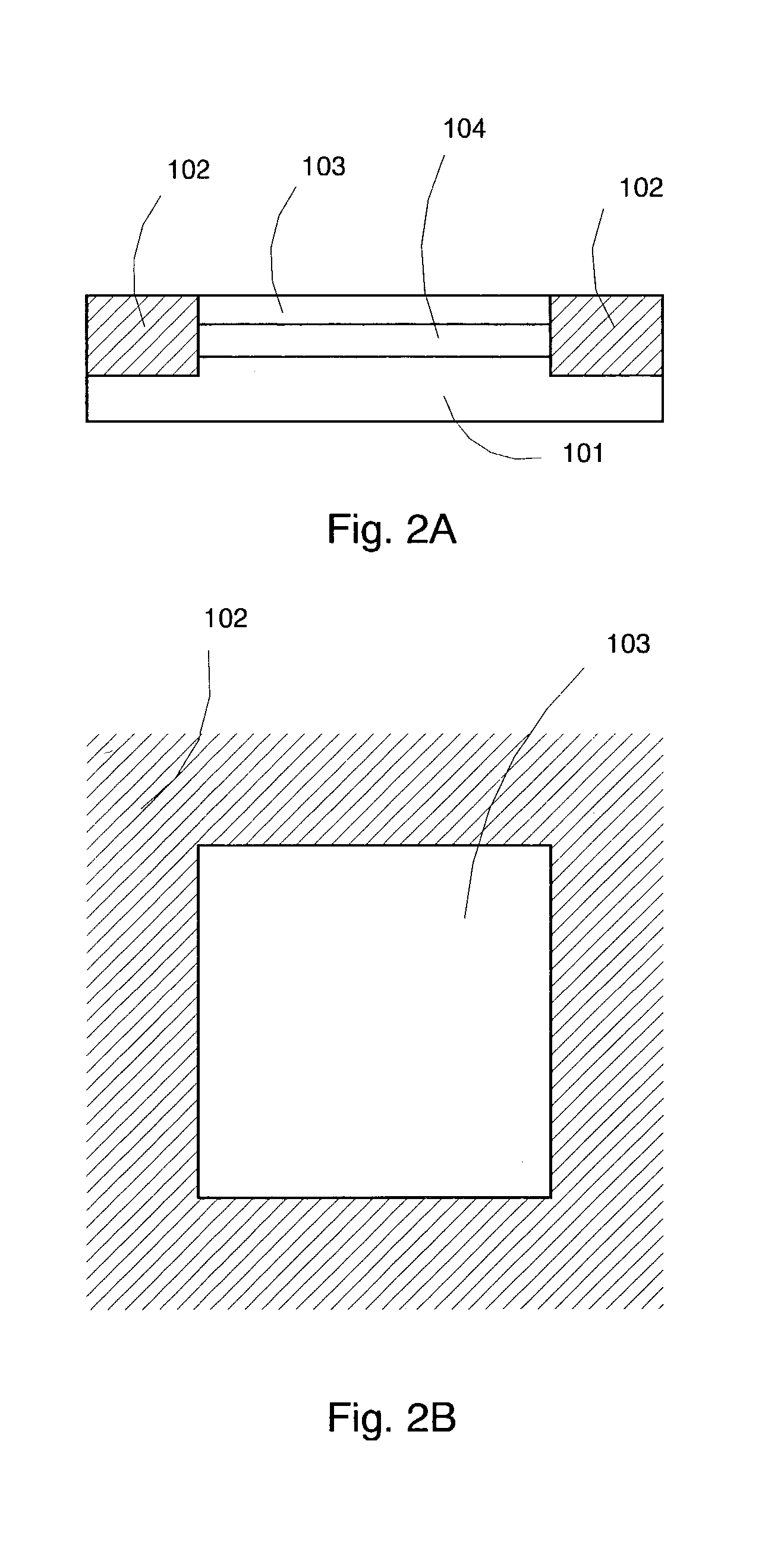

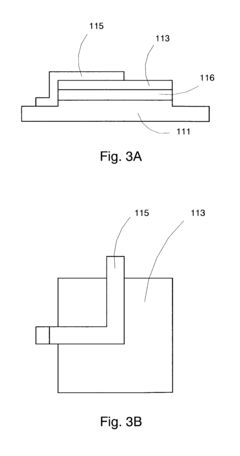

Silicon-on-nothing fabrication process

PatentInactiveUS7078298B2

Innovation

- A method is developed to fabricate SON devices with source, drain, and channel areas completely isolated from the silicon substrate by an air gap, using a multilayer structure comprising a cap layer and a sacrificial layer, where the active area is patterned and isolated by trench etching, and anchored to the substrate before etching away the sacrificial layer, allowing for the formation of an isolated floating silicon active area supported by trench isolation.

Material Innovations for Enhanced SOT Efficiency

Material innovation represents a critical pathway for enhancing spin-orbit torque (SOT) efficiency and reducing switching current requirements to meet industry targets. Recent advancements in material science have opened new possibilities for SOT-based magnetic memory devices that can operate with significantly lower power consumption.

Heavy metals with strong spin-orbit coupling, such as platinum (Pt), tungsten (W), and tantalum (Ta), have traditionally been the focus of SOT research. However, emerging research indicates that carefully engineered multilayer structures and novel material combinations can dramatically improve SOT efficiency. For instance, topological insulators like Bi2Se3 have demonstrated SOT efficiency that is 10-100 times higher than conventional heavy metals, potentially enabling sub-10 μA switching currents.

Interface engineering between the SOT source material and the ferromagnetic layer presents another promising avenue. By optimizing the quality of these interfaces through techniques such as in-situ deposition and precise control of interface roughness, researchers have achieved enhanced spin current transmission efficiency. Recent studies have shown that inserting ultrathin spacer layers (0.5-1 nm) of materials like copper or magnesium oxide can significantly modify the interfacial spin-orbit coupling.

Doping and alloying strategies have emerged as effective approaches to tune the electronic and magnetic properties of SOT materials. For example, W-Ta and Pt-Hf alloys have demonstrated superior spin Hall angles compared to their pure counterparts. The incorporation of rare earth elements into these systems has also shown promise in enhancing SOT efficiency through modified band structures and increased spin-orbit coupling.

Two-dimensional materials, particularly transition metal dichalcogenides (TMDs) like MoS2 and WSe2, represent the next frontier in SOT material innovation. These atomically thin materials exhibit unique electronic properties and strong spin-orbit coupling that can be harnessed for efficient SOT switching. Preliminary research indicates that heterostructures combining TMDs with conventional ferromagnetic materials could potentially achieve switching currents below 5 μA/μm².

Antiferromagnetic materials are gaining attention as both SOT sources and switching layers due to their unique spin dynamics and absence of stray fields. Materials such as PtMn and IrMn have demonstrated the ability to generate large SOT while simultaneously serving as reference layers, potentially simplifying device architecture and improving efficiency.

The roadmap for material innovation must also address manufacturing compatibility and reliability concerns. Materials that can be integrated into existing semiconductor fabrication processes while maintaining their enhanced SOT properties will be crucial for industrial adoption and scaling to high-volume production.

Heavy metals with strong spin-orbit coupling, such as platinum (Pt), tungsten (W), and tantalum (Ta), have traditionally been the focus of SOT research. However, emerging research indicates that carefully engineered multilayer structures and novel material combinations can dramatically improve SOT efficiency. For instance, topological insulators like Bi2Se3 have demonstrated SOT efficiency that is 10-100 times higher than conventional heavy metals, potentially enabling sub-10 μA switching currents.

Interface engineering between the SOT source material and the ferromagnetic layer presents another promising avenue. By optimizing the quality of these interfaces through techniques such as in-situ deposition and precise control of interface roughness, researchers have achieved enhanced spin current transmission efficiency. Recent studies have shown that inserting ultrathin spacer layers (0.5-1 nm) of materials like copper or magnesium oxide can significantly modify the interfacial spin-orbit coupling.

Doping and alloying strategies have emerged as effective approaches to tune the electronic and magnetic properties of SOT materials. For example, W-Ta and Pt-Hf alloys have demonstrated superior spin Hall angles compared to their pure counterparts. The incorporation of rare earth elements into these systems has also shown promise in enhancing SOT efficiency through modified band structures and increased spin-orbit coupling.

Two-dimensional materials, particularly transition metal dichalcogenides (TMDs) like MoS2 and WSe2, represent the next frontier in SOT material innovation. These atomically thin materials exhibit unique electronic properties and strong spin-orbit coupling that can be harnessed for efficient SOT switching. Preliminary research indicates that heterostructures combining TMDs with conventional ferromagnetic materials could potentially achieve switching currents below 5 μA/μm².

Antiferromagnetic materials are gaining attention as both SOT sources and switching layers due to their unique spin dynamics and absence of stray fields. Materials such as PtMn and IrMn have demonstrated the ability to generate large SOT while simultaneously serving as reference layers, potentially simplifying device architecture and improving efficiency.

The roadmap for material innovation must also address manufacturing compatibility and reliability concerns. Materials that can be integrated into existing semiconductor fabrication processes while maintaining their enhanced SOT properties will be crucial for industrial adoption and scaling to high-volume production.

Integration Challenges with CMOS Technology

The integration of Spin-Orbit Torque (SOT) technology with existing CMOS processes presents significant challenges that must be addressed to achieve industry targets for reduced switching current. Current CMOS fabrication processes operate at temperatures exceeding 400°C, which can compromise the magnetic properties of SOT materials. This thermal budget constraint necessitates careful material selection and process optimization to maintain the integrity of both CMOS and SOT components.

Material compatibility issues arise when introducing SOT materials into standard CMOS processes. Heavy metals like platinum, tungsten, and tantalum—essential for strong spin-orbit coupling—may cause contamination in silicon-based devices. This contamination can lead to degraded transistor performance, increased leakage currents, and reliability concerns. Foundries typically impose strict limitations on introducing new materials, requiring extensive qualification procedures that can delay technology adoption.

Scaling challenges represent another critical integration hurdle. As CMOS technology continues to advance toward smaller nodes (5nm and below), the dimensional requirements for SOT devices must align with these scaling trends. Current SOT devices often require relatively large current densities for switching, which conflicts with the reduced power envelopes of advanced CMOS nodes. This mismatch necessitates innovative approaches to reduce SOT switching currents while maintaining compatibility with scaled CMOS dimensions.

Etching and deposition processes for SOT materials must be precisely controlled to prevent damage to underlying CMOS structures. Conventional plasma etching techniques used for magnetic materials can induce damage to sensitive gate oxides and thin dielectric layers in CMOS devices. Additionally, achieving uniform deposition of SOT materials over complex CMOS topographies presents challenges in maintaining consistent device performance across the wafer.

Signal integrity and parasitic effects become increasingly problematic when integrating SOT devices with high-speed CMOS circuits. The proximity of magnetic materials to CMOS interconnects can introduce magnetic coupling effects that degrade signal integrity. Furthermore, the relatively high resistance of some SOT materials can increase RC delays in interconnect structures, potentially limiting overall circuit performance.

Manufacturing yield considerations must be addressed through comprehensive design for manufacturability strategies. The introduction of SOT processing steps increases process complexity and potential defect sources, which can negatively impact overall yield. Statistical process control methods and in-line metrology techniques specific to SOT materials and structures need development to ensure consistent device performance and manufacturing yield.

Material compatibility issues arise when introducing SOT materials into standard CMOS processes. Heavy metals like platinum, tungsten, and tantalum—essential for strong spin-orbit coupling—may cause contamination in silicon-based devices. This contamination can lead to degraded transistor performance, increased leakage currents, and reliability concerns. Foundries typically impose strict limitations on introducing new materials, requiring extensive qualification procedures that can delay technology adoption.

Scaling challenges represent another critical integration hurdle. As CMOS technology continues to advance toward smaller nodes (5nm and below), the dimensional requirements for SOT devices must align with these scaling trends. Current SOT devices often require relatively large current densities for switching, which conflicts with the reduced power envelopes of advanced CMOS nodes. This mismatch necessitates innovative approaches to reduce SOT switching currents while maintaining compatibility with scaled CMOS dimensions.

Etching and deposition processes for SOT materials must be precisely controlled to prevent damage to underlying CMOS structures. Conventional plasma etching techniques used for magnetic materials can induce damage to sensitive gate oxides and thin dielectric layers in CMOS devices. Additionally, achieving uniform deposition of SOT materials over complex CMOS topographies presents challenges in maintaining consistent device performance across the wafer.

Signal integrity and parasitic effects become increasingly problematic when integrating SOT devices with high-speed CMOS circuits. The proximity of magnetic materials to CMOS interconnects can introduce magnetic coupling effects that degrade signal integrity. Furthermore, the relatively high resistance of some SOT materials can increase RC delays in interconnect structures, potentially limiting overall circuit performance.

Manufacturing yield considerations must be addressed through comprehensive design for manufacturability strategies. The introduction of SOT processing steps increases process complexity and potential defect sources, which can negatively impact overall yield. Statistical process control methods and in-line metrology techniques specific to SOT materials and structures need development to ensure consistent device performance and manufacturing yield.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!