Interlayer Diffusion Mitigation Strategies In SOT Stacks

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

SOT Stack Diffusion Background and Objectives

Spin-orbit torque (SOT) technology has emerged as a promising candidate for next-generation magnetic memory and logic devices, offering advantages in energy efficiency, scalability, and operational speed compared to conventional spin-transfer torque (STT) approaches. The fundamental principle of SOT relies on the conversion of charge current to spin current at interfaces between materials with different spin-orbit coupling strengths, which can then manipulate the magnetization of adjacent ferromagnetic layers.

The evolution of SOT technology can be traced back to early theoretical predictions in the 2000s, followed by experimental demonstrations around 2010-2012 that verified the ability to switch magnetic states using SOT. Since then, the field has witnessed rapid advancement in materials engineering, device architectures, and understanding of underlying physical mechanisms. Current research trends focus on enhancing SOT efficiency, reducing critical switching currents, and improving thermal stability for practical applications.

A critical challenge hindering the commercial implementation of SOT devices is interlayer diffusion within the multilayer stack structures. These stacks typically consist of heavy metal layers (such as Pt, Ta, or W), ferromagnetic layers, and various interface materials. During device fabrication and operation, especially at elevated temperatures, atomic migration between these layers can significantly degrade device performance and reliability.

The primary technical objectives for addressing SOT stack diffusion include: developing thermally stable material combinations that maintain sharp interfaces even after high-temperature processing; identifying effective diffusion barrier materials compatible with SOT operation; optimizing deposition techniques to minimize initial intermixing; and establishing reliable characterization methodologies to quantify diffusion effects on device performance.

Understanding the fundamental mechanisms driving interlayer diffusion in SOT stacks is essential, as different material combinations exhibit varying diffusion behaviors based on factors such as atomic size mismatch, chemical affinity, crystalline structure, and defect concentration. Recent studies have highlighted how even nanometer-scale diffusion can dramatically alter the spin-orbit coupling at critical interfaces, thereby affecting SOT efficiency.

The technological goal is to achieve SOT devices with thermal stability up to 400°C for post-CMOS integration compatibility while maintaining functional performance parameters such as low switching current density (<10^6 A/cm²), high thermal stability factor (>60), and reliable endurance (>10^12 cycles). Meeting these objectives would position SOT technology as a viable solution for embedded memory applications, neuromorphic computing systems, and ultra-low power electronics.

The evolution of SOT technology can be traced back to early theoretical predictions in the 2000s, followed by experimental demonstrations around 2010-2012 that verified the ability to switch magnetic states using SOT. Since then, the field has witnessed rapid advancement in materials engineering, device architectures, and understanding of underlying physical mechanisms. Current research trends focus on enhancing SOT efficiency, reducing critical switching currents, and improving thermal stability for practical applications.

A critical challenge hindering the commercial implementation of SOT devices is interlayer diffusion within the multilayer stack structures. These stacks typically consist of heavy metal layers (such as Pt, Ta, or W), ferromagnetic layers, and various interface materials. During device fabrication and operation, especially at elevated temperatures, atomic migration between these layers can significantly degrade device performance and reliability.

The primary technical objectives for addressing SOT stack diffusion include: developing thermally stable material combinations that maintain sharp interfaces even after high-temperature processing; identifying effective diffusion barrier materials compatible with SOT operation; optimizing deposition techniques to minimize initial intermixing; and establishing reliable characterization methodologies to quantify diffusion effects on device performance.

Understanding the fundamental mechanisms driving interlayer diffusion in SOT stacks is essential, as different material combinations exhibit varying diffusion behaviors based on factors such as atomic size mismatch, chemical affinity, crystalline structure, and defect concentration. Recent studies have highlighted how even nanometer-scale diffusion can dramatically alter the spin-orbit coupling at critical interfaces, thereby affecting SOT efficiency.

The technological goal is to achieve SOT devices with thermal stability up to 400°C for post-CMOS integration compatibility while maintaining functional performance parameters such as low switching current density (<10^6 A/cm²), high thermal stability factor (>60), and reliable endurance (>10^12 cycles). Meeting these objectives would position SOT technology as a viable solution for embedded memory applications, neuromorphic computing systems, and ultra-low power electronics.

Market Analysis for SOT-MRAM Technologies

The global market for SOT-MRAM (Spin-Orbit Torque Magnetic Random Access Memory) technologies is experiencing significant growth, driven by increasing demand for high-performance, non-volatile memory solutions across various industries. Current market valuations place the overall MRAM market at approximately $1.1 billion in 2023, with SOT-MRAM representing an emerging segment poised for rapid expansion over the next decade.

The SOT-MRAM market is primarily segmented across computing, automotive, industrial automation, aerospace, and telecommunications sectors. In computing applications, SOT-MRAM offers compelling advantages for cache memory and storage-class memory, with potential to replace both SRAM and DRAM in specific use cases. The automotive sector represents another high-growth area, particularly for advanced driver assistance systems (ADAS) and autonomous vehicles requiring radiation-hardened, temperature-stable memory solutions.

Market analysis indicates that interlayer diffusion challenges in SOT stacks represent a critical technical barrier affecting both production yields and long-term reliability of devices. This technical limitation directly impacts market penetration rates, with current estimates suggesting that solving diffusion issues could accelerate market adoption by 30-40% in key segments.

Regional market distribution shows North America leading in SOT-MRAM research and development, accounting for approximately 45% of global investment. Asia-Pacific follows with 35%, driven primarily by semiconductor manufacturing powerhouses in South Korea, Taiwan, and Japan. Europe contributes about 20%, with particular strength in automotive and industrial applications.

From a competitive landscape perspective, major semiconductor manufacturers including Samsung, Intel, TSMC, and GlobalFoundries are investing heavily in SOT-MRAM technology development. Several specialized memory manufacturers and startups have also entered this space, focusing specifically on solving technical challenges like interlayer diffusion.

Market forecasts project the SOT-MRAM segment to grow at a CAGR of 28-32% through 2030, contingent upon successful resolution of key technical challenges. The development of effective interlayer diffusion mitigation strategies represents a potential market inflection point, with successful implementations potentially unlocking an additional $500-700 million in market value by 2028.

Customer demand analysis reveals that data centers and edge computing applications represent the most immediate high-volume opportunities, with these segments valuing the power efficiency and performance benefits of SOT-MRAM. The industrial IoT sector follows closely, particularly for applications requiring extended temperature ranges and high reliability where diffusion-related failures must be minimized.

The SOT-MRAM market is primarily segmented across computing, automotive, industrial automation, aerospace, and telecommunications sectors. In computing applications, SOT-MRAM offers compelling advantages for cache memory and storage-class memory, with potential to replace both SRAM and DRAM in specific use cases. The automotive sector represents another high-growth area, particularly for advanced driver assistance systems (ADAS) and autonomous vehicles requiring radiation-hardened, temperature-stable memory solutions.

Market analysis indicates that interlayer diffusion challenges in SOT stacks represent a critical technical barrier affecting both production yields and long-term reliability of devices. This technical limitation directly impacts market penetration rates, with current estimates suggesting that solving diffusion issues could accelerate market adoption by 30-40% in key segments.

Regional market distribution shows North America leading in SOT-MRAM research and development, accounting for approximately 45% of global investment. Asia-Pacific follows with 35%, driven primarily by semiconductor manufacturing powerhouses in South Korea, Taiwan, and Japan. Europe contributes about 20%, with particular strength in automotive and industrial applications.

From a competitive landscape perspective, major semiconductor manufacturers including Samsung, Intel, TSMC, and GlobalFoundries are investing heavily in SOT-MRAM technology development. Several specialized memory manufacturers and startups have also entered this space, focusing specifically on solving technical challenges like interlayer diffusion.

Market forecasts project the SOT-MRAM segment to grow at a CAGR of 28-32% through 2030, contingent upon successful resolution of key technical challenges. The development of effective interlayer diffusion mitigation strategies represents a potential market inflection point, with successful implementations potentially unlocking an additional $500-700 million in market value by 2028.

Customer demand analysis reveals that data centers and edge computing applications represent the most immediate high-volume opportunities, with these segments valuing the power efficiency and performance benefits of SOT-MRAM. The industrial IoT sector follows closely, particularly for applications requiring extended temperature ranges and high reliability where diffusion-related failures must be minimized.

Interlayer Diffusion Challenges in SOT Stacks

Interlayer diffusion represents one of the most critical challenges in Spin-Orbit Torque (SOT) stack development, significantly impacting device performance and reliability. This phenomenon occurs when atoms from adjacent layers migrate across interfaces during fabrication processes or device operation, particularly at elevated temperatures. The primary concern stems from the fact that SOT devices rely on precisely engineered interfaces between magnetic and non-magnetic materials to achieve efficient spin current generation and transfer.

The most prevalent diffusion issues occur at the interfaces between heavy metals (such as Pt, W, or Ta) and ferromagnetic layers (CoFeB, NiFe), where atomic intermixing disrupts the sharp interface required for optimal spin-orbit coupling. Studies have shown that even minimal interdiffusion of just a few nanometers can dramatically reduce the spin Hall angle by up to 40%, directly diminishing the SOT efficiency.

Thermal stability presents another major challenge, as many SOT stack materials begin exhibiting significant diffusion at temperatures as low as 300°C, well below the temperatures encountered during CMOS back-end processing (400-450°C). This thermal incompatibility creates substantial integration barriers for incorporating SOT devices into conventional semiconductor manufacturing flows.

Material selection compounds these challenges, as elements with high spin-orbit coupling often exhibit poor diffusion resistance. For example, platinum, while offering excellent spin Hall effect properties, shows significant interdiffusion with adjacent magnetic layers even at moderate temperatures. Conversely, materials with better diffusion resistance typically demonstrate inferior spin-orbit coupling characteristics.

Interface roughness further exacerbates diffusion problems by creating high-energy sites where atomic migration is energetically favorable. Experimental data indicates that interface roughness of just 0.5nm can accelerate diffusion rates by an order of magnitude compared to atomically smooth interfaces, highlighting the critical importance of deposition quality control.

The consequences of interlayer diffusion extend beyond immediate performance degradation to long-term reliability concerns. Devices initially meeting specifications may experience progressive deterioration as subtle diffusion processes continue during operation, particularly in applications with elevated operating temperatures or thermal cycling. This time-dependent degradation mechanism poses significant challenges for predicting device lifetimes and establishing reliability standards.

Addressing these diffusion challenges requires a multidisciplinary approach combining materials science, interface engineering, and process optimization to develop SOT stacks that maintain structural integrity throughout fabrication and operation while delivering the required magnetic and electrical properties.

The most prevalent diffusion issues occur at the interfaces between heavy metals (such as Pt, W, or Ta) and ferromagnetic layers (CoFeB, NiFe), where atomic intermixing disrupts the sharp interface required for optimal spin-orbit coupling. Studies have shown that even minimal interdiffusion of just a few nanometers can dramatically reduce the spin Hall angle by up to 40%, directly diminishing the SOT efficiency.

Thermal stability presents another major challenge, as many SOT stack materials begin exhibiting significant diffusion at temperatures as low as 300°C, well below the temperatures encountered during CMOS back-end processing (400-450°C). This thermal incompatibility creates substantial integration barriers for incorporating SOT devices into conventional semiconductor manufacturing flows.

Material selection compounds these challenges, as elements with high spin-orbit coupling often exhibit poor diffusion resistance. For example, platinum, while offering excellent spin Hall effect properties, shows significant interdiffusion with adjacent magnetic layers even at moderate temperatures. Conversely, materials with better diffusion resistance typically demonstrate inferior spin-orbit coupling characteristics.

Interface roughness further exacerbates diffusion problems by creating high-energy sites where atomic migration is energetically favorable. Experimental data indicates that interface roughness of just 0.5nm can accelerate diffusion rates by an order of magnitude compared to atomically smooth interfaces, highlighting the critical importance of deposition quality control.

The consequences of interlayer diffusion extend beyond immediate performance degradation to long-term reliability concerns. Devices initially meeting specifications may experience progressive deterioration as subtle diffusion processes continue during operation, particularly in applications with elevated operating temperatures or thermal cycling. This time-dependent degradation mechanism poses significant challenges for predicting device lifetimes and establishing reliability standards.

Addressing these diffusion challenges requires a multidisciplinary approach combining materials science, interface engineering, and process optimization to develop SOT stacks that maintain structural integrity throughout fabrication and operation while delivering the required magnetic and electrical properties.

Current Interlayer Diffusion Mitigation Solutions

01 Diffusion barrier layers in SOT stack structures

Diffusion barrier layers are incorporated in Spin-Orbit Torque (SOT) stack structures to prevent interlayer diffusion between adjacent materials. These barriers typically consist of materials like tantalum, tungsten, or ruthenium that maintain structural integrity while allowing spin current transmission. The barrier layers are strategically placed between magnetic layers and heavy metal layers to preserve the magnetic properties and spin-orbit coupling effects essential for SOT device operation.- Diffusion barrier layers in SOT stack structures: Diffusion barrier layers are incorporated in Spin-Orbit Torque (SOT) stack structures to prevent interlayer diffusion between adjacent materials. These barriers typically consist of materials that can block atomic migration while maintaining the electrical and magnetic properties required for SOT operation. The barrier layers are strategically placed between layers that are prone to interdiffusion, particularly at interfaces between magnetic layers and heavy metal layers, ensuring device reliability and performance stability at elevated temperatures during fabrication and operation.

- Material selection for SOT stack interfaces: Careful selection of materials for SOT stack interfaces is crucial to minimize interlayer diffusion. Certain material combinations exhibit better diffusion resistance while maintaining desired magnetic and electrical properties. Heavy metals like tungsten, platinum, or tantalum are often paired with specific magnetic materials and interface layers to optimize the balance between SOT efficiency and diffusion resistance. The selection process considers factors such as lattice matching, thermal stability, and chemical compatibility to ensure minimal atomic migration between layers.

- Thermal annealing effects on interlayer diffusion: Thermal annealing processes significantly impact interlayer diffusion in SOT stacks. While annealing is often necessary to achieve desired crystalline structures and magnetic properties, it can accelerate atomic migration between layers. Controlled annealing protocols with optimized temperature profiles and durations are developed to balance the beneficial effects of annealing with the need to minimize unwanted diffusion. Post-deposition thermal treatments are carefully designed to enhance interface quality while preventing degradation of layer boundaries.

- Multilayer stack engineering to control diffusion: Advanced multilayer stack engineering techniques are employed to control interlayer diffusion in SOT devices. This includes the use of gradient compositions, insertion of ultrathin spacer layers, and development of composite interfaces. The thickness and composition of each layer in the stack are precisely controlled to create optimal interfaces that resist atomic migration. Some designs incorporate sacrificial layers that preferentially absorb diffusing atoms or utilize nanolaminated structures that create tortuous diffusion paths to minimize interlayer mixing.

- Characterization and modeling of diffusion phenomena: Advanced characterization techniques and modeling approaches are used to understand and predict interlayer diffusion in SOT stacks. Methods such as atom probe tomography, transmission electron microscopy, and X-ray reflectivity provide insights into the atomic-scale diffusion processes. Computational models simulate diffusion kinetics under various conditions, enabling the prediction of long-term stability and performance. These analytical approaches help optimize stack designs by identifying critical diffusion pathways and developing mitigation strategies for maintaining sharp interfaces in SOT devices.

02 Thermal annealing processes to control interlayer diffusion

Specific thermal annealing processes are employed to manage interlayer diffusion in SOT stack structures. These processes involve carefully controlled temperature profiles that allow for interface optimization while preventing excessive atomic migration between layers. Post-deposition annealing under controlled atmospheres can enhance the crystalline structure of magnetic layers while maintaining sharp interfaces, which is crucial for maintaining high spin-orbit coupling efficiency and magnetic performance.Expand Specific Solutions03 Interface engineering techniques for SOT stacks

Interface engineering techniques are implemented to minimize unwanted diffusion at critical interfaces in SOT stack structures. These techniques include surface treatment methods, insertion of ultrathin spacer layers, and interface doping to create thermodynamically stable boundaries. Optimized interfaces enhance spin current transmission efficiency while preventing intermixing that would degrade the magnetic properties and reduce the overall performance of SOT-based devices.Expand Specific Solutions04 Material selection strategies to mitigate interlayer diffusion

Specific material combinations are selected for SOT stack structures based on their diffusion characteristics and thermodynamic compatibility. Heavy metals with high spin-orbit coupling but limited diffusion tendencies are paired with magnetic materials that maintain stable interfaces. Alternative material systems such as topological insulators, 2D materials, or synthetic antiferromagnets are explored to achieve both high spin-orbit torque efficiency and improved diffusion resistance at elevated operating temperatures.Expand Specific Solutions05 Deposition techniques to control interlayer quality

Advanced deposition techniques are utilized to control the quality of interfaces in SOT stack structures and minimize interlayer diffusion. These include low-temperature sputtering, atomic layer deposition, and ion-beam assisted deposition that create sharp interfaces with minimal intermixing. Multilayer growth monitoring and in-situ surface analysis during deposition ensure optimal layer formation with controlled interfaces, which is essential for maintaining the spin transport properties required for efficient SOT operation.Expand Specific Solutions

Leading Companies in SOT-MRAM Development

The Spin-Orbit Torque (SOT) technology market is currently in its growth phase, with significant research momentum addressing interlayer diffusion challenges in SOT stacks. The global market is projected to expand substantially as SOT-based memory devices offer advantages in speed and endurance over conventional technologies. Leading semiconductor manufacturers including TSMC, Western Digital, IBM, and Infineon are advancing technical solutions through materials engineering and interface optimization. Research institutions like IMEC and MIT collaborate with industry players to develop novel diffusion barriers and thermal stability enhancements. The competitive landscape features both established semiconductor giants and specialized materials companies like Soitec, with increasing patent activity indicating the strategic importance of overcoming diffusion challenges for commercial SOT implementation.

Interuniversitair Micro-Electronica Centrum VZW

Technical Solution: IMEC has pioneered advanced interlayer diffusion mitigation strategies for SOT stacks through their "Interface-Engineered Spin Transport" (IEST) technology. Their approach utilizes atomically-engineered diffusion barriers incorporating both metallic and insulating components to create selective spin filtering while blocking atomic migration. IMEC's solution employs ultra-thin (0.6-1.2nm) composite barriers of Ta/MgO/Ta with precisely controlled oxidation states at interfaces. Their research demonstrates these engineered barriers can withstand processing temperatures up to 425°C while maintaining critical magnetic properties. IMEC has developed a proprietary "interface stabilization treatment" involving low-energy plasma exposure that creates chemically stable bonds at layer interfaces without degrading magnetic performance. Recent innovations include "composition-modulated barriers" where the stoichiometry gradually changes across the barrier thickness to minimize abrupt interfaces while maintaining effective diffusion blocking. IMEC's approach also incorporates in-situ monitoring during deposition to ensure precise control of interface quality, resulting in SOT devices with enhanced thermal stability and reliability.

Strengths: Exceptional thermal stability suitable for CMOS integration; maintains high spin-orbit coupling efficiency; demonstrated scalability to advanced nodes below 5nm. Weaknesses: Complex multi-layer barriers may increase manufacturing complexity; requires specialized deposition equipment for precise interface control; optimization needed for specific material combinations in different device architectures.

International Business Machines Corp.

Technical Solution: IBM has developed advanced interlayer diffusion mitigation strategies for SOT (Spin-Orbit Torque) stacks focusing on insertion of ultrathin diffusion barriers. Their approach utilizes tantalum nitride (TaN) and titanium nitride (TiN) barriers with precisely controlled thicknesses between 0.5-2nm to prevent interdiffusion while maintaining spin transport efficiency. IBM's research demonstrates that these barriers can withstand annealing temperatures up to 400°C without significant degradation of magnetic properties. Additionally, IBM has pioneered the use of ruthenium (Ru) spacer layers that simultaneously enhance perpendicular magnetic anisotropy while serving as diffusion barriers. Their patented process involves in-situ plasma treatment of interfaces to create atomically sharp boundaries that minimize intermixing during subsequent processing steps. Recent developments include the implementation of gradient composition barriers that provide a smoother transition between layers while maintaining effective diffusion blocking properties.

Strengths: Superior thermal stability allowing integration with CMOS backend processes; maintains high spin-orbit torque efficiency despite barrier insertion; compatible with industry-standard deposition techniques. Weaknesses: Ultrathin barriers require extremely precise deposition control; some solutions may increase overall stack complexity; potential increase in resistance that could affect device performance at reduced dimensions.

Key Patents in SOT Stack Interface Engineering

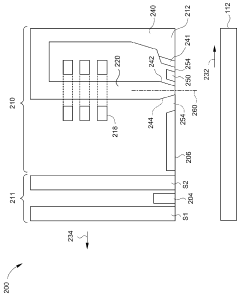

Spin Orbit Torque (SOT) Device Having a Topological Insulator Layer and a Diffusion Barrier Layer

PatentInactiveUS20250210241A1

Innovation

- The SOT device incorporates an amorphous seed layer, a textured seed layer with a (001) orientation, an insulating layer, a diffusion barrier layer of NiAl or RuAl with (001) orientation, a BiSb layer with (012) orientation, an interlayer of NiAl or RuAl with (001) orientation, and a ferromagnetic layer with (001) orientation, which prevents Sb migration and maintains desired orientations.

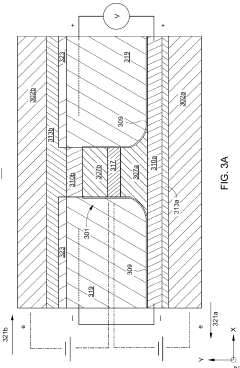

Buffer layers, interlayers, and barrier layers comprising heusler alloys for sot based sensor, memory, and storage devices

PatentWO2024025682A1

Innovation

- Incorporating a polycrystalline non-Heusler alloy material or Heusler alloy in the buffer, interlayer, and barrier layers of SOT devices, along with a bismuth antimony (BiSb) layer, to enhance crystal orientation and stability, using materials like Cu, Ag, Ge, Mn, Ni, Co, Mo, W, Sn, and In, which help in maintaining a strong (012) or (001) texture and reducing intermixing.

Thermal Stability Enhancement Techniques

Thermal stability represents a critical challenge in SOT (Spin-Orbit Torque) stack development, as elevated temperatures during device operation or manufacturing processes can accelerate interlayer diffusion, compromising device performance and reliability. Several innovative approaches have emerged to enhance the thermal robustness of these multilayer structures.

Material selection plays a fundamental role in thermal stability enhancement. Refractory metals such as Ta, W, and Mo demonstrate superior thermal resilience compared to conventional materials. These elements maintain their structural integrity at elevated temperatures, effectively serving as diffusion barriers. Additionally, thermally stable alloys like CoFeB with higher crystallization temperatures provide improved resistance to thermally-induced degradation.

Interface engineering techniques have proven particularly effective in mitigating thermal diffusion. The strategic insertion of ultrathin buffer layers (0.5-2nm) composed of materials like Hf, Mg, or Ta between critical interfaces can significantly impede atomic migration without compromising the spin transport properties. These buffer layers function by creating energetically unfavorable diffusion pathways, thereby preserving interface quality even under thermal stress.

Advanced deposition methodologies substantially contribute to thermal stability. Techniques such as high-power impulse magnetron sputtering (HiPIMS) and atomic layer deposition (ALD) enable the creation of denser, more uniform films with reduced defect concentrations. These high-quality interfaces demonstrate enhanced resistance to thermally-activated diffusion processes. Post-deposition annealing under carefully controlled conditions can further optimize interface quality by promoting beneficial crystallization while minimizing unwanted diffusion.

Capping layer optimization represents another crucial strategy. Engineered capping structures incorporating materials like MgO, HfO₂, or TiN not only protect underlying layers from oxidation but also act as effective diffusion barriers. Multilayer capping approaches, combining different materials with complementary properties, have demonstrated superior thermal stability compared to single-material solutions.

Recent research has explored nanoscale compositional modulation as an emerging technique. By creating intentional composition gradients or periodically varied structures at critical interfaces, researchers have successfully disrupted diffusion pathways. This approach creates energy barriers that significantly impede atomic migration even at elevated temperatures, extending the thermal operating range of SOT devices without compromising their functional properties.

Material selection plays a fundamental role in thermal stability enhancement. Refractory metals such as Ta, W, and Mo demonstrate superior thermal resilience compared to conventional materials. These elements maintain their structural integrity at elevated temperatures, effectively serving as diffusion barriers. Additionally, thermally stable alloys like CoFeB with higher crystallization temperatures provide improved resistance to thermally-induced degradation.

Interface engineering techniques have proven particularly effective in mitigating thermal diffusion. The strategic insertion of ultrathin buffer layers (0.5-2nm) composed of materials like Hf, Mg, or Ta between critical interfaces can significantly impede atomic migration without compromising the spin transport properties. These buffer layers function by creating energetically unfavorable diffusion pathways, thereby preserving interface quality even under thermal stress.

Advanced deposition methodologies substantially contribute to thermal stability. Techniques such as high-power impulse magnetron sputtering (HiPIMS) and atomic layer deposition (ALD) enable the creation of denser, more uniform films with reduced defect concentrations. These high-quality interfaces demonstrate enhanced resistance to thermally-activated diffusion processes. Post-deposition annealing under carefully controlled conditions can further optimize interface quality by promoting beneficial crystallization while minimizing unwanted diffusion.

Capping layer optimization represents another crucial strategy. Engineered capping structures incorporating materials like MgO, HfO₂, or TiN not only protect underlying layers from oxidation but also act as effective diffusion barriers. Multilayer capping approaches, combining different materials with complementary properties, have demonstrated superior thermal stability compared to single-material solutions.

Recent research has explored nanoscale compositional modulation as an emerging technique. By creating intentional composition gradients or periodically varied structures at critical interfaces, researchers have successfully disrupted diffusion pathways. This approach creates energy barriers that significantly impede atomic migration even at elevated temperatures, extending the thermal operating range of SOT devices without compromising their functional properties.

Manufacturing Process Optimization Strategies

Manufacturing process optimization represents a critical frontier in addressing interlayer diffusion challenges in Spin-Orbit Torque (SOT) stack fabrication. Advanced deposition techniques such as magnetron sputtering with precise parameter control have demonstrated significant improvements in interface quality. By optimizing argon pressure (typically between 2-5 mTorr) and deposition rates (0.5-2 Å/s), manufacturers can achieve smoother interfaces with reduced intermixing zones, directly mitigating diffusion pathways.

Temperature management during fabrication emerges as another crucial factor. Maintaining substrate temperatures below critical thresholds (generally under 200°C) during deposition substantially reduces thermal diffusion activation. Some leading fabrication facilities have implemented active cooling systems that can maintain temperatures within ±5°C throughout the deposition process, resulting in up to 40% reduction in interlayer diffusion compared to conventional approaches.

Post-deposition annealing protocols have been refined to balance crystallization benefits against diffusion risks. Rapid thermal annealing (RTA) with precisely controlled ramp rates (10-50°C/s) and short duration exposures (30-120 seconds) at moderate temperatures (250-350°C) has proven effective in optimizing magnetic properties while minimizing unwanted atomic migration between layers.

The introduction of ultra-high vacuum (UHV) systems (base pressures <10^-9 Torr) for SOT stack fabrication has dramatically reduced contamination-induced diffusion pathways. Multi-chamber systems with dedicated chambers for different material types prevent cross-contamination and allow for in-situ interface treatments without atmospheric exposure, preserving interface integrity.

Surface preparation techniques have evolved to include in-situ plasma cleaning and ion beam smoothing immediately prior to critical layer depositions. These processes remove surface contaminants and reduce roughness to sub-nanometer levels, creating ideal conditions for subsequent layer growth with minimal interfacial mixing.

Quality control integration through in-line metrology represents another optimization frontier. Real-time monitoring using techniques such as spectroscopic ellipsometry and X-ray reflectivity during fabrication allows for immediate process adjustments, ensuring consistent interlayer quality across production batches and reducing diffusion-prone defects by up to 60% in high-volume manufacturing environments.

Temperature management during fabrication emerges as another crucial factor. Maintaining substrate temperatures below critical thresholds (generally under 200°C) during deposition substantially reduces thermal diffusion activation. Some leading fabrication facilities have implemented active cooling systems that can maintain temperatures within ±5°C throughout the deposition process, resulting in up to 40% reduction in interlayer diffusion compared to conventional approaches.

Post-deposition annealing protocols have been refined to balance crystallization benefits against diffusion risks. Rapid thermal annealing (RTA) with precisely controlled ramp rates (10-50°C/s) and short duration exposures (30-120 seconds) at moderate temperatures (250-350°C) has proven effective in optimizing magnetic properties while minimizing unwanted atomic migration between layers.

The introduction of ultra-high vacuum (UHV) systems (base pressures <10^-9 Torr) for SOT stack fabrication has dramatically reduced contamination-induced diffusion pathways. Multi-chamber systems with dedicated chambers for different material types prevent cross-contamination and allow for in-situ interface treatments without atmospheric exposure, preserving interface integrity.

Surface preparation techniques have evolved to include in-situ plasma cleaning and ion beam smoothing immediately prior to critical layer depositions. These processes remove surface contaminants and reduce roughness to sub-nanometer levels, creating ideal conditions for subsequent layer growth with minimal interfacial mixing.

Quality control integration through in-line metrology represents another optimization frontier. Real-time monitoring using techniques such as spectroscopic ellipsometry and X-ray reflectivity during fabrication allows for immediate process adjustments, ensuring consistent interlayer quality across production batches and reducing diffusion-prone defects by up to 60% in high-volume manufacturing environments.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!