Testing Standards For SOT MRAM Performance Characterization

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

SOT MRAM Technology Background and Objectives

Spin-Orbit Torque Magnetoresistive Random Access Memory (SOT MRAM) represents a significant advancement in non-volatile memory technology, emerging as a promising solution to address the limitations of conventional memory architectures. The evolution of this technology can be traced back to the discovery of spin-transfer torque effects in magnetic materials in the early 2000s, which laid the groundwork for various spintronic memory technologies including STT-MRAM (Spin-Transfer Torque MRAM).

SOT MRAM specifically leverages the spin-orbit coupling phenomenon, where an electric current generates a spin polarization perpendicular to both the current direction and the interface normal. This mechanism enables more efficient magnetization switching compared to its STT-MRAM predecessor, offering advantages in terms of endurance, power consumption, and operational speed.

The development trajectory of SOT MRAM has accelerated significantly since 2015, with research institutions and semiconductor companies intensifying their efforts to overcome technical barriers. The technology has progressed from theoretical concepts to experimental demonstrations, and now stands at the threshold of commercial viability, though standardized testing protocols remain underdeveloped.

The primary technical objective in SOT MRAM development is to establish comprehensive and standardized testing methodologies that accurately characterize device performance across various operational parameters. These include write/read speeds, endurance cycles, data retention capabilities, and power efficiency metrics. Standardization is crucial for enabling meaningful comparisons between different SOT MRAM implementations and facilitating technology maturation.

Additionally, testing standards must address the unique challenges posed by SOT MRAM's operating principles, such as the impact of thermal effects on switching reliability, the influence of material interfaces on spin current efficiency, and the scalability of performance metrics across different device geometries. These standards should also incorporate reliability testing under varied environmental conditions to assess real-world performance.

The ultimate goal of SOT MRAM testing standardization extends beyond mere performance verification to enabling systematic technology optimization. By establishing clear benchmarks and measurement protocols, researchers and manufacturers can identify critical performance bottlenecks, accelerate development cycles, and facilitate the technology's integration into mainstream computing architectures.

As SOT MRAM continues to mature, these testing standards will play a pivotal role in determining its competitive positioning against other emerging memory technologies such as RRAM, PCM, and FeRAM, particularly in applications demanding high endurance, low latency, and energy efficiency.

SOT MRAM specifically leverages the spin-orbit coupling phenomenon, where an electric current generates a spin polarization perpendicular to both the current direction and the interface normal. This mechanism enables more efficient magnetization switching compared to its STT-MRAM predecessor, offering advantages in terms of endurance, power consumption, and operational speed.

The development trajectory of SOT MRAM has accelerated significantly since 2015, with research institutions and semiconductor companies intensifying their efforts to overcome technical barriers. The technology has progressed from theoretical concepts to experimental demonstrations, and now stands at the threshold of commercial viability, though standardized testing protocols remain underdeveloped.

The primary technical objective in SOT MRAM development is to establish comprehensive and standardized testing methodologies that accurately characterize device performance across various operational parameters. These include write/read speeds, endurance cycles, data retention capabilities, and power efficiency metrics. Standardization is crucial for enabling meaningful comparisons between different SOT MRAM implementations and facilitating technology maturation.

Additionally, testing standards must address the unique challenges posed by SOT MRAM's operating principles, such as the impact of thermal effects on switching reliability, the influence of material interfaces on spin current efficiency, and the scalability of performance metrics across different device geometries. These standards should also incorporate reliability testing under varied environmental conditions to assess real-world performance.

The ultimate goal of SOT MRAM testing standardization extends beyond mere performance verification to enabling systematic technology optimization. By establishing clear benchmarks and measurement protocols, researchers and manufacturers can identify critical performance bottlenecks, accelerate development cycles, and facilitate the technology's integration into mainstream computing architectures.

As SOT MRAM continues to mature, these testing standards will play a pivotal role in determining its competitive positioning against other emerging memory technologies such as RRAM, PCM, and FeRAM, particularly in applications demanding high endurance, low latency, and energy efficiency.

Market Demand Analysis for SOT MRAM Solutions

The global market for Spin-Orbit Torque Magnetic Random Access Memory (SOT MRAM) solutions is experiencing significant growth driven by increasing demand for advanced non-volatile memory technologies. Current market analysis indicates that the memory semiconductor sector is actively seeking alternatives to conventional technologies that can address limitations in power consumption, endurance, and data retention. SOT MRAM has emerged as a promising candidate due to its potential to combine the speed of SRAM with the non-volatility of flash memory, while offering superior endurance compared to other emerging memory technologies.

Industry research suggests that data centers and enterprise storage systems represent the largest immediate market opportunity for SOT MRAM solutions. These environments require high-performance, energy-efficient memory systems capable of handling intensive read/write operations while maintaining data integrity. The exponential growth in data processing demands, coupled with increasing focus on energy efficiency in data centers, creates a compelling value proposition for SOT MRAM technology.

The automotive and industrial IoT sectors also demonstrate substantial growth potential for SOT MRAM applications. Advanced driver-assistance systems (ADAS) and autonomous vehicles require memory solutions that can withstand extreme operating conditions while delivering reliable, high-speed performance. Similarly, industrial automation systems benefit from the radiation hardness and temperature stability that SOT MRAM potentially offers.

Market forecasts indicate that the overall MRAM market is expected to grow at a compound annual growth rate exceeding 35% through 2026, with SOT MRAM gradually capturing market share from older MRAM technologies like STT-MRAM. This growth trajectory is supported by increasing investments from major semiconductor manufacturers who are expanding their MRAM production capabilities.

A critical factor driving market demand is the need for standardized testing methodologies for SOT MRAM performance characterization. Current stakeholders report significant challenges in comparing solutions across vendors due to inconsistent testing protocols. This has created a market gap for universally accepted testing standards that can accurately measure key performance parameters such as write energy, read/write speeds, endurance cycles, and data retention across varying environmental conditions.

Consumer electronics manufacturers have also expressed growing interest in SOT MRAM for next-generation mobile devices, where battery life and performance are paramount concerns. The ability to replace multiple memory types with a single SOT MRAM solution offers potential for simplified device architecture and reduced power consumption, addressing key consumer demands for longer-lasting, faster-performing devices.

Industry research suggests that data centers and enterprise storage systems represent the largest immediate market opportunity for SOT MRAM solutions. These environments require high-performance, energy-efficient memory systems capable of handling intensive read/write operations while maintaining data integrity. The exponential growth in data processing demands, coupled with increasing focus on energy efficiency in data centers, creates a compelling value proposition for SOT MRAM technology.

The automotive and industrial IoT sectors also demonstrate substantial growth potential for SOT MRAM applications. Advanced driver-assistance systems (ADAS) and autonomous vehicles require memory solutions that can withstand extreme operating conditions while delivering reliable, high-speed performance. Similarly, industrial automation systems benefit from the radiation hardness and temperature stability that SOT MRAM potentially offers.

Market forecasts indicate that the overall MRAM market is expected to grow at a compound annual growth rate exceeding 35% through 2026, with SOT MRAM gradually capturing market share from older MRAM technologies like STT-MRAM. This growth trajectory is supported by increasing investments from major semiconductor manufacturers who are expanding their MRAM production capabilities.

A critical factor driving market demand is the need for standardized testing methodologies for SOT MRAM performance characterization. Current stakeholders report significant challenges in comparing solutions across vendors due to inconsistent testing protocols. This has created a market gap for universally accepted testing standards that can accurately measure key performance parameters such as write energy, read/write speeds, endurance cycles, and data retention across varying environmental conditions.

Consumer electronics manufacturers have also expressed growing interest in SOT MRAM for next-generation mobile devices, where battery life and performance are paramount concerns. The ability to replace multiple memory types with a single SOT MRAM solution offers potential for simplified device architecture and reduced power consumption, addressing key consumer demands for longer-lasting, faster-performing devices.

Current Testing Challenges and Limitations

Despite significant advancements in SOT MRAM technology, the field faces substantial challenges in standardized testing methodologies. Current testing protocols exhibit considerable inconsistency across research institutions and manufacturers, creating difficulties in comparing performance metrics between different SOT MRAM devices. This lack of standardization impedes meaningful benchmarking and slows industry-wide adoption of this promising technology.

One critical limitation is the absence of universally accepted measurement techniques for key SOT MRAM parameters. Switching current density (Jc), one of the most important performance indicators, is often measured using different methods and under varying conditions, leading to discrepancies in reported values. Similarly, thermal stability factor (Δ) measurements show significant variations depending on the specific testing approach employed, complicating reliability assessments.

The characterization of write error rates presents another significant challenge. Current testing methodologies struggle to accurately capture the stochastic nature of SOT-induced switching, particularly at high speeds and under varying temperature conditions. This limitation becomes especially problematic when evaluating devices intended for applications requiring exceptional reliability, such as automotive or aerospace systems.

Endurance testing represents a particularly problematic area. Accelerated testing methods often fail to accurately predict long-term device performance, while comprehensive lifetime testing is prohibitively time-consuming. The industry lacks standardized protocols for stress testing that can reliably correlate to real-world performance across diverse operating environments.

Temperature dependency characterization remains inadequately addressed in current testing frameworks. SOT MRAM performance metrics can vary significantly across temperature ranges, yet standardized methods for characterizing this behavior across the full operational spectrum (-40°C to 125°C for industrial applications) are not well established. This gap creates uncertainty in predicting device performance in real-world applications.

Testing equipment limitations further compound these challenges. High-precision measurements of switching dynamics require specialized instrumentation that is not uniformly available across the industry. The lack of standardized calibration procedures for such equipment introduces additional variables that complicate cross-comparison of results between different research groups and manufacturers.

Finally, there is insufficient consensus on reliability qualification standards specific to SOT MRAM. While established memory technologies have well-defined qualification procedures (JEDEC standards for DRAM, NAND, etc.), SOT MRAM lacks equivalent industry-wide accepted testing protocols. This absence creates uncertainty for potential adopters regarding long-term reliability and performance stability, ultimately slowing market penetration despite the technology's promising characteristics.

One critical limitation is the absence of universally accepted measurement techniques for key SOT MRAM parameters. Switching current density (Jc), one of the most important performance indicators, is often measured using different methods and under varying conditions, leading to discrepancies in reported values. Similarly, thermal stability factor (Δ) measurements show significant variations depending on the specific testing approach employed, complicating reliability assessments.

The characterization of write error rates presents another significant challenge. Current testing methodologies struggle to accurately capture the stochastic nature of SOT-induced switching, particularly at high speeds and under varying temperature conditions. This limitation becomes especially problematic when evaluating devices intended for applications requiring exceptional reliability, such as automotive or aerospace systems.

Endurance testing represents a particularly problematic area. Accelerated testing methods often fail to accurately predict long-term device performance, while comprehensive lifetime testing is prohibitively time-consuming. The industry lacks standardized protocols for stress testing that can reliably correlate to real-world performance across diverse operating environments.

Temperature dependency characterization remains inadequately addressed in current testing frameworks. SOT MRAM performance metrics can vary significantly across temperature ranges, yet standardized methods for characterizing this behavior across the full operational spectrum (-40°C to 125°C for industrial applications) are not well established. This gap creates uncertainty in predicting device performance in real-world applications.

Testing equipment limitations further compound these challenges. High-precision measurements of switching dynamics require specialized instrumentation that is not uniformly available across the industry. The lack of standardized calibration procedures for such equipment introduces additional variables that complicate cross-comparison of results between different research groups and manufacturers.

Finally, there is insufficient consensus on reliability qualification standards specific to SOT MRAM. While established memory technologies have well-defined qualification procedures (JEDEC standards for DRAM, NAND, etc.), SOT MRAM lacks equivalent industry-wide accepted testing protocols. This absence creates uncertainty for potential adopters regarding long-term reliability and performance stability, ultimately slowing market penetration despite the technology's promising characteristics.

Current Testing Methodologies and Standards

01 SOT-MRAM device structure optimization

Spin-Orbit Torque Magnetic Random Access Memory (SOT-MRAM) performance can be enhanced through structural optimizations of the device. These optimizations include modifications to the magnetic tunnel junction (MTJ) stack design, integration of novel materials with high spin-orbit coupling, and engineering of the interface between layers to improve spin current efficiency. Such structural improvements lead to better switching characteristics, reduced power consumption, and increased reliability of SOT-MRAM devices.- SOT-MRAM device structure optimization: Spin-Orbit Torque Magnetic Random Access Memory (SOT-MRAM) performance can be enhanced through structural optimizations of the device. These optimizations include improved magnetic tunnel junction (MTJ) designs, novel electrode configurations, and advanced material interfaces that facilitate more efficient spin current generation and transfer. By engineering the physical structure of SOT-MRAM devices, manufacturers can achieve higher switching efficiency, reduced power consumption, and improved thermal stability.

- Material selection for enhanced SOT efficiency: The choice of materials significantly impacts SOT-MRAM performance. Heavy metals with strong spin-orbit coupling (such as Pt, W, or Ta), optimized ferromagnetic layers, and carefully engineered interfaces can dramatically improve spin current generation and magnetic switching efficiency. Novel material combinations and multilayer structures are being developed to enhance spin-orbit torque effects while maintaining compatibility with semiconductor manufacturing processes, resulting in devices with lower switching currents and higher reliability.

- Switching dynamics and speed optimization: Improving the switching dynamics of SOT-MRAM is crucial for enhancing its performance as a high-speed memory solution. Research focuses on reducing switching latency through optimized current pulse shapes, magnetic field assistance techniques, and novel switching mechanisms. Advanced designs aim to achieve sub-nanosecond switching times while maintaining reliability and endurance. Understanding and controlling the magnetization dynamics during switching operations enables the development of faster and more energy-efficient SOT-MRAM devices.

- Integration with CMOS technology: Successful integration of SOT-MRAM with conventional CMOS technology is essential for its commercial viability. This includes developing compatible fabrication processes, addressing thermal budget constraints, and designing efficient peripheral circuits for read/write operations. Advanced integration schemes focus on reducing cell size, improving yield, and ensuring reliable operation across varying environmental conditions. Optimized CMOS-MRAM integration enables the creation of hybrid memory systems that leverage the advantages of both technologies.

- Reliability and endurance enhancement: Improving the reliability and endurance of SOT-MRAM devices is critical for their adoption in various applications. This involves addressing issues such as read disturbance, write error rates, and degradation mechanisms over time. Enhanced error correction techniques, optimized read/write circuits, and robust device designs contribute to improved data retention and extended device lifetime. Research focuses on understanding failure mechanisms at the nanoscale and developing solutions that ensure consistent performance over billions of write cycles and under various operating conditions.

02 Switching efficiency enhancement techniques

Various techniques can be employed to enhance the switching efficiency of SOT-MRAM, which directly impacts its performance. These include optimizing the spin Hall angle of materials, implementing dual spin-orbit torque schemes, utilizing field-free switching mechanisms, and engineering the shape anisotropy of the free layer. Enhanced switching efficiency results in faster operation speeds, lower critical current requirements, and improved energy efficiency of SOT-MRAM devices.Expand Specific Solutions03 Thermal stability and reliability improvements

Thermal stability and reliability are critical factors affecting SOT-MRAM performance. Approaches to improve these aspects include developing thermally robust magnetic materials, implementing temperature compensation layers, optimizing the thickness and composition of the free layer, and designing heat dissipation structures. These improvements help maintain data retention capabilities at elevated temperatures and extend the operational lifetime of SOT-MRAM devices.Expand Specific Solutions04 Integration with CMOS technology

Successful integration of SOT-MRAM with CMOS technology is essential for its commercial viability and performance in real-world applications. This involves developing compatible fabrication processes, designing efficient peripheral circuits for read/write operations, optimizing cell architecture for high density, and implementing error correction schemes. Effective CMOS integration enables SOT-MRAM to achieve competitive performance metrics while maintaining manufacturability at scale.Expand Specific Solutions05 Advanced materials for SOT-MRAM

The development and implementation of advanced materials significantly impact SOT-MRAM performance. These materials include heavy metals with enhanced spin Hall effect, synthetic antiferromagnets for improved stability, novel tunnel barrier materials for higher magnetoresistance ratio, and engineered seed layers for better crystallinity. The use of these advanced materials leads to improved switching efficiency, reduced power consumption, enhanced thermal stability, and overall better performance of SOT-MRAM devices.Expand Specific Solutions

Key Industry Players in SOT MRAM Development

The SOT MRAM testing standards landscape is currently in an emerging growth phase, with the market expected to expand significantly as this technology matures. The global competition is characterized by established semiconductor giants like IBM, Samsung, and TSMC leading fundamental research, while specialized memory manufacturers such as Western Digital and ChangXin Memory Technologies focus on commercialization aspects. Technical maturity varies across testing domains, with IBM demonstrating advanced characterization methodologies, TSMC refining manufacturing process validation, and Samsung developing integrated testing frameworks. Academic institutions including KAIST and Fudan University contribute significantly to standardization efforts, while equipment providers like Applied Materials develop specialized testing tools. The ecosystem reflects a collaborative yet competitive environment working toward unified performance metrics and reliability standards.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive testing standards for SOT MRAM performance characterization focusing on reliability and endurance metrics. Their approach includes specialized test equipment for measuring switching current density, thermal stability, and read/write error rates. IBM's testing methodology incorporates both static and dynamic measurements to evaluate SOT MRAM devices under various operating conditions. They have established standardized procedures for characterizing write error rate (WER) as a function of pulse width and amplitude, and developed statistical models to predict device performance and lifetime. IBM's testing infrastructure includes custom-designed probe stations capable of applying precise magnetic fields while simultaneously measuring electrical characteristics at different temperatures, allowing for thorough evaluation of SOT MRAM's temperature dependence and stability.

Strengths: IBM's testing standards benefit from their extensive experience in memory technologies and integration with CMOS processes. Their comprehensive approach addresses both fundamental physics and practical implementation challenges. Weaknesses: Their testing methodologies may be optimized for their specific device architectures and may not be universally applicable to all SOT MRAM implementations.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed sophisticated testing standards for SOT MRAM performance characterization focused on process integration and yield optimization. Their methodology includes specialized test structures embedded within production wafers to monitor key performance indicators throughout the manufacturing process. TSMC's approach incorporates high-precision electrical measurement techniques for characterizing switching current distributions across wafers and lots, enabling statistical process control. They have established standardized test sequences for evaluating read/write performance under various operating conditions, including temperature cycling and voltage variations. TSMC's testing infrastructure includes automated systems capable of performing both DC and high-speed pulse measurements to comprehensively assess SOT MRAM device characteristics. Their testing standards also address reliability aspects through accelerated stress testing protocols designed to identify potential failure mechanisms and establish appropriate design margins.

Strengths: TSMC's testing standards excel in process integration aspects and statistical analysis capabilities, leveraging their extensive manufacturing expertise. Their approach effectively identifies process-induced variations that impact device performance. Weaknesses: Their testing methodology may be more focused on process control than fundamental device physics exploration, potentially limiting insights into novel optimization approaches.

Critical Performance Parameters and Measurement Techniques

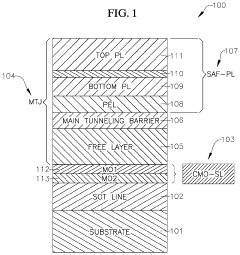

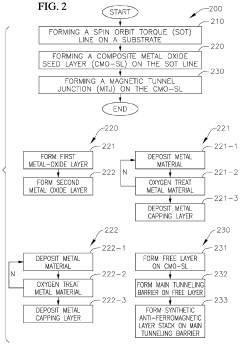

Spin-orbit torque magnetic random-access memory (sot-MRAM) device

PatentPendingUS20240023458A1

Innovation

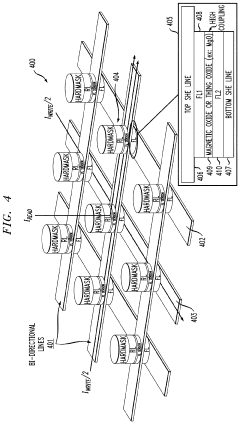

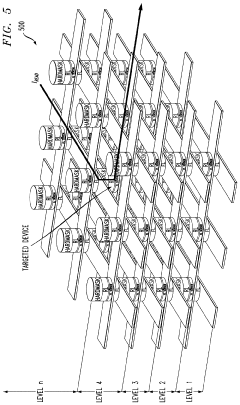

- The SOT-MRAM device incorporates a spin orbit torque line and a composite metal oxide seed layer beneath a magnetic tunnel junction, enabling efficient transverse spin-current transmission and interface perpendicular magnetic anisotropy for fast switching and data retention, with separate read/write paths.

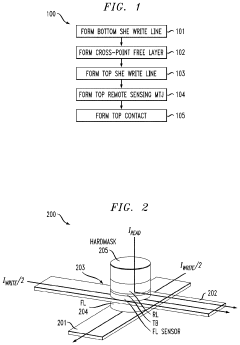

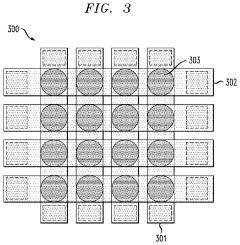

Spin orbit-torque magnetic random-access memory (sot-MRAM) with cross-point spin hall effect (SHE) write lines and remote sensing read magnetic tunnel-junction (MTJ)

PatentActiveUS20230086181A1

Innovation

- A cross-point SOT-MRAM cell design is implemented, featuring a first and second Spin Hall Effect (SHE) write line that are non-colinear, a cross-point free layer with dielectric isolation, and a remote sensing Magnetic Tunnel Junction (MTJ) to enable independent write and read operations without the need for STT-assisted writing, allowing for true cross-point architecture and improved integration density.

Reliability and Endurance Validation Frameworks

Reliability and endurance validation frameworks for SOT MRAM represent critical infrastructure for ensuring device performance over extended operational lifetimes. These frameworks must systematically address the unique challenges posed by spin-orbit torque technology while maintaining compatibility with established semiconductor testing methodologies. Current validation approaches typically incorporate multi-level testing regimes beginning with accelerated stress testing under elevated temperatures (typically 85-125°C) and voltages exceeding normal operational parameters by 10-30%.

Statistical sampling methodologies have emerged as essential components of these frameworks, with leading manufacturers implementing Weibull distribution analysis to predict failure rates and establish meaningful metrics for device lifetime estimation. The industry has gradually converged on standardized endurance testing protocols requiring a minimum of 10^12 write cycles for enterprise applications and 10^15 cycles for specialized high-reliability scenarios, with bit error rate measurements conducted at logarithmic intervals throughout the cycling process.

Time-dependent dielectric breakdown (TDDB) testing has been adapted specifically for SOT MRAM structures, focusing on the integrity of the tunnel barrier and the stability of the interface between the SOT channel and magnetic layers. These tests typically employ constant voltage stress methods with periodic interruptions for parameter verification, allowing for the construction of failure distribution models that inform reliability projections.

Data retention validation represents another crucial framework component, with current standards requiring demonstration of 10-year data retention at 85°C through accelerated testing methodologies. The Arrhenius model serves as the primary mathematical framework for extrapolating high-temperature test results to normal operating conditions, though recent research suggests modifications may be necessary to account for SOT-specific failure mechanisms.

Radiation hardness testing has gained prominence in validation frameworks, particularly for applications in aerospace and defense sectors. These tests evaluate single-event upset (SEU) susceptibility through heavy ion bombardment at varying linear energy transfer (LET) levels, with SOT MRAM demonstrating inherent advantages over conventional memory technologies due to its resistance to radiation-induced state changes.

Emerging validation approaches increasingly incorporate in-situ monitoring techniques that allow for real-time observation of device parameters during stress testing, enabling more nuanced understanding of degradation mechanisms. Machine learning algorithms have begun to enhance these frameworks by identifying subtle precursors to failure and optimizing test conditions based on accumulated data from previous validation cycles.

Statistical sampling methodologies have emerged as essential components of these frameworks, with leading manufacturers implementing Weibull distribution analysis to predict failure rates and establish meaningful metrics for device lifetime estimation. The industry has gradually converged on standardized endurance testing protocols requiring a minimum of 10^12 write cycles for enterprise applications and 10^15 cycles for specialized high-reliability scenarios, with bit error rate measurements conducted at logarithmic intervals throughout the cycling process.

Time-dependent dielectric breakdown (TDDB) testing has been adapted specifically for SOT MRAM structures, focusing on the integrity of the tunnel barrier and the stability of the interface between the SOT channel and magnetic layers. These tests typically employ constant voltage stress methods with periodic interruptions for parameter verification, allowing for the construction of failure distribution models that inform reliability projections.

Data retention validation represents another crucial framework component, with current standards requiring demonstration of 10-year data retention at 85°C through accelerated testing methodologies. The Arrhenius model serves as the primary mathematical framework for extrapolating high-temperature test results to normal operating conditions, though recent research suggests modifications may be necessary to account for SOT-specific failure mechanisms.

Radiation hardness testing has gained prominence in validation frameworks, particularly for applications in aerospace and defense sectors. These tests evaluate single-event upset (SEU) susceptibility through heavy ion bombardment at varying linear energy transfer (LET) levels, with SOT MRAM demonstrating inherent advantages over conventional memory technologies due to its resistance to radiation-induced state changes.

Emerging validation approaches increasingly incorporate in-situ monitoring techniques that allow for real-time observation of device parameters during stress testing, enabling more nuanced understanding of degradation mechanisms. Machine learning algorithms have begun to enhance these frameworks by identifying subtle precursors to failure and optimizing test conditions based on accumulated data from previous validation cycles.

Industry Standardization Efforts and Compliance Requirements

The standardization landscape for SOT MRAM testing remains in its developmental stages, with several industry bodies working to establish comprehensive frameworks. The Joint Electron Device Engineering Council (JEDEC) has taken a leading role by forming specialized task forces focused on emerging memory technologies, including SOT MRAM. Their JC-42.4 Committee on MRAM Standards has begun drafting preliminary testing protocols that address unique SOT MRAM characteristics such as switching current thresholds, thermal stability factors, and endurance parameters.

IEEE has contributed significantly through its P1765 Working Group, which is developing standards specifically for spin-based memory testing methodologies. This initiative aims to create uniform measurement techniques for parameters like spin-orbit torque efficiency, domain wall velocity, and magnetization switching dynamics - critical metrics for SOT MRAM performance evaluation.

Semiconductor Equipment and Materials International (SEMI) has established the Magnetoresistive Random Access Memory Standards Committee, which collaborates with device manufacturers to define standardized testing equipment specifications and measurement procedures. Their recent M108 guideline provides recommendations for SOT MRAM characterization equipment calibration.

Compliance requirements for SOT MRAM testing are increasingly stringent as the technology approaches commercial deployment. Manufacturers must demonstrate adherence to reliability standards including JESD47 (Stress-Test-Driven Qualification of Integrated Circuits) and JESD22 (Reliability Test Methods), adapted specifically for SOT MRAM characteristics. These standards mandate specific testing conditions for parameters such as data retention (typically 10 years at operating temperature), endurance (minimum 10^12 cycles), and read/write speed verification.

International compliance frameworks are emerging through collaborative efforts between the International Electrotechnical Commission (IEC) and regional standardization bodies. The IEC Technical Committee 47 has initiated work on SOT MRAM-specific testing requirements that harmonize approaches across different regions, facilitating global market access for SOT MRAM products.

Industry consortia like MRAM Developers Forum and the SOT Alliance have established voluntary certification programs that verify compliance with emerging standards. These certification processes typically involve third-party validation of test results against benchmark performance metrics, providing market differentiation for compliant products while accelerating standardization adoption throughout the supply chain.

IEEE has contributed significantly through its P1765 Working Group, which is developing standards specifically for spin-based memory testing methodologies. This initiative aims to create uniform measurement techniques for parameters like spin-orbit torque efficiency, domain wall velocity, and magnetization switching dynamics - critical metrics for SOT MRAM performance evaluation.

Semiconductor Equipment and Materials International (SEMI) has established the Magnetoresistive Random Access Memory Standards Committee, which collaborates with device manufacturers to define standardized testing equipment specifications and measurement procedures. Their recent M108 guideline provides recommendations for SOT MRAM characterization equipment calibration.

Compliance requirements for SOT MRAM testing are increasingly stringent as the technology approaches commercial deployment. Manufacturers must demonstrate adherence to reliability standards including JESD47 (Stress-Test-Driven Qualification of Integrated Circuits) and JESD22 (Reliability Test Methods), adapted specifically for SOT MRAM characteristics. These standards mandate specific testing conditions for parameters such as data retention (typically 10 years at operating temperature), endurance (minimum 10^12 cycles), and read/write speed verification.

International compliance frameworks are emerging through collaborative efforts between the International Electrotechnical Commission (IEC) and regional standardization bodies. The IEC Technical Committee 47 has initiated work on SOT MRAM-specific testing requirements that harmonize approaches across different regions, facilitating global market access for SOT MRAM products.

Industry consortia like MRAM Developers Forum and the SOT Alliance have established voluntary certification programs that verify compliance with emerging standards. These certification processes typically involve third-party validation of test results against benchmark performance metrics, providing market differentiation for compliant products while accelerating standardization adoption throughout the supply chain.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!