Reliability Stress Tests For Back End CMOS Compatible SOT Films

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SOT Film Technology Background and Objectives

Spin-Orbit Torque (SOT) technology has emerged as a promising candidate for next-generation memory and logic devices, offering advantages in energy efficiency, speed, and endurance compared to conventional CMOS technologies. The evolution of SOT films began in the early 2000s with the discovery of spin Hall effect and has accelerated significantly over the past decade with advancements in material science and fabrication techniques. This technology represents a convergence of spintronics and conventional semiconductor processing, potentially enabling novel computing architectures beyond traditional von Neumann paradigms.

The fundamental principle behind SOT technology relies on the conversion of charge current to spin current through spin-orbit coupling effects in heavy metals or topological insulators. These materials, when interfaced with ferromagnetic layers, can efficiently manipulate magnetic states without requiring large current densities, thus addressing power consumption challenges in modern computing systems. Recent developments have focused on enhancing the spin-orbit coupling efficiency and thermal stability of these multilayer film structures.

Back-end CMOS compatible SOT films represent a critical advancement, as they enable integration with existing semiconductor manufacturing processes without requiring significant modifications to front-end processing. This compatibility substantially reduces barriers to adoption and allows for heterogeneous integration of memory and logic functions. The technological trajectory indicates a steady improvement in material properties, with spin Hall angles increasing from less than 0.1 to values approaching 0.5 in certain material systems over the past five years.

The primary technical objectives for SOT film development include achieving reliable switching at sub-nanosecond timescales, reducing critical current densities below 10^6 A/cm², enhancing thermal stability for data retention beyond 10 years at operating temperatures, and ensuring compatibility with standard CMOS back-end-of-line processes. Additionally, there is significant focus on developing materials that maintain performance integrity under various stress conditions, including thermal cycling, voltage stress, and magnetic field interference.

Reliability testing of these films presents unique challenges due to the complex interplay between electrical, magnetic, and thermal properties at nanoscale dimensions. Understanding degradation mechanisms under various stress conditions is essential for predicting device lifetimes and establishing appropriate qualification standards for commercial deployment. Current research aims to establish standardized reliability stress test protocols specifically tailored for SOT-based devices, as existing semiconductor reliability frameworks may not adequately address the unique failure modes of these novel materials.

The global research landscape shows accelerating interest in SOT technology, with annual publications increasing by approximately 30% year-over-year since 2015. Major semiconductor manufacturers have established dedicated research programs, signaling industry recognition of SOT's potential to address scaling limitations in conventional memory technologies.

The fundamental principle behind SOT technology relies on the conversion of charge current to spin current through spin-orbit coupling effects in heavy metals or topological insulators. These materials, when interfaced with ferromagnetic layers, can efficiently manipulate magnetic states without requiring large current densities, thus addressing power consumption challenges in modern computing systems. Recent developments have focused on enhancing the spin-orbit coupling efficiency and thermal stability of these multilayer film structures.

Back-end CMOS compatible SOT films represent a critical advancement, as they enable integration with existing semiconductor manufacturing processes without requiring significant modifications to front-end processing. This compatibility substantially reduces barriers to adoption and allows for heterogeneous integration of memory and logic functions. The technological trajectory indicates a steady improvement in material properties, with spin Hall angles increasing from less than 0.1 to values approaching 0.5 in certain material systems over the past five years.

The primary technical objectives for SOT film development include achieving reliable switching at sub-nanosecond timescales, reducing critical current densities below 10^6 A/cm², enhancing thermal stability for data retention beyond 10 years at operating temperatures, and ensuring compatibility with standard CMOS back-end-of-line processes. Additionally, there is significant focus on developing materials that maintain performance integrity under various stress conditions, including thermal cycling, voltage stress, and magnetic field interference.

Reliability testing of these films presents unique challenges due to the complex interplay between electrical, magnetic, and thermal properties at nanoscale dimensions. Understanding degradation mechanisms under various stress conditions is essential for predicting device lifetimes and establishing appropriate qualification standards for commercial deployment. Current research aims to establish standardized reliability stress test protocols specifically tailored for SOT-based devices, as existing semiconductor reliability frameworks may not adequately address the unique failure modes of these novel materials.

The global research landscape shows accelerating interest in SOT technology, with annual publications increasing by approximately 30% year-over-year since 2015. Major semiconductor manufacturers have established dedicated research programs, signaling industry recognition of SOT's potential to address scaling limitations in conventional memory technologies.

Market Analysis for CMOS-Compatible SOT Films

The global market for CMOS-compatible SOT (Spin-Orbit Torque) films is experiencing significant growth, driven by increasing demand for advanced memory technologies with higher performance and lower power consumption. Current market valuations estimate the SOT-MRAM segment to reach approximately $500 million by 2025, with a compound annual growth rate of 40% from 2021 to 2025. This growth trajectory is primarily fueled by applications in data centers, automotive electronics, and IoT devices where non-volatility and endurance are critical requirements.

The demand landscape for CMOS-compatible SOT films is segmented across multiple industries. The data storage sector represents the largest market share, with enterprise storage solutions increasingly adopting SOT-based technologies to address performance bottlenecks in conventional storage hierarchies. Automotive electronics constitutes the fastest-growing segment, with projected market penetration increasing from 5% in 2022 to potentially 20% by 2027, particularly in advanced driver-assistance systems (ADAS) and autonomous driving platforms.

Geographically, North America leads the market with approximately 40% share, followed by Asia-Pacific at 35% and Europe at 20%. The Asia-Pacific region, particularly Taiwan, South Korea, and China, is expected to demonstrate the highest growth rate due to substantial investments in semiconductor manufacturing infrastructure and government initiatives supporting advanced memory technologies.

Key market drivers include the growing need for energy-efficient computing solutions, increasing data processing requirements, and the expanding edge computing ecosystem. The reliability aspects of SOT films directly impact market adoption rates, with industries placing premium value on technologies demonstrating superior endurance under thermal stress and radiation exposure conditions.

Market challenges include competition from alternative emerging memory technologies such as RRAM and PCM, which are also targeting similar application spaces. Additionally, the relatively higher manufacturing costs associated with specialized materials for SOT films present market entry barriers, particularly for smaller semiconductor manufacturers.

Customer requirements are increasingly focused on reliability metrics, with industry specifications demanding operational stability across temperature ranges from -40°C to 125°C for automotive applications and radiation hardness for aerospace implementations. The market shows clear correlation between demonstrated reliability through standardized stress tests and commercial adoption rates, making reliability engineering a critical factor in market penetration strategies for SOT-based technologies.

The demand landscape for CMOS-compatible SOT films is segmented across multiple industries. The data storage sector represents the largest market share, with enterprise storage solutions increasingly adopting SOT-based technologies to address performance bottlenecks in conventional storage hierarchies. Automotive electronics constitutes the fastest-growing segment, with projected market penetration increasing from 5% in 2022 to potentially 20% by 2027, particularly in advanced driver-assistance systems (ADAS) and autonomous driving platforms.

Geographically, North America leads the market with approximately 40% share, followed by Asia-Pacific at 35% and Europe at 20%. The Asia-Pacific region, particularly Taiwan, South Korea, and China, is expected to demonstrate the highest growth rate due to substantial investments in semiconductor manufacturing infrastructure and government initiatives supporting advanced memory technologies.

Key market drivers include the growing need for energy-efficient computing solutions, increasing data processing requirements, and the expanding edge computing ecosystem. The reliability aspects of SOT films directly impact market adoption rates, with industries placing premium value on technologies demonstrating superior endurance under thermal stress and radiation exposure conditions.

Market challenges include competition from alternative emerging memory technologies such as RRAM and PCM, which are also targeting similar application spaces. Additionally, the relatively higher manufacturing costs associated with specialized materials for SOT films present market entry barriers, particularly for smaller semiconductor manufacturers.

Customer requirements are increasingly focused on reliability metrics, with industry specifications demanding operational stability across temperature ranges from -40°C to 125°C for automotive applications and radiation hardness for aerospace implementations. The market shows clear correlation between demonstrated reliability through standardized stress tests and commercial adoption rates, making reliability engineering a critical factor in market penetration strategies for SOT-based technologies.

Current Reliability Challenges in Back End SOT Films

The integration of Spin-Orbit Torque (SOT) films into back-end-of-line (BEOL) CMOS processes presents significant reliability challenges that must be addressed before widespread commercial implementation. Current SOT films face thermal stability issues when subjected to the temperature ranges required for BEOL processing, which typically reach 400-450°C. These elevated temperatures can trigger undesirable diffusion, intermixing at interfaces, and crystallization processes that degrade the magnetic and electrical properties essential for SOT functionality.

Material degradation represents another critical challenge, as SOT films often incorporate heavy metals like Pt, W, or Ta that can diffuse into adjacent layers during thermal cycling. This diffusion compromises the sharp interfaces necessary for efficient spin-current generation and reduces overall device performance. Additionally, the formation of intermetallic compounds at these interfaces can fundamentally alter the spin-orbit coupling properties that enable SOT switching.

Mechanical stress-induced failures pose significant reliability concerns, particularly as SOT films must maintain integrity through multiple processing steps. The coefficient of thermal expansion mismatch between SOT materials and surrounding dielectrics or metallization layers generates substantial mechanical stress during thermal cycling. This stress manifests as delamination, cracking, or void formation that can completely disrupt device operation.

Electromigration effects become increasingly problematic as device dimensions shrink and current densities rise. The high current densities required for SOT switching (typically 10^11-10^12 A/m²) accelerate atomic migration, particularly at grain boundaries and interfaces, leading to resistance drift and eventual device failure. This challenge is compounded by the multi-layer structure of SOT devices, where each interface presents a potential failure point.

Oxidation and corrosion susceptibility presents another reliability hurdle, as many SOT materials (particularly those containing Fe, Co, or rare earth elements) exhibit high reactivity with oxygen and moisture. Even trace amounts of these contaminants during processing can form oxide layers that significantly degrade spin transport properties. Protective capping layers often introduce additional interfaces that complicate the spin transport mechanism.

Time-dependent dielectric breakdown (TDDB) has emerged as a reliability concern specific to SOT devices integrated with CMOS technology. The thin tunnel barriers or oxide layers often employed in SOT structures can experience premature breakdown under the electric fields present during operation, leading to catastrophic device failure or increased leakage currents that compromise energy efficiency.

Material degradation represents another critical challenge, as SOT films often incorporate heavy metals like Pt, W, or Ta that can diffuse into adjacent layers during thermal cycling. This diffusion compromises the sharp interfaces necessary for efficient spin-current generation and reduces overall device performance. Additionally, the formation of intermetallic compounds at these interfaces can fundamentally alter the spin-orbit coupling properties that enable SOT switching.

Mechanical stress-induced failures pose significant reliability concerns, particularly as SOT films must maintain integrity through multiple processing steps. The coefficient of thermal expansion mismatch between SOT materials and surrounding dielectrics or metallization layers generates substantial mechanical stress during thermal cycling. This stress manifests as delamination, cracking, or void formation that can completely disrupt device operation.

Electromigration effects become increasingly problematic as device dimensions shrink and current densities rise. The high current densities required for SOT switching (typically 10^11-10^12 A/m²) accelerate atomic migration, particularly at grain boundaries and interfaces, leading to resistance drift and eventual device failure. This challenge is compounded by the multi-layer structure of SOT devices, where each interface presents a potential failure point.

Oxidation and corrosion susceptibility presents another reliability hurdle, as many SOT materials (particularly those containing Fe, Co, or rare earth elements) exhibit high reactivity with oxygen and moisture. Even trace amounts of these contaminants during processing can form oxide layers that significantly degrade spin transport properties. Protective capping layers often introduce additional interfaces that complicate the spin transport mechanism.

Time-dependent dielectric breakdown (TDDB) has emerged as a reliability concern specific to SOT devices integrated with CMOS technology. The thin tunnel barriers or oxide layers often employed in SOT structures can experience premature breakdown under the electric fields present during operation, leading to catastrophic device failure or increased leakage currents that compromise energy efficiency.

Established Reliability Test Methodologies

01 Material composition for enhanced SOT film reliability

The reliability of spin-orbit torque (SOT) films can be significantly improved through specific material compositions. These compositions typically include heavy metals with strong spin-orbit coupling such as platinum, tungsten, or tantalum combined with ferromagnetic materials. The interface quality between these layers is crucial for maintaining consistent spin-orbit torque effects over time. Certain dopants and interlayer materials can be incorporated to enhance thermal stability and reduce degradation under operating conditions.- Material composition for enhanced SOT film reliability: The reliability of spin-orbit torque (SOT) films can be significantly improved through specific material compositions. These compositions typically include heavy metals with strong spin-orbit coupling such as platinum, tungsten, or tantalum combined with ferromagnetic materials. The interface quality between these layers is critical for maintaining consistent SOT effects over time. Certain dopants and interlayer materials can be incorporated to enhance thermal stability and reduce degradation under operating conditions, thereby extending the operational lifetime of SOT-based devices.

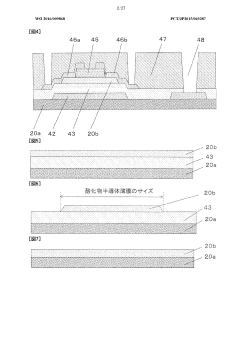

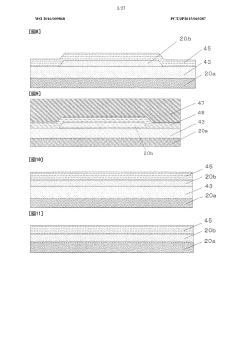

- Structural design for reliability improvement in SOT films: Specific structural designs can enhance the reliability of SOT films. These include multilayer structures with carefully engineered thicknesses, buffer layers to reduce lattice mismatch, and capping layers to prevent oxidation. The crystalline orientation and grain structure of the films significantly impact their long-term stability. Techniques such as interface engineering and strain management can reduce defect formation and migration during operation. These structural optimizations help maintain consistent SOT efficiency over extended periods and under various operating conditions.

- Thermal stability enhancement methods for SOT films: Thermal stability is crucial for SOT film reliability, especially in high-performance applications. Various methods can be employed to enhance thermal stability, including heat treatment processes during fabrication, incorporation of thermally stable barrier layers, and selection of materials with compatible thermal expansion coefficients. Advanced annealing techniques can optimize the microstructure and reduce thermal stress. Additionally, thermal management structures can be integrated to dissipate heat efficiently during device operation, preventing degradation of the SOT effect at elevated temperatures.

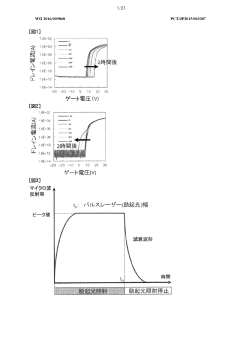

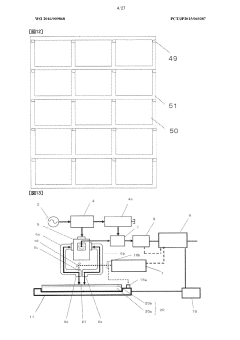

- Testing and characterization methods for SOT film reliability: Specialized testing and characterization methods are essential for evaluating and ensuring the reliability of SOT films. These include accelerated aging tests, thermal cycling, and electrical stress testing to predict long-term performance. Advanced analytical techniques such as high-resolution transmission electron microscopy, X-ray diffraction, and magnetic force microscopy can be used to monitor structural and magnetic property changes over time. In-situ measurements during operation can provide real-time data on SOT efficiency and stability. These comprehensive testing protocols help identify failure mechanisms and optimize film design for enhanced reliability.

- Integration techniques for reliable SOT-based devices: Successful integration of SOT films into practical devices requires specialized techniques to maintain reliability. These include optimized deposition methods that ensure uniform film quality across wafers, compatible etching processes that preserve interface integrity, and passivation techniques that protect films from environmental degradation. Careful consideration of electrical contacts and interconnects is necessary to prevent electromigration and other reliability issues. Additionally, packaging solutions that shield SOT films from mechanical stress, moisture, and contaminants significantly extend device lifetime. These integration approaches are critical for translating promising SOT film properties into reliable commercial devices.

02 Structural design for reliability improvement

Specific structural designs can enhance the reliability of SOT films. These include multilayer structures with carefully engineered thicknesses, buffer layers to reduce lattice mismatch, and capping layers to prevent oxidation. The crystalline orientation and grain structure of the films play important roles in determining long-term performance stability. Some designs incorporate gradient compositions or symmetry-breaking elements to optimize the spin current generation while maintaining structural integrity under thermal and electrical stress.Expand Specific Solutions03 Testing and characterization methods for SOT film reliability

Various testing methodologies have been developed to evaluate the reliability of SOT films. These include accelerated aging tests, thermal cycling, electrical stress testing, and magnetic field endurance tests. Advanced characterization techniques such as ferromagnetic resonance spectroscopy, magneto-optical Kerr effect measurements, and spin-torque ferromagnetic resonance are employed to monitor changes in SOT efficiency over time. These methods help identify failure mechanisms and predict the operational lifetime of SOT-based devices under various conditions.Expand Specific Solutions04 Integration techniques for reliable SOT devices

Successful integration of SOT films into practical devices requires specialized techniques to maintain reliability. These include optimized deposition methods such as sputtering with precise control of parameters, post-deposition annealing protocols, and interface engineering. Encapsulation strategies protect the films from environmental degradation. The electrical connection design and current distribution patterns are critical for preventing localized heating and electromigration that could compromise long-term stability. Compatible fabrication processes ensure that subsequent manufacturing steps do not damage the SOT film structure.Expand Specific Solutions05 Reliability enhancement through circuit design

Circuit-level approaches can significantly improve the operational reliability of SOT films. These include current regulation circuits that prevent damaging current spikes, temperature compensation mechanisms, and feedback systems that adjust operating parameters based on performance monitoring. Redundancy schemes and error correction techniques can be implemented to maintain system functionality even if individual SOT elements degrade. Power management strategies minimize thermal stress during operation, while specialized reading and writing protocols extend the functional lifetime of SOT-based memory and logic devices.Expand Specific Solutions

Leading Companies in SOT Film Manufacturing

The reliability stress testing for Back End CMOS Compatible SOT (Spin-Orbit Torque) films is currently in an early growth phase, with the market expanding as emerging memory technologies gain traction. The global landscape is dominated by major semiconductor foundries including TSMC, GlobalFoundries, Samsung, and SMIC, who are investing in SOT technology as a potential successor to conventional memory solutions. Technical maturity remains moderate, with companies like IBM, Infineon, and Micron leading research efforts to overcome reliability challenges in high-temperature environments and extended cycling conditions. The competitive dynamics show a clear division between established foundry players focusing on manufacturing scalability and specialized research entities addressing fundamental material science challenges.

GLOBALFOUNDRIES, Inc.

Technical Solution: GLOBALFOUNDRIES has developed comprehensive reliability stress test methodologies specifically for back-end CMOS compatible SOT (Spin-Orbit Torque) films. Their approach integrates time-dependent dielectric breakdown (TDDB) tests with specialized thermal cycling protocols designed to evaluate SOT film integrity in advanced nodes. The company employs proprietary high-temperature operating life (HTOL) testing at temperatures up to 125°C while applying varying current densities to simulate real-world operational stresses. Their test suite includes electromigration analysis specifically calibrated for SOT material interfaces with conventional CMOS back-end metals. GLOBALFOUNDRIES has implemented automated test equipment (ATE) platforms that can simultaneously evaluate thousands of test structures, enabling statistically significant reliability data collection across process variations.

Strengths: Comprehensive test methodology covering multiple failure mechanisms specific to SOT films; large-scale statistical analysis capabilities; established correlation between accelerated tests and field reliability. Weaknesses: Tests primarily optimized for their specific process technology; relatively high cost of implementation; longer qualification timeline compared to conventional CMOS processes.

International Business Machines Corp.

Technical Solution: IBM has pioneered advanced reliability stress testing methodologies for back-end CMOS compatible SOT films through their "Triangulated Reliability Assessment" framework. This approach combines electrical, thermal, and mechanical stress testing to comprehensively evaluate SOT film integrity. Their methodology includes specialized bias temperature instability (BTI) tests modified for SOT materials, with particular focus on interface degradation mechanisms between magnetic layers and CMOS interconnects. IBM employs in-situ monitoring techniques during stress testing, allowing real-time observation of failure mechanisms rather than just end-point measurements. Their reliability models incorporate machine learning algorithms trained on extensive test data to predict lifetime performance under various operating conditions. IBM has also developed non-destructive evaluation techniques using advanced imaging and spectroscopy to correlate physical changes with electrical performance degradation.

Strengths: Industry-leading in-situ monitoring capabilities; sophisticated predictive modeling; extensive experience with hybrid material systems integration. Weaknesses: Complex test infrastructure requirements; higher implementation costs; tests optimized primarily for research rather than high-volume manufacturing environments.

Critical Patents in SOT Film Reliability Testing

Method for evaluating quality of oxide semiconductor thin film and laminated body having protective film on surface of oxide semiconductor thin film, and method for managing quality of oxide semiconductor thin film

PatentWO2016009868A1

Innovation

- A method involving the measurement of defects in the oxide semiconductor thin film and its interface with a protective film using both contact and non-contact methods, specifically the microwave photoconductivity decay (μ-PCD) method, to evaluate the electronic state and predict optimal manufacturing conditions for reducing defects and enhancing stress resistance.

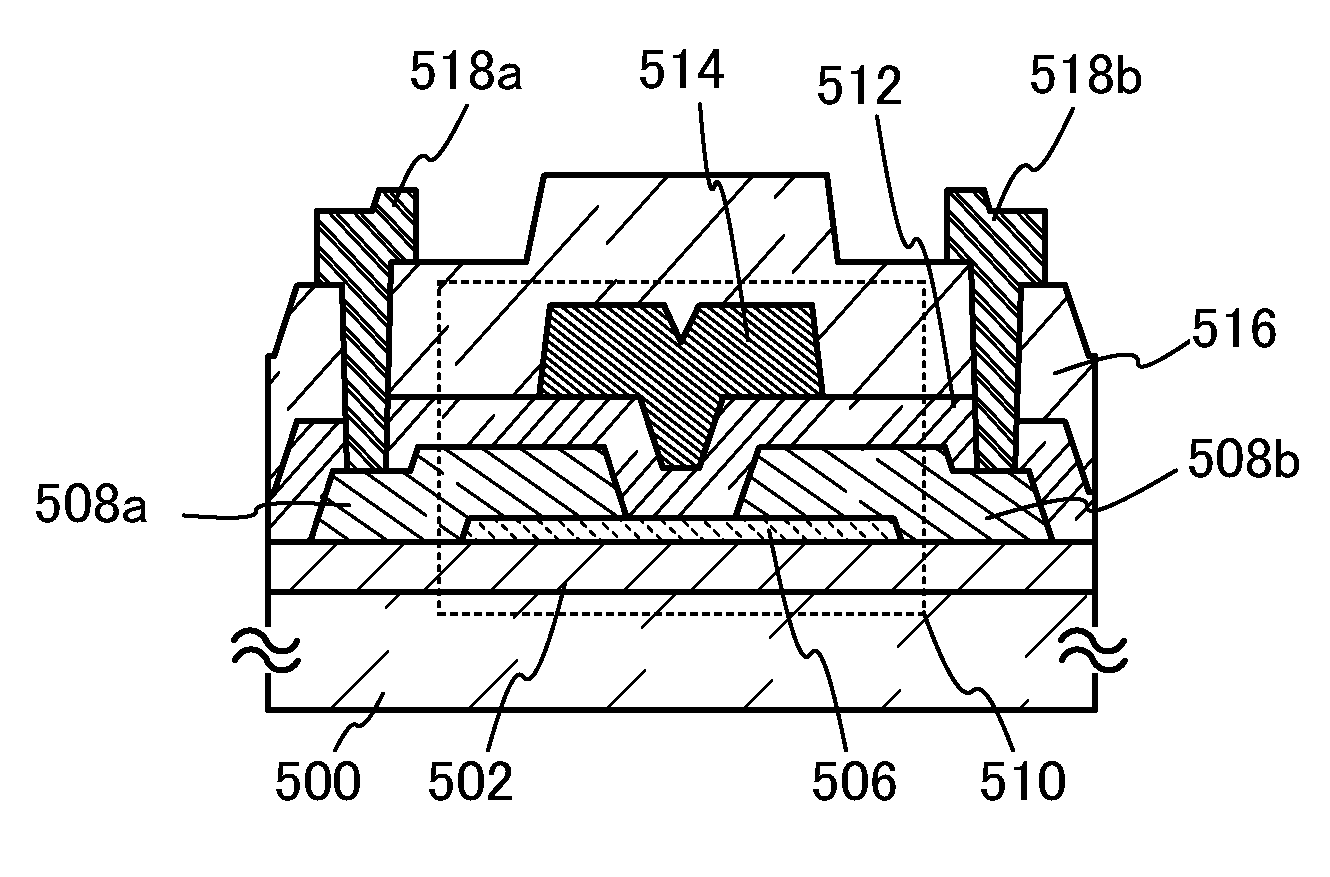

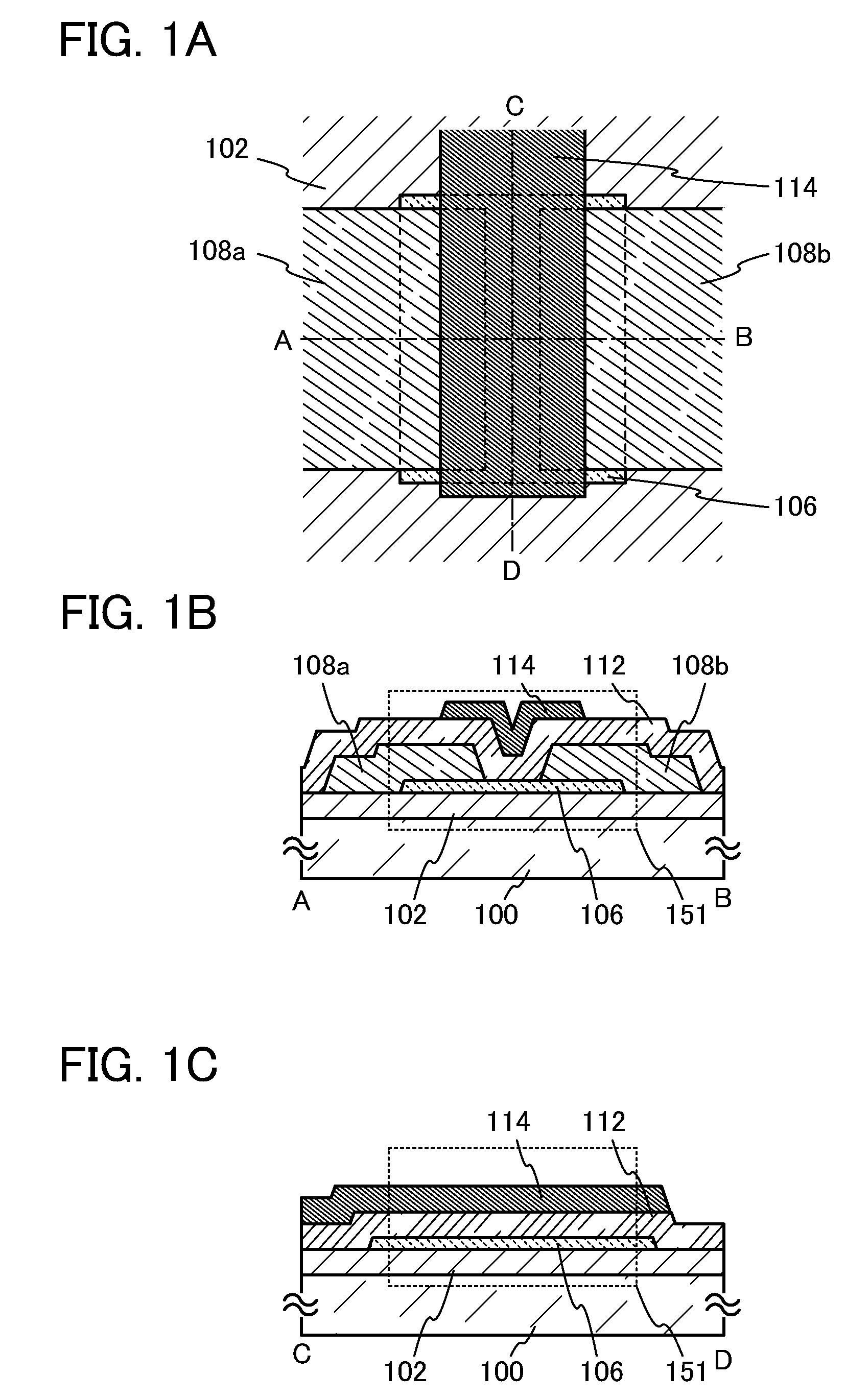

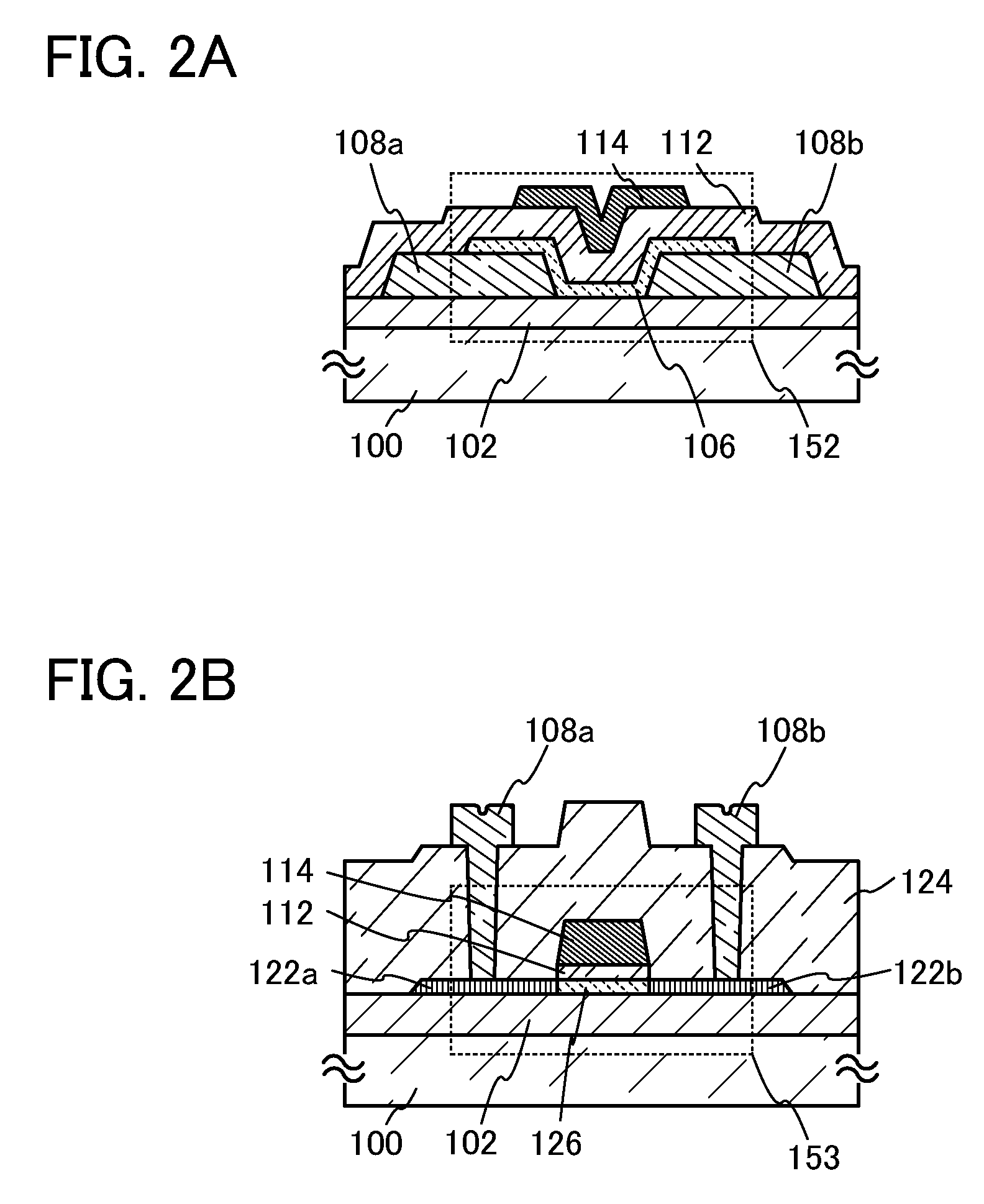

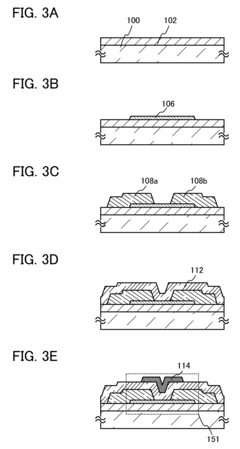

Semiconductor device

PatentActiveUS20110284844A1

Innovation

- An insulating layer that releases oxygen by heating is used as a base layer to supply oxygen to the oxide semiconductor layer, reducing interface states and oxygen deficiency, thereby stabilizing the threshold voltage and improving reliability.

Standardization Efforts for SOT Film Reliability

The standardization of reliability testing for Spin-Orbit Torque (SOT) films represents a critical frontier in semiconductor manufacturing, particularly as these materials gain prominence in back-end CMOS compatible processes. Currently, the industry faces significant challenges due to the absence of universally accepted testing protocols, which hampers cross-comparison of research results and slows commercial adoption.

Several international bodies have begun coordinating standardization efforts, with the Joint Electron Device Engineering Council (JEDEC) establishing a specialized working group focused on SOT film reliability in 2021. This group aims to develop comprehensive testing methodologies that address the unique characteristics of SOT materials when integrated into CMOS back-end processes.

The IEEE Magnetics Society has simultaneously launched an initiative to standardize terminology and measurement techniques specific to SOT films. Their framework proposes standardized stress test conditions including temperature ranges (25°C to 150°C), magnetic field strengths (0-2T), and current density parameters (10^6 to 10^8 A/cm²) that reflect realistic operating conditions in semiconductor devices.

Semiconductor manufacturers including Samsung, TSMC, and Intel have formed an industry consortium dedicated to establishing reliability qualification standards for SOT-based memory technologies. Their collaborative approach focuses on accelerated lifetime testing protocols and failure analysis methodologies specifically tailored to back-end processing constraints.

The International Electrotechnical Commission (IEC) has published preliminary guidelines (IEC 63365) addressing reliability assessment for emerging spintronic devices, with a dedicated section on SOT film testing. These guidelines emphasize the importance of standardized sample preparation to ensure meaningful comparisons across different research and manufacturing facilities.

European efforts through the EMMC (European Materials Modelling Council) have concentrated on developing digital twins for SOT film reliability testing, creating virtual testing environments that can predict long-term reliability based on accelerated stress test data. This approach potentially reduces physical testing requirements while improving statistical confidence in reliability projections.

A significant challenge in standardization remains the correlation between accelerated stress tests and actual device performance in field conditions. Current proposals advocate for a multi-tiered testing approach that combines high-stress conditions for failure mechanism identification with moderate stress conditions that better represent operational environments.

The timeline for full standardization remains fluid, with most industry analysts projecting comprehensive standards to emerge within the next 3-5 years as the technology matures and more manufacturers incorporate SOT films into production devices.

Several international bodies have begun coordinating standardization efforts, with the Joint Electron Device Engineering Council (JEDEC) establishing a specialized working group focused on SOT film reliability in 2021. This group aims to develop comprehensive testing methodologies that address the unique characteristics of SOT materials when integrated into CMOS back-end processes.

The IEEE Magnetics Society has simultaneously launched an initiative to standardize terminology and measurement techniques specific to SOT films. Their framework proposes standardized stress test conditions including temperature ranges (25°C to 150°C), magnetic field strengths (0-2T), and current density parameters (10^6 to 10^8 A/cm²) that reflect realistic operating conditions in semiconductor devices.

Semiconductor manufacturers including Samsung, TSMC, and Intel have formed an industry consortium dedicated to establishing reliability qualification standards for SOT-based memory technologies. Their collaborative approach focuses on accelerated lifetime testing protocols and failure analysis methodologies specifically tailored to back-end processing constraints.

The International Electrotechnical Commission (IEC) has published preliminary guidelines (IEC 63365) addressing reliability assessment for emerging spintronic devices, with a dedicated section on SOT film testing. These guidelines emphasize the importance of standardized sample preparation to ensure meaningful comparisons across different research and manufacturing facilities.

European efforts through the EMMC (European Materials Modelling Council) have concentrated on developing digital twins for SOT film reliability testing, creating virtual testing environments that can predict long-term reliability based on accelerated stress test data. This approach potentially reduces physical testing requirements while improving statistical confidence in reliability projections.

A significant challenge in standardization remains the correlation between accelerated stress tests and actual device performance in field conditions. Current proposals advocate for a multi-tiered testing approach that combines high-stress conditions for failure mechanism identification with moderate stress conditions that better represent operational environments.

The timeline for full standardization remains fluid, with most industry analysts projecting comprehensive standards to emerge within the next 3-5 years as the technology matures and more manufacturers incorporate SOT films into production devices.

Environmental Impact of SOT Film Processing

The manufacturing processes for Spin-Orbit Torque (SOT) films in CMOS-compatible back-end-of-line (BEOL) integration present significant environmental considerations that must be addressed. The deposition of SOT materials, primarily heavy metals such as platinum, tungsten, and tantalum, involves processes that generate waste materials requiring specialized handling and disposal protocols. These metals, while essential for SOT functionality, can pose environmental hazards if released into ecosystems through improper waste management.

Chemical vapor deposition (CVD) and physical vapor deposition (PVD) techniques used in SOT film processing consume substantial energy and utilize precursor gases that may include greenhouse gas compounds. For instance, the plasma-enhanced CVD methods commonly employed for uniform SOT film deposition require high-temperature operations and specialized gas mixtures, contributing to the carbon footprint of semiconductor manufacturing facilities. Recent industry assessments indicate that SOT film processing accounts for approximately 3-5% of the total energy consumption in advanced semiconductor fabrication plants.

Water usage represents another critical environmental concern in SOT film processing. The cleaning and etching steps necessary for SOT film patterning utilize ultra-pure water resources, with estimates suggesting that a typical 300mm wafer fabrication facility may consume between 2-4 million gallons of water daily. Wastewater from these processes contains trace metals and chemical compounds that require advanced treatment systems before discharge.

The reliability stress testing of SOT films introduces additional environmental considerations. Accelerated aging tests, thermal cycling, and humidity stress evaluations generate electronic waste containing the tested SOT materials. As these tests are designed to push materials to failure, they may release particulates and compounds that require specialized filtration and containment systems within testing facilities.

Recent advancements in green manufacturing techniques are beginning to address these environmental challenges. Atomic layer deposition (ALD) methods for SOT film processing offer more precise material utilization, reducing waste generation by up to 40% compared to conventional techniques. Additionally, closed-loop water recycling systems specifically designed for semiconductor fabrication have demonstrated the potential to reduce freshwater consumption by 60-80% in SOT processing steps.

The semiconductor industry has established collaborative initiatives focused on developing environmentally sustainable practices for emerging memory technologies, including SOT-based devices. These efforts include the implementation of life cycle assessment methodologies to quantify environmental impacts and identify opportunities for process optimization. As reliability testing protocols for SOT films continue to evolve, integrating environmental considerations into test design represents an important frontier for sustainable semiconductor manufacturing.

Chemical vapor deposition (CVD) and physical vapor deposition (PVD) techniques used in SOT film processing consume substantial energy and utilize precursor gases that may include greenhouse gas compounds. For instance, the plasma-enhanced CVD methods commonly employed for uniform SOT film deposition require high-temperature operations and specialized gas mixtures, contributing to the carbon footprint of semiconductor manufacturing facilities. Recent industry assessments indicate that SOT film processing accounts for approximately 3-5% of the total energy consumption in advanced semiconductor fabrication plants.

Water usage represents another critical environmental concern in SOT film processing. The cleaning and etching steps necessary for SOT film patterning utilize ultra-pure water resources, with estimates suggesting that a typical 300mm wafer fabrication facility may consume between 2-4 million gallons of water daily. Wastewater from these processes contains trace metals and chemical compounds that require advanced treatment systems before discharge.

The reliability stress testing of SOT films introduces additional environmental considerations. Accelerated aging tests, thermal cycling, and humidity stress evaluations generate electronic waste containing the tested SOT materials. As these tests are designed to push materials to failure, they may release particulates and compounds that require specialized filtration and containment systems within testing facilities.

Recent advancements in green manufacturing techniques are beginning to address these environmental challenges. Atomic layer deposition (ALD) methods for SOT film processing offer more precise material utilization, reducing waste generation by up to 40% compared to conventional techniques. Additionally, closed-loop water recycling systems specifically designed for semiconductor fabrication have demonstrated the potential to reduce freshwater consumption by 60-80% in SOT processing steps.

The semiconductor industry has established collaborative initiatives focused on developing environmentally sustainable practices for emerging memory technologies, including SOT-based devices. These efforts include the implementation of life cycle assessment methodologies to quantify environmental impacts and identify opportunities for process optimization. As reliability testing protocols for SOT films continue to evolve, integrating environmental considerations into test design represents an important frontier for sustainable semiconductor manufacturing.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!