Modeling SOT MRAM Switching Dynamics Compact Models

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SOT MRAM Technology Background and Objectives

Spin-Orbit Torque Magnetoresistive Random Access Memory (SOT-MRAM) represents a significant advancement in non-volatile memory technology, emerging from decades of research in spintronics and magnetic materials. The evolution of MRAM technology began with Toggle MRAM, progressed through Spin-Transfer Torque (STT) MRAM, and has now reached the SOT-MRAM paradigm, which offers superior performance characteristics including faster switching speeds, lower energy consumption, and enhanced endurance.

The fundamental principle behind SOT-MRAM involves the manipulation of magnetic states through spin-orbit coupling effects, where an in-plane current generates a torque capable of switching the magnetization direction of a ferromagnetic layer. This mechanism differs significantly from its STT-MRAM predecessor, which relies on a perpendicular current path through the magnetic tunnel junction (MTJ) for switching operations.

Current technological trends indicate a growing interest in SOT-MRAM due to its potential to overcome the limitations of existing memory technologies. The separation of read and write paths in SOT-MRAM architecture addresses the reliability concerns associated with STT-MRAM, particularly regarding the oxide barrier degradation during write operations. This structural advantage positions SOT-MRAM as a promising candidate for next-generation cache memory applications.

The primary objective of modeling SOT-MRAM switching dynamics through compact models is to establish accurate, computationally efficient representations of device behavior that can be integrated into circuit design environments. These models must capture the complex physics of spin-orbit interactions while remaining accessible for large-scale circuit simulations, striking a balance between physical accuracy and computational practicality.

Developing comprehensive compact models requires addressing several key challenges, including the accurate representation of thermal effects, material interface properties, and switching stochasticity. The models must also account for various SOT mechanisms, including spin Hall effect (SHE) and Rashba effect, which contribute differently to the overall switching dynamics depending on material composition and device geometry.

The technological trajectory suggests that SOT-MRAM could potentially replace SRAM in cache hierarchies and even challenge DRAM in certain applications, provided that density and cost metrics continue to improve. Industry projections indicate that SOT-MRAM may achieve commercial viability within the next 3-5 years, with initial applications focusing on edge computing devices and IoT systems where power efficiency is paramount.

Research objectives in this field extend beyond basic functionality to include optimization for specific application requirements, such as ultra-low power operation for IoT devices or radiation hardness for aerospace applications. The development of accurate compact models will accelerate this optimization process by enabling rapid design exploration and performance prediction.

The fundamental principle behind SOT-MRAM involves the manipulation of magnetic states through spin-orbit coupling effects, where an in-plane current generates a torque capable of switching the magnetization direction of a ferromagnetic layer. This mechanism differs significantly from its STT-MRAM predecessor, which relies on a perpendicular current path through the magnetic tunnel junction (MTJ) for switching operations.

Current technological trends indicate a growing interest in SOT-MRAM due to its potential to overcome the limitations of existing memory technologies. The separation of read and write paths in SOT-MRAM architecture addresses the reliability concerns associated with STT-MRAM, particularly regarding the oxide barrier degradation during write operations. This structural advantage positions SOT-MRAM as a promising candidate for next-generation cache memory applications.

The primary objective of modeling SOT-MRAM switching dynamics through compact models is to establish accurate, computationally efficient representations of device behavior that can be integrated into circuit design environments. These models must capture the complex physics of spin-orbit interactions while remaining accessible for large-scale circuit simulations, striking a balance between physical accuracy and computational practicality.

Developing comprehensive compact models requires addressing several key challenges, including the accurate representation of thermal effects, material interface properties, and switching stochasticity. The models must also account for various SOT mechanisms, including spin Hall effect (SHE) and Rashba effect, which contribute differently to the overall switching dynamics depending on material composition and device geometry.

The technological trajectory suggests that SOT-MRAM could potentially replace SRAM in cache hierarchies and even challenge DRAM in certain applications, provided that density and cost metrics continue to improve. Industry projections indicate that SOT-MRAM may achieve commercial viability within the next 3-5 years, with initial applications focusing on edge computing devices and IoT systems where power efficiency is paramount.

Research objectives in this field extend beyond basic functionality to include optimization for specific application requirements, such as ultra-low power operation for IoT devices or radiation hardness for aerospace applications. The development of accurate compact models will accelerate this optimization process by enabling rapid design exploration and performance prediction.

Market Analysis for SOT MRAM Applications

The global market for Spin-Orbit Torque Magnetic Random Access Memory (SOT MRAM) is experiencing significant growth as the technology matures from research laboratories to commercial applications. Current market projections indicate that the overall MRAM market, including SOT MRAM, is expected to reach $5 billion by 2028, with a compound annual growth rate of approximately 29% from 2023 to 2028. SOT MRAM represents an emerging segment within this broader market, with increasing adoption rates as its advantages over conventional memory technologies become more apparent.

The primary market drivers for SOT MRAM include the growing demand for energy-efficient, non-volatile memory solutions in data centers, where power consumption and heat generation are critical concerns. Data centers currently account for approximately 2% of global electricity consumption, creating strong incentives for adopting more energy-efficient memory technologies like SOT MRAM.

The automotive sector represents another significant market opportunity, particularly for advanced driver assistance systems (ADAS) and autonomous vehicles, which require reliable, radiation-resistant memory that can operate across wide temperature ranges. Industry analysts project that automotive memory requirements will grow at 25% annually through 2026, with safety-critical applications increasingly demanding the reliability characteristics that SOT MRAM provides.

Consumer electronics manufacturers are also showing interest in SOT MRAM for next-generation smartphones, wearables, and IoT devices, where battery life extension is a key competitive advantage. The ability of SOT MRAM to reduce standby power consumption by up to 40% compared to conventional memory solutions makes it particularly attractive for these applications.

Enterprise storage systems represent another promising application area, with the need for fast, non-volatile cache memory growing as data processing requirements increase. The enterprise storage market is projected to reach $78 billion by 2027, with memory subsystems accounting for approximately 15% of this value.

From a geographical perspective, North America currently leads SOT MRAM research and development activities, with approximately 45% of patents and commercial initiatives. Asia-Pacific, particularly Japan, South Korea, and Taiwan, follows closely with significant investments in manufacturing infrastructure for advanced memory technologies.

Market challenges include the relatively high production costs compared to established memory technologies like DRAM and flash memory. However, as manufacturing processes mature and economies of scale are achieved, the cost gap is expected to narrow significantly by 2025. Additionally, the need for specialized design tools and compact models for SOT MRAM, including accurate switching dynamics models, represents both a market challenge and opportunity for EDA tool providers and semiconductor IP companies.

The primary market drivers for SOT MRAM include the growing demand for energy-efficient, non-volatile memory solutions in data centers, where power consumption and heat generation are critical concerns. Data centers currently account for approximately 2% of global electricity consumption, creating strong incentives for adopting more energy-efficient memory technologies like SOT MRAM.

The automotive sector represents another significant market opportunity, particularly for advanced driver assistance systems (ADAS) and autonomous vehicles, which require reliable, radiation-resistant memory that can operate across wide temperature ranges. Industry analysts project that automotive memory requirements will grow at 25% annually through 2026, with safety-critical applications increasingly demanding the reliability characteristics that SOT MRAM provides.

Consumer electronics manufacturers are also showing interest in SOT MRAM for next-generation smartphones, wearables, and IoT devices, where battery life extension is a key competitive advantage. The ability of SOT MRAM to reduce standby power consumption by up to 40% compared to conventional memory solutions makes it particularly attractive for these applications.

Enterprise storage systems represent another promising application area, with the need for fast, non-volatile cache memory growing as data processing requirements increase. The enterprise storage market is projected to reach $78 billion by 2027, with memory subsystems accounting for approximately 15% of this value.

From a geographical perspective, North America currently leads SOT MRAM research and development activities, with approximately 45% of patents and commercial initiatives. Asia-Pacific, particularly Japan, South Korea, and Taiwan, follows closely with significant investments in manufacturing infrastructure for advanced memory technologies.

Market challenges include the relatively high production costs compared to established memory technologies like DRAM and flash memory. However, as manufacturing processes mature and economies of scale are achieved, the cost gap is expected to narrow significantly by 2025. Additionally, the need for specialized design tools and compact models for SOT MRAM, including accurate switching dynamics models, represents both a market challenge and opportunity for EDA tool providers and semiconductor IP companies.

Current Challenges in SOT MRAM Modeling

Despite significant advancements in Spin-Orbit Torque Magnetic Random Access Memory (SOT-MRAM) technology, modeling the switching dynamics accurately remains a formidable challenge. Current compact models struggle to capture the complex interplay between various physical phenomena that govern SOT-MRAM operation. The primary difficulty lies in simultaneously accounting for thermal effects, material interface properties, and spin transport mechanisms within computationally efficient frameworks suitable for circuit-level simulations.

One major challenge is the accurate representation of temperature dependencies in SOT-MRAM switching. Existing models often employ simplified assumptions that fail to capture the non-linear thermal behaviors observed in experimental devices, particularly at scaled dimensions below 30nm. This discrepancy creates significant reliability concerns when designing SOT-MRAM for applications requiring operation across wide temperature ranges.

The multi-physics nature of SOT switching presents another substantial modeling hurdle. Current approaches frequently treat magnetization dynamics, spin transport, and thermal effects as separate phenomena with simplified coupling mechanisms. However, experimental evidence increasingly demonstrates that these processes are deeply intertwined, with feedback loops that significantly impact switching behavior. Developing unified models that coherently integrate these physical domains without excessive computational overhead remains an open problem.

Material interface effects represent a particularly challenging aspect to model accurately. The efficiency of spin-current generation and transmission across material boundaries depends critically on interface quality, which can vary substantially between theoretical models and fabricated devices. Compact models struggle to parameterize these interface-dependent behaviors in ways that remain physically meaningful while maintaining computational efficiency.

Variability modeling presents another significant challenge. Device-to-device variations stemming from fabrication processes and intrinsic material properties significantly impact SOT-MRAM performance. Current compact models typically address variability through statistical approaches that may not adequately capture the physical origins of these variations, limiting their predictive power for technology scaling and yield optimization.

Time-dependent reliability effects, such as breakdown mechanisms and performance degradation under repeated cycling, remain poorly represented in existing compact models. The long-term behavior of SOT-MRAM devices involves complex degradation mechanisms that current models typically address through empirical fitting rather than physics-based approaches, limiting their applicability for lifetime predictions.

One major challenge is the accurate representation of temperature dependencies in SOT-MRAM switching. Existing models often employ simplified assumptions that fail to capture the non-linear thermal behaviors observed in experimental devices, particularly at scaled dimensions below 30nm. This discrepancy creates significant reliability concerns when designing SOT-MRAM for applications requiring operation across wide temperature ranges.

The multi-physics nature of SOT switching presents another substantial modeling hurdle. Current approaches frequently treat magnetization dynamics, spin transport, and thermal effects as separate phenomena with simplified coupling mechanisms. However, experimental evidence increasingly demonstrates that these processes are deeply intertwined, with feedback loops that significantly impact switching behavior. Developing unified models that coherently integrate these physical domains without excessive computational overhead remains an open problem.

Material interface effects represent a particularly challenging aspect to model accurately. The efficiency of spin-current generation and transmission across material boundaries depends critically on interface quality, which can vary substantially between theoretical models and fabricated devices. Compact models struggle to parameterize these interface-dependent behaviors in ways that remain physically meaningful while maintaining computational efficiency.

Variability modeling presents another significant challenge. Device-to-device variations stemming from fabrication processes and intrinsic material properties significantly impact SOT-MRAM performance. Current compact models typically address variability through statistical approaches that may not adequately capture the physical origins of these variations, limiting their predictive power for technology scaling and yield optimization.

Time-dependent reliability effects, such as breakdown mechanisms and performance degradation under repeated cycling, remain poorly represented in existing compact models. The long-term behavior of SOT-MRAM devices involves complex degradation mechanisms that current models typically address through empirical fitting rather than physics-based approaches, limiting their applicability for lifetime predictions.

Current Compact Modeling Approaches

01 SOT-MRAM switching mechanisms and dynamics

Spin-Orbit Torque (SOT) switching in MRAM devices involves the manipulation of magnetic moments through spin-orbit coupling effects. The switching dynamics are characterized by the interaction between spin currents and magnetic layers, which determines the speed and efficiency of the memory operation. These mechanisms include field-like torques and damping-like torques that affect the magnetization reversal process, with various factors influencing the critical current required for switching and the overall switching time.- SOT-MRAM switching mechanisms and dynamics: Spin-Orbit Torque (SOT) switching in MRAM involves the manipulation of magnetic moments through spin-orbit coupling effects. The switching dynamics are characterized by the interaction between spin current and magnetization, leading to deterministic magnetization reversal. These mechanisms enable faster and more energy-efficient switching compared to conventional STT-MRAM, with reduced latency and improved reliability for high-speed memory applications.

- Material composition and structure for enhanced SOT efficiency: The material composition and structure of SOT-MRAM devices significantly impact switching dynamics. Multilayer structures incorporating heavy metals (such as Pt, Ta, or W) adjacent to ferromagnetic layers create strong spin-orbit coupling interfaces. Advanced material combinations and engineered interfaces enhance spin current generation and improve switching efficiency, while optimized magnetic tunnel junction (MTJ) structures reduce the critical current needed for reliable switching operations.

- Current pulse optimization for SOT switching: The characteristics of current pulses significantly affect SOT-MRAM switching dynamics. Pulse amplitude, duration, and shape can be optimized to achieve faster and more reliable switching while minimizing power consumption. Advanced pulse schemes, including multi-pulse sequences and shaped waveforms, can overcome energy barriers more efficiently and improve switching reliability under various operating conditions.

- Thermal effects and stability in SOT-MRAM: Thermal effects play a crucial role in SOT-MRAM switching dynamics. Temperature fluctuations can influence the energy barrier for magnetization reversal and affect switching reliability. Advanced designs incorporate thermal stability factors to ensure data retention while maintaining switching efficiency. Thermal management techniques and materials with optimized temperature coefficients help maintain consistent performance across operating temperature ranges.

- Integration and scaling of SOT-MRAM technology: Integration and scaling considerations are essential for practical SOT-MRAM implementation. Device architectures that enable high-density memory arrays while maintaining switching reliability present significant challenges. Advanced fabrication techniques allow for reduced device dimensions while preserving SOT switching efficiency. Three-terminal and novel device configurations offer advantages for specific applications, with optimized layouts that minimize cross-talk and interference between adjacent memory cells.

02 Material composition and structure optimization for SOT-MRAM

The performance of SOT-MRAM devices heavily depends on the materials used and their structural configuration. Heavy metals with strong spin-orbit coupling (such as Pt, Ta, or W) are commonly used as spin current generators. The magnetic free layer composition, thickness, and interface quality significantly impact switching efficiency. Multi-layer structures with carefully engineered interfaces can enhance spin current generation and improve switching dynamics, while reducing the energy required for reliable operation.Expand Specific Solutions03 Energy efficiency and thermal stability in SOT switching

Energy efficiency is a critical consideration in SOT-MRAM design, with research focused on reducing the critical current density required for reliable switching while maintaining thermal stability. Various approaches include optimizing the magnetic anisotropy, engineering the spin Hall angle of materials, and developing novel device geometries. Thermal effects play a significant role in switching dynamics, affecting both reliability and data retention. Advanced designs incorporate features to manage thermal fluctuations while ensuring low-power operation.Expand Specific Solutions04 Integration and fabrication techniques for SOT-MRAM

The integration of SOT-MRAM into existing semiconductor processes presents challenges that require specialized fabrication techniques. These include precise deposition methods for ultrathin magnetic layers, interface engineering to enhance spin transport, and compatibility with CMOS processing. Advanced lithography and etching processes are employed to create nanoscale device structures with the required magnetic properties. Post-fabrication treatments such as annealing can be used to optimize magnetic properties and interface quality for improved switching performance.Expand Specific Solutions05 Novel SOT-MRAM architectures and control schemes

Innovative device architectures are being developed to enhance SOT-MRAM performance, including three-terminal configurations that separate the read and write paths, dual spin-orbit layers for enhanced efficiency, and hybrid switching schemes combining multiple mechanisms. Advanced control schemes utilize precise current pulses with optimized amplitude, duration, and shape to achieve faster and more reliable switching. Some designs incorporate assisting mechanisms such as external magnetic fields or strain to reduce the energy barrier for magnetization reversal, resulting in improved switching dynamics.Expand Specific Solutions

Key Industry Players in MRAM Technology

The SOT MRAM switching dynamics compact modeling landscape is currently in a growth phase, with the market expanding rapidly as MRAM emerges as a promising non-volatile memory technology. The global competition is led by major semiconductor players including IBM, Samsung Electronics, and TSMC, who are developing advanced modeling techniques to optimize SOT MRAM performance. Technology maturity varies, with established companies like Qualcomm and GlobalFoundries focusing on integration into commercial products, while research institutions such as IMEC, CNRS, and various universities are advancing fundamental understanding of switching physics. Specialized companies like Antaios are emerging with innovative SOT-based solutions. The field is characterized by intense collaboration between industry and academia to overcome challenges in accurate modeling of the complex magnetic dynamics at nanoscale dimensions.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive compact models for SOT-MRAM (Spin-Orbit Torque Magnetic Random Access Memory) switching dynamics that incorporate both macrospin and micromagnetic approaches. Their models account for thermal effects, material interface properties, and spin-current distributions to accurately predict switching behavior. IBM's approach includes a physics-based compact model that captures the non-linear dynamics of magnetization switching under various bias conditions and temperatures. They've implemented these models in industry-standard SPICE simulators for circuit designers, enabling accurate performance prediction at the device and system levels. IBM has also developed specialized parameter extraction methodologies to calibrate their models against experimental data from fabricated SOT-MRAM devices, ensuring high fidelity between simulations and real-world performance.

Strengths: IBM's models offer exceptional accuracy by incorporating complex physical phenomena while maintaining computational efficiency. Their integration with standard design tools facilitates adoption by circuit designers. Weaknesses: The models may require extensive characterization data for parameter calibration, potentially limiting applicability to novel materials or device structures without sufficient experimental validation.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered compact modeling approaches for SOT-MRAM that focus on practical implementation in high-volume manufacturing environments. Their models incorporate both deterministic and probabilistic switching behaviors, accounting for process variations critical for yield prediction. Samsung's approach includes multi-physics simulations that couple electrical, magnetic, and thermal domains to capture the complete device behavior. They've developed specialized Verilog-A compact models that can be directly integrated into their memory design workflow, enabling system architects to evaluate SOT-MRAM performance at the array level. Samsung has also created unique modeling techniques that address reliability concerns such as read disturbance, write errors, and endurance limitations, providing a comprehensive framework for SOT-MRAM implementation in commercial products.

Strengths: Samsung's models excel in manufacturing-oriented parameters and variability analysis, making them highly practical for commercial deployment. Their integration with existing memory design flows accelerates adoption. Weaknesses: Their models may prioritize computational efficiency over capturing certain fundamental physical phenomena, potentially limiting accuracy in exploring novel switching mechanisms.

Critical Patents in SOT MRAM Modeling

Design of spin-orbit torque magnetic random access memory

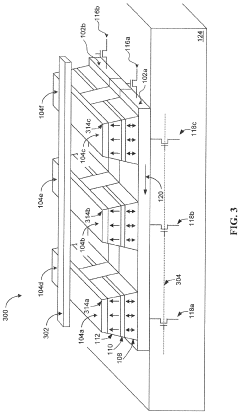

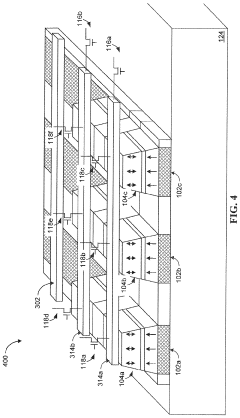

PatentWO2019106436A1

Innovation

- The use of two alternating electric currents with correlated phases in a ferromagnetic/heavy-metal bilayer, where the total current density is constant and its direction rotates, reducing the minimal reversal current density to as low as 10^8 A/m^2, allowing for magnetization reversal in a few nanoseconds with a current density of 10^9 A/m^2, which is lower than conventional schemes.

Spin-orbit torque (SOT) magnetic memory with voltage or current assisted switching

PatentActiveUS10600465B1

Innovation

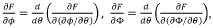

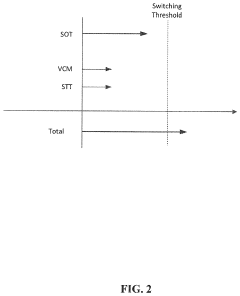

- The implementation of a magnetic storage device with a grid structure featuring SOT-MRAM devices, where a first write current provides a magnetic torque below the switching threshold and a second write current, applied along the axis of individual SOT-MRAM devices, combines with voltage-controlled magnetic anisotropy to exceed the switching threshold, allowing for precise switching of magnetic orientations while minimizing unnecessary switching in other devices.

Integration with CMOS Technology

The integration of SOT-MRAM with CMOS technology represents a critical pathway for the commercial viability of this emerging memory technology. Current CMOS fabrication processes have been optimized over decades, achieving remarkable efficiency and reliability. The incorporation of SOT-MRAM elements into these established processes requires careful consideration of material compatibility, thermal budgets, and process flow modifications.

From a materials perspective, SOT-MRAM structures typically involve heavy metals (such as Pt, Ta, or W), ferromagnetic layers, and tunnel barrier materials that are not standard in conventional CMOS processes. The deposition and patterning of these materials must be achieved without compromising the integrity of existing CMOS components. Particularly challenging is the preservation of magnetic properties during high-temperature CMOS backend processes, which can potentially degrade the performance of magnetic tunnel junctions.

Process integration schemes generally follow two approaches: MRAM-first and MRAM-last. The MRAM-first approach incorporates magnetic elements early in the fabrication sequence, potentially allowing for higher thermal budgets but requiring protection during subsequent processing steps. The MRAM-last approach adds magnetic elements after most high-temperature processes are completed, reducing thermal exposure but introducing challenges in interconnection and planarization.

Compact modeling plays a crucial role in this integration effort by providing circuit designers with accurate representations of SOT-MRAM behavior within standard electronic design automation (EDA) tools. These models must capture the unique switching dynamics of SOT-MRAM while maintaining compatibility with industry-standard SPICE-based simulation environments. The development of Verilog-A models that accurately represent SOT-induced magnetization dynamics has enabled preliminary circuit-level simulations incorporating these novel devices.

Scaling considerations present another significant challenge. As CMOS technology continues to advance toward smaller nodes (5nm and beyond), SOT-MRAM elements must similarly scale to maintain area efficiency. This scaling affects not only the physical dimensions but also the switching current densities, thermal stability, and reliability of the devices. Compact models must evolve to accurately represent these scaling effects.

Recent demonstrations by major semiconductor manufacturers have shown promising results in integrating SOT-MRAM with advanced CMOS nodes. These proof-of-concept implementations have validated the feasibility of incorporating SOT-MRAM as embedded memory in logic processes, potentially offering advantages in terms of speed, endurance, and power consumption compared to conventional embedded memories like SRAM and flash.

From a materials perspective, SOT-MRAM structures typically involve heavy metals (such as Pt, Ta, or W), ferromagnetic layers, and tunnel barrier materials that are not standard in conventional CMOS processes. The deposition and patterning of these materials must be achieved without compromising the integrity of existing CMOS components. Particularly challenging is the preservation of magnetic properties during high-temperature CMOS backend processes, which can potentially degrade the performance of magnetic tunnel junctions.

Process integration schemes generally follow two approaches: MRAM-first and MRAM-last. The MRAM-first approach incorporates magnetic elements early in the fabrication sequence, potentially allowing for higher thermal budgets but requiring protection during subsequent processing steps. The MRAM-last approach adds magnetic elements after most high-temperature processes are completed, reducing thermal exposure but introducing challenges in interconnection and planarization.

Compact modeling plays a crucial role in this integration effort by providing circuit designers with accurate representations of SOT-MRAM behavior within standard electronic design automation (EDA) tools. These models must capture the unique switching dynamics of SOT-MRAM while maintaining compatibility with industry-standard SPICE-based simulation environments. The development of Verilog-A models that accurately represent SOT-induced magnetization dynamics has enabled preliminary circuit-level simulations incorporating these novel devices.

Scaling considerations present another significant challenge. As CMOS technology continues to advance toward smaller nodes (5nm and beyond), SOT-MRAM elements must similarly scale to maintain area efficiency. This scaling affects not only the physical dimensions but also the switching current densities, thermal stability, and reliability of the devices. Compact models must evolve to accurately represent these scaling effects.

Recent demonstrations by major semiconductor manufacturers have shown promising results in integrating SOT-MRAM with advanced CMOS nodes. These proof-of-concept implementations have validated the feasibility of incorporating SOT-MRAM as embedded memory in logic processes, potentially offering advantages in terms of speed, endurance, and power consumption compared to conventional embedded memories like SRAM and flash.

Reliability and Endurance Considerations

Reliability and endurance represent critical performance metrics for SOT-MRAM technology in practical applications. Current SOT-MRAM devices demonstrate write endurance capabilities of 10^12-10^15 cycles, significantly outperforming conventional Flash memory (10^4-10^5 cycles) and approaching SRAM/DRAM levels. However, compact modeling of reliability factors remains challenging due to the complex interplay of material degradation, thermal effects, and switching variability.

The primary reliability concerns in SOT-MRAM arise from material interface degradation over repeated switching cycles. Heavy metal/ferromagnet interfaces experience atomic diffusion and structural changes that alter spin-orbit coupling efficiency. Compact models must incorporate time-dependent parameters that capture this degradation, typically through accelerated testing data fitted to modified Weibull distributions or mean-time-to-failure (MTTF) projections.

Thermal stability represents another crucial reliability factor affecting data retention. The thermal stability factor Δ (defined as E_b/k_B T, where E_b is the energy barrier) determines how long magnetic states remain stable against thermal fluctuations. For 10-year data retention, Δ values exceeding 60-80 are typically required. Compact models must account for how Δ evolves with cycling, as repeated switching events can reduce thermal stability through microstructural changes in the free layer.

Process variations introduce significant device-to-device switching variability, affecting both reliability and endurance. Statistical compact models incorporating variation-aware parameters have been developed to address this challenge. These models typically employ Monte Carlo methods with carefully calibrated parameter distributions to predict yield and failure rates across large memory arrays.

Read disturbance effects present another reliability concern, where repeated read operations may inadvertently destabilize stored data. Compact models must capture the cumulative impact of sub-threshold current pulses on magnetic stability. Recent research indicates that incorporating stochastic thermal field effects into compact models provides more accurate prediction of read disturbance failures.

Radiation hardness represents a specialized reliability consideration for aerospace and military applications. SOT-MRAM demonstrates inherent resistance to single-event upsets compared to charge-based memories, but comprehensive compact models must still account for radiation-induced parameter shifts, particularly in the heavy metal layer where spin-orbit coupling occurs.

Future compact modeling approaches are increasingly incorporating machine learning techniques to predict reliability and endurance. Neural network models trained on extensive experimental data can capture complex degradation patterns that traditional physics-based models might miss, potentially enabling more accurate lifetime predictions and adaptive error correction strategies.

The primary reliability concerns in SOT-MRAM arise from material interface degradation over repeated switching cycles. Heavy metal/ferromagnet interfaces experience atomic diffusion and structural changes that alter spin-orbit coupling efficiency. Compact models must incorporate time-dependent parameters that capture this degradation, typically through accelerated testing data fitted to modified Weibull distributions or mean-time-to-failure (MTTF) projections.

Thermal stability represents another crucial reliability factor affecting data retention. The thermal stability factor Δ (defined as E_b/k_B T, where E_b is the energy barrier) determines how long magnetic states remain stable against thermal fluctuations. For 10-year data retention, Δ values exceeding 60-80 are typically required. Compact models must account for how Δ evolves with cycling, as repeated switching events can reduce thermal stability through microstructural changes in the free layer.

Process variations introduce significant device-to-device switching variability, affecting both reliability and endurance. Statistical compact models incorporating variation-aware parameters have been developed to address this challenge. These models typically employ Monte Carlo methods with carefully calibrated parameter distributions to predict yield and failure rates across large memory arrays.

Read disturbance effects present another reliability concern, where repeated read operations may inadvertently destabilize stored data. Compact models must capture the cumulative impact of sub-threshold current pulses on magnetic stability. Recent research indicates that incorporating stochastic thermal field effects into compact models provides more accurate prediction of read disturbance failures.

Radiation hardness represents a specialized reliability consideration for aerospace and military applications. SOT-MRAM demonstrates inherent resistance to single-event upsets compared to charge-based memories, but comprehensive compact models must still account for radiation-induced parameter shifts, particularly in the heavy metal layer where spin-orbit coupling occurs.

Future compact modeling approaches are increasingly incorporating machine learning techniques to predict reliability and endurance. Neural network models trained on extensive experimental data can capture complex degradation patterns that traditional physics-based models might miss, potentially enabling more accurate lifetime predictions and adaptive error correction strategies.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!