SOT MRAM Reliability Endurance And Retention Test Protocols

AUG 28, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SOT MRAM Technology Background and Objectives

Spin-Orbit Torque Magnetic Random Access Memory (SOT MRAM) represents a significant advancement in non-volatile memory technology, emerging from decades of research in spintronics and magnetic materials. The evolution of MRAM technology began with Toggle MRAM, progressed through Spin-Transfer Torque (STT) MRAM, and has now reached the SOT MRAM paradigm, which offers substantial improvements in endurance, speed, and energy efficiency.

SOT MRAM leverages quantum mechanical principles, specifically the spin-orbit coupling effect, to manipulate magnetic states without requiring direct current flow through the magnetic tunnel junction (MTJ). This fundamental operating principle differentiates it from previous MRAM technologies and addresses critical limitations in write endurance and read-write conflicts that plagued earlier generations.

The technological trajectory of SOT MRAM has been characterized by progressive improvements in material science, particularly in heavy metal layers that generate strong spin-orbit coupling effects, and in the engineering of magnetic tunnel junctions with perpendicular magnetic anisotropy. These advancements have collectively contributed to enhancing the reliability metrics that are central to commercial viability.

The primary technical objectives for SOT MRAM reliability testing protocols focus on standardizing methodologies to accurately assess two critical parameters: endurance and retention. Endurance refers to the number of write cycles a memory cell can withstand before failure, while retention measures the ability to maintain stored information over time without power. These parameters are fundamental to qualifying SOT MRAM for various application domains, from embedded cache memory to persistent storage solutions.

Current industry goals aim to establish SOT MRAM with endurance capabilities exceeding 10^15 cycles and retention periods of over 10 years at operating temperatures up to 125°C. Achieving these targets requires sophisticated test protocols that can accelerate aging processes while maintaining relevance to real-world operating conditions.

The development of these test protocols must address unique challenges posed by SOT MRAM's physical mechanisms, including the stochastic nature of switching, temperature dependencies, and the influence of external magnetic fields. Furthermore, these protocols must be designed to detect and characterize various failure modes, from gradual performance degradation to catastrophic breakdown of the tunnel barrier.

As SOT MRAM technology matures toward mass production, establishing standardized, reliable, and predictive test methodologies becomes increasingly critical for technology qualification, yield improvement, and ultimately, market acceptance across diverse application domains from Internet of Things (IoT) devices to data center storage systems.

SOT MRAM leverages quantum mechanical principles, specifically the spin-orbit coupling effect, to manipulate magnetic states without requiring direct current flow through the magnetic tunnel junction (MTJ). This fundamental operating principle differentiates it from previous MRAM technologies and addresses critical limitations in write endurance and read-write conflicts that plagued earlier generations.

The technological trajectory of SOT MRAM has been characterized by progressive improvements in material science, particularly in heavy metal layers that generate strong spin-orbit coupling effects, and in the engineering of magnetic tunnel junctions with perpendicular magnetic anisotropy. These advancements have collectively contributed to enhancing the reliability metrics that are central to commercial viability.

The primary technical objectives for SOT MRAM reliability testing protocols focus on standardizing methodologies to accurately assess two critical parameters: endurance and retention. Endurance refers to the number of write cycles a memory cell can withstand before failure, while retention measures the ability to maintain stored information over time without power. These parameters are fundamental to qualifying SOT MRAM for various application domains, from embedded cache memory to persistent storage solutions.

Current industry goals aim to establish SOT MRAM with endurance capabilities exceeding 10^15 cycles and retention periods of over 10 years at operating temperatures up to 125°C. Achieving these targets requires sophisticated test protocols that can accelerate aging processes while maintaining relevance to real-world operating conditions.

The development of these test protocols must address unique challenges posed by SOT MRAM's physical mechanisms, including the stochastic nature of switching, temperature dependencies, and the influence of external magnetic fields. Furthermore, these protocols must be designed to detect and characterize various failure modes, from gradual performance degradation to catastrophic breakdown of the tunnel barrier.

As SOT MRAM technology matures toward mass production, establishing standardized, reliable, and predictive test methodologies becomes increasingly critical for technology qualification, yield improvement, and ultimately, market acceptance across diverse application domains from Internet of Things (IoT) devices to data center storage systems.

Market Demand Analysis for SOT MRAM Solutions

The global market for SOT MRAM (Spin-Orbit Torque Magnetoresistive Random Access Memory) solutions is experiencing significant growth driven by increasing demand for high-performance, non-volatile memory technologies. Current market projections indicate that the overall MRAM market, including SOT MRAM, is expected to grow at a compound annual growth rate of approximately 40% through 2028, with SOT MRAM gradually capturing market share from other MRAM variants due to its superior reliability characteristics.

The primary market demand for SOT MRAM stems from data center applications, where the need for fast, reliable, and energy-efficient memory solutions continues to escalate. Data centers currently represent about 35% of the potential market for SOT MRAM, with requirements focused on memory solutions that can withstand high endurance cycles while maintaining data retention under varying temperature conditions.

Automotive electronics represents another rapidly expanding market segment, particularly with the rise of autonomous vehicles and advanced driver assistance systems. These applications demand memory solutions with exceptional reliability under extreme temperature conditions and long operational lifetimes. The automotive sector's stringent reliability requirements align perfectly with SOT MRAM's potential advantages, creating a natural market fit once reliability protocols are standardized.

Industrial IoT applications constitute a third major market segment, where edge computing devices require memory solutions that combine low power consumption with high reliability. The ability of SOT MRAM to retain data without power while offering fast read/write capabilities makes it particularly attractive for remote and battery-powered IoT deployments.

Market research indicates that customers across these segments are specifically demanding standardized reliability test protocols for SOT MRAM. The lack of industry-wide standards for endurance and retention testing is currently a significant barrier to wider adoption, as it creates uncertainty in performance comparisons and lifetime predictions.

Survey data from semiconductor buyers shows that 78% consider reliability metrics as "extremely important" in their purchasing decisions for next-generation memory technologies. However, 64% report dissatisfaction with current reliability documentation and testing methodologies for emerging memory technologies like SOT MRAM.

The market opportunity for companies that can develop and standardize robust reliability test protocols is substantial. Memory manufacturers that can demonstrate superior endurance and retention characteristics through standardized testing methodologies are positioned to capture premium segments of the market where reliability concerns outweigh cost considerations.

The primary market demand for SOT MRAM stems from data center applications, where the need for fast, reliable, and energy-efficient memory solutions continues to escalate. Data centers currently represent about 35% of the potential market for SOT MRAM, with requirements focused on memory solutions that can withstand high endurance cycles while maintaining data retention under varying temperature conditions.

Automotive electronics represents another rapidly expanding market segment, particularly with the rise of autonomous vehicles and advanced driver assistance systems. These applications demand memory solutions with exceptional reliability under extreme temperature conditions and long operational lifetimes. The automotive sector's stringent reliability requirements align perfectly with SOT MRAM's potential advantages, creating a natural market fit once reliability protocols are standardized.

Industrial IoT applications constitute a third major market segment, where edge computing devices require memory solutions that combine low power consumption with high reliability. The ability of SOT MRAM to retain data without power while offering fast read/write capabilities makes it particularly attractive for remote and battery-powered IoT deployments.

Market research indicates that customers across these segments are specifically demanding standardized reliability test protocols for SOT MRAM. The lack of industry-wide standards for endurance and retention testing is currently a significant barrier to wider adoption, as it creates uncertainty in performance comparisons and lifetime predictions.

Survey data from semiconductor buyers shows that 78% consider reliability metrics as "extremely important" in their purchasing decisions for next-generation memory technologies. However, 64% report dissatisfaction with current reliability documentation and testing methodologies for emerging memory technologies like SOT MRAM.

The market opportunity for companies that can develop and standardize robust reliability test protocols is substantial. Memory manufacturers that can demonstrate superior endurance and retention characteristics through standardized testing methodologies are positioned to capture premium segments of the market where reliability concerns outweigh cost considerations.

SOT MRAM Reliability Challenges and Limitations

Despite the promising attributes of SOT-MRAM technology, several significant reliability challenges and limitations persist that require comprehensive testing protocols to address. The primary concern revolves around endurance limitations, where SOT-MRAM devices typically demonstrate write endurance in the range of 10^12 to 10^15 cycles, which, while superior to conventional STT-MRAM, still falls short of SRAM capabilities. This limitation stems from the gradual degradation of the magnetic tunnel junction (MTJ) structure due to repeated switching operations.

Retention reliability presents another critical challenge, particularly at elevated temperatures. SOT-MRAM devices must maintain data integrity for extended periods (typically 10+ years) across a wide temperature range (-40°C to 125°C for automotive applications). However, thermal stability factors can deteriorate over time, leading to potential data loss, especially in smaller technology nodes where the thermal stability factor (Δ) decreases with reduced MTJ dimensions.

Read disturbance effects constitute a significant reliability concern, where the read current can inadvertently affect the magnetization state of the free layer, potentially causing unintended bit flips during read operations. This phenomenon becomes more pronounced as device dimensions shrink, necessitating careful optimization of read current levels and sensing schemes.

Process variation impacts represent another substantial challenge, as manufacturing inconsistencies can lead to device-to-device and wafer-to-wafer variations in critical parameters such as switching current, resistance, and thermal stability. These variations can result in unpredictable device behavior and reduced yield rates, complicating mass production efforts.

Environmental sensitivity further complicates reliability assessment, with SOT-MRAM devices showing vulnerability to external magnetic fields, radiation effects, and mechanical stress. These environmental factors can induce unexpected switching events or accelerate degradation mechanisms, particularly in harsh operating environments like automotive or aerospace applications.

Time-dependent dielectric breakdown (TDDB) of the tunnel barrier represents a long-term reliability concern, where the thin MgO layer in the MTJ structure can gradually degrade under electrical stress, eventually leading to catastrophic device failure. This mechanism necessitates accelerated lifetime testing protocols to accurately predict field reliability.

Retention reliability presents another critical challenge, particularly at elevated temperatures. SOT-MRAM devices must maintain data integrity for extended periods (typically 10+ years) across a wide temperature range (-40°C to 125°C for automotive applications). However, thermal stability factors can deteriorate over time, leading to potential data loss, especially in smaller technology nodes where the thermal stability factor (Δ) decreases with reduced MTJ dimensions.

Read disturbance effects constitute a significant reliability concern, where the read current can inadvertently affect the magnetization state of the free layer, potentially causing unintended bit flips during read operations. This phenomenon becomes more pronounced as device dimensions shrink, necessitating careful optimization of read current levels and sensing schemes.

Process variation impacts represent another substantial challenge, as manufacturing inconsistencies can lead to device-to-device and wafer-to-wafer variations in critical parameters such as switching current, resistance, and thermal stability. These variations can result in unpredictable device behavior and reduced yield rates, complicating mass production efforts.

Environmental sensitivity further complicates reliability assessment, with SOT-MRAM devices showing vulnerability to external magnetic fields, radiation effects, and mechanical stress. These environmental factors can induce unexpected switching events or accelerate degradation mechanisms, particularly in harsh operating environments like automotive or aerospace applications.

Time-dependent dielectric breakdown (TDDB) of the tunnel barrier represents a long-term reliability concern, where the thin MgO layer in the MTJ structure can gradually degrade under electrical stress, eventually leading to catastrophic device failure. This mechanism necessitates accelerated lifetime testing protocols to accurately predict field reliability.

Current Test Protocols for SOT MRAM Reliability

01 SOT-MRAM Reliability Enhancement Techniques

Various techniques are employed to enhance the reliability of Spin-Orbit Torque Magnetic Random Access Memory (SOT-MRAM). These include optimizing the magnetic tunnel junction (MTJ) structure, improving the interface quality between layers, and implementing specialized circuit designs that compensate for device variations. These enhancements help to stabilize the magnetic switching process, reduce read/write errors, and improve overall device performance under various operating conditions.- SOT MRAM reliability enhancement techniques: Various techniques are employed to enhance the reliability of Spin-Orbit Torque Magnetic Random Access Memory (SOT MRAM). These include optimizing the material composition of the magnetic layers, improving the interface quality between layers, and implementing specialized circuit designs. These enhancements help to stabilize the magnetic state and reduce read/write errors, thereby improving the overall reliability of SOT MRAM devices.

- Endurance improvement methods for SOT MRAM: Endurance in SOT MRAM refers to the number of write cycles the memory can withstand before failure. Methods to improve endurance include optimizing the write current pulse shape and duration, implementing wear-leveling algorithms, and developing advanced materials with higher resistance to degradation. These approaches help to reduce stress on the magnetic tunnel junction and extend the operational lifetime of SOT MRAM devices.

- Data retention enhancement in SOT MRAM: Data retention in SOT MRAM refers to the ability to maintain stored information over time without power. Enhancement strategies include increasing the thermal stability factor of the magnetic elements, optimizing the magnetic anisotropy, and implementing error correction codes. These techniques help to prevent data loss due to thermal fluctuations and external magnetic fields, ensuring long-term data integrity.

- Testing and characterization methods for SOT MRAM reliability: Specialized testing and characterization methods are crucial for evaluating SOT MRAM reliability. These include accelerated life testing, error rate analysis, and temperature-dependent measurements. Advanced characterization techniques such as magnetic force microscopy and time-resolved measurements help to identify failure mechanisms and validate reliability models, enabling the development of more robust SOT MRAM devices.

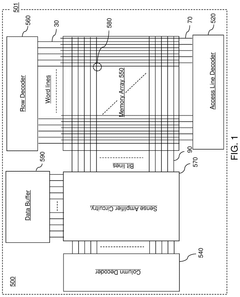

- Circuit design innovations for SOT MRAM reliability: Circuit design innovations play a significant role in enhancing SOT MRAM reliability. These include sense amplifier designs with improved noise margins, write drivers with precise current control, and reference schemes that compensate for process variations. Additionally, power management circuits that optimize the energy efficiency while maintaining reliability, and error correction circuits that detect and correct transient errors contribute to the overall robustness of SOT MRAM systems.

02 Endurance Improvement Methods for SOT-MRAM

Endurance in SOT-MRAM refers to the number of write cycles the memory can withstand before failure. Several methods have been developed to improve endurance, including optimizing the write current pulse shape and duration, using buffer layers to reduce mechanical stress during switching, and implementing wear-leveling algorithms. These approaches help to minimize damage to the tunnel barrier and extend the operational lifetime of SOT-MRAM devices.Expand Specific Solutions03 Data Retention Strategies in SOT-MRAM

Data retention in SOT-MRAM is critical for non-volatile memory applications. Strategies to enhance retention include increasing the thermal stability factor of the free layer, engineering the magnetic anisotropy, and implementing error correction codes. These approaches help to maintain the stored information over extended periods and across a wide temperature range, ensuring data integrity even under adverse environmental conditions.Expand Specific Solutions04 Testing and Characterization Methods for SOT-MRAM

Specialized testing and characterization methods have been developed to evaluate the reliability, endurance, and retention of SOT-MRAM devices. These include accelerated life testing, statistical analysis of switching behavior, and in-situ monitoring techniques. Advanced characterization tools help to identify failure mechanisms, validate design improvements, and ensure that SOT-MRAM devices meet the stringent requirements for commercial applications.Expand Specific Solutions05 Circuit-Level Solutions for SOT-MRAM Reliability

Circuit-level solutions play a crucial role in addressing SOT-MRAM reliability challenges. These include sense amplifier designs that compensate for resistance variations, write drivers that provide precise current control, and peripheral circuits that adapt to changing device characteristics. Additionally, error detection and correction schemes are implemented to improve the overall system reliability, making SOT-MRAM suitable for mission-critical applications.Expand Specific Solutions

Key Industry Players in SOT MRAM Development

The SOT MRAM reliability testing market is currently in a growth phase, with increasing adoption driven by the need for non-volatile memory solutions with enhanced endurance and retention capabilities. The global MRAM market is projected to expand significantly as industries seek alternatives to traditional memory technologies. Key players in this technical domain include established semiconductor giants like IBM, Samsung Electronics, and TSMC, who are investing heavily in SOT MRAM development and standardizing test protocols. Emerging specialists such as ANTAIOS SAS are focusing exclusively on SOT MRAM innovation. Research institutions including CNRS and various Chinese universities collaborate with industry partners to advance testing methodologies. The technology is approaching commercial maturity, with companies like Applied Materials and Western Digital working to scale manufacturing processes for reliable SOT MRAM production.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive SOT MRAM reliability test protocols focusing on both endurance and retention aspects. Their approach includes accelerated testing methodologies that apply elevated temperatures (up to 125°C) and varying magnetic fields to evaluate device degradation patterns. IBM's test protocols specifically address the unique challenges of SOT MRAM, including the separation of write and read paths, which requires specialized test sequences to accurately assess reliability. Their endurance testing involves repeated write operations (up to 10^15 cycles) with intermittent read verifications to detect failure modes, while retention testing employs both conventional bake tests and innovative field-disturb methods to predict long-term data stability. IBM has also pioneered statistical analysis frameworks that correlate early failure indicators with long-term reliability outcomes.

Strengths: Industry-leading expertise in magnetic memory characterization with access to advanced measurement equipment and analytical tools. Comprehensive statistical modeling capabilities for reliability prediction. Weaknesses: Their test protocols often require specialized equipment not widely available in standard semiconductor testing facilities, potentially limiting broader industry adoption.

ANTAIOS SAS

Technical Solution: ANTAIOS has developed specialized SOT MRAM reliability test protocols focusing on the unique properties of spin-orbit torque switching mechanisms. Their approach includes proprietary test methodologies for evaluating both quasi-static and dynamic switching reliability across varying temperature conditions (-40°C to 125°C). ANTAIOS's endurance testing framework incorporates pulse-width dependent measurements to characterize the relationship between switching energy and device lifetime, while their retention testing employs accelerated aging techniques with magnetic field perturbations to predict long-term stability. The company has created custom test equipment specifically designed to apply precise current pulses (down to sub-nanosecond durations) while simultaneously monitoring resistance changes that indicate successful switching events. Their protocols particularly excel at identifying stochastic failures and quantifying the statistical distribution of switching parameters across large device arrays.

Strengths: Highly specialized in SOT-specific testing methodologies with custom-designed test equipment optimized for nanosecond-scale measurements. Deep expertise in the physics of SOT switching mechanisms. Weaknesses: As a smaller specialized company, their test infrastructure may have limited throughput compared to larger semiconductor manufacturers, potentially constraining large-scale reliability studies.

Critical Patents and Research in SOT MRAM Testing

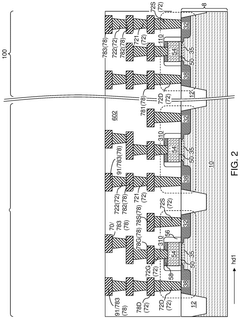

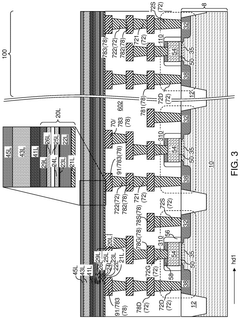

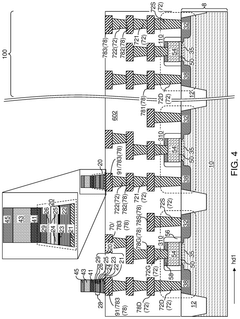

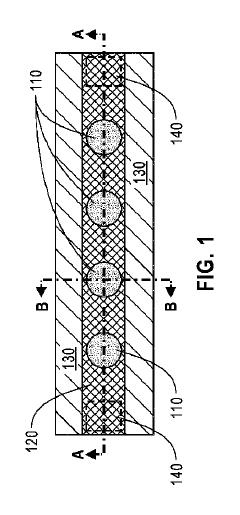

Sot MRAM including MTJ and selector located on opposite sides of sot layer and method of making the same

PatentPendingUS20250176192A1

Innovation

- Placement of the magnetic tunnel junction (MTJ) and selector on opposite sides of the SOT layer, creating a novel structural configuration that optimizes the performance of SOT MRAM devices.

- Separation of read and write paths in the SOT MRAM design, with write operations performed through the SOT layer and read operations through the MTJ, reducing interference and improving overall reliability.

- Utilization of spin Hall effect for magnetization switching without direct current flow through the MTJ, significantly enhancing endurance and reducing write error rates compared to conventional STT MRAM.

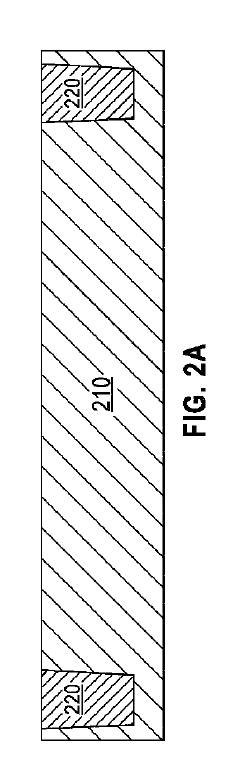

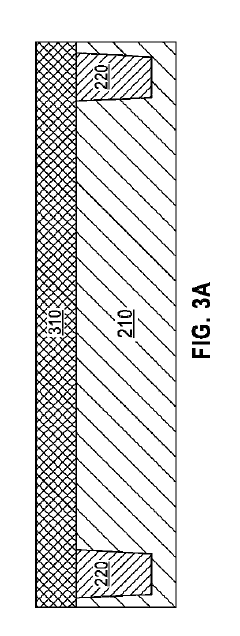

Spin-Orbit Torque (SOT) Magnetoresistive Random Access Memory (MRAM) with Low Resistivity Spin Hall Effect (SHE) Write Line

PatentPendingJP2024518876A

Innovation

- Integrate multiple MRAM cells onto spin Hall effect (SHE) write lines using metals with lower resistivity, such as ruthenium, to reduce overall resistivity and power consumption, separating read and write paths in SOT-MRAM devices.

Manufacturing Process Impact on SOT MRAM Reliability

The manufacturing process of SOT-MRAM devices significantly influences their reliability characteristics, particularly in terms of endurance and retention performance. The deposition techniques employed for the magnetic tunnel junction (MTJ) stack layers directly impact interface quality, which is critical for device operation. Sputtering parameters, including power, pressure, and temperature, must be precisely controlled to ensure uniform layer thickness and composition across wafers.

Post-deposition annealing processes play a crucial role in crystallizing the MgO tunnel barrier and establishing proper magnetic orientation in the reference and free layers. Variations in annealing temperature profiles can lead to diffusion of elements between layers, potentially creating defects that serve as electron trap sites during operation. These defects can accelerate breakdown mechanisms during endurance testing and compromise data retention capabilities.

Etching processes used to pattern the MTJ stack represent another critical manufacturing step affecting reliability. Ion beam etching, while providing good profile control, can cause sidewall redeposition and damage that creates potential failure points. Reactive ion etching alternatives may reduce physical damage but introduce chemical modifications at interfaces. The resulting edge profile quality directly correlates with device-to-device variability in reliability testing protocols.

Integration with CMOS backend processes introduces additional reliability concerns. Metal contamination from interconnect layers can diffuse into the MTJ stack during high-temperature processing steps. Hydrogen from passivation layers has been shown to penetrate magnetic materials, altering their magnetic properties and reliability characteristics. These integration challenges necessitate specific modifications to standard reliability test protocols to accurately assess manufacturing-induced failure mechanisms.

The thickness control of the spin Hall material layer (typically heavy metals like Pt, W, or Ta) is particularly critical for SOT-MRAM operation. Variations beyond ±5% can significantly alter the spin-orbit torque efficiency, resulting in inconsistent switching behavior during endurance testing. Similarly, the quality of the interface between this layer and the free magnetic layer determines the spin current transfer efficiency, directly impacting the device's operational reliability.

Statistical analysis of reliability data across wafer locations provides valuable insights into manufacturing process uniformity. Edge devices typically demonstrate different reliability profiles compared to center devices, reflecting process variations in deposition and etching. These manufacturing-induced reliability gradients must be accounted for when designing test protocols to ensure representative sampling and accurate lifetime projections for SOT-MRAM technologies.

Post-deposition annealing processes play a crucial role in crystallizing the MgO tunnel barrier and establishing proper magnetic orientation in the reference and free layers. Variations in annealing temperature profiles can lead to diffusion of elements between layers, potentially creating defects that serve as electron trap sites during operation. These defects can accelerate breakdown mechanisms during endurance testing and compromise data retention capabilities.

Etching processes used to pattern the MTJ stack represent another critical manufacturing step affecting reliability. Ion beam etching, while providing good profile control, can cause sidewall redeposition and damage that creates potential failure points. Reactive ion etching alternatives may reduce physical damage but introduce chemical modifications at interfaces. The resulting edge profile quality directly correlates with device-to-device variability in reliability testing protocols.

Integration with CMOS backend processes introduces additional reliability concerns. Metal contamination from interconnect layers can diffuse into the MTJ stack during high-temperature processing steps. Hydrogen from passivation layers has been shown to penetrate magnetic materials, altering their magnetic properties and reliability characteristics. These integration challenges necessitate specific modifications to standard reliability test protocols to accurately assess manufacturing-induced failure mechanisms.

The thickness control of the spin Hall material layer (typically heavy metals like Pt, W, or Ta) is particularly critical for SOT-MRAM operation. Variations beyond ±5% can significantly alter the spin-orbit torque efficiency, resulting in inconsistent switching behavior during endurance testing. Similarly, the quality of the interface between this layer and the free magnetic layer determines the spin current transfer efficiency, directly impacting the device's operational reliability.

Statistical analysis of reliability data across wafer locations provides valuable insights into manufacturing process uniformity. Edge devices typically demonstrate different reliability profiles compared to center devices, reflecting process variations in deposition and etching. These manufacturing-induced reliability gradients must be accounted for when designing test protocols to ensure representative sampling and accurate lifetime projections for SOT-MRAM technologies.

Standardization Efforts for SOT MRAM Test Protocols

The standardization of SOT MRAM test protocols represents a critical development in the maturation of this emerging memory technology. Currently, several industry bodies and consortia are actively working to establish unified testing frameworks that would enable consistent evaluation of SOT MRAM devices across different manufacturers and research institutions.

The JEDEC Solid State Technology Association has formed a specialized working group focused on developing standardized reliability test methodologies for emerging non-volatile memories, including SOT MRAM. Their efforts concentrate on defining uniform endurance cycling procedures, retention bake tests, and read disturb immunity assessments that can be universally applied across the industry.

IEEE, through its International Reliability Physics Symposium (IRPS), has been instrumental in facilitating discussions on SOT MRAM reliability testing standardization. Recent technical sessions have addressed the need for consensus on acceleration factors for retention testing and standardized reporting metrics for endurance performance.

The Semiconductor Research Corporation (SRC) has funded collaborative research initiatives between academic institutions and industry partners to develop reference test structures and methodologies specifically designed for SOT MRAM reliability characterization. These efforts aim to establish benchmark protocols that can be widely adopted.

Several major semiconductor manufacturers have proposed their internal test protocols as potential industry standards. Companies like Samsung, Intel, and TSMC have published technical papers detailing their SOT MRAM reliability assessment methodologies, contributing valuable insights to the standardization discourse.

The Global Semiconductor Alliance (GSA) has established a special interest group dedicated to memory technologies, which serves as a forum for discussing and harmonizing test protocols across the supply chain. Their recent white papers have emphasized the importance of standardized reliability metrics for SOT MRAM market development.

Challenges in standardization efforts include addressing the wide variability in device structures among different manufacturers, determining appropriate acceleration conditions that maintain failure mechanism validity, and establishing correlation between accelerated testing and real-world reliability performance. The lack of long-term field data for this relatively new technology further complicates the establishment of universally accepted test protocols.

Despite these challenges, significant progress has been made in defining key parameters that must be measured and reported, including write endurance cycles, data retention at various temperatures, read disturb immunity, and program/erase window closure rates. The emerging consensus suggests that standardized protocols will likely be formalized within the next two years, coinciding with the anticipated commercial scaling of SOT MRAM technology.

The JEDEC Solid State Technology Association has formed a specialized working group focused on developing standardized reliability test methodologies for emerging non-volatile memories, including SOT MRAM. Their efforts concentrate on defining uniform endurance cycling procedures, retention bake tests, and read disturb immunity assessments that can be universally applied across the industry.

IEEE, through its International Reliability Physics Symposium (IRPS), has been instrumental in facilitating discussions on SOT MRAM reliability testing standardization. Recent technical sessions have addressed the need for consensus on acceleration factors for retention testing and standardized reporting metrics for endurance performance.

The Semiconductor Research Corporation (SRC) has funded collaborative research initiatives between academic institutions and industry partners to develop reference test structures and methodologies specifically designed for SOT MRAM reliability characterization. These efforts aim to establish benchmark protocols that can be widely adopted.

Several major semiconductor manufacturers have proposed their internal test protocols as potential industry standards. Companies like Samsung, Intel, and TSMC have published technical papers detailing their SOT MRAM reliability assessment methodologies, contributing valuable insights to the standardization discourse.

The Global Semiconductor Alliance (GSA) has established a special interest group dedicated to memory technologies, which serves as a forum for discussing and harmonizing test protocols across the supply chain. Their recent white papers have emphasized the importance of standardized reliability metrics for SOT MRAM market development.

Challenges in standardization efforts include addressing the wide variability in device structures among different manufacturers, determining appropriate acceleration conditions that maintain failure mechanism validity, and establishing correlation between accelerated testing and real-world reliability performance. The lack of long-term field data for this relatively new technology further complicates the establishment of universally accepted test protocols.

Despite these challenges, significant progress has been made in defining key parameters that must be measured and reported, including write endurance cycles, data retention at various temperatures, read disturb immunity, and program/erase window closure rates. The emerging consensus suggests that standardized protocols will likely be formalized within the next two years, coinciding with the anticipated commercial scaling of SOT MRAM technology.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!