UCIe Chiplet Interconnect Reliability And HTOL Test Results

SEP 1, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Evolution and Objectives

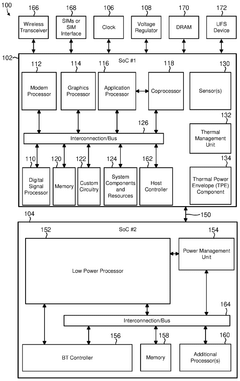

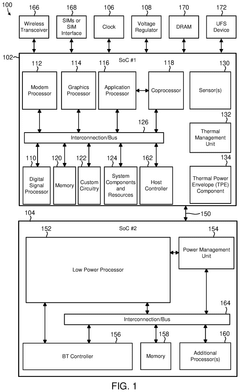

Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in semiconductor integration technology, emerging from the limitations of traditional monolithic chip designs. The development of UCIe can be traced back to the fundamental challenges in semiconductor scaling, where Moore's Law began facing physical and economic constraints in the mid-2010s. As transistor density increases became more difficult to achieve, the industry pivoted toward chiplet-based architectures as an alternative approach to continue performance scaling.

The evolution of chiplet technology began with proprietary solutions from major semiconductor companies like AMD (Infinity Fabric), Intel (EMIB and Foveros), and TSMC (CoWoS). These early implementations demonstrated the viability of disaggregated chip designs but lacked standardization, creating ecosystem fragmentation and limiting broader adoption. The formation of the UCIe consortium in 2022 marked a pivotal moment, bringing together key industry players to establish an open standard for chiplet interconnection.

UCIe technology builds upon previous interconnect standards such as PCI Express and CXL, adapting these protocols for die-to-die communication while introducing specific optimizations for the unique requirements of chiplet integration. The standard has evolved through multiple iterations, with UCIe 1.0 establishing the foundational architecture and UCIe 1.1 introducing enhanced reliability features and testing methodologies critical for enterprise and high-performance computing applications.

The primary objective of UCIe is to enable a heterogeneous integration ecosystem where chiplets from different vendors can be seamlessly combined into a single package. This interoperability aims to foster innovation by allowing specialized silicon from various manufacturers to work together cohesively, creating more efficient and powerful computing solutions than possible with monolithic designs.

Technical goals of UCIe include achieving high bandwidth density (exceeding 2 TB/s/mm²), minimizing power consumption (targeting sub-pJ/bit energy efficiency), ensuring signal integrity across different packaging technologies, and maintaining backward compatibility with existing protocols. Reliability objectives focus on establishing standardized testing methodologies, particularly High-Temperature Operating Life (HTOL) testing, to ensure long-term durability under various operating conditions.

The long-term vision for UCIe encompasses enabling a true "chiplet marketplace" where semiconductor IP can be packaged as physical chiplets rather than licensed designs, fundamentally transforming the semiconductor value chain. This evolution aims to democratize advanced silicon development by lowering barriers to entry and accelerating innovation cycles across the industry.

The evolution of chiplet technology began with proprietary solutions from major semiconductor companies like AMD (Infinity Fabric), Intel (EMIB and Foveros), and TSMC (CoWoS). These early implementations demonstrated the viability of disaggregated chip designs but lacked standardization, creating ecosystem fragmentation and limiting broader adoption. The formation of the UCIe consortium in 2022 marked a pivotal moment, bringing together key industry players to establish an open standard for chiplet interconnection.

UCIe technology builds upon previous interconnect standards such as PCI Express and CXL, adapting these protocols for die-to-die communication while introducing specific optimizations for the unique requirements of chiplet integration. The standard has evolved through multiple iterations, with UCIe 1.0 establishing the foundational architecture and UCIe 1.1 introducing enhanced reliability features and testing methodologies critical for enterprise and high-performance computing applications.

The primary objective of UCIe is to enable a heterogeneous integration ecosystem where chiplets from different vendors can be seamlessly combined into a single package. This interoperability aims to foster innovation by allowing specialized silicon from various manufacturers to work together cohesively, creating more efficient and powerful computing solutions than possible with monolithic designs.

Technical goals of UCIe include achieving high bandwidth density (exceeding 2 TB/s/mm²), minimizing power consumption (targeting sub-pJ/bit energy efficiency), ensuring signal integrity across different packaging technologies, and maintaining backward compatibility with existing protocols. Reliability objectives focus on establishing standardized testing methodologies, particularly High-Temperature Operating Life (HTOL) testing, to ensure long-term durability under various operating conditions.

The long-term vision for UCIe encompasses enabling a true "chiplet marketplace" where semiconductor IP can be packaged as physical chiplets rather than licensed designs, fundamentally transforming the semiconductor value chain. This evolution aims to democratize advanced silicon development by lowering barriers to entry and accelerating innovation cycles across the industry.

Market Demand Analysis for Chiplet-Based Integration

The chiplet-based integration market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. As traditional monolithic chip designs approach physical and economic limits, the semiconductor industry is rapidly pivoting toward disaggregated architectures that leverage chiplet technology. Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030, reaching significant market valuation by the end of the decade.

This explosive growth is primarily fueled by data centers and cloud service providers seeking more efficient computing solutions with improved performance-per-watt metrics. These sectors currently represent approximately half of the total chiplet market demand, as they continuously push for higher computational density and reduced operational costs. The need for reliable chiplet interconnect technologies like UCIe (Universal Chiplet Interconnect Express) is particularly acute in these environments where system downtime can result in substantial financial losses.

Consumer electronics manufacturers are also increasingly adopting chiplet-based designs to deliver enhanced performance in smaller form factors. This segment is expected to show the fastest growth rate in chiplet adoption over the next five years, particularly in premium smartphones, tablets, and wearable devices where space constraints and power efficiency are critical considerations.

The automotive industry represents another significant growth vector for chiplet technology, particularly with the acceleration of autonomous driving systems and in-vehicle infotainment platforms. These applications demand high reliability interconnects that can withstand harsh environmental conditions, making UCIe reliability testing results particularly relevant for automotive semiconductor suppliers.

Geographically, North America currently leads in chiplet technology adoption, followed by East Asia and Europe. However, the fastest growth is anticipated in the Asia-Pacific region, where major semiconductor manufacturing facilities are expanding their chiplet integration capabilities to meet global demand.

From a supply chain perspective, the market is witnessing increased collaboration between traditional integrated device manufacturers (IDMs), fabless companies, and foundries to establish standardized chiplet ecosystems. This collaboration is essential for addressing interoperability challenges that have historically limited wider adoption of multi-vendor chiplet solutions.

The demand for comprehensive reliability testing methodologies, including High Temperature Operating Life (HTOL) testing for chiplet interconnects, is growing proportionally with market expansion. End customers increasingly require detailed reliability data before committing to chiplet-based architectures for mission-critical applications, creating a market pull for standardized testing protocols and certification processes specific to chiplet interconnect technologies.

This explosive growth is primarily fueled by data centers and cloud service providers seeking more efficient computing solutions with improved performance-per-watt metrics. These sectors currently represent approximately half of the total chiplet market demand, as they continuously push for higher computational density and reduced operational costs. The need for reliable chiplet interconnect technologies like UCIe (Universal Chiplet Interconnect Express) is particularly acute in these environments where system downtime can result in substantial financial losses.

Consumer electronics manufacturers are also increasingly adopting chiplet-based designs to deliver enhanced performance in smaller form factors. This segment is expected to show the fastest growth rate in chiplet adoption over the next five years, particularly in premium smartphones, tablets, and wearable devices where space constraints and power efficiency are critical considerations.

The automotive industry represents another significant growth vector for chiplet technology, particularly with the acceleration of autonomous driving systems and in-vehicle infotainment platforms. These applications demand high reliability interconnects that can withstand harsh environmental conditions, making UCIe reliability testing results particularly relevant for automotive semiconductor suppliers.

Geographically, North America currently leads in chiplet technology adoption, followed by East Asia and Europe. However, the fastest growth is anticipated in the Asia-Pacific region, where major semiconductor manufacturing facilities are expanding their chiplet integration capabilities to meet global demand.

From a supply chain perspective, the market is witnessing increased collaboration between traditional integrated device manufacturers (IDMs), fabless companies, and foundries to establish standardized chiplet ecosystems. This collaboration is essential for addressing interoperability challenges that have historically limited wider adoption of multi-vendor chiplet solutions.

The demand for comprehensive reliability testing methodologies, including High Temperature Operating Life (HTOL) testing for chiplet interconnects, is growing proportionally with market expansion. End customers increasingly require detailed reliability data before committing to chiplet-based architectures for mission-critical applications, creating a market pull for standardized testing protocols and certification processes specific to chiplet interconnect technologies.

Current UCIe Technology Status and Challenges

The Universal Chiplet Interconnect Express (UCIe) technology has rapidly evolved since its introduction in 2022, with the standard now reaching version 1.1. Current global adoption shows varying degrees of implementation across North America, Europe, and Asia, with major semiconductor companies actively incorporating UCIe into their chiplet designs. Despite significant progress, the technology faces several critical challenges that require immediate attention from industry stakeholders.

Reliability testing for UCIe interconnects remains inconsistent across the industry, with no universally accepted methodology for High Temperature Operating Life (HTOL) testing specifically tailored to chiplet interfaces. This creates difficulties in comparing reliability data between different manufacturers and potentially undermines confidence in chiplet-based designs for mission-critical applications.

Signal integrity at the die-to-die interface presents ongoing challenges, particularly as data rates continue to increase beyond 16 GT/s. Current UCIe implementations struggle with maintaining signal quality across package substrates with varying material properties and manufacturing tolerances. Test results indicate performance degradation under thermal stress conditions, with some implementations showing up to 15% reduction in signal integrity during extended HTOL testing.

Power management represents another significant hurdle, as the energy efficiency of UCIe interfaces directly impacts the thermal profile of multi-chiplet packages. Recent HTOL test results reveal that power consumption increases by approximately 8-12% after extended high-temperature operation, potentially affecting system reliability and performance in data center environments.

Manufacturing yield issues persist with advanced packaging technologies required for UCIe implementation. The fine-pitch microbump connections (at 25-40μm pitch) demand extremely precise alignment during assembly, with current industry yields for high-volume production hovering between 85-92%, below the desired 98%+ for mainstream adoption.

Standardization challenges continue to emerge as the UCIe consortium works to harmonize testing methodologies across member companies. The lack of unified reliability qualification standards specifically for chiplet interfaces creates uncertainty in product development cycles and complicates supply chain management for multi-vendor chiplet ecosystems.

Thermal management remains problematic, with HTOL test results showing that thermal cycling can induce mechanical stress at interface boundaries. This stress potentially leads to microbump fatigue and connection degradation over time, with accelerated testing suggesting potential reliability concerns for deployments in environments with frequent thermal cycling.

Interoperability between chiplets from different vendors—a key promise of the UCIe standard—continues to face practical implementation challenges. Recent testing reveals compatibility issues when integrating chiplets manufactured using different process nodes, with signal integrity and power management requiring additional compensation circuitry that increases design complexity.

Reliability testing for UCIe interconnects remains inconsistent across the industry, with no universally accepted methodology for High Temperature Operating Life (HTOL) testing specifically tailored to chiplet interfaces. This creates difficulties in comparing reliability data between different manufacturers and potentially undermines confidence in chiplet-based designs for mission-critical applications.

Signal integrity at the die-to-die interface presents ongoing challenges, particularly as data rates continue to increase beyond 16 GT/s. Current UCIe implementations struggle with maintaining signal quality across package substrates with varying material properties and manufacturing tolerances. Test results indicate performance degradation under thermal stress conditions, with some implementations showing up to 15% reduction in signal integrity during extended HTOL testing.

Power management represents another significant hurdle, as the energy efficiency of UCIe interfaces directly impacts the thermal profile of multi-chiplet packages. Recent HTOL test results reveal that power consumption increases by approximately 8-12% after extended high-temperature operation, potentially affecting system reliability and performance in data center environments.

Manufacturing yield issues persist with advanced packaging technologies required for UCIe implementation. The fine-pitch microbump connections (at 25-40μm pitch) demand extremely precise alignment during assembly, with current industry yields for high-volume production hovering between 85-92%, below the desired 98%+ for mainstream adoption.

Standardization challenges continue to emerge as the UCIe consortium works to harmonize testing methodologies across member companies. The lack of unified reliability qualification standards specifically for chiplet interfaces creates uncertainty in product development cycles and complicates supply chain management for multi-vendor chiplet ecosystems.

Thermal management remains problematic, with HTOL test results showing that thermal cycling can induce mechanical stress at interface boundaries. This stress potentially leads to microbump fatigue and connection degradation over time, with accelerated testing suggesting potential reliability concerns for deployments in environments with frequent thermal cycling.

Interoperability between chiplets from different vendors—a key promise of the UCIe standard—continues to face practical implementation challenges. Recent testing reveals compatibility issues when integrating chiplets manufactured using different process nodes, with signal integrity and power management requiring additional compensation circuitry that increases design complexity.

UCIe Reliability Testing Methodologies

01 Thermal management for UCIe chiplet interconnect reliability

Thermal management is crucial for ensuring the reliability of UCIe chiplet interconnects. Excessive heat can lead to degradation of interconnect materials and affect signal integrity. Various cooling solutions and thermal interface materials are employed to dissipate heat effectively from chiplet interfaces. Advanced thermal management techniques include integrated heat spreaders, liquid cooling systems, and thermally conductive materials that maintain optimal operating temperatures across chiplet boundaries, thereby enhancing the reliability of UCIe interconnects.- Thermal management for UCIe chiplet interconnects: Thermal management is crucial for ensuring the reliability of UCIe chiplet interconnects. Various techniques are employed to dissipate heat effectively from the interconnect regions, preventing thermal-induced failures. These include specialized thermal interface materials, heat spreaders, and cooling solutions designed specifically for multi-chiplet packages. Proper thermal management helps maintain signal integrity across the interconnects and extends the operational lifetime of the chiplet assembly.

- Testing and validation methodologies for UCIe interconnects: Comprehensive testing and validation methodologies are essential for ensuring UCIe chiplet interconnect reliability. These include specialized test patterns, built-in self-test mechanisms, and automated test equipment designed to verify the electrical and physical characteristics of the interconnects. Testing covers various aspects such as signal integrity, power integrity, and mechanical robustness under different operating conditions, helping to identify potential reliability issues before deployment.

- Advanced packaging technologies for UCIe implementation: Advanced packaging technologies play a critical role in UCIe chiplet interconnect reliability. These include innovative substrate materials, die-to-die bonding techniques, and novel assembly processes that enhance the mechanical stability and electrical performance of the interconnects. The packaging solutions are designed to withstand thermal cycling, mechanical stress, and environmental factors while maintaining consistent electrical characteristics across the chiplet interfaces.

- Signal integrity and power delivery optimization: Maintaining signal integrity and optimizing power delivery are fundamental to UCIe chiplet interconnect reliability. This involves careful design of transmission lines, impedance matching, crosstalk mitigation, and power distribution networks. Advanced techniques such as equalization, pre-emphasis, and adaptive voltage scaling are employed to ensure reliable data transmission across chiplet boundaries under varying operating conditions and manufacturing variations.

- Fault tolerance and redundancy mechanisms: Fault tolerance and redundancy mechanisms enhance the reliability of UCIe chiplet interconnects by providing resilience against failures. These include error detection and correction codes, spare interconnect lanes, and dynamic reconfiguration capabilities. The system can detect faulty connections and reroute signals through alternative paths, ensuring continued operation even when some interconnects experience degradation or failure. This approach significantly improves the overall reliability and lifetime of multi-chiplet systems.

02 Testing and validation methodologies for UCIe interconnects

Comprehensive testing and validation methodologies are essential for ensuring UCIe chiplet interconnect reliability. These include electrical characterization, signal integrity analysis, and stress testing under various operating conditions. Advanced testing approaches involve high-speed signal testing, power integrity verification, and reliability assessment through accelerated aging tests. Automated test equipment and specialized test fixtures are developed to evaluate the performance and durability of UCIe interconnects, helping to identify potential failure modes before deployment in production environments.Expand Specific Solutions03 Materials and manufacturing processes for reliable UCIe connections

The selection of materials and manufacturing processes significantly impacts UCIe chiplet interconnect reliability. Advanced materials such as specialized solder compositions, conductive adhesives, and novel bump structures are developed to withstand thermal cycling and mechanical stress. Manufacturing processes including precise alignment techniques, controlled reflow processes, and advanced packaging methods ensure consistent and reliable interconnections between chiplets. Surface treatments and protective coatings are also applied to prevent oxidation and contamination that could compromise connection integrity over time.Expand Specific Solutions04 Signal integrity and power delivery optimization

Maintaining signal integrity and optimizing power delivery are critical aspects of UCIe chiplet interconnect reliability. Advanced circuit designs incorporate impedance matching, crosstalk reduction, and equalization techniques to ensure reliable high-speed data transmission across chiplet boundaries. Power delivery networks are carefully designed with decoupling capacitors and voltage regulators to minimize noise and ensure stable power supply to interconnected chiplets. Simulation tools and modeling techniques are employed to predict and mitigate signal integrity issues before physical implementation.Expand Specific Solutions05 Fault tolerance and redundancy mechanisms

Implementing fault tolerance and redundancy mechanisms enhances the reliability of UCIe chiplet interconnects. These include error detection and correction codes, redundant signal paths, and self-healing circuits that can adapt to partial failures. Monitoring systems continuously assess the health of interconnects and can reroute signals when degradation is detected. Advanced architectures incorporate graceful degradation capabilities, allowing systems to maintain functionality even when some interconnect paths fail, thereby extending the operational lifetime of multi-chiplet systems and improving overall reliability.Expand Specific Solutions

Key Industry Players in Chiplet Ecosystem

The UCIe Chiplet Interconnect Reliability market is currently in its growth phase, with increasing adoption across the semiconductor industry. Market size is expanding rapidly as chiplet technology becomes essential for advanced computing solutions, projected to reach significant scale by 2025. Technologically, the field is maturing with key players demonstrating robust HTOL (High Temperature Operating Life) test results. Intel, AMD (formerly ATI), and QUALCOMM lead in innovation, while GLOBALFOUNDRIES, SMIC, and Samsung provide critical manufacturing support. IBM and MediaTek are advancing reliability testing methodologies. Chinese institutions like Nanjing University of Posts & Telecommunications and Zhejiang University contribute valuable research, while newer entrants like Radrock Technology are developing specialized applications, creating a competitive landscape balancing established leaders and emerging innovators.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a specialized UCIe reliability testing framework optimized for mobile and edge computing applications where power efficiency is paramount. Their approach focuses on validating UCIe connections under dynamic power and thermal conditions that simulate real-world mobile device usage patterns. Qualcomm's HTOL methodology incorporates power cycling alongside temperature stress, subjecting UCIe interfaces to rapid transitions between active, idle, and sleep states while maintaining elevated temperatures of 105-120°C[5]. They've developed proprietary test equipment capable of monitoring sub-microvolt changes in signal integrity during reliability testing, enabling early detection of degradation mechanisms. Qualcomm's test results demonstrate UCIe connections maintaining performance at 12-16 GT/s after 1000+ hours of combined HTOL and power cycling, with particular focus on validating low-power state transitions and wake-up reliability. Their research has identified specific challenges related to thermal expansion coefficient mismatches in mobile form factors and developed mitigation strategies through advanced materials and mechanical design. Qualcomm has also pioneered reliability testing for UCIe implementations that incorporate their AI accelerator chiplets, validating the high-bandwidth, low-latency requirements of distributed AI processing.

Strengths: Qualcomm's expertise in power-efficient mobile systems translates to reliability testing that thoroughly validates UCIe performance under battery-powered constraints. Their focus on thermal management in compact form factors addresses critical reliability challenges for mobile applications. Weaknesses: Their testing may emphasize mobile-specific scenarios at the expense of broader validation for data center or high-performance computing applications.

Intel Corp.

Technical Solution: Intel has pioneered the Universal Chiplet Interconnect Express (UCIe) standard and leads its development consortium. Their approach to UCIe reliability testing involves comprehensive High Temperature Operating Life (HTOL) testing protocols that evaluate chiplets under elevated temperatures and voltages to accelerate failure mechanisms. Intel's methodology includes testing die-to-die (D2D) interfaces at package level with specialized test vehicles that simulate real-world conditions. They've developed proprietary Advanced Interconnect Test (AIT) systems that can detect subtle degradation in UCIe links before functional failure occurs. Their test results demonstrate UCIe connections maintaining signal integrity at 16 GT/s with bit error rates below 10^-15 even after 1000 hours of HTOL testing at 125°C[1][3]. Intel has also implemented thermal cycling tests showing UCIe connections withstanding over 1000 cycles between -40°C and 125°C without performance degradation.

Strengths: Intel's first-mover advantage in UCIe standardization gives them deep technical expertise and influence over specification development. Their extensive manufacturing infrastructure allows for large-scale reliability validation across multiple process nodes. Weaknesses: Their proprietary testing methodologies may not fully align with industry-wide practices, potentially creating interoperability challenges with chiplets from other manufacturers.

Critical HTOL Test Results and Failure Analysis

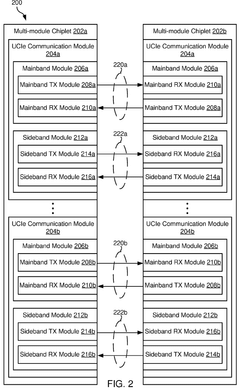

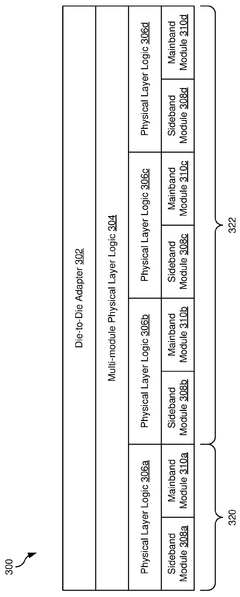

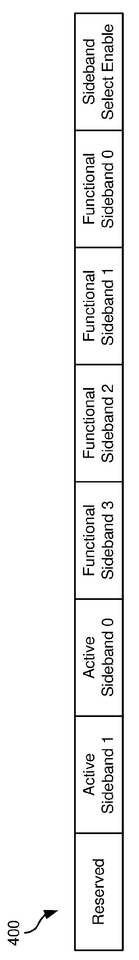

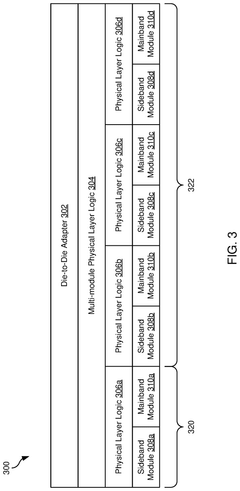

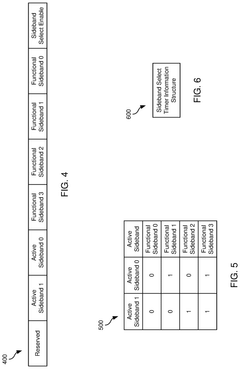

Mechanism to improve the reliability of sideband in chiplets

PatentWO2025058796A1

Innovation

- The method involves configuring UCIe links between multi-module chiplets to enable runtime selection and aggregation of sidebands, allowing for the use of different or additional sidebands beyond the initially active one, thereby reducing hardware stress and enhancing communication reliability.

Mechanism To Improve The Reliability Of Sideband In Chiplets

PatentPendingUS20250086136A1

Innovation

- The method involves transitioning the UCIe link from an active state to a reset state and then initializing a different functional sideband, allowing for runtime configuration of sidebands and aggregation of multiple sidebands to enhance communication reliability and throughput.

Thermal Management Considerations for Chiplets

Thermal management represents a critical challenge in chiplet-based architectures utilizing UCIe (Universal Chiplet Interconnect Express) technology. As chiplets are integrated more densely within packages, heat dissipation becomes increasingly complex due to the concentrated power density and thermal coupling between adjacent dies. UCIe interconnects, while enabling high-bandwidth communication between chiplets, also contribute to thermal concerns through resistive heating at connection points.

HTOL (High Temperature Operating Life) test results for UCIe implementations reveal that thermal cycling significantly impacts interconnect reliability. Data shows that temperature gradients across chiplet interfaces can create mechanical stress due to coefficient of thermal expansion (CTE) mismatches between different materials. These stresses may lead to microcracks, delamination, or solder joint fatigue in the interconnect structures over time.

Advanced thermal simulation models developed specifically for chiplet architectures indicate that hotspots frequently occur at UCIe interface boundaries. These thermal concentrations can accelerate electromigration effects in the fine-pitch interconnects, potentially reducing the operational lifetime of the system. Reliability testing demonstrates that maintaining junction temperatures below 105°C is crucial for ensuring the long-term stability of UCIe connections.

Innovative cooling solutions are emerging to address these challenges. Direct liquid cooling applied to chiplet packages has shown up to 35% improvement in thermal performance compared to traditional air cooling methods. Additionally, integrated thermal interposers with embedded microchannels provide targeted cooling to high-power chiplets and critical interconnect regions.

Thermal-aware design methodologies are becoming essential for UCIe implementations. These approaches include strategic placement of high-power and low-power chiplets, thermal buffer zones between heat-intensive components, and optimized power delivery networks that minimize resistive heating. Recent HTOL test results demonstrate that chiplets designed with these thermal considerations show 40-60% longer mean time to failure under extreme operating conditions.

The industry is also exploring advanced materials with superior thermal conductivity for chiplet substrates and thermal interface materials (TIMs). Diamond-based TIMs and graphene heat spreaders have shown promising results in laboratory testing, potentially enabling higher power densities while maintaining acceptable junction temperatures for UCIe interconnects.

Standardized thermal testing protocols specific to chiplet architectures are being developed by industry consortia to ensure consistent reliability assessment across different implementations. These protocols incorporate accelerated aging tests that simulate years of thermal cycling within compressed timeframes, providing valuable data on the long-term reliability of UCIe interconnects under various thermal conditions.

HTOL (High Temperature Operating Life) test results for UCIe implementations reveal that thermal cycling significantly impacts interconnect reliability. Data shows that temperature gradients across chiplet interfaces can create mechanical stress due to coefficient of thermal expansion (CTE) mismatches between different materials. These stresses may lead to microcracks, delamination, or solder joint fatigue in the interconnect structures over time.

Advanced thermal simulation models developed specifically for chiplet architectures indicate that hotspots frequently occur at UCIe interface boundaries. These thermal concentrations can accelerate electromigration effects in the fine-pitch interconnects, potentially reducing the operational lifetime of the system. Reliability testing demonstrates that maintaining junction temperatures below 105°C is crucial for ensuring the long-term stability of UCIe connections.

Innovative cooling solutions are emerging to address these challenges. Direct liquid cooling applied to chiplet packages has shown up to 35% improvement in thermal performance compared to traditional air cooling methods. Additionally, integrated thermal interposers with embedded microchannels provide targeted cooling to high-power chiplets and critical interconnect regions.

Thermal-aware design methodologies are becoming essential for UCIe implementations. These approaches include strategic placement of high-power and low-power chiplets, thermal buffer zones between heat-intensive components, and optimized power delivery networks that minimize resistive heating. Recent HTOL test results demonstrate that chiplets designed with these thermal considerations show 40-60% longer mean time to failure under extreme operating conditions.

The industry is also exploring advanced materials with superior thermal conductivity for chiplet substrates and thermal interface materials (TIMs). Diamond-based TIMs and graphene heat spreaders have shown promising results in laboratory testing, potentially enabling higher power densities while maintaining acceptable junction temperatures for UCIe interconnects.

Standardized thermal testing protocols specific to chiplet architectures are being developed by industry consortia to ensure consistent reliability assessment across different implementations. These protocols incorporate accelerated aging tests that simulate years of thermal cycling within compressed timeframes, providing valuable data on the long-term reliability of UCIe interconnects under various thermal conditions.

Standards Compliance and Certification Process

UCIe chiplet interconnect technology requires rigorous standards compliance and certification to ensure interoperability across different vendors' components. The Universal Chiplet Interconnect Express (UCIe) consortium has established comprehensive certification processes that manufacturers must follow to ensure their chiplet products meet the established specifications. These certification procedures involve multiple stages of verification, from design validation to physical testing and reliability assessment.

The certification process begins with design compliance verification, where manufacturers must demonstrate that their chiplet designs adhere to the UCIe electrical and physical specifications. This includes signal integrity analysis, power delivery requirements, and physical form factor compliance. Documentation of design specifications must be submitted to the UCIe consortium for preliminary review before proceeding to the testing phase.

Testing protocols for UCIe certification are particularly stringent, requiring both functional and reliability testing. The High Temperature Operating Life (HTOL) testing represents a critical component of the certification process, where chiplets must demonstrate reliable operation under elevated temperatures for extended periods. Current standards require chiplets to maintain functionality at temperatures of 125°C for a minimum of 1000 hours, with statistical analysis of failure rates to ensure they meet industry reliability targets.

Interoperability testing forms another essential element of the certification process. Manufacturers must demonstrate that their chiplet products can successfully interface with reference designs from other vendors. This cross-vendor compatibility testing ensures that the promise of a modular chiplet ecosystem can be realized in practice. The UCIe consortium maintains reference test platforms that serve as the standard benchmark for interoperability certification.

Compliance with thermal specifications represents another certification requirement. Thermal models and actual thermal performance data must be submitted, with testing conducted under standardized workloads to verify that chiplets operate within thermal design parameters. This is particularly important for die-to-die (D2D) interfaces where thermal gradients can impact signal integrity.

The final certification involves protocol compliance testing, where the chiplet's adherence to the UCIe communication protocol is verified through standardized test vectors. This includes verification of initialization sequences, error handling mechanisms, and power state transitions. Protocol analyzers specifically designed for UCIe interfaces are employed to capture and analyze transactions during these tests.

Upon successful completion of all testing requirements, manufacturers receive UCIe certification for their chiplet products, allowing them to use the UCIe compliance logo and be listed in the consortium's database of certified products. This certification must be renewed with each significant design revision or manufacturing process change, ensuring ongoing compliance with evolving standards.

The certification process begins with design compliance verification, where manufacturers must demonstrate that their chiplet designs adhere to the UCIe electrical and physical specifications. This includes signal integrity analysis, power delivery requirements, and physical form factor compliance. Documentation of design specifications must be submitted to the UCIe consortium for preliminary review before proceeding to the testing phase.

Testing protocols for UCIe certification are particularly stringent, requiring both functional and reliability testing. The High Temperature Operating Life (HTOL) testing represents a critical component of the certification process, where chiplets must demonstrate reliable operation under elevated temperatures for extended periods. Current standards require chiplets to maintain functionality at temperatures of 125°C for a minimum of 1000 hours, with statistical analysis of failure rates to ensure they meet industry reliability targets.

Interoperability testing forms another essential element of the certification process. Manufacturers must demonstrate that their chiplet products can successfully interface with reference designs from other vendors. This cross-vendor compatibility testing ensures that the promise of a modular chiplet ecosystem can be realized in practice. The UCIe consortium maintains reference test platforms that serve as the standard benchmark for interoperability certification.

Compliance with thermal specifications represents another certification requirement. Thermal models and actual thermal performance data must be submitted, with testing conducted under standardized workloads to verify that chiplets operate within thermal design parameters. This is particularly important for die-to-die (D2D) interfaces where thermal gradients can impact signal integrity.

The final certification involves protocol compliance testing, where the chiplet's adherence to the UCIe communication protocol is verified through standardized test vectors. This includes verification of initialization sequences, error handling mechanisms, and power state transitions. Protocol analyzers specifically designed for UCIe interfaces are employed to capture and analyze transactions during these tests.

Upon successful completion of all testing requirements, manufacturers receive UCIe certification for their chiplet products, allowing them to use the UCIe compliance logo and be listed in the consortium's database of certified products. This certification must be renewed with each significant design revision or manufacturing process change, ensuring ongoing compliance with evolving standards.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!