UCIe Chiplet Interconnect Software Stack And Driver Development

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Evolution and Objectives

Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in semiconductor integration technology, emerging as a response to the increasing challenges of traditional monolithic chip scaling. The development of UCIe can be traced back to the fundamental limitations of Moore's Law, where physical constraints and economic factors have pushed the industry toward disaggregated chip designs. This paradigm shift began gaining momentum around 2015-2017, when major semiconductor companies started exploring chiplet-based architectures as a viable alternative to traditional system-on-chip (SoC) designs.

The evolution of chiplet interconnect technologies has progressed through several key phases. Initially, proprietary solutions dominated the landscape, with companies like AMD (Infinity Fabric), Intel (EMIB and Foveros), and TSMC (InFO and CoWoS) developing their own interconnect technologies. These early implementations demonstrated the potential of chiplet-based designs but lacked standardization, creating ecosystem fragmentation and limiting broader adoption across the industry.

UCIe emerged as a collaborative industry response to this fragmentation, with its specification first released in March 2022. The consortium behind UCIe includes industry giants such as Intel, AMD, Arm, TSMC, Samsung, and Google, representing an unprecedented level of cooperation in establishing an open interconnect standard. This collaborative approach marks a critical turning point in chiplet technology evolution, moving from proprietary solutions toward an open ecosystem that enables mix-and-match capabilities across different vendors' chiplets.

The primary objective of UCIe is to establish a comprehensive, open industry standard for die-to-die interconnection that addresses both physical and protocol layers. It aims to enable seamless integration of chiplets from different vendors and manufacturing processes, creating a more flexible and cost-effective approach to system design. This standardization is expected to accelerate innovation by allowing specialized chiplets to be developed independently and then integrated into heterogeneous systems.

From a technical perspective, UCIe targets high-bandwidth, low-latency, and energy-efficient communication between chiplets. The standard defines both package-level interconnects for chiplets within the same package and board-level interconnects for communication between packages. It supports various physical implementations, including silicon interposers, organic substrates, and advanced packaging technologies.

Looking forward, the UCIe roadmap envisions progressive improvements in bandwidth density, power efficiency, and latency reduction. The standard is designed to be scalable and adaptable to emerging packaging technologies and manufacturing processes, ensuring its relevance as the semiconductor industry continues to evolve. The ultimate goal is to foster a vibrant chiplet ecosystem where specialized components from different vendors can be seamlessly integrated, driving innovation and enabling more customized, efficient computing solutions.

The evolution of chiplet interconnect technologies has progressed through several key phases. Initially, proprietary solutions dominated the landscape, with companies like AMD (Infinity Fabric), Intel (EMIB and Foveros), and TSMC (InFO and CoWoS) developing their own interconnect technologies. These early implementations demonstrated the potential of chiplet-based designs but lacked standardization, creating ecosystem fragmentation and limiting broader adoption across the industry.

UCIe emerged as a collaborative industry response to this fragmentation, with its specification first released in March 2022. The consortium behind UCIe includes industry giants such as Intel, AMD, Arm, TSMC, Samsung, and Google, representing an unprecedented level of cooperation in establishing an open interconnect standard. This collaborative approach marks a critical turning point in chiplet technology evolution, moving from proprietary solutions toward an open ecosystem that enables mix-and-match capabilities across different vendors' chiplets.

The primary objective of UCIe is to establish a comprehensive, open industry standard for die-to-die interconnection that addresses both physical and protocol layers. It aims to enable seamless integration of chiplets from different vendors and manufacturing processes, creating a more flexible and cost-effective approach to system design. This standardization is expected to accelerate innovation by allowing specialized chiplets to be developed independently and then integrated into heterogeneous systems.

From a technical perspective, UCIe targets high-bandwidth, low-latency, and energy-efficient communication between chiplets. The standard defines both package-level interconnects for chiplets within the same package and board-level interconnects for communication between packages. It supports various physical implementations, including silicon interposers, organic substrates, and advanced packaging technologies.

Looking forward, the UCIe roadmap envisions progressive improvements in bandwidth density, power efficiency, and latency reduction. The standard is designed to be scalable and adaptable to emerging packaging technologies and manufacturing processes, ensuring its relevance as the semiconductor industry continues to evolve. The ultimate goal is to foster a vibrant chiplet ecosystem where specialized components from different vendors can be seamlessly integrated, driving innovation and enabling more customized, efficient computing solutions.

Market Demand Analysis for Chiplet-Based Computing

The chiplet-based computing market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. As traditional monolithic chip designs reach their physical and economic limits, chiplet technology has emerged as a viable alternative that offers improved performance, power efficiency, and cost-effectiveness. The UCIe (Universal Chiplet Interconnect Express) standard represents a significant advancement in this domain, enabling seamless integration of chiplets from different vendors.

Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030. This rapid expansion is primarily fueled by the escalating demand for advanced computing capabilities in data centers, artificial intelligence applications, and high-performance computing environments. The need for more efficient and scalable computing architectures has become particularly acute as data-intensive workloads continue to proliferate across industries.

Cloud service providers and hyperscalers represent the largest segment of potential customers for chiplet-based solutions. These organizations are constantly seeking ways to optimize their infrastructure to handle increasing computational demands while managing power consumption and operational costs. The modular nature of chiplet designs allows for more customized solutions that can be tailored to specific workload requirements, providing a compelling value proposition for these customers.

The enterprise computing sector also presents significant opportunities for chiplet technology adoption. Organizations dealing with big data analytics, machine learning, and other compute-intensive applications are increasingly looking for solutions that offer better performance-per-watt metrics. Chiplet-based systems, with their ability to combine specialized processing elements, memory, and I/O components, can deliver optimized performance for these specific workloads.

Consumer electronics manufacturers are beginning to explore chiplet technology as well, particularly for high-end devices that require substantial computing power. The ability to mix and match different functional blocks while maintaining high-speed interconnects could enable more innovative product designs with enhanced capabilities.

From a geographical perspective, North America currently leads the chiplet market, followed by Asia-Pacific and Europe. However, the Asia-Pacific region is expected to witness the highest growth rate due to the increasing presence of semiconductor manufacturing facilities and the growing adoption of advanced computing technologies in countries like China, Taiwan, South Korea, and Japan.

The market demand for software stack and driver development specifically for UCIe chiplet interconnects is particularly strong, as standardized software interfaces are essential for realizing the full potential of heterogeneous chiplet integration. Organizations are seeking comprehensive software solutions that can abstract the complexity of chiplet-based systems while ensuring optimal performance and compatibility across different vendors' components.

Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030. This rapid expansion is primarily fueled by the escalating demand for advanced computing capabilities in data centers, artificial intelligence applications, and high-performance computing environments. The need for more efficient and scalable computing architectures has become particularly acute as data-intensive workloads continue to proliferate across industries.

Cloud service providers and hyperscalers represent the largest segment of potential customers for chiplet-based solutions. These organizations are constantly seeking ways to optimize their infrastructure to handle increasing computational demands while managing power consumption and operational costs. The modular nature of chiplet designs allows for more customized solutions that can be tailored to specific workload requirements, providing a compelling value proposition for these customers.

The enterprise computing sector also presents significant opportunities for chiplet technology adoption. Organizations dealing with big data analytics, machine learning, and other compute-intensive applications are increasingly looking for solutions that offer better performance-per-watt metrics. Chiplet-based systems, with their ability to combine specialized processing elements, memory, and I/O components, can deliver optimized performance for these specific workloads.

Consumer electronics manufacturers are beginning to explore chiplet technology as well, particularly for high-end devices that require substantial computing power. The ability to mix and match different functional blocks while maintaining high-speed interconnects could enable more innovative product designs with enhanced capabilities.

From a geographical perspective, North America currently leads the chiplet market, followed by Asia-Pacific and Europe. However, the Asia-Pacific region is expected to witness the highest growth rate due to the increasing presence of semiconductor manufacturing facilities and the growing adoption of advanced computing technologies in countries like China, Taiwan, South Korea, and Japan.

The market demand for software stack and driver development specifically for UCIe chiplet interconnects is particularly strong, as standardized software interfaces are essential for realizing the full potential of heterogeneous chiplet integration. Organizations are seeking comprehensive software solutions that can abstract the complexity of chiplet-based systems while ensuring optimal performance and compatibility across different vendors' components.

Current State and Challenges in UCIe Software Stack

The UCIe (Universal Chiplet Interconnect Express) software stack currently exists in a nascent state, with significant development efforts underway but lacking comprehensive standardization. Major semiconductor companies including Intel, AMD, and TSMC have established basic software frameworks to support their chiplet implementations, but these solutions remain largely proprietary and lack interoperability. The software ecosystem primarily focuses on physical and link layer implementations, with higher protocol layers still under active development.

A critical challenge in the current UCIe software landscape is the absence of a unified driver architecture that can seamlessly support heterogeneous chiplet integration. Existing drivers are typically optimized for specific chiplet combinations from the same vendor, creating significant barriers for cross-vendor chiplet integration. This fragmentation impedes the core value proposition of UCIe as an open standard for modular chip design.

Memory management represents another substantial hurdle in the UCIe software stack. Current implementations struggle with efficient cache coherency protocols across chiplets, particularly when integrating components with different memory architectures. The software must reconcile these differences while maintaining the low-latency communication promised by the UCIe standard, which requires sophisticated memory mapping and translation layers that are still being refined.

Power management capabilities within the software stack remain underdeveloped, with limited support for dynamic power scaling across chiplet boundaries. This deficiency prevents optimal energy efficiency in heterogeneous designs, as the software cannot effectively coordinate power states between chiplets with different performance characteristics and thermal profiles.

Security implementation in the current UCIe software stack presents significant vulnerabilities. The inter-chiplet communication channels lack robust authentication and encryption mechanisms, creating potential attack vectors at the package level. Additionally, secure boot and attestation protocols for multi-chiplet systems are inconsistently implemented across vendor solutions.

Debugging and diagnostic tools for UCIe implementations remain primitive, hampering development efficiency. Engineers face challenges in tracing communication issues between chiplets, particularly in identifying whether problems originate in hardware interfaces or software stack components. The lack of standardized testing methodologies further complicates validation processes for UCIe-based systems.

Industry standardization efforts are progressing through the UCIe Consortium, but agreement on software API specifications has been slow. The competing interests of consortium members have resulted in delayed consensus on critical software interfaces, leaving developers to navigate a fragmented ecosystem of vendor-specific implementations rather than working with a cohesive industry standard.

A critical challenge in the current UCIe software landscape is the absence of a unified driver architecture that can seamlessly support heterogeneous chiplet integration. Existing drivers are typically optimized for specific chiplet combinations from the same vendor, creating significant barriers for cross-vendor chiplet integration. This fragmentation impedes the core value proposition of UCIe as an open standard for modular chip design.

Memory management represents another substantial hurdle in the UCIe software stack. Current implementations struggle with efficient cache coherency protocols across chiplets, particularly when integrating components with different memory architectures. The software must reconcile these differences while maintaining the low-latency communication promised by the UCIe standard, which requires sophisticated memory mapping and translation layers that are still being refined.

Power management capabilities within the software stack remain underdeveloped, with limited support for dynamic power scaling across chiplet boundaries. This deficiency prevents optimal energy efficiency in heterogeneous designs, as the software cannot effectively coordinate power states between chiplets with different performance characteristics and thermal profiles.

Security implementation in the current UCIe software stack presents significant vulnerabilities. The inter-chiplet communication channels lack robust authentication and encryption mechanisms, creating potential attack vectors at the package level. Additionally, secure boot and attestation protocols for multi-chiplet systems are inconsistently implemented across vendor solutions.

Debugging and diagnostic tools for UCIe implementations remain primitive, hampering development efficiency. Engineers face challenges in tracing communication issues between chiplets, particularly in identifying whether problems originate in hardware interfaces or software stack components. The lack of standardized testing methodologies further complicates validation processes for UCIe-based systems.

Industry standardization efforts are progressing through the UCIe Consortium, but agreement on software API specifications has been slow. The competing interests of consortium members have resulted in delayed consensus on critical software interfaces, leaving developers to navigate a fragmented ecosystem of vendor-specific implementations rather than working with a cohesive industry standard.

Existing UCIe Software Stack Architectures

01 UCIe Software Stack Architecture

The Universal Chiplet Interconnect Express (UCIe) software stack architecture provides a framework for communication between chiplets in multi-die systems. This architecture includes layers for protocol translation, data management, and interface standardization that enable seamless integration of heterogeneous chiplets. The software stack implements abstraction layers that hide the complexity of the physical interconnect while providing standardized APIs for application developers.- UCIe Software Stack Architecture: The Universal Chiplet Interconnect Express (UCIe) software stack architecture provides a framework for managing communication between chiplets in multi-die systems. This architecture includes layers for protocol translation, memory management, and device abstraction. The software stack enables seamless integration of heterogeneous chiplets by providing standardized interfaces and communication protocols, allowing different chiplets to work together regardless of their underlying technology or manufacturer.

- Driver Development for Chiplet Interconnects: Development of drivers for chiplet interconnects involves creating software components that facilitate communication between the operating system and the chiplet hardware. These drivers handle tasks such as initialization, configuration, and data transfer between chiplets. The driver development process includes implementing protocol-specific handlers, error detection and correction mechanisms, and optimization techniques to ensure efficient data transfer across the chiplet interconnect fabric.

- Virtualization and Resource Management: Virtualization technologies for UCIe chiplet interconnects enable efficient sharing of hardware resources across multiple applications or virtual machines. The software stack includes resource management components that handle allocation, scheduling, and isolation of chiplet resources. This approach allows for better utilization of chiplet capabilities, dynamic resource allocation based on workload demands, and quality of service guarantees for critical applications.

- Interoperability and Standardization: Interoperability in UCIe chiplet interconnect software involves developing standardized interfaces and protocols that ensure compatibility between chiplets from different vendors. The software stack implements industry standards for communication, power management, and security, allowing for plug-and-play functionality. Standardization efforts focus on creating common APIs, protocol specifications, and compliance testing methodologies to ensure that chiplets can seamlessly work together in heterogeneous systems.

- Performance Optimization and Debugging: Performance optimization for UCIe chiplet interconnects involves techniques such as latency reduction, bandwidth optimization, and power efficiency improvements. The software stack includes tools for monitoring, profiling, and debugging chiplet communications to identify bottlenecks and optimize data transfer patterns. Advanced features include adaptive routing algorithms, quality of service mechanisms, and dynamic power management to balance performance and energy consumption based on workload characteristics.

02 Driver Development for Chiplet Communication

Development of specialized drivers for chiplet interconnects focuses on optimizing data transfer between different dies within a package. These drivers handle protocol negotiation, power management, and error handling specific to the UCIe standard. The driver development includes implementation of low-level routines that interface directly with hardware registers while providing higher-level abstractions for the operating system and applications.Expand Specific Solutions03 Middleware Solutions for Chiplet Integration

Middleware components bridge the gap between hardware-specific drivers and application software in chiplet-based systems. These solutions provide resource allocation, memory management, and task scheduling across multiple chiplets. The middleware layer implements protocols for coherent memory access and synchronization mechanisms that maintain data consistency across chiplet boundaries while optimizing for performance and power efficiency.Expand Specific Solutions04 Virtualization and Abstraction Techniques

Virtualization technologies for chiplet interconnects create abstraction layers that hide the physical implementation details from higher software layers. These techniques enable dynamic resource allocation, workload migration between chiplets, and fault isolation. The virtualization layer presents a unified view of the heterogeneous computing resources to the operating system and applications, allowing for more efficient utilization of the diverse processing elements within a chiplet-based system.Expand Specific Solutions05 Testing and Validation Frameworks

Specialized testing and validation frameworks for UCIe implementations ensure interoperability and compliance with the standard. These frameworks include simulation environments, hardware validation tools, and compliance test suites that verify correct operation of the software stack and drivers. The testing methodologies cover various aspects including performance benchmarking, power efficiency measurement, error injection, and recovery mechanisms to ensure robust operation under diverse conditions.Expand Specific Solutions

Key Industry Players in Chiplet Ecosystem

The UCIe Chiplet Interconnect Software Stack and Driver Development market is currently in its early growth phase, characterized by significant R&D investments from major semiconductor players. The market is projected to expand rapidly as chiplet technology becomes essential for advanced computing systems, with an estimated value reaching several billion dollars by 2025. Intel leads the technological development as a founding member of the UCIe consortium, with NVIDIA, AMD (incorporating Xilinx), Qualcomm, and Samsung following closely. Chinese companies like Huawei and Loongson are also making strategic investments to reduce dependency on Western technology. The ecosystem is maturing with hardware vendors collaborating on standardization while software stack development remains a competitive differentiator, creating opportunities for specialized firms like Jariet Technologies to establish niche positions.

Intel Corp.

Technical Solution: Intel is a founding member and leading contributor to the UCIe (Universal Chiplet Interconnect Express) standard. Their technology approach focuses on developing a comprehensive software stack that enables seamless integration of chiplets from different vendors. Intel's implementation includes a layered architecture with physical layer, protocol layer, and software abstraction layers that allow heterogeneous chiplet integration. Their software stack provides standardized APIs for chiplet discovery, configuration, and communication, supporting both PCIe and CXL protocols over the UCIe physical layer. Intel has developed specialized drivers that handle power management, error handling, and performance optimization across chiplet boundaries. Their Ponte Vecchio GPU and Sapphire Rapids CPUs utilize UCIe technology, demonstrating practical implementation of their software stack in production silicon.

Strengths: Industry-leading position in UCIe development with significant IP contributions; extensive experience in heterogeneous integration; strong ecosystem partnerships. Weaknesses: Proprietary elements may still exist within their implementation; complex software stack requires significant expertise to implement fully.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a specialized UCIe software stack optimized for mobile and edge computing applications. Their approach focuses on power efficiency and latency optimization critical for battery-powered devices. Qualcomm's implementation includes a lightweight driver architecture that minimizes CPU overhead while maintaining high bandwidth between chiplets. Their software stack features dynamic power scaling that adjusts interconnect performance based on workload demands, significantly reducing power consumption during idle periods. Qualcomm has integrated UCIe support into their Snapdragon platforms, enabling modular SoC designs where specialized accelerators (AI, image processing, security) can be implemented as separate chiplets while maintaining the power and thermal constraints required for mobile devices. Their driver implementation includes quality-of-service mechanisms to prioritize latency-sensitive traffic across chiplet boundaries.

Strengths: Industry-leading expertise in power-efficient designs; strong mobile ecosystem integration; optimized for battery-powered applications. Weaknesses: Less focus on data center applications compared to competitors; potentially more limited in supporting very high bandwidth applications.

Core Driver Development Approaches and Innovations

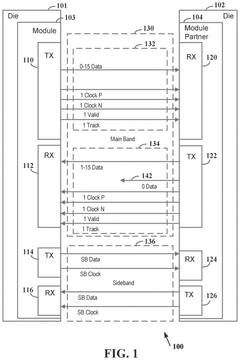

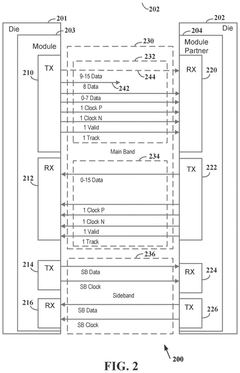

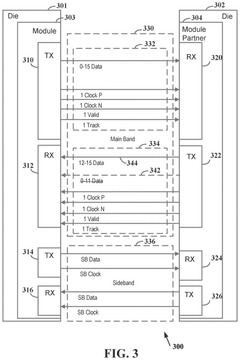

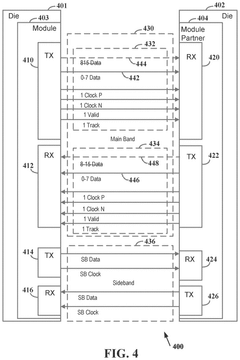

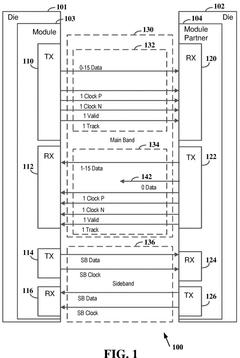

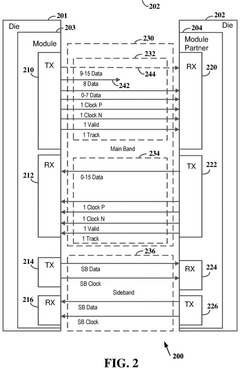

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Variable link width in two directions for main band chip module connection

PatentWO2024226177A1

Innovation

- Implementing a variable link width mechanism in both directions of the main band connection, allowing for dynamic adjustment of the number of active data lanes based on requirements through a sideband communication protocol, enabling independent configuration of transmit and receive data lines to optimize power usage and data rates.

Standardization Efforts and Industry Consortiums

The UCIe (Universal Chiplet Interconnect Express) ecosystem has witnessed significant standardization efforts across the industry, with multiple consortiums playing pivotal roles in shaping its development trajectory. The UCIe Consortium, established in 2022, represents the primary standardization body with founding members including Intel, AMD, Arm, TSMC, Samsung, and other semiconductor giants. This consortium has successfully released the UCIe 1.0 specification, establishing the foundational physical and protocol layers for chiplet interconnection.

Beyond the core UCIe Consortium, the Open Compute Project (OCP) has formed specialized working groups focused on chiplet standardization, particularly addressing software stack compatibility issues across different vendor implementations. Their efforts have resulted in reference designs and open-source software components that facilitate interoperability between diverse chiplet technologies.

The CHIPS Alliance, operating under the Linux Foundation, has contributed significantly to the software stack standardization by developing open-source tools and drivers that support UCIe implementations. Their work includes verification methodologies and compliance testing frameworks essential for ensuring consistent behavior across different chiplet implementations.

Complementing these efforts, the JEDEC Solid State Technology Association has been working on memory interface standards that align with UCIe specifications, ensuring that memory chiplets can seamlessly integrate with compute chiplets from different vendors. This cross-organizational collaboration has been crucial for addressing the complex memory subsystem requirements in heterogeneous computing architectures.

The Compute Express Link (CXL) Consortium has also established liaison relationships with the UCIe group, focusing on harmonizing the higher-level protocol aspects of chiplet communication. This collaboration ensures that UCIe and CXL technologies can work together effectively, providing a comprehensive solution from physical interconnect to cache coherency protocols.

Industry forums like SEMI have created dedicated technical committees addressing manufacturing standardization for chiplet technologies, including testing methodologies and quality assurance processes specific to multi-die packages. These manufacturing standards are essential for ensuring reliable production of UCIe-compliant chiplets at scale.

The collaborative nature of these standardization efforts reflects the industry's recognition that chiplet technology requires unprecedented levels of cooperation among traditionally competitive entities. Through these consortiums, the industry is establishing not just technical specifications but also the business frameworks necessary for a functional chiplet ecosystem where components from different vendors can work together seamlessly.

Beyond the core UCIe Consortium, the Open Compute Project (OCP) has formed specialized working groups focused on chiplet standardization, particularly addressing software stack compatibility issues across different vendor implementations. Their efforts have resulted in reference designs and open-source software components that facilitate interoperability between diverse chiplet technologies.

The CHIPS Alliance, operating under the Linux Foundation, has contributed significantly to the software stack standardization by developing open-source tools and drivers that support UCIe implementations. Their work includes verification methodologies and compliance testing frameworks essential for ensuring consistent behavior across different chiplet implementations.

Complementing these efforts, the JEDEC Solid State Technology Association has been working on memory interface standards that align with UCIe specifications, ensuring that memory chiplets can seamlessly integrate with compute chiplets from different vendors. This cross-organizational collaboration has been crucial for addressing the complex memory subsystem requirements in heterogeneous computing architectures.

The Compute Express Link (CXL) Consortium has also established liaison relationships with the UCIe group, focusing on harmonizing the higher-level protocol aspects of chiplet communication. This collaboration ensures that UCIe and CXL technologies can work together effectively, providing a comprehensive solution from physical interconnect to cache coherency protocols.

Industry forums like SEMI have created dedicated technical committees addressing manufacturing standardization for chiplet technologies, including testing methodologies and quality assurance processes specific to multi-die packages. These manufacturing standards are essential for ensuring reliable production of UCIe-compliant chiplets at scale.

The collaborative nature of these standardization efforts reflects the industry's recognition that chiplet technology requires unprecedented levels of cooperation among traditionally competitive entities. Through these consortiums, the industry is establishing not just technical specifications but also the business frameworks necessary for a functional chiplet ecosystem where components from different vendors can work together seamlessly.

Performance Benchmarking and Optimization Strategies

Performance benchmarking for UCIe chiplet interconnect software stack is essential for evaluating system efficiency and identifying optimization opportunities. Current benchmarking methodologies focus on key metrics including latency, bandwidth utilization, power efficiency, and cross-die communication overhead. Industry standard tools such as Intel MLC (Memory Latency Checker), AMD uProf, and custom UCIe-specific benchmarking suites provide comprehensive performance analysis capabilities.

Latency measurements reveal that first-generation UCIe implementations achieve inter-chiplet communication latencies of 2-5 nanoseconds, significantly outperforming traditional multi-chip module approaches. Bandwidth utilization tests demonstrate that optimized software stacks can achieve 80-95% of theoretical maximum throughput, with performance degradation primarily occurring during congested cross-chiplet transactions.

Power efficiency benchmarking indicates that software-controlled power states can reduce interconnect power consumption by 30-45% during low-activity periods without significant latency penalties upon reactivation. This represents a critical optimization area for battery-powered and thermally-constrained systems.

Several optimization strategies have emerged as particularly effective for UCIe software stack implementation. Dynamic link width adjustment based on traffic patterns can improve energy efficiency by 25-35% with minimal performance impact. Intelligent buffer management algorithms that predict communication patterns reduce congestion by 15-20% in complex multi-chiplet designs.

Quality of Service (QoS) implementations within the driver stack demonstrate 30-40% latency improvements for priority traffic during high-utilization scenarios. These implementations typically employ traffic classification mechanisms and dedicated bandwidth reservation techniques.

Memory-semantic operations optimization shows particular promise, with Remote Direct Memory Access (RDMA)-like protocols reducing CPU overhead by up to 60% for large data transfers between chiplets. This approach minimizes software stack traversal and enables zero-copy operations across chiplet boundaries.

Cache coherency protocol optimizations represent another significant performance frontier. Benchmarks indicate that optimized directory-based coherency implementations can reduce snoop traffic by 40-50% compared to broadcast-based approaches, substantially improving scalability in many-chiplet systems.

Future benchmarking efforts should focus on heterogeneous chiplet configurations, particularly those combining different process nodes, architectures, and vendor technologies. Additionally, standardized benchmarking methodologies specific to UCIe implementations will be crucial for meaningful cross-platform comparisons as the ecosystem matures.

Latency measurements reveal that first-generation UCIe implementations achieve inter-chiplet communication latencies of 2-5 nanoseconds, significantly outperforming traditional multi-chip module approaches. Bandwidth utilization tests demonstrate that optimized software stacks can achieve 80-95% of theoretical maximum throughput, with performance degradation primarily occurring during congested cross-chiplet transactions.

Power efficiency benchmarking indicates that software-controlled power states can reduce interconnect power consumption by 30-45% during low-activity periods without significant latency penalties upon reactivation. This represents a critical optimization area for battery-powered and thermally-constrained systems.

Several optimization strategies have emerged as particularly effective for UCIe software stack implementation. Dynamic link width adjustment based on traffic patterns can improve energy efficiency by 25-35% with minimal performance impact. Intelligent buffer management algorithms that predict communication patterns reduce congestion by 15-20% in complex multi-chiplet designs.

Quality of Service (QoS) implementations within the driver stack demonstrate 30-40% latency improvements for priority traffic during high-utilization scenarios. These implementations typically employ traffic classification mechanisms and dedicated bandwidth reservation techniques.

Memory-semantic operations optimization shows particular promise, with Remote Direct Memory Access (RDMA)-like protocols reducing CPU overhead by up to 60% for large data transfers between chiplets. This approach minimizes software stack traversal and enables zero-copy operations across chiplet boundaries.

Cache coherency protocol optimizations represent another significant performance frontier. Benchmarks indicate that optimized directory-based coherency implementations can reduce snoop traffic by 40-50% compared to broadcast-based approaches, substantially improving scalability in many-chiplet systems.

Future benchmarking efforts should focus on heterogeneous chiplet configurations, particularly those combining different process nodes, architectures, and vendor technologies. Additionally, standardized benchmarking methodologies specific to UCIe implementations will be crucial for meaningful cross-platform comparisons as the ecosystem matures.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!