Duty cycle calibration circuit

A technology for calibrating circuit and duty cycle, applied in the field of signal processing, can solve the problems of short delay time of delay unit and large area occupied by the duty cycle calibration circuit, achieve long delay time, increase delay time, reduce The effect of small power consumption and area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

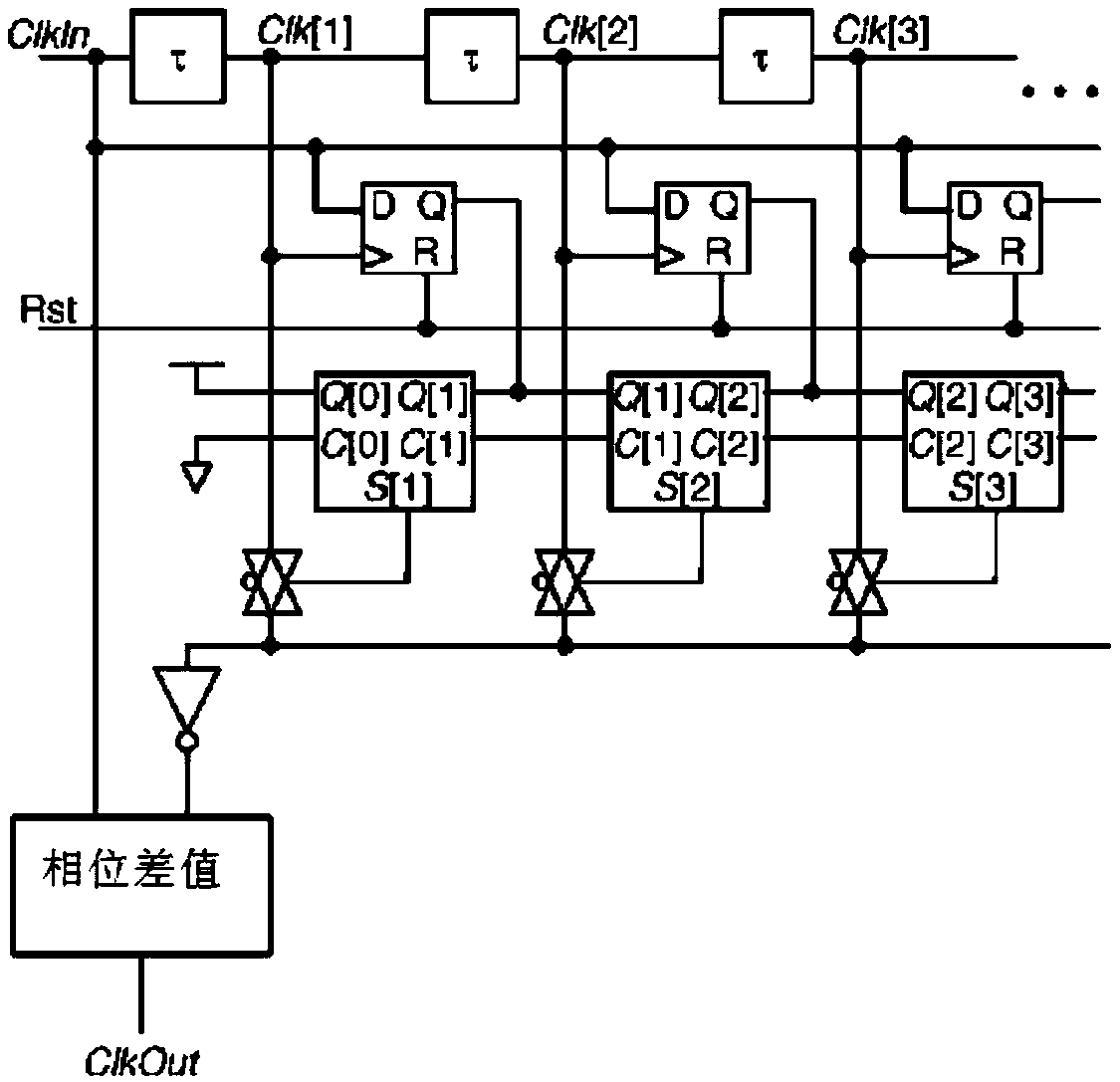

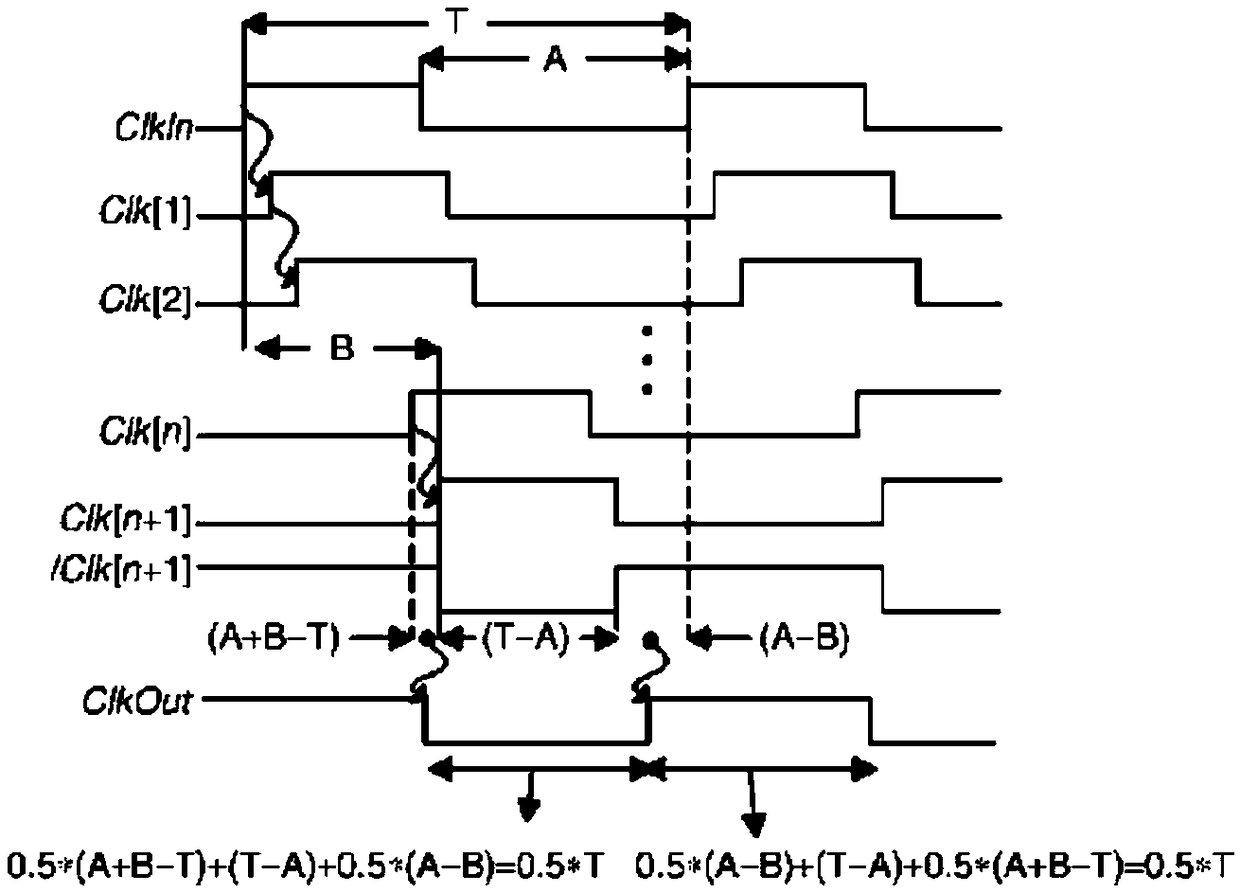

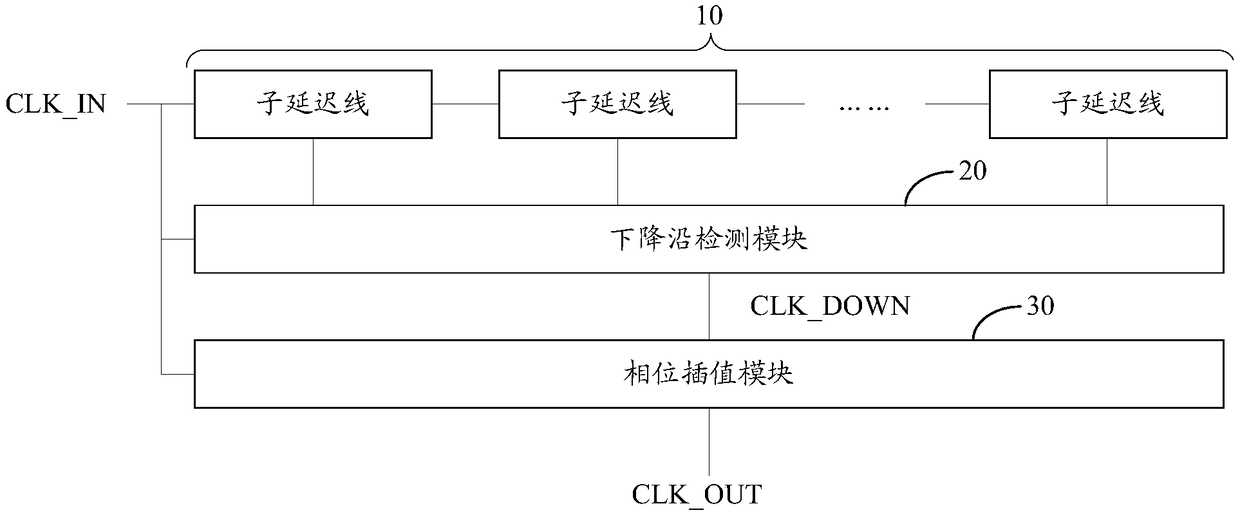

Embodiment Construction

[0059] In order to enable those skilled in the art to better understand the solution of the present application, the technical solution in the embodiment of the application will be clearly and completely described below in conjunction with the accompanying drawings in the embodiment of the application. Obviously, the described embodiment is only It is a part of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

[0060] It should be understood that in this application, "at least one (item)" means one or more, and "multiple" means two or more. "And / or" is used to describe the association relationship of associated objects, indicating that there can be three types of relationships, for example, "A and / or B" can mean: only A exists, only B exists, and A and B exist at the same...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More