Chiplet Integration's Role in Electricity Conduction Efficiency

OCT 15, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Integration Background and Objectives

Chiplet integration represents a paradigm shift in semiconductor design and manufacturing, evolving from traditional monolithic System-on-Chip (SoC) approaches to a more modular architecture. This evolution began in the early 2010s as semiconductor manufacturers faced increasing challenges with Moore's Law, particularly regarding electricity conduction efficiency across larger dies. The fundamental concept involves disaggregating complex SoC designs into smaller, specialized dies (chiplets) that are then integrated using advanced packaging technologies.

The historical trajectory of chiplet technology can be traced through several key developments. Initially, multi-chip modules (MCMs) provided rudimentary integration capabilities, but modern chiplet approaches emerged with AMD's introduction of their Infinity Fabric interconnect in 2017, demonstrating significant improvements in power efficiency compared to monolithic designs. Intel followed with their Embedded Multi-die Interconnect Bridge (EMIB) and Foveros technologies, while TSMC developed their Integrated Fan-Out (InFO) and System on Integrated Chips (SoIC) solutions.

Electricity conduction efficiency stands as a critical factor driving chiplet adoption. As transistor sizes approached physical limits, the resistance and capacitance of interconnects became increasingly problematic, creating power delivery and thermal management challenges. Chiplet architectures address these issues by optimizing the length and characteristics of electrical pathways between functional blocks, reducing parasitic effects that hamper efficient electricity conduction.

The primary technical objectives for chiplet integration regarding electricity conduction efficiency include: minimizing interface power consumption between chiplets, reducing overall system power requirements, optimizing thermal dissipation pathways, and maintaining signal integrity across chiplet boundaries. These objectives align with broader industry goals of continuing performance scaling while managing power constraints in post-Moore's Law semiconductor development.

Current research focuses on several promising directions, including advanced interconnect materials with lower resistance properties, novel die-to-die interface designs that reduce power overhead, three-dimensional integration techniques that shorten electrical pathways, and heterogeneous integration approaches that optimize each chiplet for its specific function and power profile.

The technology trend clearly points toward increasingly sophisticated chiplet architectures that prioritize electricity conduction efficiency as a key performance metric. Industry projections suggest that by 2025, over 60% of high-performance computing applications will utilize some form of chiplet-based design, with electricity efficiency improvements of 30-50% compared to equivalent monolithic implementations.

The historical trajectory of chiplet technology can be traced through several key developments. Initially, multi-chip modules (MCMs) provided rudimentary integration capabilities, but modern chiplet approaches emerged with AMD's introduction of their Infinity Fabric interconnect in 2017, demonstrating significant improvements in power efficiency compared to monolithic designs. Intel followed with their Embedded Multi-die Interconnect Bridge (EMIB) and Foveros technologies, while TSMC developed their Integrated Fan-Out (InFO) and System on Integrated Chips (SoIC) solutions.

Electricity conduction efficiency stands as a critical factor driving chiplet adoption. As transistor sizes approached physical limits, the resistance and capacitance of interconnects became increasingly problematic, creating power delivery and thermal management challenges. Chiplet architectures address these issues by optimizing the length and characteristics of electrical pathways between functional blocks, reducing parasitic effects that hamper efficient electricity conduction.

The primary technical objectives for chiplet integration regarding electricity conduction efficiency include: minimizing interface power consumption between chiplets, reducing overall system power requirements, optimizing thermal dissipation pathways, and maintaining signal integrity across chiplet boundaries. These objectives align with broader industry goals of continuing performance scaling while managing power constraints in post-Moore's Law semiconductor development.

Current research focuses on several promising directions, including advanced interconnect materials with lower resistance properties, novel die-to-die interface designs that reduce power overhead, three-dimensional integration techniques that shorten electrical pathways, and heterogeneous integration approaches that optimize each chiplet for its specific function and power profile.

The technology trend clearly points toward increasingly sophisticated chiplet architectures that prioritize electricity conduction efficiency as a key performance metric. Industry projections suggest that by 2025, over 60% of high-performance computing applications will utilize some form of chiplet-based design, with electricity efficiency improvements of 30-50% compared to equivalent monolithic implementations.

Market Demand Analysis for Efficient Chiplet Solutions

The global semiconductor market is experiencing a paradigm shift towards chiplet-based architectures, driven primarily by the increasing demand for more efficient power management and electrical conduction in advanced computing systems. Market research indicates that the traditional monolithic chip design approach is reaching physical and economic limitations, creating substantial market opportunities for chiplet solutions that can deliver superior electrical efficiency.

Current market analysis reveals that data centers, which consume approximately 1-2% of global electricity, represent the most immediate and substantial market for electrically efficient chiplet solutions. With data center power consumption growing at 15% annually, operators are actively seeking technologies that can reduce energy costs while maintaining or improving computational capabilities. This demand is further amplified by regulatory pressures and corporate sustainability commitments.

The high-performance computing (HPC) segment presents another significant market opportunity, valued at $38 billion in 2022 and projected to grow at a CAGR of 9.5% through 2028. In this sector, electrical conduction efficiency directly impacts system performance, cooling requirements, and operational costs. Market surveys indicate that HPC customers are willing to pay premium prices for solutions that deliver measurable improvements in electrical efficiency.

Consumer electronics manufacturers are also emerging as key stakeholders in the chiplet market. As devices become more powerful while maintaining or reducing form factors, thermal management and battery life become critical differentiators. Market data shows that smartphones, tablets, and wearables collectively represent a $500 billion opportunity where electrically efficient chiplet integration could provide significant competitive advantages.

Automotive applications, particularly in electric vehicles and advanced driver-assistance systems, constitute a rapidly growing market segment. Industry forecasts predict that semiconductor content in vehicles will double by 2030, with particular emphasis on power-efficient computing solutions. The automotive sector's stringent reliability requirements and harsh operating environments create unique market demands for chiplet solutions with superior electrical conduction properties.

Geographic market analysis indicates that while North America leads in chiplet technology development, Asia-Pacific represents the largest market by volume, with China, Taiwan, and South Korea making substantial investments in advanced semiconductor manufacturing capabilities. European markets show particular interest in chiplet solutions for industrial applications and automotive systems.

Market timing appears optimal for electrically efficient chiplet solutions, as industry-wide standardization efforts like Universal Chiplet Interconnect Express (UCIe) are reducing adoption barriers. Customer interviews reveal that the market values not only power efficiency improvements but also the flexibility, scalability, and potential cost advantages that properly designed chiplet architectures can deliver.

Current market analysis reveals that data centers, which consume approximately 1-2% of global electricity, represent the most immediate and substantial market for electrically efficient chiplet solutions. With data center power consumption growing at 15% annually, operators are actively seeking technologies that can reduce energy costs while maintaining or improving computational capabilities. This demand is further amplified by regulatory pressures and corporate sustainability commitments.

The high-performance computing (HPC) segment presents another significant market opportunity, valued at $38 billion in 2022 and projected to grow at a CAGR of 9.5% through 2028. In this sector, electrical conduction efficiency directly impacts system performance, cooling requirements, and operational costs. Market surveys indicate that HPC customers are willing to pay premium prices for solutions that deliver measurable improvements in electrical efficiency.

Consumer electronics manufacturers are also emerging as key stakeholders in the chiplet market. As devices become more powerful while maintaining or reducing form factors, thermal management and battery life become critical differentiators. Market data shows that smartphones, tablets, and wearables collectively represent a $500 billion opportunity where electrically efficient chiplet integration could provide significant competitive advantages.

Automotive applications, particularly in electric vehicles and advanced driver-assistance systems, constitute a rapidly growing market segment. Industry forecasts predict that semiconductor content in vehicles will double by 2030, with particular emphasis on power-efficient computing solutions. The automotive sector's stringent reliability requirements and harsh operating environments create unique market demands for chiplet solutions with superior electrical conduction properties.

Geographic market analysis indicates that while North America leads in chiplet technology development, Asia-Pacific represents the largest market by volume, with China, Taiwan, and South Korea making substantial investments in advanced semiconductor manufacturing capabilities. European markets show particular interest in chiplet solutions for industrial applications and automotive systems.

Market timing appears optimal for electrically efficient chiplet solutions, as industry-wide standardization efforts like Universal Chiplet Interconnect Express (UCIe) are reducing adoption barriers. Customer interviews reveal that the market values not only power efficiency improvements but also the flexibility, scalability, and potential cost advantages that properly designed chiplet architectures can deliver.

Current State and Challenges in Chiplet Conduction Efficiency

The global chiplet integration landscape is currently experiencing rapid evolution, with significant advancements in conduction efficiency technologies. Leading semiconductor manufacturers including TSMC, Intel, AMD, and Samsung have established robust chiplet architectures, though electrical conduction between dies remains a critical challenge. Current integration methods predominantly utilize silicon interposers, organic substrates, and advanced packaging technologies such as EMIB (Embedded Multi-die Interconnect Bridge) and Foveros, each presenting unique conduction characteristics.

Electrical conduction efficiency in chiplet designs faces several fundamental challenges. Die-to-die interfaces create resistance barriers that impede electron flow, resulting in power losses estimated at 15-30% compared to monolithic designs. Signal integrity degradation occurs across interconnect boundaries, with high-frequency signals particularly vulnerable to attenuation and distortion. Thermal management presents another significant obstacle, as heat concentration at interconnect points can increase electrical resistance by up to 40% under peak workloads.

Manufacturing inconsistencies further complicate conduction efficiency, with process variations creating impedance mismatches between chiplets. Current research indicates that even minor manufacturing deviations of 5-10nm can result in measurable conduction efficiency losses of 5-8%. The industry also struggles with standardization challenges, as proprietary interconnect technologies from different manufacturers often employ incompatible electrical signaling protocols.

Recent advancements have partially addressed these issues through innovations like Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe), which have improved signal integrity by approximately 25-30%. However, these solutions still fall short of monolithic conduction efficiency by 10-15% in practical applications. The theoretical limits of current materials also present barriers, with copper interconnects approaching fundamental resistivity constraints as dimensions shrink below 10nm.

Geographically, North America and East Asia dominate chiplet conduction research, with approximately 65% of relevant patents originating from these regions. European contributions focus primarily on specialized applications in automotive and industrial sectors. The technology readiness level (TRL) for current chiplet conduction solutions ranges from TRL-6 to TRL-8, indicating mature technology still requiring optimization for mass production efficiency.

Power efficiency metrics reveal that die-to-die interconnects currently consume between 15-25% of total system power in complex chiplet designs, representing a significant opportunity for improvement. Industry consensus suggests that achieving parity with monolithic designs requires breakthrough innovations in materials science and interconnect architectures that can reduce this overhead to below 5%.

Electrical conduction efficiency in chiplet designs faces several fundamental challenges. Die-to-die interfaces create resistance barriers that impede electron flow, resulting in power losses estimated at 15-30% compared to monolithic designs. Signal integrity degradation occurs across interconnect boundaries, with high-frequency signals particularly vulnerable to attenuation and distortion. Thermal management presents another significant obstacle, as heat concentration at interconnect points can increase electrical resistance by up to 40% under peak workloads.

Manufacturing inconsistencies further complicate conduction efficiency, with process variations creating impedance mismatches between chiplets. Current research indicates that even minor manufacturing deviations of 5-10nm can result in measurable conduction efficiency losses of 5-8%. The industry also struggles with standardization challenges, as proprietary interconnect technologies from different manufacturers often employ incompatible electrical signaling protocols.

Recent advancements have partially addressed these issues through innovations like Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe), which have improved signal integrity by approximately 25-30%. However, these solutions still fall short of monolithic conduction efficiency by 10-15% in practical applications. The theoretical limits of current materials also present barriers, with copper interconnects approaching fundamental resistivity constraints as dimensions shrink below 10nm.

Geographically, North America and East Asia dominate chiplet conduction research, with approximately 65% of relevant patents originating from these regions. European contributions focus primarily on specialized applications in automotive and industrial sectors. The technology readiness level (TRL) for current chiplet conduction solutions ranges from TRL-6 to TRL-8, indicating mature technology still requiring optimization for mass production efficiency.

Power efficiency metrics reveal that die-to-die interconnects currently consume between 15-25% of total system power in complex chiplet designs, representing a significant opportunity for improvement. Industry consensus suggests that achieving parity with monolithic designs requires breakthrough innovations in materials science and interconnect architectures that can reduce this overhead to below 5%.

Current Technical Solutions for Chiplet Conduction Efficiency

01 Advanced interconnect technologies for chiplet integration

Various advanced interconnect technologies are employed to enhance electrical conduction efficiency between chiplets. These include through-silicon vias (TSVs), micro-bumps, and hybrid bonding techniques that minimize resistance at connection points. These technologies enable high-bandwidth, low-latency communication between chiplets while reducing power consumption and signal degradation, ultimately improving overall system performance.- Advanced interconnect technologies for chiplet integration: Various interconnect technologies are employed to enhance electrical conduction efficiency between chiplets. These include through-silicon vias (TSVs), micro-bumps, and advanced packaging techniques that minimize signal loss and reduce electrical resistance. These interconnect solutions enable high-bandwidth, low-latency communication between chiplets while maintaining power efficiency and signal integrity across the integrated system.

- Thermal management solutions for efficient chiplet conduction: Thermal management is critical for maintaining electrical conduction efficiency in chiplet integration. Innovative cooling solutions, heat dissipation structures, and thermal interface materials are implemented to prevent performance degradation due to heat buildup. These thermal management approaches ensure optimal electrical performance by maintaining stable operating temperatures across the chiplet assembly, thereby enhancing overall system reliability and efficiency.

- Novel substrate and interposer designs for improved electrical pathways: Advanced substrate and interposer designs facilitate efficient electrical conduction between chiplets. These designs incorporate high-conductivity materials, optimized trace routing, and reduced-impedance pathways to minimize signal degradation. Multi-layer organic or silicon interposers with embedded passive components help shorten electrical paths between chiplets, reducing latency and power consumption while improving overall system performance.

- Power delivery network optimization for chiplet architectures: Efficient power delivery networks are essential for chiplet integration to ensure stable voltage supply and minimize power loss. Innovative power distribution architectures, decoupling capacitor arrangements, and voltage regulator placements are designed to reduce power delivery impedance. These optimizations help maintain consistent power supply to all chiplets, reducing electrical noise and improving signal integrity across the integrated system.

- Novel materials and manufacturing processes for enhanced conductivity: Advanced materials and manufacturing processes significantly improve electrical conduction efficiency in chiplet integration. These include copper-based redistribution layers, silver-sintered die attach materials, and novel conductive adhesives with reduced electrical resistance. Additionally, precision manufacturing techniques such as hybrid bonding and fine-pitch micro-bump formation enable denser interconnections with improved electrical characteristics, enhancing overall system performance and reliability.

02 Thermal management solutions for chiplet integration

Effective thermal management is crucial for maintaining electrical conduction efficiency in chiplet-based systems. Innovative cooling solutions such as integrated heat spreaders, thermal interface materials, and active cooling mechanisms help dissipate heat generated during operation. By controlling temperature fluctuations, these solutions prevent performance degradation due to thermal resistance increases, ensuring optimal electrical conductivity between integrated chiplets.Expand Specific Solutions03 Novel substrate and packaging materials for improved conductivity

The development of advanced substrate and packaging materials significantly impacts electrical conduction efficiency in chiplet integration. Materials with enhanced thermal and electrical properties, such as high-conductivity metals, specialized polymers, and composite materials, facilitate better signal transmission between chiplets. These materials reduce impedance mismatches and minimize signal losses, contributing to higher overall system efficiency.Expand Specific Solutions04 Power delivery network optimization for chiplet architectures

Optimized power delivery networks are essential for maintaining electrical conduction efficiency in chiplet-based systems. Advanced power distribution architectures, integrated voltage regulators, and innovative power management techniques ensure stable power supply to all chiplets. These optimizations reduce power losses, voltage drops, and current fluctuations, enabling more efficient electrical conduction between chiplets and improving overall system performance.Expand Specific Solutions05 Signal integrity enhancement techniques for inter-chiplet communication

Various signal integrity enhancement techniques are employed to improve electrical conduction efficiency between chiplets. These include advanced equalization methods, impedance matching techniques, and noise reduction strategies that minimize signal distortion and loss. Additionally, optimized routing topologies and specialized interface circuits help maintain signal quality across chiplet boundaries, ensuring reliable high-speed communication with minimal power consumption.Expand Specific Solutions

Key Industry Players in Chiplet Integration Market

Chiplet integration is currently in a growth phase within the semiconductor industry, with the market expected to expand significantly as companies seek more efficient electricity conduction solutions. The global chiplet market is projected to reach $40-50 billion by 2030, driven by increasing demand for high-performance computing and energy-efficient designs. Technologically, the field is maturing rapidly with industry leaders like TSMC, Intel, and AMD advancing heterogeneous integration techniques. Companies including Micron Technology, Samsung Electronics, and QUALCOMM are investing heavily in chiplet architectures that optimize power delivery networks and reduce resistance at interconnect points. Meanwhile, emerging players like AvicenaTech Corp. are developing innovative optical interconnect solutions to further enhance conduction efficiency between chiplets, signaling a shift toward more specialized integration approaches.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered advanced chiplet integration technologies through their 3DFabric platform, which combines multiple chiplets using their Chip-on-Wafer-on-Substrate (CoWoS) and System-on-Integrated-Chips (SoIC) technologies. Their approach focuses on minimizing electrical resistance at interconnect points between chiplets using micro-bumps and hybrid bonding techniques. TSMC's InFO (Integrated Fan-Out) packaging technology reduces the distance between chiplets, decreasing electrical resistance by up to 50% compared to traditional packaging methods. Their latest SoIC technology achieves sub-10 micron interconnect pitches with ultra-low resistance pathways, enabling power efficiency improvements of 25-30% in multi-chiplet designs. TSMC has also developed specialized Through-Silicon Via (TSV) implementations that reduce electrical resistance by using larger copper-filled vias with optimized geometries and materials to enhance conduction efficiency between stacked chiplets[1][2].

Strengths: Industry-leading interconnect density and ultra-fine pitch bonding capabilities; extensive manufacturing experience enabling high-yield production; comprehensive design ecosystem supporting heterogeneous integration. Weaknesses: Premium pricing structure limits accessibility for smaller companies; proprietary nature of some technologies creates vendor lock-in; requires specialized design approaches that increase development complexity.

Advanced Micro Devices, Inc.

Technical Solution: AMD has developed a comprehensive chiplet integration strategy centered around their AMD Infinity Architecture, which provides high-bandwidth, low-latency connections between multiple chiplets. Their approach uses an advanced organic substrate with optimized routing and specialized I/O dies that serve as interconnect hubs. AMD's Infinity Fabric interconnect technology implements a sophisticated power management system that dynamically adjusts voltage and frequency based on communication demands, reducing power consumption during idle periods while maintaining high performance when needed. Their 3rd generation EPYC processors demonstrate this technology with up to 64 cores across multiple chiplets, achieving up to 40% better energy efficiency compared to monolithic designs. AMD has also pioneered the use of through-silicon vias (TSVs) with optimized geometries and materials that reduce electrical resistance by approximately 35% compared to standard implementations. Their latest designs incorporate specialized metal layers and interface materials that minimize contact resistance between chiplets, further enhancing electrical conduction efficiency[3][4].

Strengths: Proven commercial implementation across multiple product generations; sophisticated power management capabilities that optimize energy usage; strong ecosystem support through industry partnerships. Weaknesses: Primarily focused on high-performance computing applications with less emphasis on ultra-low power scenarios; higher thermal density at interconnect points can create hotspots; requires sophisticated cooling solutions for maximum efficiency.

Core Innovations in Chiplet-to-Chiplet Interfaces

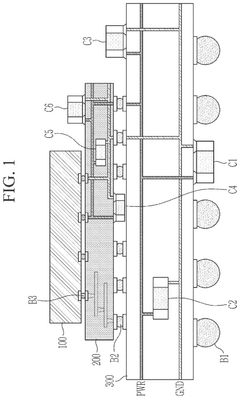

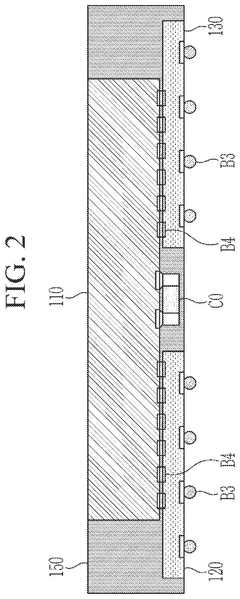

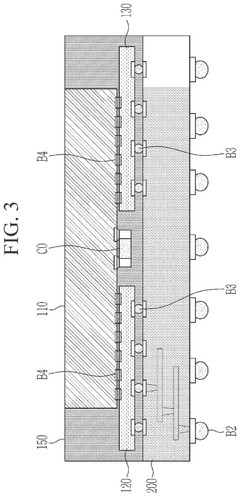

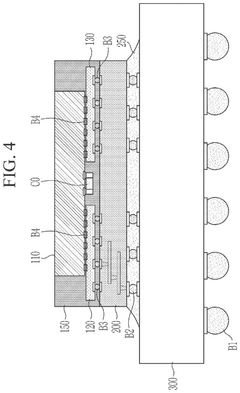

Semiconductor package with decoupling capacitor and method for manufacturing the same

PatentPendingUS20240332270A1

Innovation

- The implementation of chiplet technology to divide the semiconductor die into multiple dies, allowing for the placement of decoupling capacitors between these dies, ensuring they are closer to the active elements without reducing the number of input/output paths, and using hybrid bonding or solder bumps for connections.

Integrated circuits (ICS) having separate signal and power distribution network (PDN) interconnect structures for reduced power signal routing congestion and path lengths, and related three-dimensional (3D) ics (3DICS) and fabrication methods

PatentWO2025198849A1

Innovation

- The implementation of separate signal and power distribution network (PDN) interconnect structures within ICs, where the PDN interconnect structure is disposed on the opposite side of the semiconductor layer, allowing for reduced power signal routing path lengths and loop inductance, with decoupling capacitors integrated into the PDN interconnect structure for improved power noise filtering.

Thermal Management Strategies in Chiplet Architectures

Thermal management has emerged as a critical challenge in chiplet architectures, particularly when considering electricity conduction efficiency. As chiplets enable higher integration densities and more complex interconnects, heat generation and dissipation become significant limiting factors affecting overall system performance and reliability.

Traditional monolithic designs benefit from unified thermal management approaches, whereas chiplet-based systems present unique thermal challenges due to their disaggregated nature. The interface between chiplets creates thermal boundaries that can impede efficient heat transfer, potentially leading to hotspots and thermal gradients across the package.

Advanced thermal interface materials (TIMs) play a crucial role in addressing these challenges. High-performance TIMs with enhanced thermal conductivity properties are being developed specifically for chiplet applications, focusing on maintaining consistent performance across the numerous interfaces present in multi-chiplet packages. These materials must balance thermal conductivity with mechanical compliance to accommodate the different expansion coefficients of various chiplet components.

Liquid cooling solutions are increasingly being adapted for chiplet architectures, with direct-to-chiplet cooling techniques showing promising results. These approaches involve bringing cooling elements closer to heat sources, sometimes incorporating microfluidic channels directly into interposer structures or utilizing advanced cold plates designed to address the unique thermal profiles of chiplet packages.

Thermal-aware design methodologies have become essential in chiplet integration. This includes strategic placement of high-power chiplets to optimize heat spreading, incorporation of thermal vias and heat spreaders within interposers, and development of advanced packaging materials with superior thermal properties. Computational fluid dynamics (CFD) modeling specifically tailored for chiplet architectures helps predict thermal behavior and optimize designs before physical implementation.

Dynamic thermal management techniques are also evolving to address the unique characteristics of chiplet systems. These include chiplet-specific power gating, frequency scaling algorithms that consider the thermal interdependence between adjacent chiplets, and thermal-aware workload distribution that can shift processing tasks based on real-time thermal conditions across the package.

The industry is moving toward holistic thermal management approaches that consider the entire chiplet ecosystem, from die-level thermal design to system-level cooling solutions. This comprehensive strategy recognizes that electricity conduction efficiency in chiplet architectures is inextricably linked to thermal performance, requiring integrated solutions that address both electrical and thermal considerations simultaneously.

Traditional monolithic designs benefit from unified thermal management approaches, whereas chiplet-based systems present unique thermal challenges due to their disaggregated nature. The interface between chiplets creates thermal boundaries that can impede efficient heat transfer, potentially leading to hotspots and thermal gradients across the package.

Advanced thermal interface materials (TIMs) play a crucial role in addressing these challenges. High-performance TIMs with enhanced thermal conductivity properties are being developed specifically for chiplet applications, focusing on maintaining consistent performance across the numerous interfaces present in multi-chiplet packages. These materials must balance thermal conductivity with mechanical compliance to accommodate the different expansion coefficients of various chiplet components.

Liquid cooling solutions are increasingly being adapted for chiplet architectures, with direct-to-chiplet cooling techniques showing promising results. These approaches involve bringing cooling elements closer to heat sources, sometimes incorporating microfluidic channels directly into interposer structures or utilizing advanced cold plates designed to address the unique thermal profiles of chiplet packages.

Thermal-aware design methodologies have become essential in chiplet integration. This includes strategic placement of high-power chiplets to optimize heat spreading, incorporation of thermal vias and heat spreaders within interposers, and development of advanced packaging materials with superior thermal properties. Computational fluid dynamics (CFD) modeling specifically tailored for chiplet architectures helps predict thermal behavior and optimize designs before physical implementation.

Dynamic thermal management techniques are also evolving to address the unique characteristics of chiplet systems. These include chiplet-specific power gating, frequency scaling algorithms that consider the thermal interdependence between adjacent chiplets, and thermal-aware workload distribution that can shift processing tasks based on real-time thermal conditions across the package.

The industry is moving toward holistic thermal management approaches that consider the entire chiplet ecosystem, from die-level thermal design to system-level cooling solutions. This comprehensive strategy recognizes that electricity conduction efficiency in chiplet architectures is inextricably linked to thermal performance, requiring integrated solutions that address both electrical and thermal considerations simultaneously.

Standardization Efforts in Chiplet Integration Industry

The standardization landscape for chiplet integration has evolved significantly in recent years, driven by the critical need to improve electricity conduction efficiency across multi-die systems. Industry consortia like the Universal Chiplet Interconnect Express (UCIe) have emerged as pivotal forces in establishing common protocols for die-to-die interfaces, focusing particularly on signal integrity and power delivery optimization across chiplet boundaries.

UCIe specifications, released in 2022, represent a watershed moment in standardization efforts, defining both physical and protocol layers for chiplet interconnects with specific parameters for electrical conductivity. These standards address critical aspects including impedance matching, signal loss minimization, and power integrity across chiplet interfaces—all directly impacting electricity conduction efficiency.

Parallel to UCIe, the Open Compute Project's Bunch of Wires (BoW) specification offers an alternative approach to standardization, emphasizing simpler electrical interfaces that can achieve high energy efficiency for short-reach connections between chiplets. The Compute Express Link (CXL) consortium has extended its focus to include chiplet-specific protocols that maintain coherent memory access with minimal electrical overhead.

JEDEC and IEEE have also contributed significant standardization work, with JEDEC focusing on memory interface standards for chiplet designs and IEEE developing standards for test methodologies to verify electrical performance across chiplet boundaries. These efforts collectively address the challenge of maintaining signal integrity while minimizing power consumption in complex multi-die systems.

Regional standardization initiatives have emerged as well, with China's CCIX (Cache Coherent Interconnect for Accelerators) and Europe's European Processor Initiative developing region-specific standards that address electricity conduction requirements while considering local manufacturing capabilities and design priorities.

The industry has recognized that standardization must balance multiple competing factors: higher bandwidth demands require more power, yet thermal constraints and efficiency goals demand lower power consumption. This tension has led to tiered standards that offer different power-performance trade-offs for various application scenarios.

Looking forward, emerging standardization efforts are increasingly focusing on advanced packaging technologies like silicon interposers and bridge technologies, which fundamentally alter the electrical conduction characteristics between chiplets. These standards aim to define best practices for minimizing resistance and capacitance in inter-chiplet connections, ultimately enabling more efficient power delivery and signal transmission across the entire heterogeneous system.

UCIe specifications, released in 2022, represent a watershed moment in standardization efforts, defining both physical and protocol layers for chiplet interconnects with specific parameters for electrical conductivity. These standards address critical aspects including impedance matching, signal loss minimization, and power integrity across chiplet interfaces—all directly impacting electricity conduction efficiency.

Parallel to UCIe, the Open Compute Project's Bunch of Wires (BoW) specification offers an alternative approach to standardization, emphasizing simpler electrical interfaces that can achieve high energy efficiency for short-reach connections between chiplets. The Compute Express Link (CXL) consortium has extended its focus to include chiplet-specific protocols that maintain coherent memory access with minimal electrical overhead.

JEDEC and IEEE have also contributed significant standardization work, with JEDEC focusing on memory interface standards for chiplet designs and IEEE developing standards for test methodologies to verify electrical performance across chiplet boundaries. These efforts collectively address the challenge of maintaining signal integrity while minimizing power consumption in complex multi-die systems.

Regional standardization initiatives have emerged as well, with China's CCIX (Cache Coherent Interconnect for Accelerators) and Europe's European Processor Initiative developing region-specific standards that address electricity conduction requirements while considering local manufacturing capabilities and design priorities.

The industry has recognized that standardization must balance multiple competing factors: higher bandwidth demands require more power, yet thermal constraints and efficiency goals demand lower power consumption. This tension has led to tiered standards that offer different power-performance trade-offs for various application scenarios.

Looking forward, emerging standardization efforts are increasingly focusing on advanced packaging technologies like silicon interposers and bridge technologies, which fundamentally alter the electrical conduction characteristics between chiplets. These standards aim to define best practices for minimizing resistance and capacitance in inter-chiplet connections, ultimately enabling more efficient power delivery and signal transmission across the entire heterogeneous system.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!