What Are the Regulatory Challenges for Chiplet Integration Processes

OCT 15, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Integration Regulatory Landscape and Objectives

Chiplet integration technology has evolved significantly over the past decade, transforming from a theoretical concept to a practical solution for semiconductor scaling challenges. This evolution has been driven by the slowing of Moore's Law and the increasing costs associated with monolithic integration. The industry has witnessed a paradigm shift from traditional System-on-Chip (SoC) designs to more modular approaches that leverage chiplet architecture to overcome physical limitations in semiconductor manufacturing.

The regulatory landscape surrounding chiplet integration remains complex and fragmented globally. Different regions have established varying standards and compliance requirements, creating challenges for companies operating across international markets. In the United States, the Department of Commerce and Federal Communications Commission (FCC) oversee aspects of semiconductor technology deployment, while the European Union implements regulations through bodies like the European Telecommunications Standards Institute (ETSI) and various directives related to electronic components.

Asia-Pacific regions, particularly China, Japan, and South Korea, have developed their own regulatory frameworks, often with strategic national interests in mind. These disparate regulatory environments create significant compliance challenges for global chiplet deployment and integration processes. The lack of harmonized international standards specifically addressing chiplet integration further complicates the regulatory landscape.

Technical objectives in this domain focus on establishing standardized interfaces and protocols that can facilitate seamless integration while meeting regulatory requirements across jurisdictions. The DARPA CHIPS (Common Heterogeneous Integration and IP Reuse Strategies) program represents one significant initiative aimed at creating open standards for chiplet integration. Similarly, industry consortia like the Universal Chiplet Interconnect Express (UCIe) are working to develop specifications that could potentially become globally recognized standards.

The primary regulatory objectives include ensuring signal integrity across chiplet boundaries, managing thermal considerations in multi-die packages, and addressing security concerns related to the integration of components from multiple vendors. Additionally, regulatory frameworks must evolve to address novel reliability challenges unique to heterogeneous integration, including stress management at interfaces and long-term reliability of interconnects.

Looking forward, the industry aims to establish a more cohesive global regulatory framework that balances innovation with security concerns, particularly as chiplet technology becomes increasingly critical to computing infrastructure. This includes developing certification processes for chiplet compatibility, standardizing testing methodologies for integrated systems, and creating clear guidelines for intellectual property protection in multi-vendor chiplet ecosystems.

The regulatory landscape surrounding chiplet integration remains complex and fragmented globally. Different regions have established varying standards and compliance requirements, creating challenges for companies operating across international markets. In the United States, the Department of Commerce and Federal Communications Commission (FCC) oversee aspects of semiconductor technology deployment, while the European Union implements regulations through bodies like the European Telecommunications Standards Institute (ETSI) and various directives related to electronic components.

Asia-Pacific regions, particularly China, Japan, and South Korea, have developed their own regulatory frameworks, often with strategic national interests in mind. These disparate regulatory environments create significant compliance challenges for global chiplet deployment and integration processes. The lack of harmonized international standards specifically addressing chiplet integration further complicates the regulatory landscape.

Technical objectives in this domain focus on establishing standardized interfaces and protocols that can facilitate seamless integration while meeting regulatory requirements across jurisdictions. The DARPA CHIPS (Common Heterogeneous Integration and IP Reuse Strategies) program represents one significant initiative aimed at creating open standards for chiplet integration. Similarly, industry consortia like the Universal Chiplet Interconnect Express (UCIe) are working to develop specifications that could potentially become globally recognized standards.

The primary regulatory objectives include ensuring signal integrity across chiplet boundaries, managing thermal considerations in multi-die packages, and addressing security concerns related to the integration of components from multiple vendors. Additionally, regulatory frameworks must evolve to address novel reliability challenges unique to heterogeneous integration, including stress management at interfaces and long-term reliability of interconnects.

Looking forward, the industry aims to establish a more cohesive global regulatory framework that balances innovation with security concerns, particularly as chiplet technology becomes increasingly critical to computing infrastructure. This includes developing certification processes for chiplet compatibility, standardizing testing methodologies for integrated systems, and creating clear guidelines for intellectual property protection in multi-vendor chiplet ecosystems.

Market Demand Analysis for Chiplet Technology

The chiplet market is experiencing unprecedented growth driven by the increasing demand for advanced computing solutions across multiple sectors. As traditional monolithic chip designs reach their physical and economic limits, chiplet technology has emerged as a promising alternative that enables continued performance scaling while managing costs and manufacturing complexity. Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030, reflecting the industry's rapid transition toward this modular approach.

The primary market drivers for chiplet technology stem from several converging factors. Data centers and cloud service providers are seeking higher compute density and energy efficiency to handle exponentially growing workloads from artificial intelligence, machine learning, and big data applications. These applications require massive parallel processing capabilities that chiplets can deliver more effectively than traditional monolithic designs. Additionally, the automotive industry's shift toward autonomous driving and advanced driver assistance systems has created demand for high-performance, reliable computing platforms that can be customized for specific vehicle requirements.

Consumer electronics manufacturers are also embracing chiplet technology to deliver enhanced performance in smartphones, tablets, and wearable devices while maintaining competitive price points. The ability to mix and match chiplets from different process nodes allows companies to optimize cost-performance ratios and bring products to market more quickly. This flexibility is particularly valuable in the current semiconductor landscape, where supply chain disruptions have highlighted the risks of relying on single-source components.

From a geographical perspective, North America currently leads the chiplet market due to the concentration of major semiconductor companies and cloud service providers. However, Asia-Pacific is expected to witness the fastest growth, driven by substantial investments in semiconductor manufacturing infrastructure in countries like Taiwan, South Korea, and China. The European market is also expanding as regional initiatives aim to strengthen semiconductor sovereignty and reduce dependence on external suppliers.

The economic advantages of chiplet technology are compelling. By enabling the reuse of proven IP blocks and allowing different components to be manufactured using optimal process nodes, chiplets can reduce development costs by up to 30% compared to equivalent monolithic designs. Time-to-market can be shortened by 40-50%, providing significant competitive advantages in fast-evolving markets. These economics are driving adoption across both established semiconductor companies and emerging players, creating a diverse ecosystem of chiplet providers and integrators.

Despite this positive outlook, market adoption faces challenges related to standardization, testing methodologies, and supply chain coordination. The industry is actively addressing these issues through collaborative initiatives like the Universal Chiplet Interconnect Express (UCIe) consortium, which aims to establish common interfaces and protocols for chiplet integration.

The primary market drivers for chiplet technology stem from several converging factors. Data centers and cloud service providers are seeking higher compute density and energy efficiency to handle exponentially growing workloads from artificial intelligence, machine learning, and big data applications. These applications require massive parallel processing capabilities that chiplets can deliver more effectively than traditional monolithic designs. Additionally, the automotive industry's shift toward autonomous driving and advanced driver assistance systems has created demand for high-performance, reliable computing platforms that can be customized for specific vehicle requirements.

Consumer electronics manufacturers are also embracing chiplet technology to deliver enhanced performance in smartphones, tablets, and wearable devices while maintaining competitive price points. The ability to mix and match chiplets from different process nodes allows companies to optimize cost-performance ratios and bring products to market more quickly. This flexibility is particularly valuable in the current semiconductor landscape, where supply chain disruptions have highlighted the risks of relying on single-source components.

From a geographical perspective, North America currently leads the chiplet market due to the concentration of major semiconductor companies and cloud service providers. However, Asia-Pacific is expected to witness the fastest growth, driven by substantial investments in semiconductor manufacturing infrastructure in countries like Taiwan, South Korea, and China. The European market is also expanding as regional initiatives aim to strengthen semiconductor sovereignty and reduce dependence on external suppliers.

The economic advantages of chiplet technology are compelling. By enabling the reuse of proven IP blocks and allowing different components to be manufactured using optimal process nodes, chiplets can reduce development costs by up to 30% compared to equivalent monolithic designs. Time-to-market can be shortened by 40-50%, providing significant competitive advantages in fast-evolving markets. These economics are driving adoption across both established semiconductor companies and emerging players, creating a diverse ecosystem of chiplet providers and integrators.

Despite this positive outlook, market adoption faces challenges related to standardization, testing methodologies, and supply chain coordination. The industry is actively addressing these issues through collaborative initiatives like the Universal Chiplet Interconnect Express (UCIe) consortium, which aims to establish common interfaces and protocols for chiplet integration.

Global Regulatory Status and Technical Barriers

The global regulatory landscape for chiplet integration processes remains fragmented, with different regions establishing varying standards and compliance requirements. In the United States, the Department of Commerce has implemented export controls on advanced semiconductor technologies, including those related to chiplet integration, particularly targeting technologies that could have dual-use applications. These regulations have created significant barriers for international collaboration in chiplet development and manufacturing.

The European Union has established the European Chips Act, which includes provisions for chiplet technology standardization but lacks specific regulatory frameworks for integration processes. This regulatory gap creates uncertainty for companies operating in the EU market, as they must navigate a complex web of general semiconductor regulations without clear guidance on chiplet-specific compliance.

In Asia, regulatory approaches differ significantly between countries. Japan has implemented the Economic Security Promotion Act, which includes provisions for securing critical semiconductor supply chains, including chiplet technologies. South Korea has focused on incentivizing domestic chiplet development through regulatory exemptions rather than imposing strict controls. China has established its own regulatory framework through the "14th Five-Year Plan," emphasizing self-sufficiency in semiconductor technologies, including chiplet integration.

Technical barriers to regulatory compliance include the lack of standardized testing methodologies for chiplet interfaces. Without standardized testing protocols, companies struggle to demonstrate compliance with safety and performance regulations across different jurisdictions. This challenge is particularly acute for thermal management and signal integrity verification in multi-chiplet designs.

Intellectual property protection presents another significant regulatory challenge. The modular nature of chiplet designs often involves IP from multiple sources, creating complex cross-licensing requirements and potential export control complications. Different jurisdictions have varying approaches to IP protection in semiconductor technologies, leading to regulatory inconsistencies that impede global chiplet integration efforts.

Data security regulations also impact chiplet integration processes, particularly for designs intended for use in sensitive applications. Many countries have implemented regulations requiring security verification for semiconductor components used in critical infrastructure, but these requirements vary significantly and often lack chiplet-specific provisions.

The absence of global standards for chiplet integration creates technical barriers to market entry. While industry consortia like the Universal Chiplet Interconnect Express (UCIe) are working to establish standards, regulatory bodies have been slow to adopt these standards into formal compliance frameworks. This regulatory lag creates uncertainty for manufacturers and slows the broader adoption of chiplet technologies across global markets.

The European Union has established the European Chips Act, which includes provisions for chiplet technology standardization but lacks specific regulatory frameworks for integration processes. This regulatory gap creates uncertainty for companies operating in the EU market, as they must navigate a complex web of general semiconductor regulations without clear guidance on chiplet-specific compliance.

In Asia, regulatory approaches differ significantly between countries. Japan has implemented the Economic Security Promotion Act, which includes provisions for securing critical semiconductor supply chains, including chiplet technologies. South Korea has focused on incentivizing domestic chiplet development through regulatory exemptions rather than imposing strict controls. China has established its own regulatory framework through the "14th Five-Year Plan," emphasizing self-sufficiency in semiconductor technologies, including chiplet integration.

Technical barriers to regulatory compliance include the lack of standardized testing methodologies for chiplet interfaces. Without standardized testing protocols, companies struggle to demonstrate compliance with safety and performance regulations across different jurisdictions. This challenge is particularly acute for thermal management and signal integrity verification in multi-chiplet designs.

Intellectual property protection presents another significant regulatory challenge. The modular nature of chiplet designs often involves IP from multiple sources, creating complex cross-licensing requirements and potential export control complications. Different jurisdictions have varying approaches to IP protection in semiconductor technologies, leading to regulatory inconsistencies that impede global chiplet integration efforts.

Data security regulations also impact chiplet integration processes, particularly for designs intended for use in sensitive applications. Many countries have implemented regulations requiring security verification for semiconductor components used in critical infrastructure, but these requirements vary significantly and often lack chiplet-specific provisions.

The absence of global standards for chiplet integration creates technical barriers to market entry. While industry consortia like the Universal Chiplet Interconnect Express (UCIe) are working to establish standards, regulatory bodies have been slow to adopt these standards into formal compliance frameworks. This regulatory lag creates uncertainty for manufacturers and slows the broader adoption of chiplet technologies across global markets.

Current Compliance Solutions for Chiplet Integration

01 Regulatory compliance for chiplet integration

Chiplet integration processes face various regulatory challenges including compliance with international standards, certification requirements, and intellectual property protection. Companies must navigate complex regulatory frameworks that vary by region, ensuring their chiplet designs meet safety, electromagnetic compatibility, and environmental regulations. These regulatory hurdles can significantly impact time-to-market and implementation strategies for chiplet-based semiconductor products.- Regulatory compliance for chiplet integration: Chiplet integration processes face various regulatory challenges related to compliance with industry standards and government regulations. These challenges include ensuring that integrated chiplets meet safety, performance, and interoperability requirements across different jurisdictions. Companies must navigate complex regulatory frameworks that may vary by region, particularly for applications in sensitive sectors like telecommunications, healthcare, and defense. Compliance strategies often involve extensive documentation, testing protocols, and certification processes to demonstrate adherence to applicable regulations.

- Intellectual property management in chiplet ecosystems: Managing intellectual property rights presents significant regulatory challenges in chiplet integration. As chiplet technology involves components from multiple vendors being integrated into a single system, determining IP ownership, licensing requirements, and patent infringement risks becomes complex. Companies must develop comprehensive IP strategies that address cross-licensing agreements, patent pools, and standardization efforts. The fragmented nature of chiplet supply chains creates additional challenges for protecting proprietary technologies while enabling necessary interoperability between components from different manufacturers.

- Security and data protection requirements: Chiplet integration processes must address stringent security and data protection regulations, particularly for applications handling sensitive information. Regulatory challenges include implementing secure communication protocols between chiplets, preventing side-channel attacks at integration points, and ensuring data integrity across heterogeneous components. Manufacturers must design security features that comply with evolving regulations like GDPR, CCPA, and industry-specific requirements. This often necessitates specialized verification methodologies to validate security measures throughout the integration process and supply chain.

- Environmental and sustainability compliance: Chiplet integration faces regulatory challenges related to environmental sustainability and materials compliance. Regulations governing hazardous substances, electronic waste, and carbon footprint impact manufacturing processes and material selection for chiplet integration. Companies must navigate requirements like RoHS, REACH, and emerging circular economy regulations that affect packaging technologies, thermal management solutions, and end-of-life considerations. The modular nature of chiplets presents both opportunities and challenges for meeting sustainability goals through potential reuse and recycling of components.

- Standardization and interoperability challenges: The lack of universal standards for chiplet integration creates significant regulatory challenges. Different industry consortia and standard-setting organizations are developing competing or complementary specifications for chiplet interfaces, packaging, and testing methodologies. Manufacturers must navigate this fragmented landscape while ensuring their products maintain interoperability and meet performance requirements. Regulatory challenges include demonstrating compliance with emerging standards, participating in standards development processes, and managing the transition between different generations of standards as the technology evolves.

02 Thermal management and power regulation challenges

Chiplet integration introduces unique thermal management and power regulation challenges that must meet regulatory standards. The close proximity of multiple chiplets creates heat dissipation issues that require innovative cooling solutions. Power delivery networks must be designed to ensure stable voltage across all chiplets while complying with energy efficiency regulations. These thermal and power challenges are subject to strict regulatory oversight to prevent performance degradation and ensure reliability.Expand Specific Solutions03 Interoperability standards and testing protocols

Regulatory challenges exist in establishing and adhering to interoperability standards for chiplet integration. The semiconductor industry faces pressure to develop standardized interfaces and testing protocols that ensure chiplets from different manufacturers can work together seamlessly. Regulatory bodies are increasingly focused on promoting these standards to prevent market fragmentation and ensure compatibility. Companies must navigate evolving testing requirements to verify compliance with these interoperability standards.Expand Specific Solutions04 Security and data privacy compliance

Chiplet integration introduces complex security and data privacy challenges that must meet stringent regulatory requirements. The disaggregated nature of chiplet designs creates potential new attack vectors at the interfaces between chiplets. Manufacturers must implement security measures that comply with regulations like GDPR, CCPA, and industry-specific security standards. These measures include secure boot processes, encryption, and hardware-level security features to protect sensitive data processed across multiple chiplets.Expand Specific Solutions05 Supply chain verification and traceability requirements

Regulatory frameworks increasingly demand robust supply chain verification and traceability for chiplet integration processes. Manufacturers must document the origin and handling of each chiplet to comply with regulations aimed at preventing counterfeit components and ensuring national security. This includes maintaining detailed records of chiplet sources, manufacturing processes, and testing results. These traceability requirements are particularly stringent for applications in critical infrastructure, defense, and healthcare sectors.Expand Specific Solutions

Key Industry Players and Competitive Landscape

The chiplet integration regulatory landscape is evolving rapidly as the industry transitions from traditional monolithic designs to disaggregated architectures. Currently in the early growth phase, this market is expanding significantly due to increasing demand for heterogeneous integration solutions. Key players including TSMC, Intel, AMD, and GLOBALFOUNDRIES face regulatory challenges in standardization, intellectual property protection, export controls, and cross-border technology transfer. Companies like Qualcomm and Micron are navigating complex compliance requirements for chiplet interfaces and protocols. Technical maturity varies across players, with established semiconductor manufacturers having advanced capabilities while newer entrants like Chipletz and AvicenaTech focus on specialized integration technologies. The regulatory framework remains fragmented globally, creating compliance complexities for multinational operations.

Intel Corp.

Technical Solution: Intel has developed a comprehensive approach to chiplet integration regulatory challenges through their Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe) standards. Intel's strategy focuses on establishing open industry standards for chiplet-to-chiplet communication while addressing key regulatory concerns. Their approach includes implementing robust security protocols within the chiplet architecture to prevent unauthorized access and data breaches, which is critical for compliance with regulations like GDPR and CCPA. Intel has also developed specialized testing methodologies for multi-die packages that align with international quality standards and regulatory requirements. Their Embedded Multi-die Interconnect Bridge (EMIB) technology specifically addresses thermal management concerns that are subject to environmental regulations. Additionally, Intel actively participates in international standards bodies to help shape emerging regulations for chiplet technology, ensuring their solutions remain compliant across global markets while pushing for harmonized regulatory frameworks.

Strengths: Intel's leadership in establishing open industry standards like UCIe provides them significant influence in shaping regulatory frameworks. Their extensive experience with complex integration technologies gives them advanced compliance capabilities across multiple jurisdictions. Weaknesses: Their proprietary technologies may face additional scrutiny from competition regulators concerned about market dominance, and their complex supply chain increases exposure to evolving international trade regulations and export controls.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed a sophisticated approach to addressing chiplet integration regulatory challenges through their 3DFabric technology platform. This platform encompasses their Integrated Fan-Out (InFO), Chip-on-Wafer-on-Substrate (CoWoS), and System-on-Integrated-Chips (SoIC) technologies, each designed with regulatory compliance in mind. TSMC has implemented rigorous quality control systems that meet international standards like ISO 26262 for automotive applications and IEC 60601 for medical devices, ensuring their chiplet solutions comply with sector-specific regulations. Their approach includes comprehensive material compliance documentation to address RoHS, REACH, and other environmental regulations that impact semiconductor manufacturing. TSMC has also developed specialized testing protocols for heterogeneous integration that verify signal integrity across chiplet boundaries while meeting electromagnetic compatibility regulations. Additionally, they maintain detailed traceability systems throughout their manufacturing process to support product certification requirements in different jurisdictions, particularly important as chiplets may be manufactured in different locations subject to varying regulatory regimes.

Strengths: TSMC's advanced manufacturing capabilities enable precise control over integration processes, facilitating compliance with stringent quality and reliability standards. Their global presence and experience working with diverse regulatory frameworks provides adaptability to regional compliance requirements. Weaknesses: As a foundry, TSMC must navigate complex intellectual property protection challenges when integrating chiplets from multiple customers, and their position in geopolitically sensitive Taiwan creates additional regulatory complexity regarding export controls and trade restrictions.

Critical Patents and Technical Standards Analysis

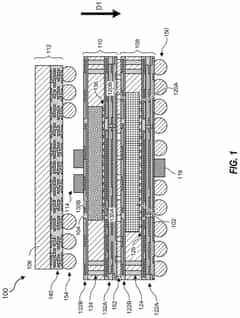

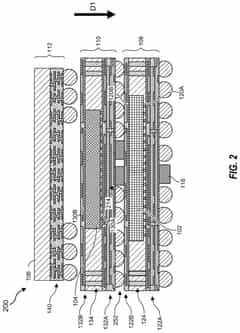

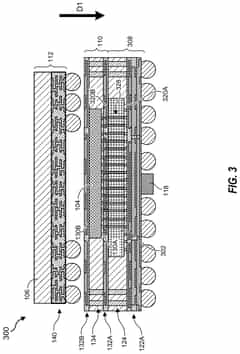

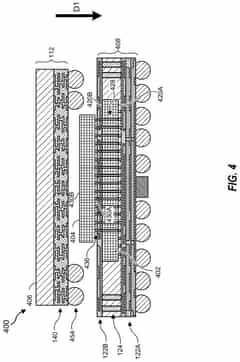

3D chiplet integration using fan-out wafer-level packaging

PatentPendingUS20240274587A1

Innovation

- The use of fan-out wafer-level packaging and three-dimensional packaging techniques for combining semiconductor chips and embedded memory in configurations such as face-to-back, back-to-back, and face-to-face orientations, enabling direct connections between chiplets and reducing assembly package sizes and manufacturing complexity.

Silicon bridge embedded fan-out packaging structure and packaging method thereof

PatentInactiveCN118737972A

Innovation

- Core pellets and silicon bridge chips using metal bumps of different heights are interconnected, and are protected by underfill and plastic sealing. Only single-sided wiring is required to achieve multi-core pellet interconnection, avoiding warpage problems caused by mismatched soldering temperatures and simplifying routing process and shortening the signal path through direct interconnection through micro-bumps.

Cross-Border Trade Implications for Chiplet Supply Chain

The global chiplet supply chain faces significant regulatory challenges that impact cross-border trade dynamics. As chiplet technology gains prominence in semiconductor manufacturing, regulatory frameworks across different jurisdictions create complex compliance requirements for companies operating internationally. The fragmented nature of chiplet production—where different components may be designed, manufactured, and integrated across multiple countries—amplifies these challenges.

Export control regulations represent a primary concern for chiplet supply chains. Countries increasingly classify advanced semiconductor technologies as strategic assets with dual-use potential, subjecting them to stringent export restrictions. The United States' Entity List restrictions, the Wassenaar Arrangement, and similar controls in other regions create a complex web of compliance requirements that chiplet manufacturers must navigate when shipping components across borders.

Tariff structures and trade agreements significantly impact the economics of chiplet integration. With components potentially crossing multiple borders before final assembly, cumulative tariffs can substantially increase production costs. The semiconductor industry faces particular challenges as trade tensions between major producing nations like the US, China, and Taiwan create uncertainty around future tariff policies and market access.

Technical standards and certification requirements vary considerably across regions, creating additional trade barriers. Chiplet manufacturers must ensure their products meet different regulatory specifications for electromagnetic compatibility, safety standards, and performance metrics in each target market. The lack of globally harmonized standards for chiplet interfaces and integration protocols further complicates cross-border trade.

Intellectual property protection presents another critical challenge. Chiplet designs often incorporate IP from multiple sources across different jurisdictions, each with varying levels of IP protection. Companies must navigate complex licensing agreements and patent landscapes while ensuring compliance with local IP laws in each market where chiplets are manufactured, integrated, or sold.

Data localization and cybersecurity regulations increasingly affect chiplet supply chains, particularly for components destined for sensitive applications. Many countries now require certain data to remain within their borders or mandate specific security protocols for hardware components, creating additional compliance burdens for international chiplet manufacturers.

The regulatory landscape for chiplet technology continues to evolve rapidly, with many jurisdictions developing new frameworks specifically targeting advanced semiconductor technologies. This regulatory uncertainty creates significant challenges for long-term supply chain planning and investment decisions in the chiplet ecosystem.

Export control regulations represent a primary concern for chiplet supply chains. Countries increasingly classify advanced semiconductor technologies as strategic assets with dual-use potential, subjecting them to stringent export restrictions. The United States' Entity List restrictions, the Wassenaar Arrangement, and similar controls in other regions create a complex web of compliance requirements that chiplet manufacturers must navigate when shipping components across borders.

Tariff structures and trade agreements significantly impact the economics of chiplet integration. With components potentially crossing multiple borders before final assembly, cumulative tariffs can substantially increase production costs. The semiconductor industry faces particular challenges as trade tensions between major producing nations like the US, China, and Taiwan create uncertainty around future tariff policies and market access.

Technical standards and certification requirements vary considerably across regions, creating additional trade barriers. Chiplet manufacturers must ensure their products meet different regulatory specifications for electromagnetic compatibility, safety standards, and performance metrics in each target market. The lack of globally harmonized standards for chiplet interfaces and integration protocols further complicates cross-border trade.

Intellectual property protection presents another critical challenge. Chiplet designs often incorporate IP from multiple sources across different jurisdictions, each with varying levels of IP protection. Companies must navigate complex licensing agreements and patent landscapes while ensuring compliance with local IP laws in each market where chiplets are manufactured, integrated, or sold.

Data localization and cybersecurity regulations increasingly affect chiplet supply chains, particularly for components destined for sensitive applications. Many countries now require certain data to remain within their borders or mandate specific security protocols for hardware components, creating additional compliance burdens for international chiplet manufacturers.

The regulatory landscape for chiplet technology continues to evolve rapidly, with many jurisdictions developing new frameworks specifically targeting advanced semiconductor technologies. This regulatory uncertainty creates significant challenges for long-term supply chain planning and investment decisions in the chiplet ecosystem.

Environmental and Sustainability Compliance Requirements

The environmental and sustainability compliance landscape for chiplet integration processes presents significant regulatory challenges for semiconductor manufacturers. As chiplet technology gains momentum, companies must navigate increasingly stringent requirements related to material usage, energy consumption, and end-of-life management.

Chiplet manufacturing involves complex processes that utilize various hazardous materials, including heavy metals and chemical compounds. Regulations such as the European Union's Restriction of Hazardous Substances (RoHS) Directive and Registration, Evaluation, Authorization, and Restriction of Chemicals (REACH) impose strict limitations on these substances. For chiplet integration specifically, the bonding materials and interconnect technologies must comply with these regulations while maintaining performance standards.

Energy efficiency requirements present another layer of compliance challenges. The European Ecodesign Directive and similar regulations worldwide mandate reduced energy consumption for electronic products. Chiplet integration processes must be optimized to minimize power consumption during both manufacturing and operation phases. This includes developing energy-efficient testing procedures and ensuring that the final integrated products meet energy rating standards across different jurisdictions.

Water usage and wastewater management regulations significantly impact chiplet manufacturing facilities. The semiconductor industry traditionally requires substantial water resources, and chiplet integration processes are no exception. Manufacturers must comply with local water quality standards and implement advanced water recycling systems to reduce consumption. In regions facing water scarcity, these requirements become particularly challenging and may influence facility location decisions.

Carbon footprint reduction targets are increasingly becoming regulatory requirements rather than voluntary initiatives. The EU Carbon Border Adjustment Mechanism and similar policies worldwide are pushing semiconductor manufacturers to measure, report, and reduce greenhouse gas emissions throughout the chiplet supply chain. This necessitates comprehensive life cycle assessments and carbon accounting systems specific to chiplet integration processes.

End-of-life considerations and circular economy principles are being incorporated into regulations such as the EU's Waste Electrical and Electronic Equipment (WEEE) Directive. Chiplet designs must account for eventual disassembly and material recovery, which presents unique challenges given the integrated nature of these components. Manufacturers must develop strategies for recycling or safely disposing of chiplet-based products while documenting compliance with extended producer responsibility requirements.

The global nature of semiconductor supply chains further complicates compliance efforts, as manufacturers must navigate varying and sometimes conflicting environmental regulations across different regions. This regulatory fragmentation increases compliance costs and may necessitate region-specific chiplet integration approaches to meet local sustainability requirements.

Chiplet manufacturing involves complex processes that utilize various hazardous materials, including heavy metals and chemical compounds. Regulations such as the European Union's Restriction of Hazardous Substances (RoHS) Directive and Registration, Evaluation, Authorization, and Restriction of Chemicals (REACH) impose strict limitations on these substances. For chiplet integration specifically, the bonding materials and interconnect technologies must comply with these regulations while maintaining performance standards.

Energy efficiency requirements present another layer of compliance challenges. The European Ecodesign Directive and similar regulations worldwide mandate reduced energy consumption for electronic products. Chiplet integration processes must be optimized to minimize power consumption during both manufacturing and operation phases. This includes developing energy-efficient testing procedures and ensuring that the final integrated products meet energy rating standards across different jurisdictions.

Water usage and wastewater management regulations significantly impact chiplet manufacturing facilities. The semiconductor industry traditionally requires substantial water resources, and chiplet integration processes are no exception. Manufacturers must comply with local water quality standards and implement advanced water recycling systems to reduce consumption. In regions facing water scarcity, these requirements become particularly challenging and may influence facility location decisions.

Carbon footprint reduction targets are increasingly becoming regulatory requirements rather than voluntary initiatives. The EU Carbon Border Adjustment Mechanism and similar policies worldwide are pushing semiconductor manufacturers to measure, report, and reduce greenhouse gas emissions throughout the chiplet supply chain. This necessitates comprehensive life cycle assessments and carbon accounting systems specific to chiplet integration processes.

End-of-life considerations and circular economy principles are being incorporated into regulations such as the EU's Waste Electrical and Electronic Equipment (WEEE) Directive. Chiplet designs must account for eventual disassembly and material recovery, which presents unique challenges given the integrated nature of these components. Manufacturers must develop strategies for recycling or safely disposing of chiplet-based products while documenting compliance with extended producer responsibility requirements.

The global nature of semiconductor supply chains further complicates compliance efforts, as manufacturers must navigate varying and sometimes conflicting environmental regulations across different regions. This regulatory fragmentation increases compliance costs and may necessitate region-specific chiplet integration approaches to meet local sustainability requirements.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!