Exploring the Legalities of Chiplet Integration Patenting

OCT 15, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Integration Patent Landscape and Objectives

Chiplet integration technology has evolved significantly over the past decade, transforming from a theoretical concept to a practical solution addressing the limitations of traditional monolithic chip designs. This evolution has been driven by the slowing of Moore's Law and the increasing challenges in semiconductor manufacturing at advanced nodes. The integration of smaller, specialized dies (chiplets) on a common substrate represents a paradigm shift in semiconductor architecture, enabling continued performance scaling while managing manufacturing costs and improving yields.

The patent landscape for chiplet integration has grown exponentially since 2015, with major semiconductor companies establishing strategic patent portfolios. Initially focused on physical integration methods, patents have expanded to cover interconnect technologies, thermal management solutions, and system-level optimization approaches. This rapid growth in patent filings indicates the industry's recognition of chiplet technology as a critical path forward for continued computing advancement.

The legal framework surrounding chiplet integration presents unique challenges due to the collaborative nature of the technology. Unlike traditional semiconductor patents that might cover a single manufacturing process or circuit design, chiplet integration often involves multiple entities and technologies working in concert. This creates complex questions regarding patent ownership, licensing requirements, and potential infringement scenarios across the supply chain.

Current objectives in the chiplet integration patent space focus on establishing clear boundaries for intellectual property protection while enabling industry-wide standardization. Organizations like the Universal Chiplet Interconnect Express (UCIe) consortium are working to develop open specifications that balance proprietary innovation with necessary interoperability. These efforts aim to prevent patent fragmentation that could impede industry-wide adoption.

The geographical distribution of chiplet integration patents reveals strategic positioning by different nations. The United States and Taiwan lead in interconnect and packaging technologies, while China has rapidly increased filings related to chiplet-based system architecture. European entities have focused on specialized applications in automotive and industrial sectors, creating distinct regional patent clusters.

Looking forward, the technical objectives for chiplet integration include developing standardized interfaces, improving die-to-die communication efficiency, and reducing power consumption at connection points. From a legal perspective, objectives include establishing clear patent pools, developing FRAND (Fair, Reasonable, And Non-Discriminatory) licensing frameworks, and creating mechanisms to navigate the complex web of intellectual property rights that will inevitably emerge as the technology matures.

The patent landscape for chiplet integration has grown exponentially since 2015, with major semiconductor companies establishing strategic patent portfolios. Initially focused on physical integration methods, patents have expanded to cover interconnect technologies, thermal management solutions, and system-level optimization approaches. This rapid growth in patent filings indicates the industry's recognition of chiplet technology as a critical path forward for continued computing advancement.

The legal framework surrounding chiplet integration presents unique challenges due to the collaborative nature of the technology. Unlike traditional semiconductor patents that might cover a single manufacturing process or circuit design, chiplet integration often involves multiple entities and technologies working in concert. This creates complex questions regarding patent ownership, licensing requirements, and potential infringement scenarios across the supply chain.

Current objectives in the chiplet integration patent space focus on establishing clear boundaries for intellectual property protection while enabling industry-wide standardization. Organizations like the Universal Chiplet Interconnect Express (UCIe) consortium are working to develop open specifications that balance proprietary innovation with necessary interoperability. These efforts aim to prevent patent fragmentation that could impede industry-wide adoption.

The geographical distribution of chiplet integration patents reveals strategic positioning by different nations. The United States and Taiwan lead in interconnect and packaging technologies, while China has rapidly increased filings related to chiplet-based system architecture. European entities have focused on specialized applications in automotive and industrial sectors, creating distinct regional patent clusters.

Looking forward, the technical objectives for chiplet integration include developing standardized interfaces, improving die-to-die communication efficiency, and reducing power consumption at connection points. From a legal perspective, objectives include establishing clear patent pools, developing FRAND (Fair, Reasonable, And Non-Discriminatory) licensing frameworks, and creating mechanisms to navigate the complex web of intellectual property rights that will inevitably emerge as the technology matures.

Market Demand Analysis for Chiplet Technology

The chiplet market is experiencing unprecedented growth, driven by the semiconductor industry's need to overcome the limitations of traditional monolithic chip designs. As Moore's Law faces physical constraints, chiplet technology has emerged as a strategic solution, allowing for the integration of multiple smaller dies into a single package. Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030, reaching significant market valuation by the end of the decade.

The primary demand drivers for chiplet technology stem from several converging factors. High-performance computing applications, including artificial intelligence and machine learning systems, require increasingly powerful processors that traditional monolithic designs struggle to deliver cost-effectively. Data centers are another major demand source, as they seek more efficient and scalable computing solutions to handle exponentially growing data processing requirements.

Consumer electronics manufacturers are also showing strong interest in chiplet technology, particularly for next-generation smartphones, tablets, and IoT devices that demand higher performance within strict power and space constraints. The automotive sector represents an emerging market, with advanced driver-assistance systems and autonomous vehicles requiring sophisticated computing capabilities that chiplet architectures can efficiently provide.

From a geographical perspective, North America currently leads the chiplet market demand, with major technology companies investing heavily in research and development. The Asia-Pacific region, particularly Taiwan, South Korea, and China, is rapidly expanding its chiplet manufacturing capabilities and market share, driven by government initiatives and private sector investments in semiconductor technology.

The patent landscape for chiplet integration is becoming increasingly complex and crowded. Companies are racing to secure intellectual property rights for various aspects of chiplet design, manufacturing, and integration techniques. This has created a significant market for licensing agreements and technology partnerships, as few organizations possess all the necessary patents to implement complete chiplet solutions independently.

Supply chain considerations are also shaping market demand dynamics. The chiplet approach allows for more distributed manufacturing processes, potentially alleviating some supply chain bottlenecks that have plagued the semiconductor industry. However, it introduces new challenges in testing, assembly, and quality control that market participants must address.

Customer demand is increasingly focused on standardization of chiplet interfaces and protocols, which would enable more flexible integration of components from different manufacturers. This standardization effort, led by consortia like the Universal Chiplet Interconnect Express (UCIe), is expected to accelerate market adoption and expand the ecosystem of chiplet suppliers and integrators.

The primary demand drivers for chiplet technology stem from several converging factors. High-performance computing applications, including artificial intelligence and machine learning systems, require increasingly powerful processors that traditional monolithic designs struggle to deliver cost-effectively. Data centers are another major demand source, as they seek more efficient and scalable computing solutions to handle exponentially growing data processing requirements.

Consumer electronics manufacturers are also showing strong interest in chiplet technology, particularly for next-generation smartphones, tablets, and IoT devices that demand higher performance within strict power and space constraints. The automotive sector represents an emerging market, with advanced driver-assistance systems and autonomous vehicles requiring sophisticated computing capabilities that chiplet architectures can efficiently provide.

From a geographical perspective, North America currently leads the chiplet market demand, with major technology companies investing heavily in research and development. The Asia-Pacific region, particularly Taiwan, South Korea, and China, is rapidly expanding its chiplet manufacturing capabilities and market share, driven by government initiatives and private sector investments in semiconductor technology.

The patent landscape for chiplet integration is becoming increasingly complex and crowded. Companies are racing to secure intellectual property rights for various aspects of chiplet design, manufacturing, and integration techniques. This has created a significant market for licensing agreements and technology partnerships, as few organizations possess all the necessary patents to implement complete chiplet solutions independently.

Supply chain considerations are also shaping market demand dynamics. The chiplet approach allows for more distributed manufacturing processes, potentially alleviating some supply chain bottlenecks that have plagued the semiconductor industry. However, it introduces new challenges in testing, assembly, and quality control that market participants must address.

Customer demand is increasingly focused on standardization of chiplet interfaces and protocols, which would enable more flexible integration of components from different manufacturers. This standardization effort, led by consortia like the Universal Chiplet Interconnect Express (UCIe), is expected to accelerate market adoption and expand the ecosystem of chiplet suppliers and integrators.

Global Chiplet Patent Status and Challenges

The global chiplet patent landscape is experiencing rapid evolution, with significant regional disparities in patent activity and protection strategies. North America, particularly the United States, currently leads in chiplet-related patent filings, with major semiconductor companies like Intel, AMD, and TSMC holding substantial portfolios. These patents primarily cover integration methodologies, interconnect technologies, and testing procedures for heterogeneous integration.

Asia follows closely, with Taiwan, South Korea, and increasingly China demonstrating aggressive patent filing strategies. Japanese companies have focused more on specialized interconnect technologies, while European entities have concentrated on system-level integration patents and standardization efforts. This geographic distribution reflects both technological capabilities and strategic business interests in the semiconductor value chain.

A critical challenge in the chiplet patent ecosystem is the emergence of "patent thickets" – dense webs of overlapping intellectual property rights that companies must navigate to commercialize new technologies. These thickets are particularly problematic in interface technologies and die-to-die communication protocols, where multiple companies claim foundational IP. The lack of standardized interfaces further complicates this landscape, creating potential barriers to market entry for smaller players.

Legal uncertainties regarding the patentability of chiplet integration methods present another significant hurdle. Different jurisdictions apply varying standards for what constitutes a patentable innovation versus an obvious combination of known elements. This creates inconsistent protection globally and increases litigation risks for companies operating across multiple markets.

Cross-licensing has emerged as a common strategy to navigate these challenges, with major players establishing complex agreements to enable technology development while protecting their IP positions. However, these arrangements often exclude smaller innovators who lack substantial patent portfolios to negotiate favorable terms.

Standard-essential patents (SEPs) represent another contentious area, as chiplet technology increasingly requires standardization for widespread adoption. Determining fair, reasonable, and non-discriminatory (FRAND) licensing terms for these patents remains challenging, with potential for anti-competitive behavior by dominant market players.

The enforcement landscape also varies significantly across regions, with some jurisdictions offering more robust protection than others. This creates strategic considerations for where companies choose to file patents and how they structure their global IP strategies. Additionally, the rapid pace of innovation often outstrips the patent examination process, leading to uncertainty about the validity and scope of granted patents in this emerging field.

Asia follows closely, with Taiwan, South Korea, and increasingly China demonstrating aggressive patent filing strategies. Japanese companies have focused more on specialized interconnect technologies, while European entities have concentrated on system-level integration patents and standardization efforts. This geographic distribution reflects both technological capabilities and strategic business interests in the semiconductor value chain.

A critical challenge in the chiplet patent ecosystem is the emergence of "patent thickets" – dense webs of overlapping intellectual property rights that companies must navigate to commercialize new technologies. These thickets are particularly problematic in interface technologies and die-to-die communication protocols, where multiple companies claim foundational IP. The lack of standardized interfaces further complicates this landscape, creating potential barriers to market entry for smaller players.

Legal uncertainties regarding the patentability of chiplet integration methods present another significant hurdle. Different jurisdictions apply varying standards for what constitutes a patentable innovation versus an obvious combination of known elements. This creates inconsistent protection globally and increases litigation risks for companies operating across multiple markets.

Cross-licensing has emerged as a common strategy to navigate these challenges, with major players establishing complex agreements to enable technology development while protecting their IP positions. However, these arrangements often exclude smaller innovators who lack substantial patent portfolios to negotiate favorable terms.

Standard-essential patents (SEPs) represent another contentious area, as chiplet technology increasingly requires standardization for widespread adoption. Determining fair, reasonable, and non-discriminatory (FRAND) licensing terms for these patents remains challenging, with potential for anti-competitive behavior by dominant market players.

The enforcement landscape also varies significantly across regions, with some jurisdictions offering more robust protection than others. This creates strategic considerations for where companies choose to file patents and how they structure their global IP strategies. Additionally, the rapid pace of innovation often outstrips the patent examination process, leading to uncertainty about the validity and scope of granted patents in this emerging field.

Current Patenting Strategies for Chiplet Integration

01 Legal frameworks for chiplet IP protection

Legal frameworks governing intellectual property rights for chiplet integration technologies are evolving to address the unique challenges of multi-die architectures. These frameworks establish guidelines for protecting innovations in chiplet design, interconnection methods, and integration techniques. Companies developing chiplet technologies must navigate complex IP landscapes to secure protection for their innovations while avoiding infringement of existing patents.- Legal frameworks for chiplet IP protection: The legal protection of intellectual property in chiplet integration involves specific frameworks that address the unique challenges of this modular approach. These frameworks cover how companies can protect their innovations in chiplet design, integration methods, and interconnect technologies. The legal considerations include patent eligibility criteria for chiplet-based systems, enforcement strategies for chiplet-specific IP, and jurisdictional differences in how chiplet technologies are protected under patent law.

- Cross-licensing and patent pooling for chiplet technologies: As chiplet integration often involves components from multiple vendors, cross-licensing agreements and patent pooling have emerged as important legal mechanisms in the industry. These arrangements allow companies to share intellectual property rights while maintaining competitive advantages. The legal structures of these agreements address issues such as royalty distribution, licensing terms for standard-essential patents in chiplet interfaces, and collaborative development frameworks that enable innovation while respecting proprietary technologies.

- Standardization and interoperability legal issues: The development of industry standards for chiplet interfaces raises significant legal questions regarding interoperability, fair use, and antitrust considerations. Legal frameworks are evolving to address how standard-essential patents should be licensed on fair, reasonable, and non-discriminatory terms. These legal structures balance the need for technological standardization with the protection of proprietary innovations, while addressing potential antitrust concerns when major industry players collaborate on chiplet interface standards.

- Patent enforcement challenges for chiplet integration: Enforcing patents in the chiplet ecosystem presents unique challenges due to the distributed nature of design and manufacturing. Legal considerations include determining liability when infringement occurs across multiple components from different vendors, establishing jurisdiction when chiplet supply chains span multiple countries, and developing appropriate remedies that address the modular nature of chiplet-based systems. Courts are developing new approaches to handle these complex cases involving multiple parties and technologies.

- Emerging legal trends in chiplet manufacturing and packaging: New legal frameworks are developing to address the unique aspects of advanced packaging and manufacturing methods used in chiplet integration. These include legal protections for novel interconnect technologies, thermal management solutions, and testing methodologies specific to chiplet-based systems. Patent strategies are evolving to cover manufacturing processes, packaging techniques, and system-level integration approaches that enable effective chiplet implementation while navigating the complex landscape of existing semiconductor patents.

02 Cross-licensing and patent pooling for chiplet standards

As chiplet integration becomes more standardized, cross-licensing agreements and patent pooling strategies are emerging as important legal mechanisms. These collaborative approaches allow multiple companies to share intellectual property related to chiplet interfaces and integration technologies, facilitating industry-wide adoption while ensuring fair compensation for innovators. Standard-essential patents for chiplet technologies often require special licensing considerations to promote interoperability.Expand Specific Solutions03 Territorial patent considerations for global chiplet supply chains

Chiplet integration involves global supply chains with design, manufacturing, and assembly potentially occurring across multiple jurisdictions. This creates complex territorial patent considerations where different legal systems may apply at various stages of the chiplet lifecycle. Companies must develop comprehensive international patent strategies to protect their innovations across all relevant territories while navigating different enforcement mechanisms and legal requirements.Expand Specific Solutions04 Patent eligibility challenges for chiplet integration methods

Determining patent eligibility for chiplet integration methods presents unique challenges as these innovations often combine hardware design with software elements. Courts and patent offices continue to refine guidelines for what constitutes patentable subject matter in this domain. Innovations that demonstrate technical improvements in chiplet communication, thermal management, or power distribution may face different eligibility considerations than purely abstract integration concepts.Expand Specific Solutions05 Infringement detection and enforcement strategies

The complex nature of chiplet integration creates challenges for detecting and enforcing patent infringement. Determining whether a multi-die product infringes on chiplet integration patents often requires sophisticated technical analysis and reverse engineering. Companies are developing specialized enforcement strategies including advanced detection methods and licensing programs specifically designed for chiplet technologies to protect their intellectual property investments.Expand Specific Solutions

Key Industry Players in Chiplet Patent Ecosystem

The chiplet integration patenting landscape is evolving rapidly in a growth-stage market projected to reach significant scale as heterogeneous integration becomes critical for semiconductor advancement. The competitive field features established players like Intel, AMD, and TSMC leading commercial implementation, while research institutions such as University of California contribute foundational IP. Technical maturity varies significantly: TSMC and Intel have advanced packaging technologies (CoWoS, EMIB), AMD has commercialized chiplet architectures in high-performance processors, and GlobalFoundries offers specialized integration services. The legal framework remains complex with cross-licensing becoming increasingly important as companies like Micron, Infineon, and Texas Instruments develop complementary technologies, creating a patent ecosystem where strategic IP positioning determines competitive advantage in this emerging semiconductor paradigm.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced packaging technologies like Chip-on-Wafer-on-Substrate (CoWoS) and Integrated Fan-Out (InFO) that enable sophisticated chiplet integration. Their legal approach to chiplet integration patenting focuses on manufacturing processes and integration techniques rather than chiplet designs themselves. TSMC has built a substantial patent portfolio covering the fabrication methods, testing procedures, and quality control processes specific to multi-die integration. Their System-on-Integrated-Chips (SoIC) technology, which enables 3D stacking of chiplets with micron-scale interconnects, is protected by numerous patents covering the manufacturing processes, materials, and testing methodologies[5]. TSMC strategically patents the equipment modifications and process innovations required for high-yield chiplet manufacturing while working with customers through collaborative development agreements that carefully delineate IP ownership. Their approach includes cross-licensing agreements with key partners to ensure freedom to operate while protecting their core manufacturing innovations.

Strengths: Extensive patent portfolio focused on manufacturing processes gives TSMC control over critical production technologies; position as a foundry allows collection of valuable cross-industry implementation data; strong relationships with multiple chiplet designers. Weaknesses: Limited control over chiplet design patents; potential exposure to patent disputes between competing customers using similar chiplet approaches; challenges in maintaining manufacturing process secrecy while pursuing patent protection.

Intel Corp.

Technical Solution: Intel has pioneered the Embedded Multi-die Interconnect Bridge (EMIB) technology for chiplet integration, which allows for high-bandwidth connections between chiplets in a package without using expensive silicon interposers. Their approach includes a comprehensive patent strategy covering both the physical integration methods and the communication protocols between chiplets. Intel's Advanced Interface Bus (AIB) serves as an open standard for die-to-die communication, which they've strategically patented while also making available through licensing to foster ecosystem development. Intel has filed numerous patents covering various aspects of chiplet design, manufacturing, and integration, creating a robust intellectual property portfolio that protects their innovations while enabling selective collaboration through their licensing programs[1][3]. Their legal approach balances proprietary technology protection with industry standardization efforts through the Universal Chiplet Interconnect Express (UCIe) consortium.

Strengths: Strong existing patent portfolio in chiplet technology; established licensing framework that balances IP protection with ecosystem development; leadership in industry standardization efforts. Weaknesses: Potential antitrust concerns due to market dominance; challenges in enforcing patents across global jurisdictions with different IP protection standards; risk of patent thickets inhibiting broader industry innovation.

Critical Patent Analysis for Chiplet Technologies

Techniques for Modular Chip Fabrication

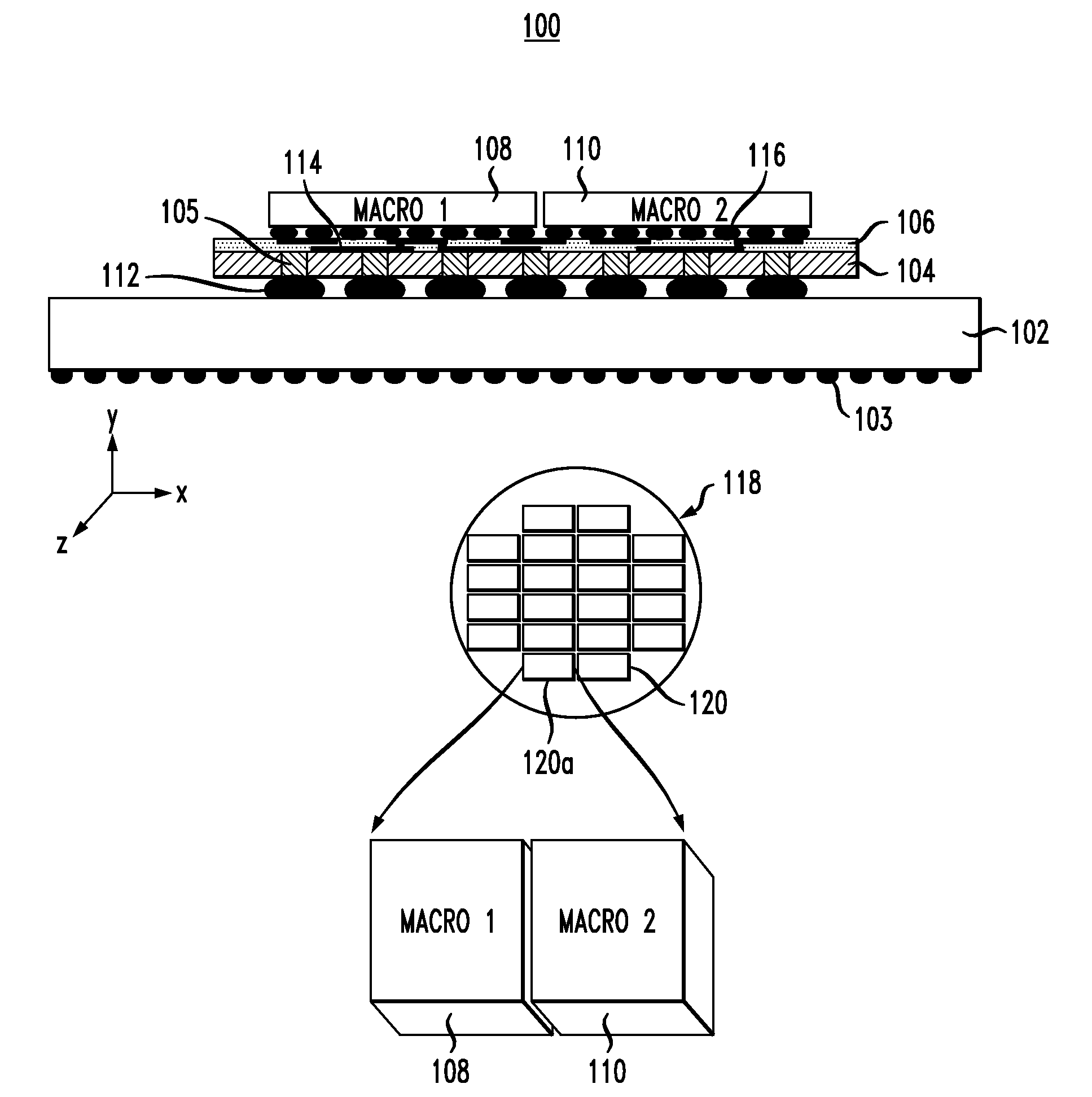

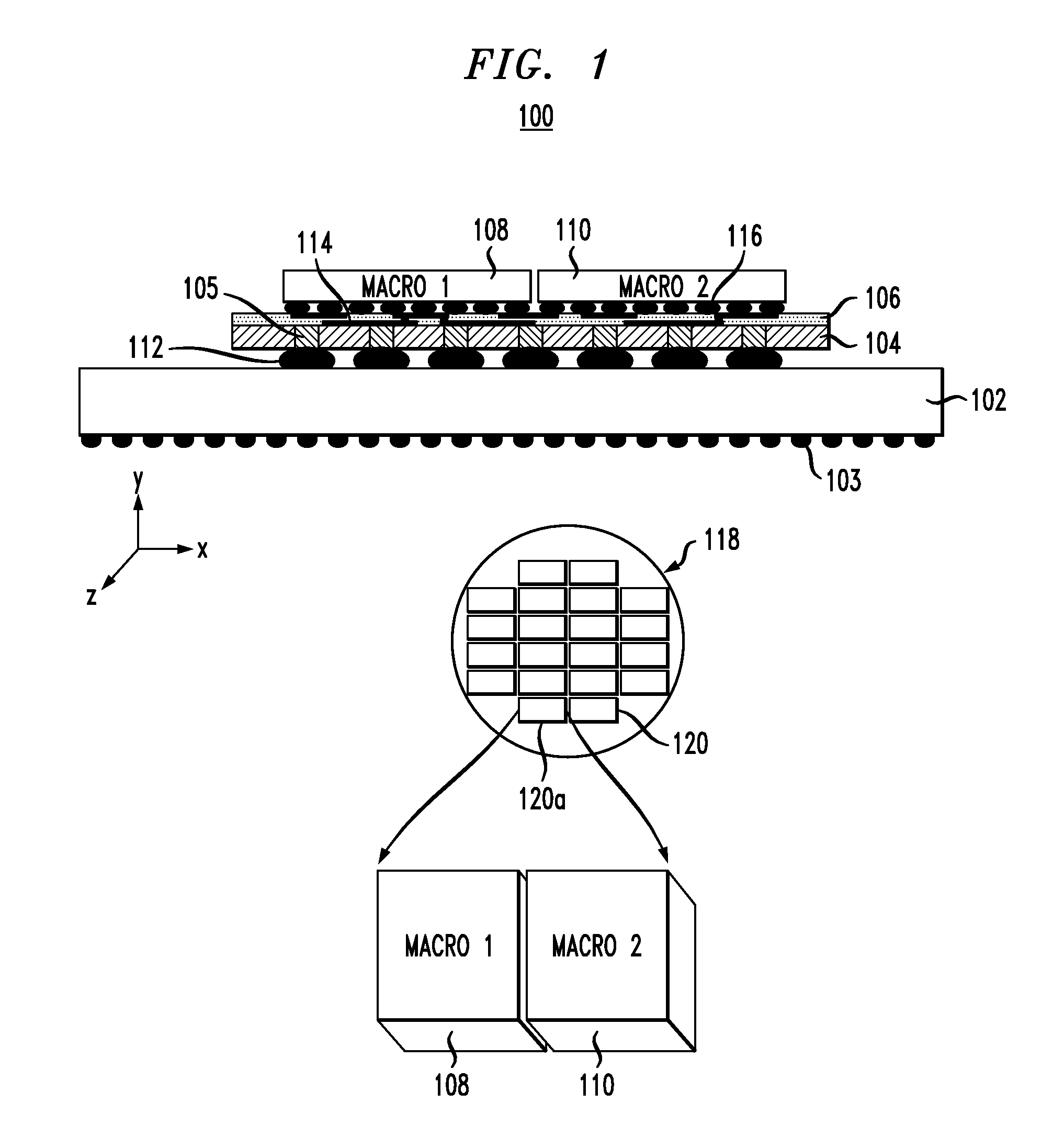

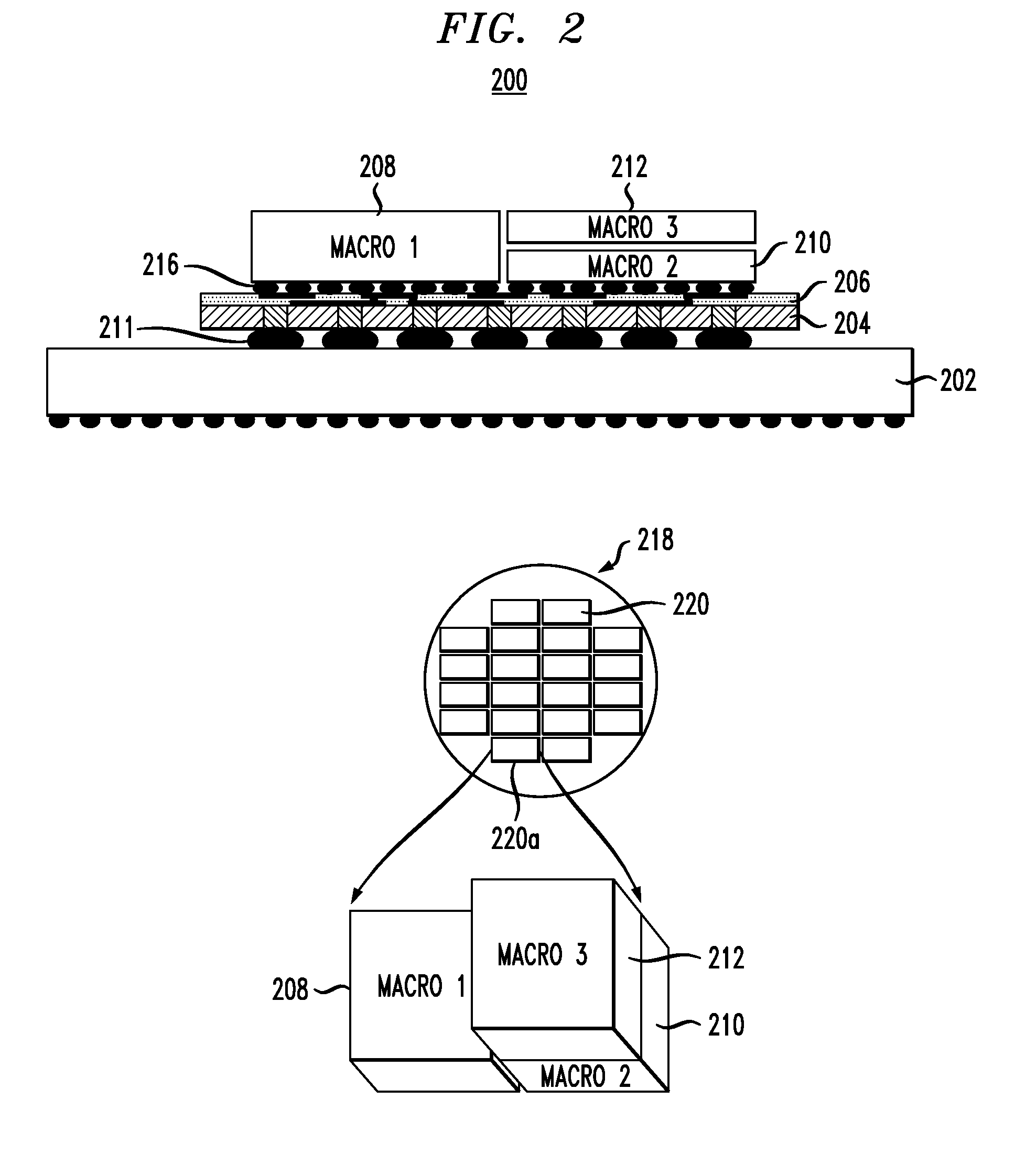

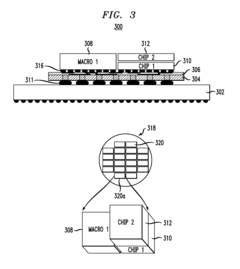

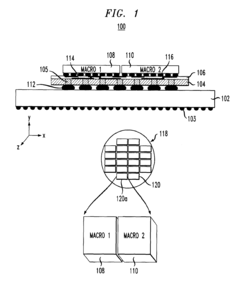

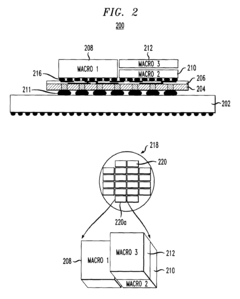

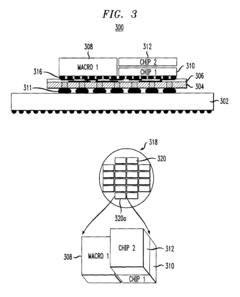

PatentActiveUS20090108427A1

Innovation

- A modular chip structure and method that include a substrate, a carrier platform with conductive vias and a wiring layer configured to divide into voltage islands, allowing for the integration of pre-designed chip circuits and macros from different semiconductor technology nodes, enabling heterogeneous chip technology integration and reducing power requirements.

Techniques for modular chip fabrication

PatentActiveUS8288866B2

Innovation

- A modular chip structure and fabrication method that includes a substrate, a carrier platform with conductive vias and a wiring layer configured to divide into voltage islands, allowing integration of pre-designed chip circuits and macros from different semiconductor nodes, enabling heterogeneous chip technology integration and reducing power requirements.

Cross-Licensing and Patent Pooling Opportunities

Cross-licensing and patent pooling represent strategic approaches to navigating the complex intellectual property landscape surrounding chiplet integration technologies. As the semiconductor industry increasingly adopts modular chiplet architectures, companies face significant challenges in managing the fragmented patent ecosystem. Cross-licensing agreements enable two or more companies to exchange patent rights, allowing each party to utilize the other's protected technologies without infringement concerns, which is particularly valuable in chiplet integration where multiple proprietary technologies must seamlessly interact.

Patent pooling extends this concept to a broader consortium model, where multiple patent holders contribute their relevant intellectual property to a collective licensing framework. This approach has gained traction in the chiplet domain as it simplifies access to essential technologies while reducing transaction costs and litigation risks. Notable examples include the CHIPS Alliance and the Open Compute Project, which have established collaborative frameworks for chiplet-related intellectual property sharing.

The economic benefits of these collaborative IP models are substantial. Research indicates that companies participating in chiplet-related patent pools can reduce licensing costs by approximately 35-40% compared to negotiating individual licenses. Furthermore, these arrangements accelerate time-to-market by eliminating protracted bilateral negotiations and reducing legal uncertainties that might otherwise delay product development cycles.

For emerging players in the chiplet space, these collaborative mechanisms provide crucial access to foundational technologies that would otherwise present insurmountable barriers to entry. Established semiconductor giants like Intel, AMD, and TSMC have increasingly recognized the strategic value of selective participation in cross-licensing and patent pooling initiatives, particularly for interface standards and interconnect technologies that benefit from industry-wide adoption.

Legal frameworks supporting these collaborative models continue to evolve. Recent developments in antitrust guidelines have clarified the permissible scope of patent pools, addressing concerns about potential anti-competitive effects while preserving innovation incentives. The European Commission's 2023 guidelines specifically acknowledge the pro-competitive benefits of technology sharing in semiconductor manufacturing, providing greater certainty for chiplet-focused collaborative arrangements.

Looking forward, the industry is likely to witness the emergence of specialized chiplet patent pools organized around specific technological domains such as die-to-die interfaces, thermal management solutions, and packaging methodologies. These focused pools will enable more efficient technology transfer while maintaining appropriate competitive boundaries between market participants.

Patent pooling extends this concept to a broader consortium model, where multiple patent holders contribute their relevant intellectual property to a collective licensing framework. This approach has gained traction in the chiplet domain as it simplifies access to essential technologies while reducing transaction costs and litigation risks. Notable examples include the CHIPS Alliance and the Open Compute Project, which have established collaborative frameworks for chiplet-related intellectual property sharing.

The economic benefits of these collaborative IP models are substantial. Research indicates that companies participating in chiplet-related patent pools can reduce licensing costs by approximately 35-40% compared to negotiating individual licenses. Furthermore, these arrangements accelerate time-to-market by eliminating protracted bilateral negotiations and reducing legal uncertainties that might otherwise delay product development cycles.

For emerging players in the chiplet space, these collaborative mechanisms provide crucial access to foundational technologies that would otherwise present insurmountable barriers to entry. Established semiconductor giants like Intel, AMD, and TSMC have increasingly recognized the strategic value of selective participation in cross-licensing and patent pooling initiatives, particularly for interface standards and interconnect technologies that benefit from industry-wide adoption.

Legal frameworks supporting these collaborative models continue to evolve. Recent developments in antitrust guidelines have clarified the permissible scope of patent pools, addressing concerns about potential anti-competitive effects while preserving innovation incentives. The European Commission's 2023 guidelines specifically acknowledge the pro-competitive benefits of technology sharing in semiconductor manufacturing, providing greater certainty for chiplet-focused collaborative arrangements.

Looking forward, the industry is likely to witness the emergence of specialized chiplet patent pools organized around specific technological domains such as die-to-die interfaces, thermal management solutions, and packaging methodologies. These focused pools will enable more efficient technology transfer while maintaining appropriate competitive boundaries between market participants.

International IP Law Implications for Chiplets

The global nature of semiconductor supply chains and the increasing adoption of chiplet technology present unique challenges in the international intellectual property landscape. Different jurisdictions maintain varying approaches to patent protection, creating a complex web of legal considerations for companies developing chiplet-based solutions. The Patent Cooperation Treaty (PCT) offers some standardization, but significant regional differences persist in how semiconductor IP is protected and enforced.

In the United States, the USPTO has established specific guidelines for chiplet-related patents, focusing on the novelty of integration methods rather than the individual components. This contrasts with the European Patent Office's approach, which places greater emphasis on the technical effect of the integration and may consider chiplet arrangements as potentially unpatentable if deemed "obvious to try" by skilled practitioners in the field.

Asian markets present further complexity, with China's rapid expansion of semiconductor patent filings creating new competitive pressures. Japan and South Korea maintain robust protection systems but differ in their treatment of chiplet integration techniques versus the underlying technologies. Taiwan, as a critical manufacturing hub, has developed specialized IP frameworks that recognize the unique position of foundries in the chiplet ecosystem.

Cross-border enforcement remains particularly challenging for chiplet technologies due to their distributed nature. When different components are manufactured in various jurisdictions and then integrated elsewhere, determining the location of infringement becomes legally complex. This has led to the emergence of specialized licensing frameworks such as the Universal Chiplet Interconnect Express (UCIe) consortium, which aims to standardize both technical interfaces and IP licensing terms.

Trade secret protection has gained renewed importance for chiplet integration, particularly for manufacturing processes that may be difficult to reverse-engineer from the final product. Companies increasingly employ hybrid protection strategies, using patents for visible integration techniques while maintaining trade secret protection for proprietary manufacturing methods.

The fragmentation of international IP regimes creates strategic opportunities but also significant risks. Companies must navigate these differences through careful portfolio management, considering where to file patents based not only on market importance but also on the strength of enforcement mechanisms and the specific legal treatment of chiplet technologies in each jurisdiction.

In the United States, the USPTO has established specific guidelines for chiplet-related patents, focusing on the novelty of integration methods rather than the individual components. This contrasts with the European Patent Office's approach, which places greater emphasis on the technical effect of the integration and may consider chiplet arrangements as potentially unpatentable if deemed "obvious to try" by skilled practitioners in the field.

Asian markets present further complexity, with China's rapid expansion of semiconductor patent filings creating new competitive pressures. Japan and South Korea maintain robust protection systems but differ in their treatment of chiplet integration techniques versus the underlying technologies. Taiwan, as a critical manufacturing hub, has developed specialized IP frameworks that recognize the unique position of foundries in the chiplet ecosystem.

Cross-border enforcement remains particularly challenging for chiplet technologies due to their distributed nature. When different components are manufactured in various jurisdictions and then integrated elsewhere, determining the location of infringement becomes legally complex. This has led to the emergence of specialized licensing frameworks such as the Universal Chiplet Interconnect Express (UCIe) consortium, which aims to standardize both technical interfaces and IP licensing terms.

Trade secret protection has gained renewed importance for chiplet integration, particularly for manufacturing processes that may be difficult to reverse-engineer from the final product. Companies increasingly employ hybrid protection strategies, using patents for visible integration techniques while maintaining trade secret protection for proprietary manufacturing methods.

The fragmentation of international IP regimes creates strategic opportunities but also significant risks. Companies must navigate these differences through careful portfolio management, considering where to file patents based not only on market importance but also on the strength of enforcement mechanisms and the specific legal treatment of chiplet technologies in each jurisdiction.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!