How Chiplet Integration Addresses Aerospace Industry Challenges

OCT 15, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Technology Evolution in Aerospace Applications

The evolution of chiplet technology in aerospace applications represents a significant paradigm shift in how complex aerospace systems are designed and manufactured. Initially emerging in the consumer electronics sector around 2017-2018, chiplet architecture has rapidly gained traction in aerospace applications due to its inherent advantages in addressing the sector's unique challenges.

In the early stages (2018-2020), aerospace manufacturers began exploring chiplet technology primarily as a means to overcome the limitations of monolithic chip designs. Traditional single-die approaches were increasingly unable to meet the demanding requirements of modern aerospace systems, particularly regarding radiation hardening, thermal management, and long-term reliability in extreme environments.

By 2020-2021, the technology witnessed accelerated adoption as aerospace companies recognized the potential of heterogeneous integration. This approach allowed for combining different process nodes and specialized functions on a single package, enabling the integration of radiation-hardened components alongside high-performance computing elements without compromising overall system integrity.

The period from 2021 to 2023 marked a significant maturation phase, with the development of aerospace-specific chiplet standards and interconnect technologies. Industry consortia established specialized protocols for chiplet-to-chiplet communication that addressed the stringent reliability requirements of aerospace applications, including redundancy mechanisms and error correction capabilities far exceeding commercial standards.

Recent developments (2023-present) have focused on advanced packaging technologies specifically designed for aerospace environments. These include specialized interposers capable of withstanding extreme temperature fluctuations, vacuum conditions, and radiation exposure while maintaining high-speed, low-latency communication between chiplets.

The technology roadmap has evolved from simple multi-chip modules to sophisticated 2.5D and 3D integration approaches. Current state-of-the-art implementations utilize silicon interposers with through-silicon vias (TSVs) and advanced die-to-die interfaces that maintain signal integrity under the harsh conditions encountered in aerospace applications.

Looking forward, the trajectory points toward even greater specialization, with chiplet designs specifically optimized for satellite constellations, deep space missions, and advanced avionics systems. The modular nature of chiplet architecture aligns perfectly with the aerospace industry's need for scalable, upgradable systems with extended operational lifespans, allowing for incremental improvements without complete system redesigns.

This evolution represents not just a technical advancement but a fundamental shift in aerospace system design philosophy—moving from monolithic, highly customized solutions toward more flexible, modular architectures that can adapt to changing mission requirements while maintaining the exceptional reliability standards demanded by the aerospace sector.

In the early stages (2018-2020), aerospace manufacturers began exploring chiplet technology primarily as a means to overcome the limitations of monolithic chip designs. Traditional single-die approaches were increasingly unable to meet the demanding requirements of modern aerospace systems, particularly regarding radiation hardening, thermal management, and long-term reliability in extreme environments.

By 2020-2021, the technology witnessed accelerated adoption as aerospace companies recognized the potential of heterogeneous integration. This approach allowed for combining different process nodes and specialized functions on a single package, enabling the integration of radiation-hardened components alongside high-performance computing elements without compromising overall system integrity.

The period from 2021 to 2023 marked a significant maturation phase, with the development of aerospace-specific chiplet standards and interconnect technologies. Industry consortia established specialized protocols for chiplet-to-chiplet communication that addressed the stringent reliability requirements of aerospace applications, including redundancy mechanisms and error correction capabilities far exceeding commercial standards.

Recent developments (2023-present) have focused on advanced packaging technologies specifically designed for aerospace environments. These include specialized interposers capable of withstanding extreme temperature fluctuations, vacuum conditions, and radiation exposure while maintaining high-speed, low-latency communication between chiplets.

The technology roadmap has evolved from simple multi-chip modules to sophisticated 2.5D and 3D integration approaches. Current state-of-the-art implementations utilize silicon interposers with through-silicon vias (TSVs) and advanced die-to-die interfaces that maintain signal integrity under the harsh conditions encountered in aerospace applications.

Looking forward, the trajectory points toward even greater specialization, with chiplet designs specifically optimized for satellite constellations, deep space missions, and advanced avionics systems. The modular nature of chiplet architecture aligns perfectly with the aerospace industry's need for scalable, upgradable systems with extended operational lifespans, allowing for incremental improvements without complete system redesigns.

This evolution represents not just a technical advancement but a fundamental shift in aerospace system design philosophy—moving from monolithic, highly customized solutions toward more flexible, modular architectures that can adapt to changing mission requirements while maintaining the exceptional reliability standards demanded by the aerospace sector.

Market Demand Analysis for Advanced Aerospace Computing

The aerospace industry is experiencing unprecedented demand for advanced computing solutions, driven by the increasing complexity of aerospace systems and the need for higher performance in harsh environments. Market analysis indicates that the global aerospace computing market is projected to grow at a compound annual growth rate of 5.8% from 2023 to 2030, reaching a value of 8.7 billion USD by the end of the forecast period. This growth is primarily fueled by the rising adoption of autonomous systems, artificial intelligence, and real-time data processing capabilities in modern aircraft and spacecraft.

Military aerospace applications represent the largest market segment, accounting for approximately 42% of the total market share. This dominance stems from increasing defense budgets worldwide and the growing emphasis on network-centric warfare capabilities that require sophisticated computing systems. Commercial aviation follows closely, with a market share of 35%, driven by the need for more efficient flight management systems, enhanced safety features, and passenger entertainment solutions.

Space exploration and satellite systems constitute the fastest-growing segment, with an annual growth rate of 7.3%. This acceleration is attributed to the proliferation of small satellite constellations, deep space missions, and the emergence of private space companies investing heavily in advanced computing infrastructure. The demand for radiation-hardened computing solutions capable of withstanding the harsh conditions of space is particularly strong in this segment.

Geographically, North America leads the market with a 38% share, followed by Europe (27%) and Asia-Pacific (24%). However, the Asia-Pacific region is expected to witness the highest growth rate due to increasing investments in aerospace technology by countries like China, India, and Japan, along with the expansion of their space programs and defense capabilities.

Key market drivers include the need for higher computational density, reduced size, weight, and power consumption (SWaP), enhanced reliability in extreme environments, and improved thermal management. Traditional monolithic system-on-chip designs are increasingly unable to meet these demanding requirements, creating a significant market gap that chiplet-based solutions are well-positioned to address.

Industry surveys indicate that 78% of aerospace system designers cite computing performance limitations as a major constraint in implementing next-generation capabilities. Additionally, 65% report challenges related to thermal management in confined spaces, while 82% express concerns about long-term reliability in radiation-exposed environments. These pain points represent critical market opportunities for chiplet integration technologies that can deliver modular, scalable, and radiation-tolerant computing solutions.

Military aerospace applications represent the largest market segment, accounting for approximately 42% of the total market share. This dominance stems from increasing defense budgets worldwide and the growing emphasis on network-centric warfare capabilities that require sophisticated computing systems. Commercial aviation follows closely, with a market share of 35%, driven by the need for more efficient flight management systems, enhanced safety features, and passenger entertainment solutions.

Space exploration and satellite systems constitute the fastest-growing segment, with an annual growth rate of 7.3%. This acceleration is attributed to the proliferation of small satellite constellations, deep space missions, and the emergence of private space companies investing heavily in advanced computing infrastructure. The demand for radiation-hardened computing solutions capable of withstanding the harsh conditions of space is particularly strong in this segment.

Geographically, North America leads the market with a 38% share, followed by Europe (27%) and Asia-Pacific (24%). However, the Asia-Pacific region is expected to witness the highest growth rate due to increasing investments in aerospace technology by countries like China, India, and Japan, along with the expansion of their space programs and defense capabilities.

Key market drivers include the need for higher computational density, reduced size, weight, and power consumption (SWaP), enhanced reliability in extreme environments, and improved thermal management. Traditional monolithic system-on-chip designs are increasingly unable to meet these demanding requirements, creating a significant market gap that chiplet-based solutions are well-positioned to address.

Industry surveys indicate that 78% of aerospace system designers cite computing performance limitations as a major constraint in implementing next-generation capabilities. Additionally, 65% report challenges related to thermal management in confined spaces, while 82% express concerns about long-term reliability in radiation-exposed environments. These pain points represent critical market opportunities for chiplet integration technologies that can deliver modular, scalable, and radiation-tolerant computing solutions.

Current Challenges and Limitations in Aerospace Chiplet Integration

Despite the promising potential of chiplet integration in aerospace applications, several significant challenges and limitations currently impede its widespread adoption. The harsh operating environment of aerospace systems presents unique constraints that conventional chiplet solutions struggle to address. Extreme temperature variations, from the sub-zero conditions at high altitudes to the intense heat generated during operation, place extraordinary demands on interconnect reliability and thermal management systems that exceed commercial chiplet design parameters.

Radiation hardening remains a critical concern, as aerospace electronics must withstand cosmic radiation and solar flares that can cause single-event upsets, latchups, and cumulative damage effects. Current chiplet integration approaches often lack sufficient radiation tolerance, requiring additional shielding or redundancy mechanisms that increase weight and complexity—both particularly problematic in aerospace applications where every gram matters.

The reliability requirements for aerospace systems significantly exceed those of commercial applications, with expected operational lifespans of 15-25 years without maintenance opportunities. This longevity requirement challenges current chiplet integration technologies, which have not been validated for such extended service periods in extreme environments. Interconnect technologies between chiplets, particularly those using micro-bumps and through-silicon vias (TSVs), face reliability concerns under the constant thermal cycling and vibration typical in aerospace operations.

Power efficiency presents another substantial hurdle. While chiplets offer theoretical power advantages through specialized silicon, the current integration approaches often introduce power overhead at interconnect boundaries. For aerospace systems with strict power budgets, these inefficiencies can be prohibitive, especially in satellite applications where power generation is severely limited.

Testing and verification methodologies for chiplet-based systems remain inadequate for aerospace standards. The complex interactions between multiple chiplets from potentially different vendors complicate fault isolation and comprehensive testing. Current known-good-die testing approaches do not fully address the unique failure modes that can emerge at the system level in aerospace environments.

Supply chain security and assurance pose significant challenges as well. The aerospace industry requires stringent traceability and authentication of components, which becomes exponentially more complex in multi-vendor chiplet ecosystems. The risk of counterfeit components or security vulnerabilities increases with the number of suppliers involved in a chiplet-based system.

Standardization efforts for chiplet interfaces, while progressing in commercial sectors, have not adequately addressed aerospace-specific requirements. The lack of industry-wide standards tailored to aerospace applications creates interoperability issues and limits the potential ecosystem benefits that chiplet integration could otherwise deliver.

Radiation hardening remains a critical concern, as aerospace electronics must withstand cosmic radiation and solar flares that can cause single-event upsets, latchups, and cumulative damage effects. Current chiplet integration approaches often lack sufficient radiation tolerance, requiring additional shielding or redundancy mechanisms that increase weight and complexity—both particularly problematic in aerospace applications where every gram matters.

The reliability requirements for aerospace systems significantly exceed those of commercial applications, with expected operational lifespans of 15-25 years without maintenance opportunities. This longevity requirement challenges current chiplet integration technologies, which have not been validated for such extended service periods in extreme environments. Interconnect technologies between chiplets, particularly those using micro-bumps and through-silicon vias (TSVs), face reliability concerns under the constant thermal cycling and vibration typical in aerospace operations.

Power efficiency presents another substantial hurdle. While chiplets offer theoretical power advantages through specialized silicon, the current integration approaches often introduce power overhead at interconnect boundaries. For aerospace systems with strict power budgets, these inefficiencies can be prohibitive, especially in satellite applications where power generation is severely limited.

Testing and verification methodologies for chiplet-based systems remain inadequate for aerospace standards. The complex interactions between multiple chiplets from potentially different vendors complicate fault isolation and comprehensive testing. Current known-good-die testing approaches do not fully address the unique failure modes that can emerge at the system level in aerospace environments.

Supply chain security and assurance pose significant challenges as well. The aerospace industry requires stringent traceability and authentication of components, which becomes exponentially more complex in multi-vendor chiplet ecosystems. The risk of counterfeit components or security vulnerabilities increases with the number of suppliers involved in a chiplet-based system.

Standardization efforts for chiplet interfaces, while progressing in commercial sectors, have not adequately addressed aerospace-specific requirements. The lack of industry-wide standards tailored to aerospace applications creates interoperability issues and limits the potential ecosystem benefits that chiplet integration could otherwise deliver.

Existing Chiplet Integration Solutions for Harsh Environments

01 Interconnect technologies for chiplet integration

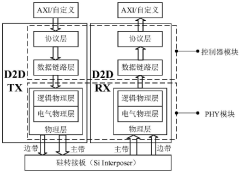

Various interconnect technologies are used to connect multiple chiplets in a package. These include advanced micro-bump technologies, through-silicon vias (TSVs), and bridge interconnects that enable high-bandwidth, low-latency communication between chiplets. These interconnect solutions address the challenges of signal integrity, power delivery, and thermal management in multi-chiplet designs, allowing for efficient data transfer between different functional blocks.- Advanced Packaging Technologies for Chiplet Integration: Various packaging technologies are employed to integrate chiplets effectively, including 2.5D and 3D integration approaches. These technologies enable the connection of multiple chiplets on a common substrate or interposer, allowing for high-bandwidth, low-latency communication between different functional blocks. Advanced packaging solutions address thermal management challenges and provide improved electrical performance while maintaining compact form factors for complex semiconductor systems.

- Interconnect Architectures for Chiplet Communication: Specialized interconnect architectures facilitate efficient communication between chiplets in multi-die systems. These include high-speed die-to-die interfaces, through-silicon vias (TSVs), and advanced bus architectures that support the bandwidth requirements of modern computing applications. The interconnect solutions are designed to minimize latency, reduce power consumption, and maintain signal integrity across chiplet boundaries, enabling seamless integration of heterogeneous components.

- Thermal Management Solutions for Chiplet Designs: Effective thermal management is critical in chiplet-based systems due to the high power density and potential hotspots created by stacking or closely placing multiple dies. Innovative cooling solutions include integrated heat spreaders, microchannel cooling systems, and advanced thermal interface materials specifically designed for chiplet architectures. These thermal management approaches ensure reliable operation and optimal performance of integrated chiplet systems under various workload conditions.

- Testing and Validation Methodologies for Chiplet Systems: Specialized testing and validation methodologies are developed to ensure the functionality and reliability of chiplet-based systems. These include known-good-die testing before integration, built-in self-test capabilities, and post-assembly validation techniques. The testing approaches address the unique challenges of verifying interconnects between chiplets and ensuring system-level performance meets specifications, while maintaining manufacturing yield and cost-effectiveness.

- Design Automation and Optimization for Chiplet Integration: Advanced design automation tools and methodologies support the complex process of chiplet integration. These include specialized electronic design automation (EDA) tools for multi-die systems, optimization algorithms for chiplet placement and routing, and design frameworks that address the unique challenges of heterogeneous integration. The design automation approaches enable efficient partitioning of system functionality across multiple chiplets while optimizing for performance, power, and area constraints.

02 Packaging technologies for chiplet integration

Advanced packaging technologies are essential for chiplet integration, including 2.5D and 3D packaging approaches. These technologies involve stacking or placing chiplets side by side on interposers or substrates. Fan-out wafer-level packaging and embedded multi-die interconnect bridge technologies enable higher integration density and improved performance while managing thermal issues and mechanical stress in heterogeneous integration scenarios.Expand Specific Solutions03 Design methodologies for chiplet-based systems

Specialized design methodologies are required for chiplet-based systems, including partitioning strategies, interface standardization, and design-for-test approaches. These methodologies address the challenges of integrating chiplets from different process nodes or manufacturers. Design tools and frameworks support the optimization of chiplet placement, power distribution, and thermal management to achieve desired system performance while maintaining manufacturability and reliability.Expand Specific Solutions04 Heterogeneous integration of chiplets

Heterogeneous integration involves combining chiplets manufactured using different process technologies or from different vendors. This approach allows for optimizing each component for its specific function, such as integrating memory chiplets with processor chiplets or analog with digital components. The integration enables system-level optimization while leveraging the best manufacturing process for each component, resulting in improved performance, power efficiency, and cost-effectiveness.Expand Specific Solutions05 Testing and validation methods for chiplet-based systems

Specialized testing and validation methods are required for chiplet-based systems to ensure proper functionality and reliability. These include pre-integration testing of individual chiplets, interface validation, and system-level testing after integration. Known-good-die testing, boundary scan techniques, and built-in self-test mechanisms help identify defects early in the manufacturing process. Post-assembly testing verifies proper communication between chiplets and overall system performance under various operating conditions.Expand Specific Solutions

Leading Aerospace and Semiconductor Industry Players

Chiplet integration is emerging as a critical solution for aerospace industry challenges, currently in the early growth phase with an estimated market size of $5-7 billion and projected to expand significantly by 2030. The technology is approaching maturity with leading semiconductor companies like TSMC, Intel, and AMD driving innovation in chiplet design and integration. Aerospace specialists including Boeing, Airbus, and Safran are adapting these technologies for high-reliability applications. Military contractors such as BAE Systems and research institutions like Naval Research Laboratory are developing radiation-hardened chiplet solutions. The ecosystem is evolving with specialized packaging providers like STATS ChipPAC and ASE Group supporting the unique requirements of aerospace applications, creating a competitive landscape that balances commercial semiconductor innovation with aerospace-specific reliability demands.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC's chiplet integration solution for aerospace applications centers on their advanced packaging technologies, particularly their Integrated Fan-Out (InFO) and System on Integrated Chips (SoIC) platforms. These technologies enable the integration of heterogeneous chiplets manufactured at different process nodes, allowing aerospace systems to combine radiation-hardened control logic with high-performance computing elements. TSMC has developed specialized through-silicon via (TSV) technology optimized for aerospace reliability requirements, featuring redundant connections and enhanced mechanical stability to withstand vibration and thermal cycling. Their CoWoS (Chip-on-Wafer-on-Substrate) platform has been adapted for aerospace applications with enhanced thermal dissipation capabilities and specialized underfill materials that maintain integrity in extreme temperature environments[3]. TSMC also offers customized testing protocols for aerospace chiplets that simulate radiation exposure, vacuum conditions, and thermal extremes to ensure reliability in space applications.

Strengths: World-leading semiconductor manufacturing capabilities; extensive experience with heterogeneous integration; advanced packaging technologies with proven reliability. Weaknesses: Limited direct aerospace industry experience compared to dedicated aerospace suppliers; primarily focused on manufacturing rather than complete aerospace system design.

Intel Corp.

Technical Solution: Intel's chiplet integration approach for aerospace applications centers around their Advanced Interface Bus (AIB) and Embedded Multi-die Interconnect Bridge (EMIB) technologies. Their solution enables heterogeneous integration of multiple silicon dies in a single package, allowing aerospace systems to combine specialized processing elements (CPUs, FPGAs, memory) while maintaining high-bandwidth, low-latency connections between them. Intel's Agilex FPGA family specifically leverages chiplet technology to deliver reconfigurable computing solutions that address the aerospace industry's need for radiation-hardened, high-performance computing in space-constrained environments. Their chiplets are designed with redundancy features and error correction capabilities critical for aerospace reliability requirements[1]. Intel has also developed specialized packaging techniques that enhance thermal management for aerospace applications where traditional cooling methods are limited.

Strengths: Industry-leading interconnect technology with proven reliability in harsh environments; extensive ecosystem support; advanced packaging expertise for thermal management. Weaknesses: Higher power consumption compared to some competitors; less experience specifically in aerospace-qualified components compared to dedicated aerospace suppliers.

Key Innovations in Radiation-Hardened Chiplet Technology

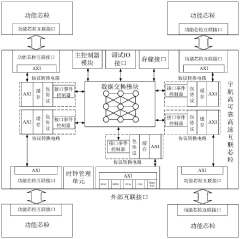

Astronavigation high-reliability high-speed interconnection core particle

PatentPendingCN117785783A

Innovation

- An aerospace high-reliability and high-speed interconnection core solution including functional core interconnection interface, external interconnection interface, protocol conversion circuit, data exchange module, clock management module, storage interface, debugging IO interface and main controller module is designed, using RS -SPC cascade code encoding and network-on-chip NoC structure realize cross-clock domain data transmission and high-reliability interconnection.

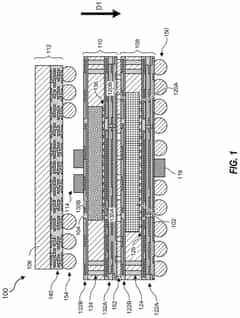

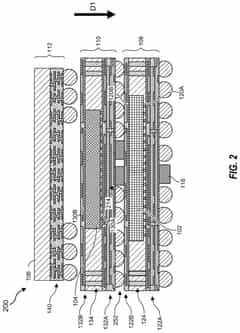

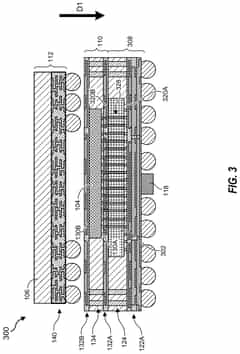

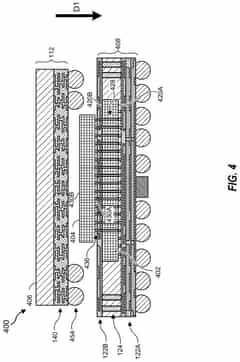

3D chiplet integration using fan-out wafer-level packaging

PatentPendingUS20240274587A1

Innovation

- The use of fan-out wafer-level packaging and three-dimensional packaging techniques for combining semiconductor chips and embedded memory in configurations such as face-to-back, back-to-back, and face-to-face orientations, enabling direct connections between chiplets and reducing assembly package sizes and manufacturing complexity.

Reliability and Certification Standards for Aerospace Electronics

The aerospace industry imposes exceptionally stringent reliability requirements on electronic components due to the extreme operating conditions and critical safety implications. Chiplet integration must adhere to these standards to be viable for aerospace applications. The DO-254 (Design Assurance Guidance for Airborne Electronic Hardware) and MIL-STD-883 (Test Methods and Procedures for Microelectronics) represent foundational certification frameworks that any chiplet-based solution must satisfy.

Reliability testing for aerospace chiplet integration encompasses extensive environmental stress screening, including thermal cycling (-65°C to +150°C), vibration testing, radiation hardening assessment, and accelerated life testing. These procedures are significantly more rigorous than those applied to commercial electronics, requiring chiplet designs to demonstrate functionality under extreme conditions while maintaining performance integrity.

Certification pathways for chiplet-based systems present unique challenges due to their modular nature. Traditional monolithic certification approaches must be adapted to address the interfaces between chiplets, requiring comprehensive documentation of each chiplet's design, manufacturing process, and testing results. The industry is currently developing specialized verification methodologies for heterogeneous integration that can satisfy aerospace certification requirements.

Fault tolerance mechanisms are particularly critical for chiplet designs in aerospace applications. Redundancy strategies at both the chiplet and system levels must be implemented, including triple modular redundancy (TMR) for critical functions and error detection and correction (EDAC) capabilities for data integrity. The distributed nature of chiplet architectures offers potential advantages for implementing sophisticated fault isolation techniques that can contain failures within individual chiplets.

Mean Time Between Failures (MTBF) requirements for aerospace electronics typically exceed 100,000 hours, necessitating exceptional quality control throughout the chiplet manufacturing and integration process. This includes stringent die-level testing before integration, comprehensive inspection of interconnects, and hermetic packaging to prevent environmental contamination.

The certification process for chiplet-based aerospace systems requires collaboration between chiplet suppliers, system integrators, and certification authorities. This collaborative approach must establish clear traceability from requirements to implementation and verification, with particular attention to interface specifications between chiplets. Industry consortia are working to standardize certification methodologies specifically for chiplet-based aerospace systems, potentially reducing certification timelines while maintaining rigorous safety standards.

Reliability testing for aerospace chiplet integration encompasses extensive environmental stress screening, including thermal cycling (-65°C to +150°C), vibration testing, radiation hardening assessment, and accelerated life testing. These procedures are significantly more rigorous than those applied to commercial electronics, requiring chiplet designs to demonstrate functionality under extreme conditions while maintaining performance integrity.

Certification pathways for chiplet-based systems present unique challenges due to their modular nature. Traditional monolithic certification approaches must be adapted to address the interfaces between chiplets, requiring comprehensive documentation of each chiplet's design, manufacturing process, and testing results. The industry is currently developing specialized verification methodologies for heterogeneous integration that can satisfy aerospace certification requirements.

Fault tolerance mechanisms are particularly critical for chiplet designs in aerospace applications. Redundancy strategies at both the chiplet and system levels must be implemented, including triple modular redundancy (TMR) for critical functions and error detection and correction (EDAC) capabilities for data integrity. The distributed nature of chiplet architectures offers potential advantages for implementing sophisticated fault isolation techniques that can contain failures within individual chiplets.

Mean Time Between Failures (MTBF) requirements for aerospace electronics typically exceed 100,000 hours, necessitating exceptional quality control throughout the chiplet manufacturing and integration process. This includes stringent die-level testing before integration, comprehensive inspection of interconnects, and hermetic packaging to prevent environmental contamination.

The certification process for chiplet-based aerospace systems requires collaboration between chiplet suppliers, system integrators, and certification authorities. This collaborative approach must establish clear traceability from requirements to implementation and verification, with particular attention to interface specifications between chiplets. Industry consortia are working to standardize certification methodologies specifically for chiplet-based aerospace systems, potentially reducing certification timelines while maintaining rigorous safety standards.

Thermal Management Strategies for Chiplet-Based Aerospace Systems

Thermal management represents a critical challenge in chiplet-based aerospace systems due to the extreme operating conditions and reliability requirements. The integration of multiple chiplets in close proximity creates concentrated heat zones that must be effectively managed to prevent performance degradation and system failure. Aerospace applications face unique thermal challenges including rapid temperature fluctuations, vacuum environments, and limited cooling options compared to terrestrial systems.

Traditional cooling methods such as air cooling become ineffective in aerospace environments, necessitating advanced thermal management strategies. Direct liquid cooling systems have emerged as a promising solution, where specialized coolants circulate through microchannels integrated within the chiplet package. These systems can achieve thermal dissipation rates exceeding 500 W/cm², significantly outperforming conventional approaches.

Advanced thermal interface materials (TIMs) play a crucial role in chiplet-based aerospace systems. Novel carbon-based TIMs, including graphene and carbon nanotubes, offer thermal conductivity values up to 2000 W/mK, dramatically improving heat transfer between chiplets and heat dissipation structures. These materials maintain performance integrity under the extreme temperature cycles experienced in aerospace applications.

Phase-change materials (PCMs) provide another innovative approach to thermal management. These materials absorb excess heat during high-processing loads by changing from solid to liquid state, effectively dampening temperature spikes. Aerospace-grade PCMs with melting points between 80-120°C have demonstrated the ability to maintain chiplet junction temperatures within safe operating ranges during computational bursts.

Three-dimensional heat spreading architectures represent the cutting edge of thermal management for chiplet systems. By incorporating diamond-copper composite materials with thermal conductivity exceeding 800 W/mK in vertical heat pipes, these designs enable efficient heat extraction from deeply stacked chiplet configurations. This approach has shown particular promise for high-altitude and space applications where radiation cooling becomes the primary heat rejection mechanism.

Active thermal management systems utilizing microelectromechanical systems (MEMS) provide dynamic response to changing thermal loads. These systems incorporate temperature sensors and microfluidic pumps that adjust cooling capacity in real-time, optimizing power consumption while maintaining thermal stability across diverse mission profiles. Recent aerospace implementations have demonstrated 30% improvements in thermal efficiency compared to passive systems.

Traditional cooling methods such as air cooling become ineffective in aerospace environments, necessitating advanced thermal management strategies. Direct liquid cooling systems have emerged as a promising solution, where specialized coolants circulate through microchannels integrated within the chiplet package. These systems can achieve thermal dissipation rates exceeding 500 W/cm², significantly outperforming conventional approaches.

Advanced thermal interface materials (TIMs) play a crucial role in chiplet-based aerospace systems. Novel carbon-based TIMs, including graphene and carbon nanotubes, offer thermal conductivity values up to 2000 W/mK, dramatically improving heat transfer between chiplets and heat dissipation structures. These materials maintain performance integrity under the extreme temperature cycles experienced in aerospace applications.

Phase-change materials (PCMs) provide another innovative approach to thermal management. These materials absorb excess heat during high-processing loads by changing from solid to liquid state, effectively dampening temperature spikes. Aerospace-grade PCMs with melting points between 80-120°C have demonstrated the ability to maintain chiplet junction temperatures within safe operating ranges during computational bursts.

Three-dimensional heat spreading architectures represent the cutting edge of thermal management for chiplet systems. By incorporating diamond-copper composite materials with thermal conductivity exceeding 800 W/mK in vertical heat pipes, these designs enable efficient heat extraction from deeply stacked chiplet configurations. This approach has shown particular promise for high-altitude and space applications where radiation cooling becomes the primary heat rejection mechanism.

Active thermal management systems utilizing microelectromechanical systems (MEMS) provide dynamic response to changing thermal loads. These systems incorporate temperature sensors and microfluidic pumps that adjust cooling capacity in real-time, optimizing power consumption while maintaining thermal stability across diverse mission profiles. Recent aerospace implementations have demonstrated 30% improvements in thermal efficiency compared to passive systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!