FinFET Gate Material Selection: Impact On Efficiency

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Gate Material Evolution and Objectives

The evolution of gate materials in FinFET technology represents one of the most significant advancements in semiconductor manufacturing over the past two decades. Initially, polysilicon gates dominated the semiconductor industry due to their compatibility with existing manufacturing processes and reasonable performance characteristics. However, as transistor dimensions continued to shrink following Moore's Law, the limitations of polysilicon became increasingly apparent, particularly in terms of gate leakage and threshold voltage control.

The transition to metal gates marked a pivotal moment in FinFET development around 2007-2008, when Intel introduced its 45nm process technology featuring high-k metal gates. This shift addressed critical challenges in device scaling, particularly the quantum tunneling effect that had become problematic with traditional SiO2 gate dielectrics at thicknesses below 2nm. The combination of high-k dielectrics (primarily HfO2-based materials) with metal gates enabled continued device scaling while maintaining acceptable leakage currents.

Material selection for FinFET gates has evolved to focus on work function engineering, with various metals and metal compounds being employed to achieve optimal threshold voltages for both NMOS and PMOS devices. TiN, TaN, and various metal alloys have emerged as prominent candidates, each offering specific advantages in terms of thermal stability, process integration, and electrical characteristics.

The primary objective of gate material research in modern FinFET technology centers on achieving an optimal balance between performance, power consumption, and manufacturability. Specifically, researchers aim to minimize gate leakage while maximizing channel control, which directly impacts transistor switching speed and energy efficiency. Work function tunability remains a critical goal, allowing precise threshold voltage adjustment for different device types within the same manufacturing process.

Another key objective involves improving reliability and reducing variability in gate stack properties. As device dimensions approach atomic scales, even minor variations in material composition or interface quality can significantly impact device performance and yield. Consequently, developing gate materials with consistent properties and stable interfaces has become increasingly important.

Looking forward, gate material research is increasingly focused on compatibility with emerging channel materials beyond silicon, such as germanium, III-V compounds, and two-dimensional materials. These alternative channel materials offer potential performance advantages but require carefully engineered gate stacks to realize their full potential. Additionally, as the industry explores vertical FinFETs and gate-all-around architectures, gate material selection must adapt to new geometric constraints and electrostatic requirements.

The transition to metal gates marked a pivotal moment in FinFET development around 2007-2008, when Intel introduced its 45nm process technology featuring high-k metal gates. This shift addressed critical challenges in device scaling, particularly the quantum tunneling effect that had become problematic with traditional SiO2 gate dielectrics at thicknesses below 2nm. The combination of high-k dielectrics (primarily HfO2-based materials) with metal gates enabled continued device scaling while maintaining acceptable leakage currents.

Material selection for FinFET gates has evolved to focus on work function engineering, with various metals and metal compounds being employed to achieve optimal threshold voltages for both NMOS and PMOS devices. TiN, TaN, and various metal alloys have emerged as prominent candidates, each offering specific advantages in terms of thermal stability, process integration, and electrical characteristics.

The primary objective of gate material research in modern FinFET technology centers on achieving an optimal balance between performance, power consumption, and manufacturability. Specifically, researchers aim to minimize gate leakage while maximizing channel control, which directly impacts transistor switching speed and energy efficiency. Work function tunability remains a critical goal, allowing precise threshold voltage adjustment for different device types within the same manufacturing process.

Another key objective involves improving reliability and reducing variability in gate stack properties. As device dimensions approach atomic scales, even minor variations in material composition or interface quality can significantly impact device performance and yield. Consequently, developing gate materials with consistent properties and stable interfaces has become increasingly important.

Looking forward, gate material research is increasingly focused on compatibility with emerging channel materials beyond silicon, such as germanium, III-V compounds, and two-dimensional materials. These alternative channel materials offer potential performance advantages but require carefully engineered gate stacks to realize their full potential. Additionally, as the industry explores vertical FinFETs and gate-all-around architectures, gate material selection must adapt to new geometric constraints and electrostatic requirements.

Market Demand Analysis for Advanced Gate Materials

The global semiconductor market has witnessed a significant shift towards advanced gate materials for FinFET technology, driven primarily by the increasing demand for higher performance and energy-efficient electronic devices. As of 2023, the market for advanced gate materials is estimated to reach $3.2 billion, with a projected compound annual growth rate of 14.7% through 2028, reflecting the industry's recognition of gate material selection as a critical factor in device efficiency.

Consumer electronics remains the largest application segment, accounting for approximately 42% of the advanced gate materials market. The proliferation of smartphones, tablets, and wearable devices has created substantial demand for processors that deliver superior performance while consuming minimal power. Device manufacturers are increasingly specifying advanced gate materials in their component requirements to meet consumer expectations for longer battery life and faster processing speeds.

Data centers represent the fastest-growing market segment, with demand increasing at nearly 18% annually. The exponential growth in cloud computing, artificial intelligence, and big data analytics has intensified the need for server processors that can handle massive computational loads while minimizing energy consumption. This sector's emphasis on total cost of ownership has elevated the importance of gate material selection, as operational efficiency directly impacts long-term operating expenses.

The automotive industry has emerged as a significant new market driver, particularly with the accelerating adoption of electric vehicles and advanced driver assistance systems. These applications require semiconductors that can operate reliably under varying temperature conditions while maintaining power efficiency. The market for automotive-grade advanced gate materials is expected to triple in size over the next five years.

Regional analysis reveals that Asia-Pacific dominates the market with a 63% share, led by manufacturing powerhouses in Taiwan, South Korea, and increasingly, mainland China. North America follows with 22%, primarily driven by design innovation rather than manufacturing volume. Europe accounts for 12% of the market, with particular strength in automotive semiconductor applications.

Industry surveys indicate that 78% of semiconductor manufacturers consider advanced gate materials a strategic priority for their technology roadmaps. The willingness to invest in new materials has increased substantially, with 67% of manufacturers reporting higher R&D allocations specifically for gate material research compared to five years ago. This trend reflects the growing recognition that traditional scaling approaches are reaching physical limits, making material innovation increasingly critical for continued performance improvements.

Consumer electronics remains the largest application segment, accounting for approximately 42% of the advanced gate materials market. The proliferation of smartphones, tablets, and wearable devices has created substantial demand for processors that deliver superior performance while consuming minimal power. Device manufacturers are increasingly specifying advanced gate materials in their component requirements to meet consumer expectations for longer battery life and faster processing speeds.

Data centers represent the fastest-growing market segment, with demand increasing at nearly 18% annually. The exponential growth in cloud computing, artificial intelligence, and big data analytics has intensified the need for server processors that can handle massive computational loads while minimizing energy consumption. This sector's emphasis on total cost of ownership has elevated the importance of gate material selection, as operational efficiency directly impacts long-term operating expenses.

The automotive industry has emerged as a significant new market driver, particularly with the accelerating adoption of electric vehicles and advanced driver assistance systems. These applications require semiconductors that can operate reliably under varying temperature conditions while maintaining power efficiency. The market for automotive-grade advanced gate materials is expected to triple in size over the next five years.

Regional analysis reveals that Asia-Pacific dominates the market with a 63% share, led by manufacturing powerhouses in Taiwan, South Korea, and increasingly, mainland China. North America follows with 22%, primarily driven by design innovation rather than manufacturing volume. Europe accounts for 12% of the market, with particular strength in automotive semiconductor applications.

Industry surveys indicate that 78% of semiconductor manufacturers consider advanced gate materials a strategic priority for their technology roadmaps. The willingness to invest in new materials has increased substantially, with 67% of manufacturers reporting higher R&D allocations specifically for gate material research compared to five years ago. This trend reflects the growing recognition that traditional scaling approaches are reaching physical limits, making material innovation increasingly critical for continued performance improvements.

Current State and Challenges in FinFET Gate Technology

The global FinFET technology landscape has evolved significantly since its commercial introduction in 2011. Currently, leading semiconductor manufacturers including TSMC, Samsung, and Intel have implemented FinFET architectures in their sub-22nm process nodes. The state-of-the-art FinFET gate technology predominantly utilizes high-k metal gate (HKMG) stacks, replacing the traditional polysilicon gates to address severe gate leakage issues at advanced nodes.

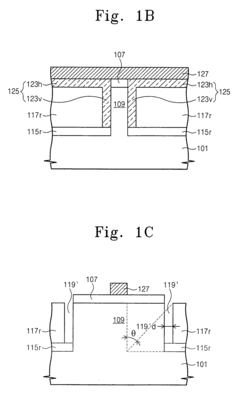

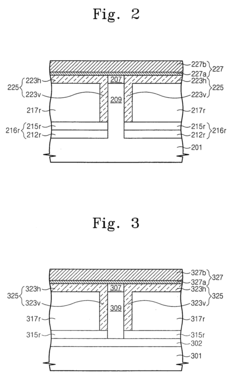

Despite widespread adoption, FinFET gate technology faces several critical challenges. Gate material selection remains a complex optimization problem balancing work function tuning, threshold voltage control, and interface quality. Current HKMG implementations typically employ hafnium-based dielectrics (HfO2, HfSiON) paired with metal gates like TiN, TaN, or TiAlN, but achieving optimal electrical characteristics across different device types (NMOS/PMOS) simultaneously presents significant difficulties.

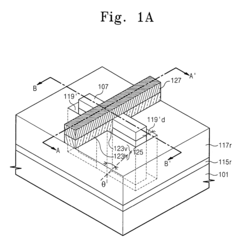

Interface quality between the gate stack and the fin channel represents another major challenge. The three-dimensional nature of FinFET structures creates complex interface conditions that can lead to mobility degradation, threshold voltage instability, and reliability concerns. Current manufacturing processes struggle to maintain uniform gate coverage around the fin structure, particularly at the fin sidewalls and corners.

Gate length scaling has reached physical limitations around 5-7nm in production nodes. As dimensions shrink further, quantum tunneling effects intensify, and variability issues become more pronounced. Statistical variations in fin dimensions and gate material properties significantly impact device performance consistency, creating yield challenges for high-volume manufacturing.

Power consumption remains a critical concern despite FinFET's improved electrostatic control. Gate leakage, while reduced compared to planar technologies, still contributes to static power consumption. Additionally, the capacitance associated with the three-dimensional gate structure increases dynamic power requirements, particularly in high-performance applications.

Reliability issues present ongoing challenges, with bias temperature instability (BTI) and hot carrier injection (HCI) degradation mechanisms affecting long-term device performance. These effects are exacerbated by the high electric fields present in scaled FinFET structures and the complex material interfaces in advanced gate stacks.

Manufacturing complexity represents a significant economic challenge. Current FinFET gate formation requires precise atomic layer deposition (ALD) processes, complex metal gate integration schemes, and sophisticated etching techniques. These requirements drive up production costs and limit technology accessibility to only the most advanced semiconductor manufacturers with sufficient capital resources.

Despite widespread adoption, FinFET gate technology faces several critical challenges. Gate material selection remains a complex optimization problem balancing work function tuning, threshold voltage control, and interface quality. Current HKMG implementations typically employ hafnium-based dielectrics (HfO2, HfSiON) paired with metal gates like TiN, TaN, or TiAlN, but achieving optimal electrical characteristics across different device types (NMOS/PMOS) simultaneously presents significant difficulties.

Interface quality between the gate stack and the fin channel represents another major challenge. The three-dimensional nature of FinFET structures creates complex interface conditions that can lead to mobility degradation, threshold voltage instability, and reliability concerns. Current manufacturing processes struggle to maintain uniform gate coverage around the fin structure, particularly at the fin sidewalls and corners.

Gate length scaling has reached physical limitations around 5-7nm in production nodes. As dimensions shrink further, quantum tunneling effects intensify, and variability issues become more pronounced. Statistical variations in fin dimensions and gate material properties significantly impact device performance consistency, creating yield challenges for high-volume manufacturing.

Power consumption remains a critical concern despite FinFET's improved electrostatic control. Gate leakage, while reduced compared to planar technologies, still contributes to static power consumption. Additionally, the capacitance associated with the three-dimensional gate structure increases dynamic power requirements, particularly in high-performance applications.

Reliability issues present ongoing challenges, with bias temperature instability (BTI) and hot carrier injection (HCI) degradation mechanisms affecting long-term device performance. These effects are exacerbated by the high electric fields present in scaled FinFET structures and the complex material interfaces in advanced gate stacks.

Manufacturing complexity represents a significant economic challenge. Current FinFET gate formation requires precise atomic layer deposition (ALD) processes, complex metal gate integration schemes, and sophisticated etching techniques. These requirements drive up production costs and limit technology accessibility to only the most advanced semiconductor manufacturers with sufficient capital resources.

Current Gate Material Solutions and Implementation

01 High-k gate dielectric materials for improved efficiency

High-k dielectric materials are used in FinFET gate structures to improve efficiency by reducing gate leakage current while maintaining equivalent oxide thickness. These materials, such as hafnium oxide, zirconium oxide, and their silicates, allow for thicker physical layers while providing better electrostatic control. The implementation of high-k dielectrics enables continued device scaling while mitigating short-channel effects and improving overall power efficiency in FinFET devices.- High-k dielectric materials for FinFET gates: High-k dielectric materials are used in FinFET gate structures to improve gate efficiency by reducing leakage current while maintaining equivalent oxide thickness. These materials allow for thicker physical gate dielectrics while providing better electrostatic control over the channel. Common high-k materials include hafnium oxide, zirconium oxide, and their silicates, which offer superior insulating properties compared to traditional silicon dioxide, enabling continued device scaling while maintaining performance.

- Metal gate electrode materials and work function engineering: Metal gate electrodes are implemented in FinFET structures to eliminate polysilicon depletion effects and improve gate efficiency. Different metal materials with specific work functions are selected for NMOS and PMOS devices to achieve optimal threshold voltages. Work function engineering involves using materials like titanium nitride, tantalum nitride, or aluminum-based compounds, sometimes in combination as metal stacks, to precisely control the electrical characteristics of the transistor and enhance overall performance.

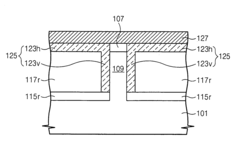

- Gate-all-around and multi-gate FinFET structures: Advanced FinFET architectures such as gate-all-around (GAA) and multi-gate structures improve gate material efficiency by enhancing channel control from multiple sides. These designs increase the effective gate area in contact with the channel, improving electrostatic control and reducing short-channel effects. The three-dimensional nature of these structures allows for better carrier transport and higher drive currents while maintaining low leakage, resulting in improved power efficiency and performance at smaller technology nodes.

- Gate fabrication techniques for improved efficiency: Specialized fabrication techniques are employed to enhance FinFET gate material efficiency. These include replacement metal gate processes, atomic layer deposition for precise thickness control, and gate-last approaches that prevent high-temperature degradation of gate materials. Advanced etching and deposition methods ensure conformal coverage around the fin structure, while strain engineering techniques modify the crystal lattice to improve carrier mobility. These manufacturing innovations result in gates with better electrical characteristics and reliability.

- Gate interface optimization and defect reduction: Optimizing the interface between the gate dielectric and the channel is crucial for FinFET efficiency. Interface engineering techniques include nitrogen incorporation, forming gas anneals, and insertion of interfacial layers to reduce defects and trap states. Careful material selection and processing minimize lattice mismatches and reduce fixed charges at interfaces. These optimizations decrease carrier scattering, enhance mobility, and improve reliability by reducing threshold voltage shifts and bias temperature instability, ultimately leading to more efficient gate operation.

02 Metal gate electrode materials and work function engineering

Metal gate electrodes are incorporated in FinFETs to eliminate poly depletion effects and enhance gate efficiency. Various metals and metal compounds with appropriate work functions are selected for NMOS and PMOS devices to achieve desired threshold voltages. Work function engineering techniques, including the use of metal alloys, capping layers, and interface treatments, enable fine-tuning of electrical characteristics. These approaches improve carrier mobility and reduce resistance in the channel, leading to better overall device performance.Expand Specific Solutions03 Gate-all-around and multi-gate FinFET structures

Advanced gate architectures such as gate-all-around (GAA) and multi-gate structures improve gate material efficiency by enhancing electrostatic control over the channel. These designs provide better short channel effect immunity and allow for more efficient use of gate materials by increasing the effective gate area. The three-dimensional nature of these structures enables more efficient carrier transport and improved subthreshold characteristics, resulting in higher performance at lower operating voltages.Expand Specific Solutions04 Gate stack engineering and interface optimization

Gate stack engineering focuses on optimizing the interfaces between different materials in the gate structure to improve efficiency. This includes the use of interface layers, barrier metals, and capping layers to reduce defects and prevent unwanted diffusion. Techniques such as nitrogen incorporation, thermal treatments, and precise deposition methods are employed to minimize interface states and enhance carrier mobility. These optimizations lead to improved reliability, reduced threshold voltage variation, and better overall gate efficiency.Expand Specific Solutions05 Advanced manufacturing processes for gate formation

Innovative manufacturing processes enhance FinFET gate material efficiency through precise control of dimensions and material properties. These include atomic layer deposition for uniform high-k dielectrics, selective etching techniques for gate patterning, and replacement metal gate processes that allow separate optimization of the gate dielectric and electrode. Self-aligned gate formation methods reduce parasitic capacitance and resistance, while stress engineering techniques improve carrier mobility. These advanced processes enable the fabrication of high-performance FinFETs with optimized gate structures.Expand Specific Solutions

Key Industry Players in Gate Material Innovation

The FinFET gate material selection market is currently in a mature growth phase, with an estimated global market size exceeding $25 billion. The technology landscape is dominated by established semiconductor manufacturers like TSMC, GlobalFoundries, and IBM, who have developed advanced gate material solutions to enhance transistor efficiency. TSMC leads with its cutting-edge high-k metal gate technology, while Intel and Samsung compete with proprietary gate stack innovations. The technology has reached commercial maturity with companies like SMIC, UMC, and Infineon implementing various approaches to optimize power consumption and performance. Applied Materials and other equipment vendors provide critical manufacturing solutions that enable these advancements. The competitive landscape continues to evolve as manufacturers seek materials that balance performance, power efficiency, and manufacturing scalability.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered advanced FinFET gate material solutions, transitioning from conventional polysilicon to high-k metal gate (HKMG) technology. Their N7+ and N5 process nodes implement a sophisticated multi-layer gate stack with hafnium-based dielectrics and specialized work function metals tailored for both NMOS and PMOS transistors[1]. TSMC's approach includes gate-last processing techniques that allow precise threshold voltage tuning through work function metal engineering. Their latest FinFET implementations incorporate stress memorization techniques and epitaxial source/drain regions to enhance carrier mobility. TSMC has also developed specialized gate stack treatments to minimize interface states and reduce threshold voltage variability, achieving sub-0.5nm equivalent oxide thickness while maintaining gate leakage below 0.01A/cm² at operating voltages[3].

Strengths: Industry-leading gate stack quality with minimal interface defects, enabling superior electrostatic control and reduced variability. Their advanced work function metal engineering allows precise Vt tuning for different application requirements. Weaknesses: Higher manufacturing complexity and cost compared to conventional gate materials, requiring specialized deposition equipment and more process steps.

GLOBALFOUNDRIES, Inc.

Technical Solution: GlobalFoundries has developed a distinctive approach to FinFET gate material selection with their 14nm and 12nm FinFET platforms. Their technology employs a gate-first high-k metal gate (HKMG) process that differs from the gate-last approach used by some competitors. This methodology incorporates hafnium-based dielectrics with carefully engineered work function metals to achieve optimal threshold voltages for different transistor types[2]. GlobalFoundries' FD-SOI technology complements their FinFET offerings with ultra-thin body and buried oxide structures that enhance electrostatic control. Their gate stack engineering includes specialized interfacial layers between the high-k dielectric and silicon channel to minimize carrier scattering and trap states. Recent advancements have focused on reducing gate resistance through innovative metal composition and deposition techniques, achieving sheet resistance below 7 ohms/square for gate electrodes[4].

Strengths: Their gate-first approach offers manufacturing simplicity and cost advantages while still delivering competitive performance. The technology shows excellent reliability characteristics with minimal bias temperature instability. Weaknesses: Somewhat higher gate-induced drain leakage compared to gate-last processes, and potentially more challenging work function metal integration for advanced nodes below 10nm.

Critical Patents and Research in Gate Material Science

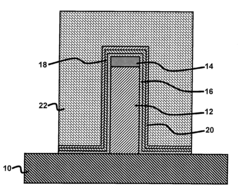

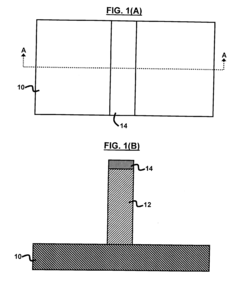

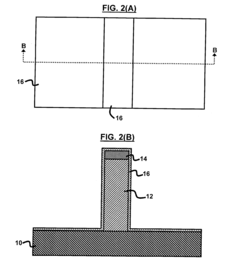

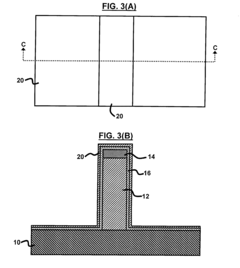

Finfet gate formed of carbon nanotubes

PatentInactiveUS20070023839A1

Innovation

- A FinFET gate structure is developed using a semiconductor wafer with a gate dielectric layer, a conductive material, activated carbon nanotubes, and a plated metal layer, where the carbon nanotubes are grown on the sidewall of the conductive material, and a seed metal layer is formed by chemically reducing metal ions, allowing for efficient metal plating without the need for long etch times.

Finfets having first and second gates of different resistivities

PatentInactiveUS7268396B2

Innovation

- A dual gate structure is implemented, where a first gate made of polysilicon provides channel control and a second gate with low-resistance material, such as metal or silicide, is in direct contact with the first gate outside the capping layer, reducing parasitic capacitance and preventing lifting phenomena.

Environmental Impact of Gate Material Selection

The selection of gate materials in FinFET technology carries significant environmental implications throughout the entire lifecycle of semiconductor devices. Traditional gate materials like polysilicon have been gradually replaced by metal gates, particularly in high-k metal gate (HKGM) configurations, which has altered the environmental footprint of semiconductor manufacturing processes. The extraction and processing of rare metals used in advanced gate structures, such as hafnium, titanium, and tantalum, involve energy-intensive mining operations that contribute to habitat destruction, water pollution, and greenhouse gas emissions.

Manufacturing processes for metal gate materials require substantial energy inputs and utilize potentially hazardous chemicals, including various precursors and etchants. The transition to atomic layer deposition (ALD) techniques for gate material deposition has improved material utilization efficiency but still involves the use of organometallic precursors that may pose environmental risks if not properly managed. Additionally, the high-temperature annealing processes required for some gate materials contribute to the overall energy consumption of semiconductor fabrication.

The environmental impact extends to operational efficiency as well. Gate material selection directly influences device power consumption, with more efficient materials reducing energy requirements during the use phase of electronic products. This is particularly significant considering that the operational energy consumption of electronic devices often exceeds the energy required for their production. Materials that enable lower threshold voltages and reduced leakage currents, such as work function-engineered metal gates, can substantially reduce the carbon footprint of computing infrastructure over its lifetime.

End-of-life considerations present another environmental dimension. Some advanced gate materials contain rare or precious metals that are difficult to recover in current recycling processes. The complex integration of these materials with other components in nanoscale structures complicates separation and reclamation efforts. Improved recycling technologies specifically designed for advanced semiconductor materials are needed to mitigate this impact.

Recent research has begun exploring more environmentally benign alternatives for gate materials, including earth-abundant metals and novel carbon-based materials like graphene. These alternatives aim to reduce dependence on rare elements while maintaining or improving device performance. Additionally, gate stack engineering approaches that minimize material usage while maximizing electrical performance are being developed to reduce environmental impact without compromising technological advancement.

Regulatory frameworks worldwide are increasingly addressing the environmental aspects of semiconductor materials, with restrictions on hazardous substances and requirements for lifecycle assessments. This regulatory landscape is driving innovation toward more sustainable gate material solutions that balance technological performance with environmental responsibility.

Manufacturing processes for metal gate materials require substantial energy inputs and utilize potentially hazardous chemicals, including various precursors and etchants. The transition to atomic layer deposition (ALD) techniques for gate material deposition has improved material utilization efficiency but still involves the use of organometallic precursors that may pose environmental risks if not properly managed. Additionally, the high-temperature annealing processes required for some gate materials contribute to the overall energy consumption of semiconductor fabrication.

The environmental impact extends to operational efficiency as well. Gate material selection directly influences device power consumption, with more efficient materials reducing energy requirements during the use phase of electronic products. This is particularly significant considering that the operational energy consumption of electronic devices often exceeds the energy required for their production. Materials that enable lower threshold voltages and reduced leakage currents, such as work function-engineered metal gates, can substantially reduce the carbon footprint of computing infrastructure over its lifetime.

End-of-life considerations present another environmental dimension. Some advanced gate materials contain rare or precious metals that are difficult to recover in current recycling processes. The complex integration of these materials with other components in nanoscale structures complicates separation and reclamation efforts. Improved recycling technologies specifically designed for advanced semiconductor materials are needed to mitigate this impact.

Recent research has begun exploring more environmentally benign alternatives for gate materials, including earth-abundant metals and novel carbon-based materials like graphene. These alternatives aim to reduce dependence on rare elements while maintaining or improving device performance. Additionally, gate stack engineering approaches that minimize material usage while maximizing electrical performance are being developed to reduce environmental impact without compromising technological advancement.

Regulatory frameworks worldwide are increasingly addressing the environmental aspects of semiconductor materials, with restrictions on hazardous substances and requirements for lifecycle assessments. This regulatory landscape is driving innovation toward more sustainable gate material solutions that balance technological performance with environmental responsibility.

Supply Chain Considerations for Gate Materials

The global supply chain for FinFET gate materials represents a complex ecosystem that significantly impacts semiconductor manufacturing efficiency and cost structures. High-k metal gate (HKGM) materials, particularly hafnium-based compounds and compatible work function metals, face unique supply chain challenges that semiconductor manufacturers must navigate strategically.

Raw material availability presents the first critical consideration, with hafnium being particularly problematic due to its limited natural occurrence. As a byproduct of zirconium processing, hafnium's supply is inherently constrained and concentrated in specific geographical regions, creating potential bottlenecks during demand surges. This concentration of supply in countries like Australia, South Africa, and China introduces geopolitical vulnerabilities that can disrupt manufacturing continuity.

Processing capabilities for these specialized materials are equally concentrated, with only a handful of companies possessing the technical expertise and equipment to refine raw materials to semiconductor-grade purity levels. This oligopolistic market structure creates dependency relationships that can impact pricing stability and negotiation leverage for chip manufacturers.

Lead times for specialized gate materials typically range from 3-6 months, necessitating sophisticated inventory management and forecasting systems. The semiconductor industry's cyclical demand patterns further complicate supply planning, as manufacturers must balance carrying costs against production disruption risks. This balancing act becomes particularly challenging during industry-wide technology transitions when material specifications evolve rapidly.

Quality control represents another critical supply chain consideration, as even minor impurities can dramatically impact transistor performance. The establishment of robust supplier qualification processes and ongoing quality monitoring systems adds complexity and cost to the supply chain management function but remains essential for maintaining yield rates.

Sustainability concerns are increasingly influencing gate material supply chains, with regulatory pressures mounting regarding rare earth elements and energy-intensive processing methods. Forward-thinking manufacturers are developing recycling programs for precious metals and exploring alternative material systems with reduced environmental footprints.

Price volatility presents an ongoing challenge, particularly for materials with limited supplier bases. Long-term supply agreements with price collars have become standard practice, though these must be balanced against the flexibility needed to adopt emerging material innovations. The development of second-source qualification programs provides important risk mitigation but requires significant engineering resources to validate material equivalency across suppliers.

Raw material availability presents the first critical consideration, with hafnium being particularly problematic due to its limited natural occurrence. As a byproduct of zirconium processing, hafnium's supply is inherently constrained and concentrated in specific geographical regions, creating potential bottlenecks during demand surges. This concentration of supply in countries like Australia, South Africa, and China introduces geopolitical vulnerabilities that can disrupt manufacturing continuity.

Processing capabilities for these specialized materials are equally concentrated, with only a handful of companies possessing the technical expertise and equipment to refine raw materials to semiconductor-grade purity levels. This oligopolistic market structure creates dependency relationships that can impact pricing stability and negotiation leverage for chip manufacturers.

Lead times for specialized gate materials typically range from 3-6 months, necessitating sophisticated inventory management and forecasting systems. The semiconductor industry's cyclical demand patterns further complicate supply planning, as manufacturers must balance carrying costs against production disruption risks. This balancing act becomes particularly challenging during industry-wide technology transitions when material specifications evolve rapidly.

Quality control represents another critical supply chain consideration, as even minor impurities can dramatically impact transistor performance. The establishment of robust supplier qualification processes and ongoing quality monitoring systems adds complexity and cost to the supply chain management function but remains essential for maintaining yield rates.

Sustainability concerns are increasingly influencing gate material supply chains, with regulatory pressures mounting regarding rare earth elements and energy-intensive processing methods. Forward-thinking manufacturers are developing recycling programs for precious metals and exploring alternative material systems with reduced environmental footprints.

Price volatility presents an ongoing challenge, particularly for materials with limited supplier bases. Long-term supply agreements with price collars have become standard practice, though these must be balanced against the flexibility needed to adopt emerging material innovations. The development of second-source qualification programs provides important risk mitigation but requires significant engineering resources to validate material equivalency across suppliers.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!