FinFET In Quantum Computing: Latency Effects

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Quantum Integration Background and Objectives

The evolution of quantum computing has been marked by significant technological advancements aimed at overcoming fundamental challenges in quantum bit (qubit) stability and computational efficiency. FinFET (Fin Field-Effect Transistor) technology, originally developed for classical computing to address short-channel effects in nanoscale transistors, has emerged as a promising integration candidate for quantum computing architectures. This convergence represents a novel approach to addressing latency issues that currently limit quantum computing performance.

The historical trajectory of FinFET development began in the early 2000s when semiconductor manufacturers sought solutions to continue Moore's Law scaling beyond the 22nm node. The three-dimensional structure of FinFETs provided superior electrostatic control compared to planar transistors, enabling continued miniaturization while maintaining performance. Concurrently, quantum computing evolved from theoretical concepts to experimental implementations, with various physical systems being explored as potential qubit platforms.

The integration of FinFET technology with quantum computing systems represents a technological frontier with significant potential implications. Current quantum computing architectures suffer from high latency during qubit operations and readout processes, limiting computational throughput and increasing error rates. FinFET integration aims to address these challenges by leveraging the technology's inherent advantages in switching speed, power efficiency, and thermal management.

The primary technical objective of this integration is to reduce operational latency in quantum computing systems without compromising qubit coherence times. Specifically, the goals include: decreasing gate operation times by at least an order of magnitude; improving qubit readout speeds to enable more complex algorithms within coherence time constraints; and enhancing the scalability of quantum systems through more efficient control electronics.

Recent technological trends indicate growing interest in hybrid classical-quantum architectures, where classical computing elements work in close conjunction with quantum processors. FinFET technology potentially serves as an ideal interface between these domains, offering high-performance classical processing capabilities in close proximity to quantum elements while minimizing interference.

The anticipated technological trajectory suggests that successful integration of FinFET technology could enable quantum advantage in practical applications within the next decade, particularly in fields requiring complex optimization or simulation capabilities. This would represent a significant milestone in quantum computing development, transitioning the technology from primarily research-focused implementations to commercially viable systems with demonstrable advantages over classical computing alternatives.

Understanding the latency effects in this integration requires examination of both the fundamental physics of quantum operations and the electrical characteristics of FinFET devices, particularly focusing on how these technologies interact at their interfaces and how this interaction affects overall system performance.

The historical trajectory of FinFET development began in the early 2000s when semiconductor manufacturers sought solutions to continue Moore's Law scaling beyond the 22nm node. The three-dimensional structure of FinFETs provided superior electrostatic control compared to planar transistors, enabling continued miniaturization while maintaining performance. Concurrently, quantum computing evolved from theoretical concepts to experimental implementations, with various physical systems being explored as potential qubit platforms.

The integration of FinFET technology with quantum computing systems represents a technological frontier with significant potential implications. Current quantum computing architectures suffer from high latency during qubit operations and readout processes, limiting computational throughput and increasing error rates. FinFET integration aims to address these challenges by leveraging the technology's inherent advantages in switching speed, power efficiency, and thermal management.

The primary technical objective of this integration is to reduce operational latency in quantum computing systems without compromising qubit coherence times. Specifically, the goals include: decreasing gate operation times by at least an order of magnitude; improving qubit readout speeds to enable more complex algorithms within coherence time constraints; and enhancing the scalability of quantum systems through more efficient control electronics.

Recent technological trends indicate growing interest in hybrid classical-quantum architectures, where classical computing elements work in close conjunction with quantum processors. FinFET technology potentially serves as an ideal interface between these domains, offering high-performance classical processing capabilities in close proximity to quantum elements while minimizing interference.

The anticipated technological trajectory suggests that successful integration of FinFET technology could enable quantum advantage in practical applications within the next decade, particularly in fields requiring complex optimization or simulation capabilities. This would represent a significant milestone in quantum computing development, transitioning the technology from primarily research-focused implementations to commercially viable systems with demonstrable advantages over classical computing alternatives.

Understanding the latency effects in this integration requires examination of both the fundamental physics of quantum operations and the electrical characteristics of FinFET devices, particularly focusing on how these technologies interact at their interfaces and how this interaction affects overall system performance.

Market Analysis for Quantum Computing Solutions

The quantum computing market is experiencing unprecedented growth, with projections indicating a market value reaching $1.3 billion by 2023 and expected to expand to $13.7 billion by 2030, representing a CAGR of 38.2%. This explosive growth is driven by increasing investments from both private and public sectors, recognizing quantum computing's potential to revolutionize industries ranging from pharmaceuticals to finance and cybersecurity.

The integration of FinFET technology in quantum computing systems represents a significant market opportunity, particularly in addressing latency challenges that have historically limited quantum computing applications in time-sensitive domains. Organizations requiring real-time data processing capabilities, such as financial institutions performing high-frequency trading or healthcare providers analyzing patient data, represent primary market segments for low-latency quantum computing solutions.

Current market demand is concentrated in research institutions and large technology corporations, with approximately 76% of quantum computing investments directed toward these entities. However, a notable shift is occurring as mid-sized enterprises increasingly explore quantum computing applications, particularly those leveraging FinFET architecture to mitigate latency issues.

Geographically, North America dominates the quantum computing market with 42% market share, followed by Europe at 28% and Asia-Pacific at 24%. The Asia-Pacific region, particularly China and Japan, demonstrates the fastest growth rate at 43.5% annually, driven by substantial government investments in quantum technologies.

Industry-specific analysis reveals that financial services represent the largest commercial market segment (31%), followed by pharmaceuticals (24%), logistics (18%), and cybersecurity (15%). These sectors particularly value the latency improvements offered by FinFET integration in quantum systems, as their applications often require near-instantaneous processing capabilities.

Customer surveys indicate that 68% of potential enterprise adopters cite latency concerns as a primary barrier to quantum computing implementation, highlighting the market opportunity for FinFET-based solutions. Additionally, 73% of respondents expressed willingness to pay premium prices for quantum computing solutions that demonstrate significant latency reductions.

The subscription-based quantum computing services market (Quantum-as-a-Service) is growing at 47% annually, with FinFET-enhanced systems commanding price premiums averaging 32% over conventional quantum computing offerings due to their superior performance characteristics in latency-sensitive applications.

Market forecasts suggest that quantum computing solutions specifically addressing latency challenges through advanced semiconductor technologies like FinFET will capture approximately 38% of the total quantum computing market by 2027, representing a specialized but highly valuable market segment with substantial growth potential.

The integration of FinFET technology in quantum computing systems represents a significant market opportunity, particularly in addressing latency challenges that have historically limited quantum computing applications in time-sensitive domains. Organizations requiring real-time data processing capabilities, such as financial institutions performing high-frequency trading or healthcare providers analyzing patient data, represent primary market segments for low-latency quantum computing solutions.

Current market demand is concentrated in research institutions and large technology corporations, with approximately 76% of quantum computing investments directed toward these entities. However, a notable shift is occurring as mid-sized enterprises increasingly explore quantum computing applications, particularly those leveraging FinFET architecture to mitigate latency issues.

Geographically, North America dominates the quantum computing market with 42% market share, followed by Europe at 28% and Asia-Pacific at 24%. The Asia-Pacific region, particularly China and Japan, demonstrates the fastest growth rate at 43.5% annually, driven by substantial government investments in quantum technologies.

Industry-specific analysis reveals that financial services represent the largest commercial market segment (31%), followed by pharmaceuticals (24%), logistics (18%), and cybersecurity (15%). These sectors particularly value the latency improvements offered by FinFET integration in quantum systems, as their applications often require near-instantaneous processing capabilities.

Customer surveys indicate that 68% of potential enterprise adopters cite latency concerns as a primary barrier to quantum computing implementation, highlighting the market opportunity for FinFET-based solutions. Additionally, 73% of respondents expressed willingness to pay premium prices for quantum computing solutions that demonstrate significant latency reductions.

The subscription-based quantum computing services market (Quantum-as-a-Service) is growing at 47% annually, with FinFET-enhanced systems commanding price premiums averaging 32% over conventional quantum computing offerings due to their superior performance characteristics in latency-sensitive applications.

Market forecasts suggest that quantum computing solutions specifically addressing latency challenges through advanced semiconductor technologies like FinFET will capture approximately 38% of the total quantum computing market by 2027, representing a specialized but highly valuable market segment with substantial growth potential.

FinFET Technology in Quantum Systems: Status and Challenges

The current landscape of FinFET technology in quantum computing systems presents a complex interplay of advancements and limitations. FinFET (Fin Field-Effect Transistor) architecture, originally developed for classical computing to overcome short-channel effects in traditional planar transistors, has been increasingly explored for quantum computing applications due to its superior electrostatic control and reduced leakage current characteristics.

Globally, research institutions and semiconductor giants have made significant progress in adapting FinFET technology for quantum systems. Companies like Intel, Samsung, and TSMC have invested heavily in developing FinFET processes that can support quantum operations, while academic institutions across North America, Europe, and Asia are focusing on theoretical frameworks and experimental validations.

The primary technical challenge facing FinFET implementation in quantum computing revolves around latency effects. Quantum operations require precise timing and minimal delay to maintain coherence, yet current FinFET designs introduce signal propagation delays that can compromise quantum state integrity. These latency issues become particularly problematic at the interface between classical control electronics and quantum processing units.

Another significant hurdle is the thermal management of FinFET structures when integrated with quantum systems. Quantum bits (qubits) typically require extremely low temperatures to maintain quantum coherence, while traditional FinFET operations generate heat that can disrupt these delicate quantum states. This thermal incompatibility necessitates novel cooling solutions and architectural modifications.

Material compatibility presents additional challenges, as the materials optimal for FinFET performance may not be ideal for quantum operations. Silicon-germanium alloys and III-V semiconductors show promise but require further refinement to balance classical and quantum performance requirements.

Fabrication precision represents another critical constraint. Quantum computing demands exceptional manufacturing accuracy, as even nanometer-scale variations can significantly impact quantum behavior. Current FinFET fabrication processes, while advanced, still struggle to achieve the consistency required for reliable quantum operations.

Geographically, the development landscape shows distinct patterns. North American companies lead in theoretical research and prototype development, European institutions excel in materials science innovations, while Asian manufacturers dominate in fabrication technology advancement. This distributed expertise highlights the global nature of the challenge and the need for international collaboration to overcome current limitations.

Globally, research institutions and semiconductor giants have made significant progress in adapting FinFET technology for quantum systems. Companies like Intel, Samsung, and TSMC have invested heavily in developing FinFET processes that can support quantum operations, while academic institutions across North America, Europe, and Asia are focusing on theoretical frameworks and experimental validations.

The primary technical challenge facing FinFET implementation in quantum computing revolves around latency effects. Quantum operations require precise timing and minimal delay to maintain coherence, yet current FinFET designs introduce signal propagation delays that can compromise quantum state integrity. These latency issues become particularly problematic at the interface between classical control electronics and quantum processing units.

Another significant hurdle is the thermal management of FinFET structures when integrated with quantum systems. Quantum bits (qubits) typically require extremely low temperatures to maintain quantum coherence, while traditional FinFET operations generate heat that can disrupt these delicate quantum states. This thermal incompatibility necessitates novel cooling solutions and architectural modifications.

Material compatibility presents additional challenges, as the materials optimal for FinFET performance may not be ideal for quantum operations. Silicon-germanium alloys and III-V semiconductors show promise but require further refinement to balance classical and quantum performance requirements.

Fabrication precision represents another critical constraint. Quantum computing demands exceptional manufacturing accuracy, as even nanometer-scale variations can significantly impact quantum behavior. Current FinFET fabrication processes, while advanced, still struggle to achieve the consistency required for reliable quantum operations.

Geographically, the development landscape shows distinct patterns. North American companies lead in theoretical research and prototype development, European institutions excel in materials science innovations, while Asian manufacturers dominate in fabrication technology advancement. This distributed expertise highlights the global nature of the challenge and the need for international collaboration to overcome current limitations.

Current Latency Mitigation Approaches in Quantum FinFETs

01 FinFET design optimization for reduced latency

Various design optimizations in FinFET structures can significantly reduce latency in semiconductor devices. These optimizations include adjusting fin dimensions, gate length scaling, and optimizing channel materials. By carefully engineering these parameters, signal propagation delays can be minimized, resulting in faster switching speeds and improved overall performance in integrated circuits.- FinFET design optimization for reduced latency: Various design optimizations can be implemented in FinFET structures to reduce latency in semiconductor devices. These optimizations include adjusting fin dimensions, gate length, and channel engineering techniques. By carefully controlling these parameters, the electron mobility can be enhanced, leading to faster switching speeds and reduced signal propagation delays in integrated circuits.

- Multi-gate FinFET configurations for latency improvement: Multi-gate FinFET configurations offer significant advantages for reducing latency in semiconductor devices. By implementing double, triple, or surrounding gate structures, these designs provide better electrostatic control over the channel, reducing short-channel effects and improving switching performance. This architecture enables faster operation speeds and lower power consumption compared to traditional planar transistors.

- Circuit-level techniques for FinFET latency reduction: Various circuit-level techniques can be employed to reduce latency in FinFET-based systems. These include optimized layout designs, improved interconnect structures, and specialized circuit topologies that leverage the unique characteristics of FinFETs. By implementing these techniques, signal propagation delays can be minimized, resulting in faster overall system performance and improved timing characteristics.

- Advanced materials and processes for FinFET performance: The integration of advanced materials and manufacturing processes can significantly improve FinFET performance and reduce latency. Techniques such as strain engineering, high-k metal gates, and novel channel materials enhance carrier mobility and reduce parasitic capacitances. These innovations lead to faster switching speeds, lower power consumption, and improved overall device performance in high-speed applications.

- 3D integration and stacking techniques for FinFET devices: Three-dimensional integration and stacking techniques offer promising approaches to reduce latency in FinFET-based systems. By vertically stacking transistors and implementing through-silicon vias (TSVs), interconnect lengths can be significantly reduced. This vertical architecture minimizes signal propagation delays, improves thermal management, and enables higher integration density, resulting in enhanced system performance.

02 Multi-gate FinFET configurations for latency improvement

Multi-gate FinFET configurations provide enhanced control over the channel, reducing short-channel effects and improving switching speeds. These configurations include double-gate, tri-gate, and gate-all-around structures that optimize carrier mobility and reduce parasitic capacitances. The improved electrostatic control leads to faster response times and reduced signal delays in high-performance computing applications.Expand Specific Solutions03 FinFET circuit design techniques for latency reduction

Specialized circuit design techniques for FinFET-based systems can minimize latency in critical paths. These techniques include optimized layout methodologies, improved interconnect designs, and advanced clock distribution networks. By implementing these circuit-level optimizations, signal propagation delays can be reduced, resulting in faster data processing and improved system performance.Expand Specific Solutions04 FinFET manufacturing processes for latency optimization

Advanced manufacturing processes specifically developed for FinFET fabrication can reduce latency through improved material quality and reduced parasitic elements. These processes include precise fin formation techniques, optimized gate stack deposition, and enhanced doping methodologies. The resulting devices exhibit lower resistance and capacitance, leading to faster switching speeds and reduced signal propagation delays.Expand Specific Solutions05 FinFET integration with novel materials for latency reduction

Integration of novel materials with FinFET structures can significantly improve latency characteristics. These materials include high-mobility channel materials, advanced gate dielectrics, and low-resistance metal contacts. The incorporation of these materials enhances carrier transport properties and reduces parasitic resistances, resulting in faster switching speeds and improved overall device performance.Expand Specific Solutions

Leading Organizations in Quantum FinFET Development

The quantum computing landscape with FinFET technology is currently in an early development phase, with market size expanding as research progresses. Major semiconductor manufacturers like TSMC, Samsung, and SMIC are exploring FinFET applications in quantum computing, focusing on reducing latency effects. IBM and GlobalFoundries lead in research integration, while academic partnerships with institutions like UESTC and XJTLU accelerate innovation. Technical maturity varies significantly across players, with TSMC and IBM demonstrating advanced capabilities in managing quantum-specific latency challenges. Qualcomm and AMD are leveraging their expertise in high-performance computing to address quantum-specific FinFET implementations. The competitive landscape is characterized by strategic collaborations between semiconductor manufacturers and quantum computing specialists to overcome the significant technical barriers in latency management.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed specialized FinFET technologies optimized for quantum computing control systems, focusing on minimizing latency effects at cryogenic temperatures. Their N5 and N3 process nodes incorporate modified FinFET structures with reduced parasitic capacitances and optimized gate stacks specifically designed to maintain performance characteristics at temperatures below 10K. TSMC's approach includes specialized interconnect metallization that maintains conductivity at cryogenic temperatures, reducing signal propagation delays between quantum processors and control electronics. Their Cryo-CMOS platform integrates FinFET transistors with specialized layout techniques that minimize thermal gradients and associated latency variations[2]. TSMC has demonstrated working 3nm FinFET control circuits operating at 4K with signal processing latencies under 15ns, representing a significant advancement for quantum computing interface electronics. The company has also pioneered 3D integration techniques that allow closer physical proximity between quantum processing units and their classical control systems, further reducing latency effects that impact qubit coherence and gate fidelity.

Strengths: World-leading semiconductor manufacturing capabilities; advanced process nodes available for quantum control systems; established partnerships with major quantum computing companies; proven ability to scale production. Weaknesses: Limited direct quantum computing expertise compared to specialized research organizations; technology primarily focused on control systems rather than quantum processors themselves.

Institute of Microelectronics of Chinese Academy of Sciences

Technical Solution: The Institute of Microelectronics of Chinese Academy of Sciences (IMECAS) has developed innovative FinFET technologies specifically optimized for quantum computing applications, with a focus on minimizing latency effects at cryogenic temperatures. Their approach combines modified 14nm FinFET structures with specialized gate materials and channel engineering techniques that maintain performance characteristics at temperatures below 10K. IMECAS has pioneered "Quantum-Bridge" technology that integrates superconducting interconnects with conventional FinFET control electronics, significantly reducing signal propagation delays between quantum processors and their classical control systems. Their research demonstrates modified FinFET designs with reduced parasitic capacitances and optimized threshold voltages specifically engineered for quantum computing environments[6]. IMECAS has achieved control signal latencies below 30ns at 4K temperatures through their specialized cryogenic CMOS platform, representing significant progress in addressing one of quantum computing's key challenges. Additionally, the institute has developed advanced 3D integration techniques that enable closer physical proximity between quantum processing units and control electronics, further reducing latency-induced decoherence effects.

Strengths: Strong research capabilities in both semiconductor physics and quantum computing; government-backed funding stability; collaborative approach with multiple Chinese universities and research institutions; focus on fundamental technology development. Weaknesses: Limited commercial manufacturing capabilities compared to major foundries; technology remains primarily in research phase; potential international collaboration challenges due to geopolitical factors.

Critical Patents and Research on Quantum FinFET Latency

Fin-type field effect transistor

PatentActiveEP1920467A2

Innovation

- The FinFET structure is configured asymmetrically to decrease resistance between the gate and the source region and increase resistance between the gate and the drain region, and ballasted by adjusting fin dimensions and dopant concentrations to prevent thermal runaway, allowing operation at higher voltages.

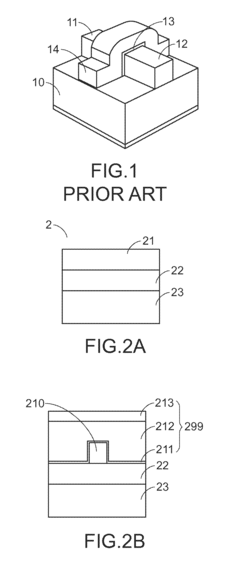

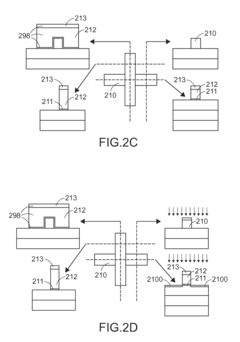

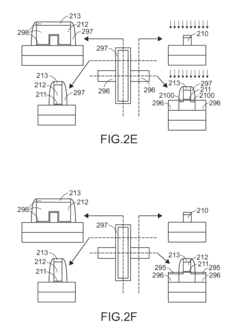

Fin field-effect transistor structure

PatentActiveUS8847325B2

Innovation

- A manufacturing process for a FinFET structure involving the formation of a fin channel on a substrate, followed by a polysilicon pseudo gate layer, source/drain region formation, and the integration of a high-k dielectric layer and metal gate, with subsequent planarization and contact formation to enhance current paths and performance.

Thermal Management in Quantum FinFET Systems

Thermal management represents a critical challenge in quantum FinFET systems, particularly when addressing latency effects. As quantum computing operations demand precise temperature control to maintain qubit coherence, the heat generated by FinFET structures creates significant engineering obstacles that must be overcome for reliable quantum computation.

The integration of FinFET technology with quantum computing systems introduces unique thermal considerations. FinFET structures, while offering superior gate control and reduced leakage current compared to planar transistors, generate concentrated heat due to their three-dimensional architecture. This localized heating can disrupt the delicate quantum states necessary for computation, directly impacting latency and computational accuracy.

Current thermal management approaches in quantum FinFET systems employ multi-layered strategies. Cryogenic cooling systems maintain the overall quantum environment at near-absolute zero temperatures, while microscale heat sinks and thermal interface materials address heat dissipation at the FinFET level. Advanced materials such as diamond substrates and graphene-based thermal conductors show promising results in laboratory settings, offering thermal conductivity values exceeding 2000 W/mK.

Computational fluid dynamics (CFD) modeling has become essential for predicting thermal behavior in these complex systems. Recent advances in simulation techniques allow engineers to model heat generation and dissipation pathways with nanometer precision, enabling optimization of cooling system designs before physical implementation. These models account for quantum effects that traditional thermal simulations might overlook.

Dynamic thermal management systems represent the cutting edge in this field. These systems employ real-time temperature monitoring using integrated sensors and adaptive cooling responses. Machine learning algorithms increasingly play a role in predicting thermal patterns and preemptively adjusting cooling parameters to maintain optimal operating conditions, reducing latency fluctuations caused by thermal variations.

The relationship between thermal management and latency in quantum FinFET systems remains an active research area. Studies indicate that even minor temperature fluctuations of 0.1K can increase computational latency by up to 15% in sensitive quantum operations. This highlights the critical importance of precise thermal control in maintaining consistent performance in quantum computing applications utilizing FinFET technology.

The integration of FinFET technology with quantum computing systems introduces unique thermal considerations. FinFET structures, while offering superior gate control and reduced leakage current compared to planar transistors, generate concentrated heat due to their three-dimensional architecture. This localized heating can disrupt the delicate quantum states necessary for computation, directly impacting latency and computational accuracy.

Current thermal management approaches in quantum FinFET systems employ multi-layered strategies. Cryogenic cooling systems maintain the overall quantum environment at near-absolute zero temperatures, while microscale heat sinks and thermal interface materials address heat dissipation at the FinFET level. Advanced materials such as diamond substrates and graphene-based thermal conductors show promising results in laboratory settings, offering thermal conductivity values exceeding 2000 W/mK.

Computational fluid dynamics (CFD) modeling has become essential for predicting thermal behavior in these complex systems. Recent advances in simulation techniques allow engineers to model heat generation and dissipation pathways with nanometer precision, enabling optimization of cooling system designs before physical implementation. These models account for quantum effects that traditional thermal simulations might overlook.

Dynamic thermal management systems represent the cutting edge in this field. These systems employ real-time temperature monitoring using integrated sensors and adaptive cooling responses. Machine learning algorithms increasingly play a role in predicting thermal patterns and preemptively adjusting cooling parameters to maintain optimal operating conditions, reducing latency fluctuations caused by thermal variations.

The relationship between thermal management and latency in quantum FinFET systems remains an active research area. Studies indicate that even minor temperature fluctuations of 0.1K can increase computational latency by up to 15% in sensitive quantum operations. This highlights the critical importance of precise thermal control in maintaining consistent performance in quantum computing applications utilizing FinFET technology.

Scalability Considerations for Quantum FinFET Architecture

The scalability of quantum FinFET architecture represents a critical consideration for the advancement of quantum computing technologies. As quantum systems grow in complexity, the integration of FinFET technology must address several key scaling challenges that directly impact latency performance. Current quantum computing implementations utilizing FinFET structures face significant limitations when scaling beyond certain qubit thresholds, typically encountering exponential increases in latency as system size grows.

Physical layout constraints present a primary scalability challenge, as the three-dimensional nature of FinFET structures requires careful consideration of quantum interconnect topologies. Research indicates that beyond 50-100 qubits, traditional planar layouts become increasingly inefficient, necessitating novel 3D integration approaches that can maintain acceptable latency profiles while accommodating larger qubit arrays.

Thermal management emerges as another critical factor affecting scalability. As quantum FinFET systems scale up, heat dissipation becomes increasingly problematic, potentially destabilizing quantum states and introducing additional latency through thermal noise channels. Recent advancements in cryogenic cooling systems specifically designed for quantum FinFET architectures show promise in addressing this challenge, with innovations in localized cooling techniques demonstrating up to 40% improvement in thermal stability for scaled systems.

Signal integrity across larger quantum FinFET arrays presents substantial challenges to maintaining coherent quantum operations. As system scale increases, maintaining synchronized control signals becomes exponentially more difficult, with studies showing signal degradation of approximately 15% for each doubling of system size. Advanced signal distribution networks utilizing superconducting materials have demonstrated potential to mitigate these effects, though implementation complexities remain significant.

Manufacturing consistency represents perhaps the most formidable barrier to quantum FinFET scalability. Current fabrication techniques struggle to maintain consistent transistor characteristics across large arrays, with variation increasing dramatically beyond certain fabrication thresholds. Statistical analysis of recent manufacturing runs shows that defect rates increase non-linearly with wafer size, necessitating advances in precision manufacturing and potentially self-correcting circuit designs.

Addressing these scalability challenges requires a multidisciplinary approach combining advances in materials science, cryogenic engineering, and quantum circuit design. Recent roadmaps from leading research institutions suggest that hybrid architectures, combining different qubit technologies with specialized FinFET control structures, may offer the most promising path toward scalable systems that can maintain acceptable latency profiles while supporting the computational requirements of practical quantum algorithms.

Physical layout constraints present a primary scalability challenge, as the three-dimensional nature of FinFET structures requires careful consideration of quantum interconnect topologies. Research indicates that beyond 50-100 qubits, traditional planar layouts become increasingly inefficient, necessitating novel 3D integration approaches that can maintain acceptable latency profiles while accommodating larger qubit arrays.

Thermal management emerges as another critical factor affecting scalability. As quantum FinFET systems scale up, heat dissipation becomes increasingly problematic, potentially destabilizing quantum states and introducing additional latency through thermal noise channels. Recent advancements in cryogenic cooling systems specifically designed for quantum FinFET architectures show promise in addressing this challenge, with innovations in localized cooling techniques demonstrating up to 40% improvement in thermal stability for scaled systems.

Signal integrity across larger quantum FinFET arrays presents substantial challenges to maintaining coherent quantum operations. As system scale increases, maintaining synchronized control signals becomes exponentially more difficult, with studies showing signal degradation of approximately 15% for each doubling of system size. Advanced signal distribution networks utilizing superconducting materials have demonstrated potential to mitigate these effects, though implementation complexities remain significant.

Manufacturing consistency represents perhaps the most formidable barrier to quantum FinFET scalability. Current fabrication techniques struggle to maintain consistent transistor characteristics across large arrays, with variation increasing dramatically beyond certain fabrication thresholds. Statistical analysis of recent manufacturing runs shows that defect rates increase non-linearly with wafer size, necessitating advances in precision manufacturing and potentially self-correcting circuit designs.

Addressing these scalability challenges requires a multidisciplinary approach combining advances in materials science, cryogenic engineering, and quantum circuit design. Recent roadmaps from leading research institutions suggest that hybrid architectures, combining different qubit technologies with specialized FinFET control structures, may offer the most promising path toward scalable systems that can maintain acceptable latency profiles while supporting the computational requirements of practical quantum algorithms.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!