Measuring FinFET Signal Delay: Best Practices And Standards

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Signal Delay Measurement Background and Objectives

FinFET technology has revolutionized semiconductor manufacturing since its commercial introduction in the early 2010s. The evolution of this three-dimensional transistor architecture represents a significant departure from traditional planar MOSFET designs, offering superior electrostatic control and reduced short-channel effects at advanced technology nodes. Signal delay measurement in FinFET devices has become increasingly critical as process geometries shrink below 10nm, where timing precision directly impacts system performance and power efficiency.

The historical progression of FinFET technology can be traced from early research at Berkeley in the late 1990s through industrial adoption beginning with Intel's 22nm node in 2011. Each subsequent technology generation has introduced new challenges in accurately measuring and characterizing signal propagation delays, necessitating continuous refinement of measurement methodologies and standards.

Current industry trends indicate a growing emphasis on precise delay measurement techniques as clock frequencies increase and timing margins decrease. The International Technology Roadmap for Semiconductors (ITRS) has consistently highlighted signal integrity and timing analysis as critical challenges for continued scaling of integrated circuits. This technical landscape underscores the importance of establishing standardized approaches to FinFET signal delay measurement.

The primary objectives of investigating FinFET signal delay measurement practices include establishing reproducible methodologies that account for the unique three-dimensional structure of these devices. This involves developing measurement protocols that accurately capture the complex capacitive and resistive parasitics inherent to FinFET architectures, which differ substantially from those in planar technologies.

Additionally, there is a pressing need to correlate simulation models with physical measurements across various operating conditions, including temperature variations, supply voltage fluctuations, and process corners. This correlation becomes increasingly challenging as devices scale down and quantum effects become more pronounced, requiring more sophisticated measurement techniques and equipment.

Another key objective is to standardize reporting metrics for signal delay in FinFET technologies, enabling meaningful comparisons across different process nodes, manufacturers, and design methodologies. This standardization effort must address the multi-dimensional nature of delay characteristics in modern FinFET devices, including considerations for different fin heights, widths, and multi-gate configurations.

The ultimate goal of these efforts is to provide semiconductor designers with reliable, accurate delay models that facilitate timing closure in complex system-on-chip designs utilizing advanced FinFET nodes. As the industry continues its march toward 3nm and beyond, the precision of signal delay measurement becomes increasingly fundamental to achieving performance targets while managing power constraints.

The historical progression of FinFET technology can be traced from early research at Berkeley in the late 1990s through industrial adoption beginning with Intel's 22nm node in 2011. Each subsequent technology generation has introduced new challenges in accurately measuring and characterizing signal propagation delays, necessitating continuous refinement of measurement methodologies and standards.

Current industry trends indicate a growing emphasis on precise delay measurement techniques as clock frequencies increase and timing margins decrease. The International Technology Roadmap for Semiconductors (ITRS) has consistently highlighted signal integrity and timing analysis as critical challenges for continued scaling of integrated circuits. This technical landscape underscores the importance of establishing standardized approaches to FinFET signal delay measurement.

The primary objectives of investigating FinFET signal delay measurement practices include establishing reproducible methodologies that account for the unique three-dimensional structure of these devices. This involves developing measurement protocols that accurately capture the complex capacitive and resistive parasitics inherent to FinFET architectures, which differ substantially from those in planar technologies.

Additionally, there is a pressing need to correlate simulation models with physical measurements across various operating conditions, including temperature variations, supply voltage fluctuations, and process corners. This correlation becomes increasingly challenging as devices scale down and quantum effects become more pronounced, requiring more sophisticated measurement techniques and equipment.

Another key objective is to standardize reporting metrics for signal delay in FinFET technologies, enabling meaningful comparisons across different process nodes, manufacturers, and design methodologies. This standardization effort must address the multi-dimensional nature of delay characteristics in modern FinFET devices, including considerations for different fin heights, widths, and multi-gate configurations.

The ultimate goal of these efforts is to provide semiconductor designers with reliable, accurate delay models that facilitate timing closure in complex system-on-chip designs utilizing advanced FinFET nodes. As the industry continues its march toward 3nm and beyond, the precision of signal delay measurement becomes increasingly fundamental to achieving performance targets while managing power constraints.

Market Demand Analysis for FinFET Signal Delay Solutions

The semiconductor industry has witnessed a significant surge in demand for accurate FinFET signal delay measurement solutions, driven primarily by the continuous miniaturization of transistor technology. As process nodes shrink below 10nm, timing precision becomes increasingly critical for maintaining performance integrity in integrated circuits. Market research indicates that the global semiconductor test equipment market, which includes signal delay measurement tools, is projected to reach $6 billion by 2026, with FinFET-specific testing solutions representing a substantial growth segment.

The demand for advanced signal delay measurement technologies stems from multiple sectors. Foremost among these is the mobile processor industry, where companies like Apple, Qualcomm, and MediaTek require precise timing characterization to optimize power consumption while maintaining performance targets. The automotive semiconductor segment presents another rapidly expanding market, with compound annual growth rates exceeding 8% as vehicles incorporate more advanced driver assistance systems and autonomous capabilities that demand highly reliable, timing-accurate components.

Data center and high-performance computing applications constitute a third major demand driver. As cloud infrastructure expands globally and AI workloads intensify, the need for server processors with optimized signal timing has created substantial market pull for sophisticated delay measurement solutions. Industry surveys reveal that over 70% of semiconductor manufacturers consider signal delay characterization a critical bottleneck in their production processes.

Geographically, the demand distribution shows concentration in East Asia, particularly Taiwan, South Korea, and China, where the majority of semiconductor fabrication occurs. However, significant research and development investments in signal delay measurement technologies are emerging from North America and Europe, where equipment manufacturers are developing next-generation solutions.

The market exhibits strong correlation between measurement precision requirements and pricing premiums. Solutions offering sub-picosecond accuracy command price premiums of 30-40% over standard measurement equipment, reflecting the critical value of timing precision in advanced node manufacturing.

Customer requirements analysis reveals five key demand factors: measurement accuracy at increasingly smaller time scales, integration with existing testing workflows, reduced testing time to improve throughput, comprehensive data analytics capabilities for identifying timing anomalies, and adaptability to various FinFET architectures from different foundries.

The market forecast indicates particularly strong growth in on-chip measurement solutions that can characterize signal delay during actual operation rather than in isolated test environments, reflecting the industry's movement toward more realistic performance assessment methodologies.

The demand for advanced signal delay measurement technologies stems from multiple sectors. Foremost among these is the mobile processor industry, where companies like Apple, Qualcomm, and MediaTek require precise timing characterization to optimize power consumption while maintaining performance targets. The automotive semiconductor segment presents another rapidly expanding market, with compound annual growth rates exceeding 8% as vehicles incorporate more advanced driver assistance systems and autonomous capabilities that demand highly reliable, timing-accurate components.

Data center and high-performance computing applications constitute a third major demand driver. As cloud infrastructure expands globally and AI workloads intensify, the need for server processors with optimized signal timing has created substantial market pull for sophisticated delay measurement solutions. Industry surveys reveal that over 70% of semiconductor manufacturers consider signal delay characterization a critical bottleneck in their production processes.

Geographically, the demand distribution shows concentration in East Asia, particularly Taiwan, South Korea, and China, where the majority of semiconductor fabrication occurs. However, significant research and development investments in signal delay measurement technologies are emerging from North America and Europe, where equipment manufacturers are developing next-generation solutions.

The market exhibits strong correlation between measurement precision requirements and pricing premiums. Solutions offering sub-picosecond accuracy command price premiums of 30-40% over standard measurement equipment, reflecting the critical value of timing precision in advanced node manufacturing.

Customer requirements analysis reveals five key demand factors: measurement accuracy at increasingly smaller time scales, integration with existing testing workflows, reduced testing time to improve throughput, comprehensive data analytics capabilities for identifying timing anomalies, and adaptability to various FinFET architectures from different foundries.

The market forecast indicates particularly strong growth in on-chip measurement solutions that can characterize signal delay during actual operation rather than in isolated test environments, reflecting the industry's movement toward more realistic performance assessment methodologies.

Current Challenges in FinFET Signal Delay Measurement

Despite significant advancements in FinFET technology, measuring signal delay in these devices presents several persistent challenges that impede accurate performance assessment. The nanoscale dimensions of modern FinFET structures create fundamental physical limitations for conventional measurement techniques. As device sizes approach sub-7nm nodes, quantum effects become increasingly prominent, introducing variability that traditional models struggle to account for.

One critical challenge is the increasing impact of parasitic capacitances and resistances that significantly affect signal propagation. These parasitics are becoming proportionally larger relative to the intrinsic device parameters as dimensions shrink, making it difficult to isolate true device performance from measurement artifacts. Furthermore, the three-dimensional nature of FinFET structures creates complex current paths that conventional two-dimensional models cannot adequately represent.

Temperature-dependent variations pose another significant obstacle. As operating frequencies increase, self-heating effects become more pronounced, creating thermal gradients across the device that dynamically alter performance characteristics during operation. Current measurement methodologies often fail to capture these thermal dynamics accurately, leading to discrepancies between measured and actual in-circuit performance.

Signal integrity issues further complicate delay measurements. At high frequencies, electromagnetic interference, crosstalk, and ground bounce create noise that can mask or distort the actual signal delay values. The industry lacks standardized methodologies for filtering these effects while preserving the integrity of delay measurements.

Process variations represent perhaps the most formidable challenge. Even minor manufacturing inconsistencies can lead to substantial performance differences between theoretically identical devices. This variability necessitates statistical approaches to delay measurement, yet there remains significant disagreement within the industry regarding appropriate statistical frameworks and confidence intervals.

Measurement equipment limitations also contribute to the challenge. Current probe technologies struggle to achieve the temporal resolution required for accurate characterization of cutting-edge FinFETs without introducing their own artifacts into the measurement process. The trade-off between measurement precision and the potential for the measurement apparatus to affect device behavior creates a fundamental dilemma.

Finally, there exists a significant gap between laboratory measurements and real-world performance. Test conditions rarely match the complex, dynamic environments in which FinFETs ultimately operate, raising questions about the practical relevance of standardized measurements. The industry continues to debate how to bridge this gap while maintaining measurement consistency and comparability across different devices and manufacturers.

One critical challenge is the increasing impact of parasitic capacitances and resistances that significantly affect signal propagation. These parasitics are becoming proportionally larger relative to the intrinsic device parameters as dimensions shrink, making it difficult to isolate true device performance from measurement artifacts. Furthermore, the three-dimensional nature of FinFET structures creates complex current paths that conventional two-dimensional models cannot adequately represent.

Temperature-dependent variations pose another significant obstacle. As operating frequencies increase, self-heating effects become more pronounced, creating thermal gradients across the device that dynamically alter performance characteristics during operation. Current measurement methodologies often fail to capture these thermal dynamics accurately, leading to discrepancies between measured and actual in-circuit performance.

Signal integrity issues further complicate delay measurements. At high frequencies, electromagnetic interference, crosstalk, and ground bounce create noise that can mask or distort the actual signal delay values. The industry lacks standardized methodologies for filtering these effects while preserving the integrity of delay measurements.

Process variations represent perhaps the most formidable challenge. Even minor manufacturing inconsistencies can lead to substantial performance differences between theoretically identical devices. This variability necessitates statistical approaches to delay measurement, yet there remains significant disagreement within the industry regarding appropriate statistical frameworks and confidence intervals.

Measurement equipment limitations also contribute to the challenge. Current probe technologies struggle to achieve the temporal resolution required for accurate characterization of cutting-edge FinFETs without introducing their own artifacts into the measurement process. The trade-off between measurement precision and the potential for the measurement apparatus to affect device behavior creates a fundamental dilemma.

Finally, there exists a significant gap between laboratory measurements and real-world performance. Test conditions rarely match the complex, dynamic environments in which FinFETs ultimately operate, raising questions about the practical relevance of standardized measurements. The industry continues to debate how to bridge this gap while maintaining measurement consistency and comparability across different devices and manufacturers.

Current Best Practices for FinFET Signal Delay Measurement

01 FinFET design optimization for signal delay reduction

Various design techniques can be employed to optimize FinFET structures specifically to reduce signal delay. These include adjusting fin dimensions, optimizing gate length, and modifying channel characteristics. By carefully engineering these parameters, designers can achieve significant improvements in signal propagation speed through FinFET-based circuits, resulting in overall better performance for high-speed applications.- FinFET design optimization for signal delay reduction: Various design techniques can be employed to optimize FinFET structures specifically to reduce signal delay. These include adjustments to fin dimensions, gate length optimization, and transistor sizing strategies. By carefully engineering these parameters, designers can minimize parasitic capacitances and resistances that contribute to signal propagation delays in FinFET-based circuits.

- Clock and signal synchronization techniques in FinFET circuits: Specialized clock distribution networks and signal synchronization methods can be implemented in FinFET-based designs to manage signal delays. These techniques include clock tree optimization, skew minimization strategies, and advanced clock gating approaches that are specifically tailored for the unique characteristics of FinFET technology, helping to maintain timing integrity across complex integrated circuits.

- Power management for delay optimization in FinFET circuits: Power management techniques can significantly impact signal delay in FinFET circuits. By implementing adaptive voltage scaling, dynamic frequency adjustment, and power gating strategies, designers can optimize the power-delay tradeoff in FinFET-based systems. These approaches help maintain performance while managing power consumption, which directly affects signal propagation characteristics.

- Buffer and repeater design for FinFET signal paths: Strategic placement and sizing of buffers and repeaters along signal paths can effectively manage signal delays in FinFET circuits. These components can be optimized for the specific electrical characteristics of FinFET technology, including their placement, sizing, and driving strength, to maintain signal integrity and minimize propagation delays across long interconnects.

- Advanced modeling and simulation techniques for FinFET delay analysis: Sophisticated modeling and simulation methodologies have been developed specifically for analyzing and predicting signal delays in FinFET circuits. These include compact models that accurately capture the unique three-dimensional structure of FinFETs, statistical variation analysis, and machine learning approaches that help designers predict and optimize timing performance during the design phase.

02 Clock and timing control in FinFET circuits

Specialized clock distribution networks and timing control mechanisms can be implemented in FinFET-based designs to manage signal delay. These approaches include adaptive clock gating, dynamic frequency scaling, and phase-locked loop optimization tailored for FinFET technology. Such techniques help maintain signal integrity while minimizing propagation delays across complex integrated circuits.Expand Specific Solutions03 Buffer and repeater design for FinFET signal paths

Strategic placement of buffers and signal repeaters in FinFET circuits can effectively manage signal delay across long interconnect paths. By optimizing buffer sizing, placement algorithms, and repeater configurations specifically for FinFET technology characteristics, designers can maintain signal integrity while minimizing propagation delay in complex integrated circuits.Expand Specific Solutions04 Power management techniques to control FinFET signal delay

Various power management approaches can be implemented to optimize signal delay in FinFET circuits. These include adaptive voltage scaling, multi-threshold voltage design, and power gating techniques specifically tailored for FinFET technology. By carefully managing power consumption and distribution, these methods help maintain optimal signal propagation speeds while minimizing energy usage.Expand Specific Solutions05 Simulation and modeling techniques for FinFET signal delay analysis

Advanced simulation and modeling methodologies have been developed specifically for analyzing and predicting signal delay in FinFET-based circuits. These approaches include multi-physics simulations, statistical timing analysis, and machine learning-based prediction models that account for the unique three-dimensional structure of FinFETs. Such tools enable designers to accurately estimate and optimize signal propagation characteristics during the design phase.Expand Specific Solutions

Key Industry Players in FinFET Testing and Measurement

The FinFET signal delay measurement landscape is currently in a growth phase, with the market expanding as advanced semiconductor technologies become more prevalent. The global competition is characterized by established leaders like TSMC, which dominates with mature FinFET processes, alongside emerging players such as SMIC and IBM developing competitive solutions. Technical maturity varies significantly across companies, with TSMC, IBM, and Synopsys demonstrating advanced measurement methodologies, while NXP, Renesas, and MaxLinear focus on application-specific optimizations. Research institutions like the Institute of Microelectronics of Chinese Academy of Sciences are contributing to standardization efforts. The market is expected to grow as FinFET technology becomes more widespread in high-performance computing, mobile devices, and automotive applications, driving demand for precise signal delay measurement solutions.

Semiconductor Manufacturing International (Shanghai) Corp.

Technical Solution: SMIC has developed an integrated FinFET signal delay measurement framework tailored to their manufacturing processes. Their methodology combines physical measurements using scanning electron microscopy (SEM) with electrical characterization to establish correlations between physical variations and timing performance. SMIC's approach incorporates dedicated test structures distributed across the wafer to capture process variations and their impact on signal delay. Their system utilizes adaptive sampling techniques that focus measurement resources on critical areas identified through preliminary analysis, improving efficiency without sacrificing accuracy. SMIC has developed specialized extraction models that account for the unique characteristics of their FinFET process, including fin height variations and gate length fluctuations. Their methodology includes comprehensive statistical analysis that enables designers to understand not just nominal delays but also their distribution across manufacturing variations, supporting robust design practices.

Strengths: Tight integration with manufacturing process; efficient resource utilization through adaptive sampling; comprehensive statistical characterization. Weaknesses: Less mature than some competitors' solutions; limited third-party tool support; primarily focused on their own process technologies.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed an advanced on-chip variation (OCV) measurement methodology specifically for FinFET technology that combines statistical analysis with direct measurement techniques. Their approach utilizes ring oscillator arrays strategically placed across the die to capture spatial and temporal variations in signal delay. TSMC's methodology incorporates multi-corner characterization that accounts for process, voltage, and temperature (PVT) variations, enabling accurate delay modeling across different operating conditions. Their proprietary Signal Integrity Analysis System (SIAS) integrates with standard EDA tools to provide comprehensive delay analysis that considers both local and global variations in FinFET structures. TSMC has also pioneered the use of embedded test structures that can be measured post-manufacturing to validate simulation models and improve correlation between predicted and actual signal delays.

Strengths: Industry-leading process technology with extensive experience in FinFET manufacturing; comprehensive measurement infrastructure; strong correlation between simulation and silicon results. Weaknesses: Proprietary methodologies may limit compatibility with some third-party tools; requires significant computational resources for full-chip analysis.

Critical Patents and Technologies in FinFET Signal Analysis

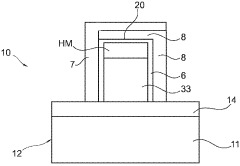

Fin-type field effect transistor

PatentActiveEP1920467A2

Innovation

- The FinFET structure is configured asymmetrically to decrease resistance between the gate and the source region and increase resistance between the gate and the drain region, and ballasted by adjusting fin dimensions and dopant concentrations to prevent thermal runaway, allowing operation at higher voltages.

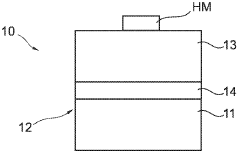

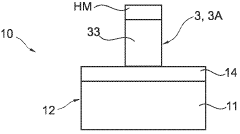

Transistor device and method of manufacturing such a transistor device

PatentWO2008072164A1

Innovation

- A transistor device with a fin structure combining FinFET and TFET technologies, featuring separate gate regions with different work functions for N-type and P-type tunneling field effect transistors, allowing for high-density integration and reduced static leakage current.

Standardization Efforts in FinFET Performance Testing

The semiconductor industry has recognized the critical need for standardized approaches to FinFET performance testing, particularly regarding signal delay measurements. Several key organizations have been instrumental in developing these standards, with the IEEE P2416 working group leading efforts to establish consistent methodologies for power and performance modeling of electronic systems.

The Joint Electron Device Engineering Council (JEDEC) has published multiple standards specifically addressing FinFET characterization, including JEP122H which outlines failure mechanisms and models for reliability testing. These standards provide semiconductor manufacturers with unified testing protocols that enable meaningful comparisons across different FinFET implementations.

The Semiconductor Research Corporation (SRC) has funded collaborative research initiatives between industry and academia to develop standardized test structures and measurement techniques. These efforts have resulted in the creation of reference designs that serve as benchmarks for evaluating signal propagation delays in various FinFET configurations.

International Technology Roadmap for Semiconductors (ITRS) has incorporated specific metrics for FinFET performance evaluation in their roadmap documents, establishing industry-wide targets for signal delay improvements. These metrics have become de facto standards that guide research and development activities across the semiconductor ecosystem.

The Silicon Integration Initiative (Si2) has developed open standards for FinFET device modeling, including the Compact Model Coalition (CMC) that standardizes SPICE models used for signal delay simulations. These standardized models ensure consistency in how delay characteristics are predicted during the design phase.

Testing equipment manufacturers have also contributed to standardization by developing calibration procedures specific to FinFET measurements. Companies like Keysight Technologies and Advantest have created reference measurement systems that implement these standards, ensuring measurement consistency across different testing facilities.

Recent collaborative efforts between major semiconductor manufacturers have focused on establishing standard test circuits for benchmarking FinFET performance. These circuits, often referred to as "golden circuits," provide a consistent basis for comparing signal delay characteristics across different process nodes and manufacturer implementations.

The Global Semiconductor Alliance (GSA) has established working groups dedicated to harmonizing test methodologies across the industry, with particular emphasis on high-frequency performance metrics relevant to advanced FinFET technologies. Their published guidelines have been widely adopted by both integrated device manufacturers and foundries.

The Joint Electron Device Engineering Council (JEDEC) has published multiple standards specifically addressing FinFET characterization, including JEP122H which outlines failure mechanisms and models for reliability testing. These standards provide semiconductor manufacturers with unified testing protocols that enable meaningful comparisons across different FinFET implementations.

The Semiconductor Research Corporation (SRC) has funded collaborative research initiatives between industry and academia to develop standardized test structures and measurement techniques. These efforts have resulted in the creation of reference designs that serve as benchmarks for evaluating signal propagation delays in various FinFET configurations.

International Technology Roadmap for Semiconductors (ITRS) has incorporated specific metrics for FinFET performance evaluation in their roadmap documents, establishing industry-wide targets for signal delay improvements. These metrics have become de facto standards that guide research and development activities across the semiconductor ecosystem.

The Silicon Integration Initiative (Si2) has developed open standards for FinFET device modeling, including the Compact Model Coalition (CMC) that standardizes SPICE models used for signal delay simulations. These standardized models ensure consistency in how delay characteristics are predicted during the design phase.

Testing equipment manufacturers have also contributed to standardization by developing calibration procedures specific to FinFET measurements. Companies like Keysight Technologies and Advantest have created reference measurement systems that implement these standards, ensuring measurement consistency across different testing facilities.

Recent collaborative efforts between major semiconductor manufacturers have focused on establishing standard test circuits for benchmarking FinFET performance. These circuits, often referred to as "golden circuits," provide a consistent basis for comparing signal delay characteristics across different process nodes and manufacturer implementations.

The Global Semiconductor Alliance (GSA) has established working groups dedicated to harmonizing test methodologies across the industry, with particular emphasis on high-frequency performance metrics relevant to advanced FinFET technologies. Their published guidelines have been widely adopted by both integrated device manufacturers and foundries.

Power-Performance Tradeoffs in FinFET Signal Measurement

The intricate relationship between power consumption and performance in FinFET signal measurement represents a critical consideration for modern semiconductor design. As transistor dimensions continue to shrink, the balance between power efficiency and signal performance becomes increasingly delicate, requiring sophisticated measurement and optimization techniques.

Power consumption in FinFET devices manifests in three primary forms: dynamic power, static leakage power, and short-circuit power. Dynamic power occurs during transistor switching operations, while static leakage persists even when the device is inactive. The measurement of signal delay must account for these power components, as they directly influence timing characteristics and overall circuit performance.

When measuring FinFET signal delay, engineers face a fundamental tradeoff: increasing operating voltage improves performance by reducing delay times but simultaneously increases power consumption quadratically. This relationship necessitates careful calibration of measurement parameters to achieve optimal results for specific application requirements.

Industry standards have evolved to address these tradeoffs through various measurement methodologies. The constant-current method provides excellent sensitivity to delay variations but may consume more power during measurement. Conversely, the constant-voltage approach offers better power efficiency but potentially reduced measurement precision, particularly at lower voltages where noise becomes more significant.

Temperature effects further complicate the power-performance equation. Higher operating temperatures increase electron mobility, potentially improving performance, but simultaneously increase leakage current and overall power consumption. Measurement protocols must therefore incorporate temperature compensation techniques to ensure consistent and comparable results across different operating conditions.

Advanced measurement techniques such as on-chip monitoring systems enable real-time power-performance optimization. These systems can dynamically adjust operating parameters based on workload requirements, maintaining an optimal balance between power efficiency and performance. However, implementing such systems introduces additional circuit complexity and potential measurement overhead.

The industry continues to develop standardized benchmarking methodologies that quantify the power-performance tradeoff. Metrics such as the Energy-Delay Product (EDP) and Power-Delay Product (PDP) provide normalized frameworks for comparing different FinFET technologies and measurement approaches. These metrics help designers make informed decisions when balancing competing requirements for power efficiency and signal performance.

Power consumption in FinFET devices manifests in three primary forms: dynamic power, static leakage power, and short-circuit power. Dynamic power occurs during transistor switching operations, while static leakage persists even when the device is inactive. The measurement of signal delay must account for these power components, as they directly influence timing characteristics and overall circuit performance.

When measuring FinFET signal delay, engineers face a fundamental tradeoff: increasing operating voltage improves performance by reducing delay times but simultaneously increases power consumption quadratically. This relationship necessitates careful calibration of measurement parameters to achieve optimal results for specific application requirements.

Industry standards have evolved to address these tradeoffs through various measurement methodologies. The constant-current method provides excellent sensitivity to delay variations but may consume more power during measurement. Conversely, the constant-voltage approach offers better power efficiency but potentially reduced measurement precision, particularly at lower voltages where noise becomes more significant.

Temperature effects further complicate the power-performance equation. Higher operating temperatures increase electron mobility, potentially improving performance, but simultaneously increase leakage current and overall power consumption. Measurement protocols must therefore incorporate temperature compensation techniques to ensure consistent and comparable results across different operating conditions.

Advanced measurement techniques such as on-chip monitoring systems enable real-time power-performance optimization. These systems can dynamically adjust operating parameters based on workload requirements, maintaining an optimal balance between power efficiency and performance. However, implementing such systems introduces additional circuit complexity and potential measurement overhead.

The industry continues to develop standardized benchmarking methodologies that quantify the power-performance tradeoff. Metrics such as the Energy-Delay Product (EDP) and Power-Delay Product (PDP) provide normalized frameworks for comparing different FinFET technologies and measurement approaches. These metrics help designers make informed decisions when balancing competing requirements for power efficiency and signal performance.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!