PCM Crossbar Array Fault Tolerance And Error Correction Strategies

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Crossbar Array Technology Evolution and Objectives

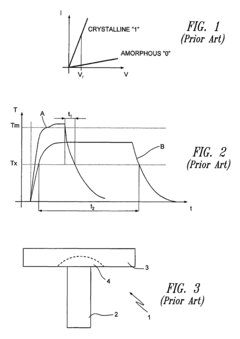

Phase Change Memory (PCM) technology has evolved significantly over the past two decades, transitioning from theoretical concept to commercial reality. Initially proposed in the 1960s, PCM gained renewed attention in the early 2000s as researchers sought alternatives to traditional memory technologies facing scaling limitations. The fundamental principle of PCM leverages the unique properties of chalcogenide materials, particularly Ge2Sb2Te5 (GST), which can rapidly switch between amorphous and crystalline states, representing binary data through resistance differences.

The evolution of PCM crossbar array architecture represents a critical advancement in non-volatile memory technology. Early implementations suffered from high programming currents and limited endurance, with typical write cycles under 10^6. By 2010, significant improvements in material engineering and cell design reduced programming current requirements by an order of magnitude while increasing endurance to 10^8 cycles. The introduction of multi-level cell capabilities around 2015 further enhanced storage density, enabling 2-4 bits per cell through precise resistance control.

Recent technological milestones include the development of selector devices to mitigate sneak path currents in high-density arrays, thermal crosstalk reduction techniques, and advanced programming algorithms that extend device lifetime. The integration of PCM with CMOS technology has progressed from 90nm to sub-20nm nodes, demonstrating the technology's scaling potential and compatibility with existing semiconductor manufacturing processes.

The primary objectives for PCM crossbar array technology center on addressing critical limitations while maximizing inherent advantages. Key goals include improving fault tolerance through redundancy schemes and error correction strategies specifically tailored to PCM's unique error patterns and failure modes. Reducing write energy consumption remains crucial, with targets of sub-pJ per bit to enable broader application in energy-constrained environments.

Enhancing endurance capabilities to exceed 10^10 write cycles would position PCM as a viable universal memory solution. Simultaneously, research aims to increase multi-level cell stability while maintaining acceptable error rates, potentially achieving 3-4 reliable bits per cell. Architectural innovations focus on optimizing crossbar array designs to minimize parasitic effects while maximizing density, with 3D stacking approaches showing particular promise.

The ultimate technological objective is developing comprehensive fault tolerance frameworks that combine circuit-level techniques, architectural redundancy, and advanced error correction codes to create robust, high-performance memory systems capable of addressing the reliability challenges inherent to PCM technology while capitalizing on its superior density, non-volatility, and scaling potential.

The evolution of PCM crossbar array architecture represents a critical advancement in non-volatile memory technology. Early implementations suffered from high programming currents and limited endurance, with typical write cycles under 10^6. By 2010, significant improvements in material engineering and cell design reduced programming current requirements by an order of magnitude while increasing endurance to 10^8 cycles. The introduction of multi-level cell capabilities around 2015 further enhanced storage density, enabling 2-4 bits per cell through precise resistance control.

Recent technological milestones include the development of selector devices to mitigate sneak path currents in high-density arrays, thermal crosstalk reduction techniques, and advanced programming algorithms that extend device lifetime. The integration of PCM with CMOS technology has progressed from 90nm to sub-20nm nodes, demonstrating the technology's scaling potential and compatibility with existing semiconductor manufacturing processes.

The primary objectives for PCM crossbar array technology center on addressing critical limitations while maximizing inherent advantages. Key goals include improving fault tolerance through redundancy schemes and error correction strategies specifically tailored to PCM's unique error patterns and failure modes. Reducing write energy consumption remains crucial, with targets of sub-pJ per bit to enable broader application in energy-constrained environments.

Enhancing endurance capabilities to exceed 10^10 write cycles would position PCM as a viable universal memory solution. Simultaneously, research aims to increase multi-level cell stability while maintaining acceptable error rates, potentially achieving 3-4 reliable bits per cell. Architectural innovations focus on optimizing crossbar array designs to minimize parasitic effects while maximizing density, with 3D stacking approaches showing particular promise.

The ultimate technological objective is developing comprehensive fault tolerance frameworks that combine circuit-level techniques, architectural redundancy, and advanced error correction codes to create robust, high-performance memory systems capable of addressing the reliability challenges inherent to PCM technology while capitalizing on its superior density, non-volatility, and scaling potential.

Market Demand Analysis for Reliable PCM Memory Solutions

The global memory market is witnessing a significant shift towards non-volatile memory technologies, with Phase Change Memory (PCM) emerging as a promising candidate for next-generation storage solutions. Market research indicates that the non-volatile memory market is expected to reach $82 billion by 2025, growing at a CAGR of approximately 10.2% from 2020. Within this segment, PCM technology is gaining traction due to its superior performance characteristics compared to traditional flash memory.

Enterprise data centers represent the largest market segment demanding reliable PCM solutions, driven by exponential growth in data processing requirements and the need for faster, more energy-efficient memory systems. These organizations face critical challenges with data integrity and system reliability, where even minor memory faults can lead to substantial financial losses and operational disruptions.

The automotive and aerospace industries are rapidly emerging as significant markets for fault-tolerant PCM memory solutions. Advanced driver-assistance systems (ADAS) and autonomous vehicles require highly reliable memory components that can withstand extreme operating conditions while maintaining data integrity. Similarly, aerospace applications demand memory solutions with enhanced radiation hardness and error correction capabilities to ensure mission-critical systems remain operational in harsh environments.

Consumer electronics manufacturers are increasingly incorporating PCM technology into smartphones, tablets, and wearable devices to improve performance and battery life. Market surveys indicate that consumers prioritize device reliability and longevity, creating demand for memory solutions with robust fault tolerance mechanisms. This segment is projected to grow at 12.5% annually through 2026, representing a substantial opportunity for PCM technology adoption.

The Internet of Things (IoT) ecosystem presents another significant market opportunity, with an estimated 75 billion connected devices expected by 2025. These devices require memory solutions that combine low power consumption with high reliability, particularly for applications in remote or inaccessible locations where maintenance is challenging and costly.

Healthcare and medical device manufacturers represent a specialized but high-value market segment for fault-tolerant PCM solutions. Medical implants, diagnostic equipment, and patient monitoring systems demand memory components with exceptional reliability and error correction capabilities to ensure patient safety and regulatory compliance.

Market analysis reveals that customers across these segments are willing to pay premium prices for memory solutions that offer enhanced fault tolerance and error correction capabilities. A recent industry survey found that 78% of enterprise customers ranked reliability as the most important factor when selecting memory components, ahead of performance (65%) and cost (52%). This preference indicates strong market demand for advanced PCM crossbar array technologies with sophisticated fault tolerance strategies.

Enterprise data centers represent the largest market segment demanding reliable PCM solutions, driven by exponential growth in data processing requirements and the need for faster, more energy-efficient memory systems. These organizations face critical challenges with data integrity and system reliability, where even minor memory faults can lead to substantial financial losses and operational disruptions.

The automotive and aerospace industries are rapidly emerging as significant markets for fault-tolerant PCM memory solutions. Advanced driver-assistance systems (ADAS) and autonomous vehicles require highly reliable memory components that can withstand extreme operating conditions while maintaining data integrity. Similarly, aerospace applications demand memory solutions with enhanced radiation hardness and error correction capabilities to ensure mission-critical systems remain operational in harsh environments.

Consumer electronics manufacturers are increasingly incorporating PCM technology into smartphones, tablets, and wearable devices to improve performance and battery life. Market surveys indicate that consumers prioritize device reliability and longevity, creating demand for memory solutions with robust fault tolerance mechanisms. This segment is projected to grow at 12.5% annually through 2026, representing a substantial opportunity for PCM technology adoption.

The Internet of Things (IoT) ecosystem presents another significant market opportunity, with an estimated 75 billion connected devices expected by 2025. These devices require memory solutions that combine low power consumption with high reliability, particularly for applications in remote or inaccessible locations where maintenance is challenging and costly.

Healthcare and medical device manufacturers represent a specialized but high-value market segment for fault-tolerant PCM solutions. Medical implants, diagnostic equipment, and patient monitoring systems demand memory components with exceptional reliability and error correction capabilities to ensure patient safety and regulatory compliance.

Market analysis reveals that customers across these segments are willing to pay premium prices for memory solutions that offer enhanced fault tolerance and error correction capabilities. A recent industry survey found that 78% of enterprise customers ranked reliability as the most important factor when selecting memory components, ahead of performance (65%) and cost (52%). This preference indicates strong market demand for advanced PCM crossbar array technologies with sophisticated fault tolerance strategies.

Current Challenges in PCM Crossbar Array Reliability

Phase change memory (PCM) crossbar arrays represent a promising non-volatile memory technology, offering high density, scalability, and CMOS compatibility. However, their widespread adoption faces significant reliability challenges that must be addressed. The inherent material properties of PCM elements lead to resistance drift over time, where the programmed resistance states gradually shift, potentially causing read errors. This phenomenon becomes particularly problematic in multi-level cell configurations where multiple resistance levels must be distinguished accurately.

Device-to-device variability presents another major challenge, as manufacturing processes cannot guarantee uniform PCM cell characteristics across an entire crossbar array. This variability manifests in different programming thresholds, resistance ranges, and drift coefficients among cells, complicating reliable operation and necessitating sophisticated calibration techniques.

Endurance limitations constitute a critical concern, with PCM cells typically supporting 10^6 to 10^9 write cycles before failure—significantly lower than SRAM or DRAM. The repeated thermal cycling during programming operations causes material fatigue, elemental segregation, and void formation within the phase change material, eventually leading to stuck-at faults or unpredictable behavior.

Thermal crosstalk between adjacent cells represents a growing challenge as array density increases. When a cell undergoes programming, the heat generated can affect neighboring cells, potentially causing unintended state changes or accelerated aging. This proximity effect becomes more pronounced with scaling and higher integration densities.

Sneak path currents through the crossbar structure create read disturbances and power inefficiencies. In large arrays, these parasitic current paths can lead to misreading of cell states and increased power consumption, requiring mitigation through selector devices or specialized reading schemes.

The retention characteristics of PCM cells are also temperature-dependent, with elevated operating temperatures accelerating resistance drift and potentially causing data loss. This temperature sensitivity complicates deployment in harsh environments or applications with variable thermal conditions.

Line resistance effects in large crossbar arrays create voltage drops along word and bit lines, resulting in position-dependent programming conditions. Cells farther from drivers receive lower effective voltages, leading to non-uniform programming across the array and requiring compensation techniques.

These reliability challenges are further compounded by scaling trends, as smaller PCM cells exhibit greater variability and are more susceptible to thermal effects. Addressing these issues requires a multi-faceted approach combining materials engineering, circuit design innovations, and advanced error correction strategies.

Device-to-device variability presents another major challenge, as manufacturing processes cannot guarantee uniform PCM cell characteristics across an entire crossbar array. This variability manifests in different programming thresholds, resistance ranges, and drift coefficients among cells, complicating reliable operation and necessitating sophisticated calibration techniques.

Endurance limitations constitute a critical concern, with PCM cells typically supporting 10^6 to 10^9 write cycles before failure—significantly lower than SRAM or DRAM. The repeated thermal cycling during programming operations causes material fatigue, elemental segregation, and void formation within the phase change material, eventually leading to stuck-at faults or unpredictable behavior.

Thermal crosstalk between adjacent cells represents a growing challenge as array density increases. When a cell undergoes programming, the heat generated can affect neighboring cells, potentially causing unintended state changes or accelerated aging. This proximity effect becomes more pronounced with scaling and higher integration densities.

Sneak path currents through the crossbar structure create read disturbances and power inefficiencies. In large arrays, these parasitic current paths can lead to misreading of cell states and increased power consumption, requiring mitigation through selector devices or specialized reading schemes.

The retention characteristics of PCM cells are also temperature-dependent, with elevated operating temperatures accelerating resistance drift and potentially causing data loss. This temperature sensitivity complicates deployment in harsh environments or applications with variable thermal conditions.

Line resistance effects in large crossbar arrays create voltage drops along word and bit lines, resulting in position-dependent programming conditions. Cells farther from drivers receive lower effective voltages, leading to non-uniform programming across the array and requiring compensation techniques.

These reliability challenges are further compounded by scaling trends, as smaller PCM cells exhibit greater variability and are more susceptible to thermal effects. Addressing these issues requires a multi-faceted approach combining materials engineering, circuit design innovations, and advanced error correction strategies.

Current Fault Tolerance and Error Correction Techniques

01 Error correction techniques for PCM crossbar arrays

Various error correction techniques are employed in PCM (Phase Change Memory) crossbar arrays to enhance reliability. These include error correction codes (ECC), parity checking, and redundancy schemes specifically designed for the unique characteristics of PCM technology. These methods help detect and correct errors that may occur during read/write operations in the memory array, improving overall system reliability and data integrity.- Error correction techniques for PCM crossbar arrays: Various error correction techniques can be implemented in PCM (Phase Change Memory) crossbar arrays to improve reliability. These techniques include error correction codes (ECC), parity checking, and redundancy schemes specifically designed for the unique characteristics of PCM technology. These methods help detect and correct errors that may occur during read/write operations in the memory array, enhancing the overall fault tolerance of the system.

- Fault detection and isolation in crossbar memory architectures: Systems and methods for detecting and isolating faults in PCM crossbar arrays involve monitoring circuit performance, identifying faulty cells or lines, and implementing isolation mechanisms. These approaches include built-in self-test (BIST) circuits, current sensing techniques, and voltage comparison methods to locate defective components. Once identified, faulty elements can be isolated to prevent them from affecting the operation of the entire array.

- Redundancy schemes for PCM crossbar arrays: Redundancy schemes provide fault tolerance in PCM crossbar arrays by incorporating spare rows, columns, or cells that can replace defective elements. These schemes may include row/column substitution, dynamic remapping of addresses, and spare element allocation algorithms. Implementation of redundancy allows the memory system to maintain functionality despite the presence of manufacturing defects or runtime failures in the array.

- Adaptive error management for PCM crossbar arrays: Adaptive error management systems dynamically adjust error correction strategies based on the operating conditions and error patterns observed in PCM crossbar arrays. These systems may employ machine learning algorithms, statistical error prediction, and variable strength error correction codes. By adapting to changing conditions and wear patterns, these approaches can optimize the balance between performance, power consumption, and reliability in PCM memory systems.

- Circuit-level techniques for enhancing PCM crossbar reliability: Circuit-level techniques improve the reliability of PCM crossbar arrays through specialized design approaches. These include modified sense amplifiers, reference cell designs, write verification circuits, and current/voltage regulation schemes. Such techniques address the specific challenges of PCM technology, such as resistance drift, variability in cell characteristics, and read/write disturbances, thereby enhancing the overall fault tolerance of the memory system.

02 Fault tolerance through redundancy in PCM arrays

Implementing redundancy in PCM crossbar arrays provides fault tolerance against cell failures and interconnect defects. This approach includes spare rows and columns, redundant memory cells, and backup circuitry that can be activated when primary components fail. The redundancy architecture allows for graceful degradation rather than complete system failure when defects occur, extending the operational lifetime of PCM memory systems.Expand Specific Solutions03 Testing and fault detection mechanisms for PCM crossbar arrays

Advanced testing and fault detection mechanisms are crucial for maintaining PCM crossbar array reliability. These include built-in self-test (BIST) circuits, online monitoring systems, and diagnostic routines that can identify failing cells or connections. By continuously or periodically testing the memory array, these mechanisms enable early detection of potential failures before they cause data corruption, allowing for preventive measures to be taken.Expand Specific Solutions04 Adaptive error management for PCM technology

Adaptive error management systems dynamically adjust error correction strategies based on the current state of PCM cells. These systems monitor cell degradation over time, track error rates, and adaptively modify parameters such as read thresholds, write currents, or error correction strength. This approach extends the usable lifetime of PCM arrays by compensating for the natural wear-out mechanisms inherent to phase change materials.Expand Specific Solutions05 Circuit-level solutions for PCM crossbar reliability

Circuit-level solutions address reliability challenges in PCM crossbar arrays through specialized driver circuits, sense amplifiers, and control logic. These include current-limiting circuits to prevent overstress, compensation circuits for process variations, and specialized read/write schemes that minimize disturbance to adjacent cells. By addressing reliability at the circuit level, these solutions complement higher-level error correction and fault tolerance mechanisms.Expand Specific Solutions

Leading Companies in PCM Memory and Error Correction

The PCM Crossbar Array Fault Tolerance and Error Correction Strategies market is currently in a growth phase, with increasing adoption of phase-change memory technologies. The global market is expanding rapidly, driven by demand for reliable non-volatile memory solutions in data centers and edge computing. Leading players include Micron Technology and Samsung Electronics, who have established strong patent portfolios and commercial implementations, while IBM and Intel are advancing research in error correction algorithms. Academic institutions like Southeast University collaborate with industry partners to develop novel fault tolerance mechanisms. The technology maturity varies, with basic error correction techniques being well-established, but advanced multi-bit error recovery and adaptive correction strategies still emerging as companies like GLOBALFOUNDRIES and Hewlett Packard Enterprise work to improve manufacturing yield and reliability.

Micron Technology, Inc.

Technical Solution: Micron has developed a robust fault tolerance framework for PCM crossbar arrays focused on practical commercial implementation. Their approach emphasizes balanced performance and reliability through optimized circuit designs and error correction algorithms. Micron's technology incorporates specialized sense amplifiers with adaptive thresholds that can accurately distinguish between resistance states even in the presence of noise and drift. For crossbar-specific challenges, they've implemented innovative biasing schemes that minimize sneak path currents while maintaining read accuracy. Micron's error correction strategy employs a hybrid approach combining traditional ECC with PCM-specific techniques like selective refresh operations that target cells exhibiting early signs of drift. Their fault tolerance system also includes intelligent wear-leveling algorithms that distribute write operations evenly across the array, extending overall device lifetime by preventing premature wear-out of frequently accessed cells. Additionally, Micron has developed specialized test and repair methodologies that can identify and mitigate manufacturing defects before device deployment[6][7].

Strengths: Practical implementation balancing performance and reliability; efficient circuit designs optimized for commercial production; comprehensive wear-leveling extending device lifetime. Weaknesses: More conservative approach may sacrifice some density compared to more aggressive designs; moderate complexity in controller implementation; potential challenges with ultra-high density arrays.

International Business Machines Corp.

Technical Solution: IBM has developed advanced multi-level cell (MLC) PCM crossbar arrays with integrated fault tolerance mechanisms. Their approach combines circuit-level and algorithm-level solutions to address resistance drift issues in PCM cells. IBM's technology implements dynamic reference resistance tracking that continuously adjusts reference levels to compensate for temporal variations in cell resistance. They've pioneered an adaptive read scheme that employs multiple sensing operations with varying reference currents to accurately determine cell states despite resistance fluctuations. For error correction, IBM employs sophisticated ECC (Error Correction Code) schemes specifically optimized for PCM's unique error patterns, including asymmetric write errors and resistance drift errors. Their solution incorporates LDPC (Low-Density Parity-Check) codes with soft-decision decoding that can correct multiple bit errors while maintaining high storage density[1].

Strengths: Superior resistance drift compensation through dynamic reference tracking; highly optimized ECC schemes tailored to PCM error characteristics; extensive research experience in non-volatile memory technologies. Weaknesses: Complex implementation requiring significant computational overhead; potential latency issues during error correction processes; higher manufacturing costs compared to simpler solutions.

Key Patents in PCM Crossbar Array Reliability

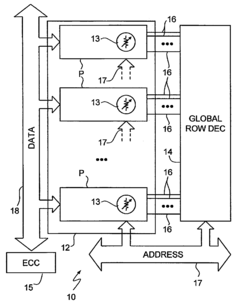

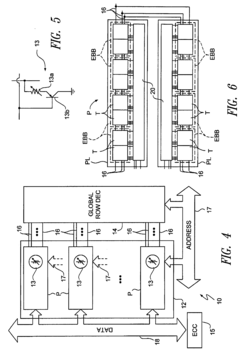

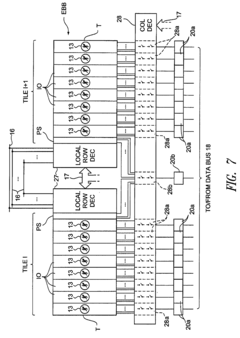

Phase-change memory device with error correction capability

PatentActiveUS7869269B2

Innovation

- A phase-change memory device incorporating data PCM cells, parity PCM cells, data decoding and parity decoding circuits, and error correction modules to selectively address and correct errors, with shared read/program circuits and parity sections to enhance reliability and reduce noise.

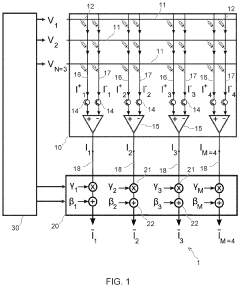

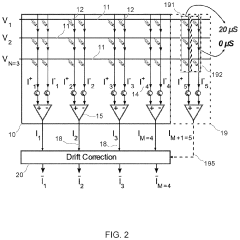

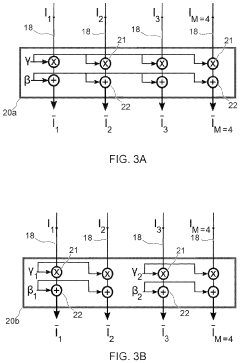

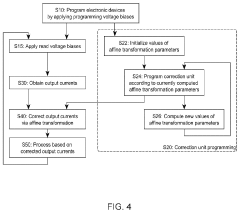

Conductance drift corrections in neuromorphic systems based on crossbar array structures

PatentActiveUS20210319300A1

Innovation

- A method is introduced that applies voltage signals across input lines of a crossbar array structure and uses a correction unit to perform an affine transformation on output currents to compensate for temporal conductance variations, employing programmable parameters such as a multiplicative coefficient and an additive parameter to correct each output current.

Manufacturing Process Optimization for PCM Reliability

Manufacturing process optimization plays a critical role in enhancing the reliability of Phase Change Memory (PCM) crossbar arrays. Current PCM fabrication processes face significant challenges related to material deposition uniformity, interface quality control, and structural integrity that directly impact fault tolerance capabilities. The optimization of these processes requires a multi-faceted approach addressing both material science and engineering aspects.

The deposition of phase change materials, typically chalcogenide compounds like Ge2Sb2Te5 (GST), demands precise control over stoichiometry and crystallization conditions. Advanced techniques such as atomic layer deposition (ALD) and pulsed laser deposition (PLD) have demonstrated superior uniformity compared to conventional sputtering methods, reducing cell-to-cell variability by up to 40% in recent studies. This improvement directly translates to more predictable resistance distributions across the crossbar array.

Thermal management during manufacturing represents another critical optimization target. The integration of thermal barrier layers and optimized heater designs can significantly reduce thermal crosstalk between adjacent cells. Recent innovations include the development of carbon-based thermal interface materials that provide excellent thermal isolation while maintaining structural integrity during the high-temperature processing steps.

Interface engineering between electrodes and phase change materials has emerged as a key reliability factor. The formation of interfacial compounds can lead to increased contact resistance and accelerated failure mechanisms. Process optimizations involving pre-deposition surface treatments and carefully controlled annealing protocols have shown promise in minimizing these undesirable reactions, extending device endurance by orders of magnitude in laboratory settings.

Dimensional control at nanoscale presents unique challenges for PCM manufacturing. As feature sizes approach sub-20nm dimensions, edge roughness and line width variations become increasingly problematic. Advanced lithography techniques coupled with atomic layer etching processes have demonstrated the ability to achieve the required dimensional precision, reducing geometric variability that would otherwise contribute to fault occurrence.

Post-fabrication treatments, including controlled crystallization annealing and passivation processes, offer additional pathways for reliability enhancement. These treatments can stabilize the microstructure of phase change materials and protect them from environmental factors that might accelerate degradation mechanisms during operation.

The collective implementation of these manufacturing optimizations has demonstrated significant improvements in PCM crossbar array yield and reliability metrics, providing a stronger foundation for implementing higher-level fault tolerance and error correction strategies.

The deposition of phase change materials, typically chalcogenide compounds like Ge2Sb2Te5 (GST), demands precise control over stoichiometry and crystallization conditions. Advanced techniques such as atomic layer deposition (ALD) and pulsed laser deposition (PLD) have demonstrated superior uniformity compared to conventional sputtering methods, reducing cell-to-cell variability by up to 40% in recent studies. This improvement directly translates to more predictable resistance distributions across the crossbar array.

Thermal management during manufacturing represents another critical optimization target. The integration of thermal barrier layers and optimized heater designs can significantly reduce thermal crosstalk between adjacent cells. Recent innovations include the development of carbon-based thermal interface materials that provide excellent thermal isolation while maintaining structural integrity during the high-temperature processing steps.

Interface engineering between electrodes and phase change materials has emerged as a key reliability factor. The formation of interfacial compounds can lead to increased contact resistance and accelerated failure mechanisms. Process optimizations involving pre-deposition surface treatments and carefully controlled annealing protocols have shown promise in minimizing these undesirable reactions, extending device endurance by orders of magnitude in laboratory settings.

Dimensional control at nanoscale presents unique challenges for PCM manufacturing. As feature sizes approach sub-20nm dimensions, edge roughness and line width variations become increasingly problematic. Advanced lithography techniques coupled with atomic layer etching processes have demonstrated the ability to achieve the required dimensional precision, reducing geometric variability that would otherwise contribute to fault occurrence.

Post-fabrication treatments, including controlled crystallization annealing and passivation processes, offer additional pathways for reliability enhancement. These treatments can stabilize the microstructure of phase change materials and protect them from environmental factors that might accelerate degradation mechanisms during operation.

The collective implementation of these manufacturing optimizations has demonstrated significant improvements in PCM crossbar array yield and reliability metrics, providing a stronger foundation for implementing higher-level fault tolerance and error correction strategies.

Scalability and Integration Considerations

As PCM crossbar arrays scale to higher densities, several critical integration challenges emerge that directly impact fault tolerance and error correction strategies. The physical scaling of PCM cells introduces increased variability in resistance states, resulting in narrower sensing margins between programmed states. This phenomenon necessitates more sophisticated error correction codes (ECCs) that can handle higher bit error rates while maintaining acceptable overhead. Current projections indicate that beyond 10nm technology nodes, conventional single-bit error correction may become insufficient, requiring migration to multi-bit correction schemes or more advanced approaches like product codes.

Integration with CMOS periphery circuits presents another significant scalability challenge. As crossbar arrays grow in size, the peripheral circuitry for addressing, sensing, and error correction must scale accordingly without dominating the overall chip area. This has prompted research into in-memory computing architectures where error correction functions are partially distributed within the memory array itself, reducing the burden on peripheral circuits while improving system resilience against localized faults.

Thermal management becomes increasingly critical at higher integration densities. The proximity of PCM cells can lead to thermal crosstalk, where the programming of one cell affects the reliability of neighboring cells. Advanced error correction strategies must account for these spatial correlations in error patterns, potentially employing adaptive coding schemes that adjust protection levels based on cell location and thermal history within the array.

3D integration offers promising pathways to overcome some scalability limitations by stacking multiple crossbar layers. However, this approach introduces new reliability concerns, particularly for cells located at layer interfaces. Specialized fault tolerance techniques for 3D-stacked PCM arrays are emerging, including layer-specific error correction strengths and inter-layer parity schemes that can detect and recover from vertical error propagation.

Power delivery networks for large-scale PCM arrays present another integration challenge affecting reliability. Voltage drops across the array can lead to inconsistent programming conditions, resulting in systematic error patterns. Advanced error correction strategies increasingly incorporate awareness of these physical layout effects, with some implementations featuring dynamic adjustment of error correction parameters based on the physical location within the array and the current state of the power delivery network.

Integration with CMOS periphery circuits presents another significant scalability challenge. As crossbar arrays grow in size, the peripheral circuitry for addressing, sensing, and error correction must scale accordingly without dominating the overall chip area. This has prompted research into in-memory computing architectures where error correction functions are partially distributed within the memory array itself, reducing the burden on peripheral circuits while improving system resilience against localized faults.

Thermal management becomes increasingly critical at higher integration densities. The proximity of PCM cells can lead to thermal crosstalk, where the programming of one cell affects the reliability of neighboring cells. Advanced error correction strategies must account for these spatial correlations in error patterns, potentially employing adaptive coding schemes that adjust protection levels based on cell location and thermal history within the array.

3D integration offers promising pathways to overcome some scalability limitations by stacking multiple crossbar layers. However, this approach introduces new reliability concerns, particularly for cells located at layer interfaces. Specialized fault tolerance techniques for 3D-stacked PCM arrays are emerging, including layer-specific error correction strengths and inter-layer parity schemes that can detect and recover from vertical error propagation.

Power delivery networks for large-scale PCM arrays present another integration challenge affecting reliability. Voltage drops across the array can lead to inconsistent programming conditions, resulting in systematic error patterns. Advanced error correction strategies increasingly incorporate awareness of these physical layout effects, with some implementations featuring dynamic adjustment of error correction parameters based on the physical location within the array and the current state of the power delivery network.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!