The Role of Standards in Resistive RAM System Adoption

OCT 9, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

ReRAM Standards Evolution and Objectives

Resistive RAM (ReRAM) technology has evolved significantly since its conceptualization in the early 1960s, with major developmental milestones occurring in the late 1990s and early 2000s. The technology's evolution has been characterized by incremental improvements in materials science, fabrication techniques, and integration methodologies. Initially, ReRAM faced challenges related to reliability, endurance, and manufacturing consistency, which hindered widespread adoption despite its promising characteristics.

The standardization efforts for ReRAM began to take shape around 2010 when industry stakeholders recognized the need for common frameworks to facilitate technology adoption. Early standards focused primarily on basic performance metrics and testing methodologies, allowing for preliminary comparisons between different ReRAM implementations. These initial standards were largely fragmented, with different organizations proposing varying approaches to ReRAM characterization.

The primary objective of ReRAM standardization is to establish a unified framework that enables interoperability, reliability assessment, and performance benchmarking across different manufacturers and implementations. This includes standardizing key parameters such as switching voltage, read/write speeds, endurance cycles, retention time, and power consumption. Additionally, standards aim to define common interfaces for ReRAM integration with existing memory hierarchies and computing architectures.

Another critical objective is to facilitate the integration of ReRAM into emerging computing paradigms, particularly neuromorphic computing and in-memory computing applications. This requires standards that address not only traditional memory metrics but also specialized characteristics relevant to these novel computing approaches, such as analog precision, state stability, and multi-level cell capabilities.

Industry consortia like JEDEC and IEEE have been instrumental in driving standardization efforts, bringing together manufacturers, researchers, and end-users to develop comprehensive standards. The JEDEC JC-42.4 Subcommittee on Nonvolatile Memory and the IEEE Working Group P1817 have been particularly active in developing ReRAM-specific standards and incorporating ReRAM into broader memory technology frameworks.

The evolution of ReRAM standards is increasingly focusing on application-specific requirements, recognizing that different use cases may demand different performance profiles. For instance, standards for ReRAM in IoT devices emphasize low power consumption and long retention, while those for data center applications prioritize endurance and speed. This targeted approach aims to accelerate adoption across diverse market segments.

Looking forward, standardization objectives are expanding to include reliability models, failure mechanisms, and qualification methodologies specific to ReRAM technology. These efforts are essential for building confidence among system designers and accelerating the transition from research prototypes to commercial products. The ultimate goal is to establish ReRAM as a standardized component in the memory ecosystem, enabling its widespread adoption in next-generation computing systems.

The standardization efforts for ReRAM began to take shape around 2010 when industry stakeholders recognized the need for common frameworks to facilitate technology adoption. Early standards focused primarily on basic performance metrics and testing methodologies, allowing for preliminary comparisons between different ReRAM implementations. These initial standards were largely fragmented, with different organizations proposing varying approaches to ReRAM characterization.

The primary objective of ReRAM standardization is to establish a unified framework that enables interoperability, reliability assessment, and performance benchmarking across different manufacturers and implementations. This includes standardizing key parameters such as switching voltage, read/write speeds, endurance cycles, retention time, and power consumption. Additionally, standards aim to define common interfaces for ReRAM integration with existing memory hierarchies and computing architectures.

Another critical objective is to facilitate the integration of ReRAM into emerging computing paradigms, particularly neuromorphic computing and in-memory computing applications. This requires standards that address not only traditional memory metrics but also specialized characteristics relevant to these novel computing approaches, such as analog precision, state stability, and multi-level cell capabilities.

Industry consortia like JEDEC and IEEE have been instrumental in driving standardization efforts, bringing together manufacturers, researchers, and end-users to develop comprehensive standards. The JEDEC JC-42.4 Subcommittee on Nonvolatile Memory and the IEEE Working Group P1817 have been particularly active in developing ReRAM-specific standards and incorporating ReRAM into broader memory technology frameworks.

The evolution of ReRAM standards is increasingly focusing on application-specific requirements, recognizing that different use cases may demand different performance profiles. For instance, standards for ReRAM in IoT devices emphasize low power consumption and long retention, while those for data center applications prioritize endurance and speed. This targeted approach aims to accelerate adoption across diverse market segments.

Looking forward, standardization objectives are expanding to include reliability models, failure mechanisms, and qualification methodologies specific to ReRAM technology. These efforts are essential for building confidence among system designers and accelerating the transition from research prototypes to commercial products. The ultimate goal is to establish ReRAM as a standardized component in the memory ecosystem, enabling its widespread adoption in next-generation computing systems.

Market Analysis for ReRAM Technology Adoption

The global ReRAM (Resistive Random Access Memory) market is experiencing significant growth, with projections indicating expansion from $1.2 billion in 2023 to approximately $4.6 billion by 2028, representing a compound annual growth rate of 30.8%. This growth is primarily driven by increasing demand for high-performance, low-power memory solutions in data centers, IoT devices, and artificial intelligence applications.

Market segmentation reveals that enterprise storage systems currently constitute the largest application segment, accounting for 42% of ReRAM deployments. The consumer electronics sector follows at 28%, with automotive applications emerging rapidly at 18% and expected to double within the next five years as autonomous driving technologies advance.

Geographically, North America leads ReRAM adoption with 38% market share, followed by Asia-Pacific at 35%, Europe at 22%, and rest of the world at 5%. China and Taiwan are demonstrating particularly aggressive growth rates, investing heavily in domestic ReRAM manufacturing capabilities to reduce dependency on imported memory technologies.

The demand drivers for ReRAM adoption are multifaceted. Power efficiency requirements in mobile and edge computing applications favor ReRAM's low energy consumption profile. Data centers are increasingly exploring ReRAM for storage class memory applications that bridge the performance gap between DRAM and NAND flash. Additionally, ReRAM's radiation hardness makes it particularly attractive for aerospace and military applications.

Market barriers include price-performance competition from established memory technologies like NAND flash and DRAM, which benefit from decades of manufacturing optimization and economies of scale. Technical challenges in scaling ReRAM to higher densities while maintaining reliability also impede broader market penetration.

Industry analysts identify standardization as a critical factor for accelerating market adoption. The lack of unified standards for ReRAM interfaces, testing methodologies, and reliability metrics creates market fragmentation and increases integration costs for system designers. Companies implementing proprietary ReRAM solutions face challenges in ecosystem development and customer acceptance.

Customer surveys indicate that 76% of potential enterprise adopters cite concerns about long-term support and cross-vendor compatibility as major factors delaying ReRAM implementation. This highlights the urgent need for industry-wide standards to facilitate broader market acceptance and technology integration across diverse applications.

Market segmentation reveals that enterprise storage systems currently constitute the largest application segment, accounting for 42% of ReRAM deployments. The consumer electronics sector follows at 28%, with automotive applications emerging rapidly at 18% and expected to double within the next five years as autonomous driving technologies advance.

Geographically, North America leads ReRAM adoption with 38% market share, followed by Asia-Pacific at 35%, Europe at 22%, and rest of the world at 5%. China and Taiwan are demonstrating particularly aggressive growth rates, investing heavily in domestic ReRAM manufacturing capabilities to reduce dependency on imported memory technologies.

The demand drivers for ReRAM adoption are multifaceted. Power efficiency requirements in mobile and edge computing applications favor ReRAM's low energy consumption profile. Data centers are increasingly exploring ReRAM for storage class memory applications that bridge the performance gap between DRAM and NAND flash. Additionally, ReRAM's radiation hardness makes it particularly attractive for aerospace and military applications.

Market barriers include price-performance competition from established memory technologies like NAND flash and DRAM, which benefit from decades of manufacturing optimization and economies of scale. Technical challenges in scaling ReRAM to higher densities while maintaining reliability also impede broader market penetration.

Industry analysts identify standardization as a critical factor for accelerating market adoption. The lack of unified standards for ReRAM interfaces, testing methodologies, and reliability metrics creates market fragmentation and increases integration costs for system designers. Companies implementing proprietary ReRAM solutions face challenges in ecosystem development and customer acceptance.

Customer surveys indicate that 76% of potential enterprise adopters cite concerns about long-term support and cross-vendor compatibility as major factors delaying ReRAM implementation. This highlights the urgent need for industry-wide standards to facilitate broader market acceptance and technology integration across diverse applications.

ReRAM Technical Challenges and Standardization Barriers

Resistive RAM (ReRAM) faces significant technical challenges that impede its widespread adoption in commercial applications. One of the primary obstacles is the lack of standardized fabrication processes across the industry. Different manufacturers employ varying materials, structures, and fabrication techniques, resulting in inconsistent device performance and reliability characteristics. This heterogeneity makes it difficult for system designers to integrate ReRAM components from different suppliers, limiting interoperability and increasing development costs.

The absence of standardized testing methodologies represents another critical barrier. Without uniform testing protocols, performance metrics such as endurance, retention time, and switching speed cannot be reliably compared across different ReRAM technologies. This creates uncertainty for potential adopters and slows market acceptance. Industry stakeholders need consistent benchmarking frameworks to evaluate competing solutions objectively and make informed implementation decisions.

Interface standardization remains underdeveloped for ReRAM systems. While traditional memory technologies benefit from well-established interface standards (such as DDR for DRAM), ReRAM lacks equivalent standardized electrical interfaces and communication protocols. This deficiency complicates system integration and forces developers to create custom interfaces, increasing design complexity and time-to-market while reducing portability across platforms.

Data reliability and error correction standards present ongoing challenges. ReRAM devices exhibit unique failure mechanisms and error patterns that differ from conventional memory technologies. Standard error correction code (ECC) schemes optimized for NAND flash or DRAM may not adequately address ReRAM's specific characteristics. The industry needs standardized reliability models and error correction techniques tailored to ReRAM's operational parameters.

The fragmented intellectual property landscape further complicates standardization efforts. Key ReRAM technologies are protected by patents held by different organizations, creating potential licensing barriers and royalty stacking issues. Without collaborative standardization initiatives, the industry risks market fragmentation and delayed technology adoption as companies pursue proprietary approaches.

Addressing these standardization barriers requires coordinated action from industry consortia, academic institutions, and standards development organizations. Initiatives like JEDEC's emerging memory standardization efforts provide promising frameworks, but broader participation and consensus-building are needed. The establishment of reference designs, compliance testing procedures, and certification programs would accelerate ReRAM adoption by reducing integration risks and ensuring interoperability across the memory ecosystem.

The absence of standardized testing methodologies represents another critical barrier. Without uniform testing protocols, performance metrics such as endurance, retention time, and switching speed cannot be reliably compared across different ReRAM technologies. This creates uncertainty for potential adopters and slows market acceptance. Industry stakeholders need consistent benchmarking frameworks to evaluate competing solutions objectively and make informed implementation decisions.

Interface standardization remains underdeveloped for ReRAM systems. While traditional memory technologies benefit from well-established interface standards (such as DDR for DRAM), ReRAM lacks equivalent standardized electrical interfaces and communication protocols. This deficiency complicates system integration and forces developers to create custom interfaces, increasing design complexity and time-to-market while reducing portability across platforms.

Data reliability and error correction standards present ongoing challenges. ReRAM devices exhibit unique failure mechanisms and error patterns that differ from conventional memory technologies. Standard error correction code (ECC) schemes optimized for NAND flash or DRAM may not adequately address ReRAM's specific characteristics. The industry needs standardized reliability models and error correction techniques tailored to ReRAM's operational parameters.

The fragmented intellectual property landscape further complicates standardization efforts. Key ReRAM technologies are protected by patents held by different organizations, creating potential licensing barriers and royalty stacking issues. Without collaborative standardization initiatives, the industry risks market fragmentation and delayed technology adoption as companies pursue proprietary approaches.

Addressing these standardization barriers requires coordinated action from industry consortia, academic institutions, and standards development organizations. Initiatives like JEDEC's emerging memory standardization efforts provide promising frameworks, but broader participation and consensus-building are needed. The establishment of reference designs, compliance testing procedures, and certification programs would accelerate ReRAM adoption by reducing integration risks and ensuring interoperability across the memory ecosystem.

Current ReRAM Standardization Approaches

01 RRAM device structure standards

Standardized structures for RRAM devices include specific electrode materials, resistive switching layers, and interface designs. These standards define the physical arrangement of components such as top and bottom electrodes, dielectric layers, and barrier layers. The standardized structures ensure consistent performance across different manufacturing processes and enable compatibility between various RRAM technologies.- RRAM Device Structure Standards: Standardized structures for RRAM devices include specific electrode materials, resistive switching layers, and interface designs. These standards define the physical arrangement of components such as top and bottom electrodes, dielectric layers, and filament formation regions. Standardized structures ensure consistent performance across different manufacturing processes and enable compatibility between different RRAM technologies.

- RRAM Operation and Programming Standards: Standards for RRAM operation define the voltage levels, pulse durations, and current limits for programming, reading, and erasing operations. These standards ensure reliable switching between high and low resistance states while maintaining data retention and endurance. Standardized programming protocols help prevent over-programming and reduce variability in device performance across different manufacturing batches.

- RRAM Integration and Fabrication Standards: Fabrication standards for RRAM specify the processes, materials, and dimensions required for manufacturing compatible devices. These standards include specifications for integration with CMOS technology, back-end-of-line processing requirements, and thermal budget constraints. Standardized fabrication methods ensure consistency in device performance and enable high-volume manufacturing of RRAM devices across different foundries.

- RRAM Testing and Characterization Standards: Testing standards for RRAM define the methods for characterizing device performance, reliability, and endurance. These standards specify procedures for measuring switching speed, retention time, resistance ratio, and cycle endurance. Standardized testing protocols enable meaningful comparison between different RRAM technologies and ensure that devices meet minimum performance requirements for commercial applications.

- RRAM Interface and Communication Standards: Interface standards for RRAM define the electrical and logical protocols for communicating with memory arrays. These standards specify signal timing, bus architectures, and command structures for reading, writing, and erasing operations. Standardized interfaces ensure compatibility between RRAM memory and various controllers or processors, enabling seamless integration into existing computing systems and facilitating the development of new memory architectures.

02 RRAM operation and programming standards

Standards for RRAM operation define the voltage levels, pulse durations, and current limits for programming, reading, and erasing operations. These specifications ensure reliable switching between high and low resistance states while maintaining data retention and endurance. The standards also address programming algorithms that optimize the trade-off between speed, power consumption, and reliability.Expand Specific Solutions03 RRAM integration and fabrication standards

Fabrication standards for RRAM specify the processes, materials, and dimensions required for manufacturing compatible devices. These standards cover deposition techniques, etching processes, and thermal treatments necessary for creating reliable resistive switching layers. They also address integration requirements with CMOS technology, including back-end-of-line processing compatibility and 3D integration approaches.Expand Specific Solutions04 RRAM testing and characterization standards

Standards for testing and characterizing RRAM devices include protocols for measuring switching speed, endurance, retention time, and reliability. These standards define test conditions, measurement techniques, and performance metrics that enable consistent evaluation across different technologies. They also specify accelerated testing methodologies for predicting long-term reliability and failure mechanisms.Expand Specific Solutions05 RRAM interface and communication standards

Interface standards for RRAM define the electrical and logical protocols for communicating with memory arrays. These specifications include addressing schemes, command structures, and data formats that ensure interoperability between RRAM devices and controllers. The standards also cover error correction codes, wear-leveling algorithms, and power management techniques optimized for resistive memory characteristics.Expand Specific Solutions

Key Industry Players in ReRAM Standardization

The Resistive RAM (ReRAM) technology market is currently in an early growth phase, characterized by increasing research activities and emerging commercial applications. The global ReRAM market is projected to expand significantly as demand for high-performance, low-power memory solutions grows across IoT, AI, and edge computing sectors. Technologically, major semiconductor players are at different maturity stages: Samsung, Micron, and Intel are leveraging their manufacturing expertise to advance ReRAM integration with existing processes; specialized companies like CrossBar and Weebit Nano are developing proprietary ReRAM architectures; while research institutions such as ITRI and universities collaborate with industry partners to address fundamental challenges. The lack of unified standards remains a critical barrier to widespread adoption, with companies like TSMC, GLOBALFOUNDRIES, and UMC working to establish fabrication protocols that could accelerate commercialization across the semiconductor ecosystem.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has been at the forefront of ReRAM standardization efforts, leveraging its position as a memory industry leader. The company has developed a vertical ReRAM architecture that utilizes a metal-oxide switching layer (typically HfO2 or TaOx) sandwiched between metal electrodes[1]. Samsung's approach to standardization includes developing ReRAM modules that are pin-compatible with existing memory interfaces, allowing system designers to adopt the technology with minimal changes to their designs. The company has been actively participating in JEDEC committees working on next-generation non-volatile memory standards, pushing for ReRAM-specific testing methodologies and reliability specifications[2]. Samsung has demonstrated ReRAM devices with multi-level cell capabilities (storing 2+ bits per cell) and has been working on standardizing the command set and programming algorithms for these advanced cells. Their ReRAM technology targets both standalone memory applications and embedded solutions for IoT and edge computing devices[3].

Strengths: Massive manufacturing infrastructure enabling rapid scaling once standards are established; extensive experience in memory standardization from DRAM and NAND flash; vertical integration allowing for complete memory subsystem optimization. Weaknesses: Internal competition with other memory technologies in Samsung's portfolio (MRAM, PRAM, etc.) may dilute focus on ReRAM standardization; conservative approach to introducing disruptive technologies to market.

Micron Technology, Inc.

Technical Solution: Micron has developed a comprehensive approach to ReRAM standardization focusing on both materials science and system integration. Their ReRAM technology utilizes a proprietary metal oxide switching layer that enables reliable resistive switching with high on/off ratios[1]. Micron's standardization strategy includes developing a unified memory architecture that can accommodate both conventional and emerging non-volatile memories, with standardized controllers that can manage the specific requirements of ReRAM operation. The company has been working on standardizing ReRAM cell characterization methods, particularly focusing on variability analysis and reliability testing protocols that can be adopted industry-wide[2]. Micron has demonstrated 3D cross-point ReRAM arrays that could serve as a foundation for future standardized memory products, with particular emphasis on storage class memory applications that bridge the performance gap between DRAM and NAND flash. Their work includes standardizing wear-leveling algorithms and error correction codes specifically optimized for ReRAM's unique characteristics[3].

Strengths: Deep expertise in memory system architecture allowing for holistic standardization approach; strong relationships with system OEMs facilitating adoption of new standards; extensive IP portfolio in non-volatile memory technologies. Weaknesses: Previous investment in competing technologies (3D XPoint) may complicate ReRAM standardization strategy; challenges in balancing proprietary technology advantages against open standardization needs.

Critical Patents and Technical Literature in ReRAM Standards

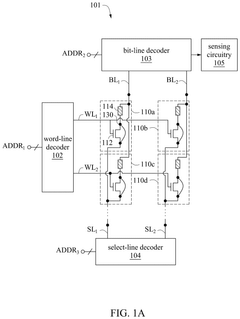

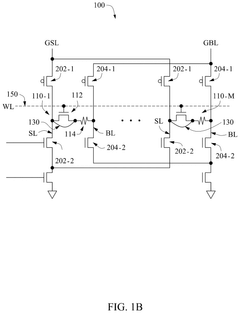

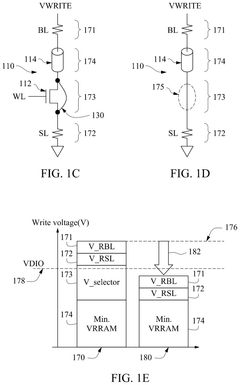

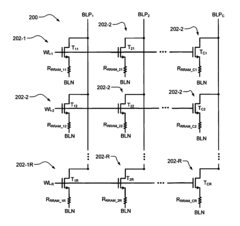

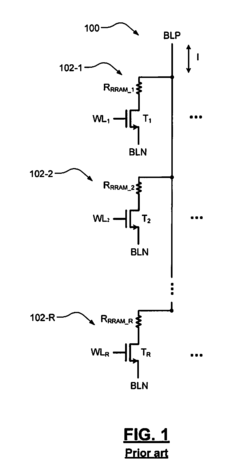

Resistive memory with low voltage operation

PatentActiveUS20240355389A1

Innovation

- Bypassing or removing the selector device or transistor in RRAM memory cells using metal wiring to eliminate IR drop, thereby reducing the minimum voltage required for write operations and eliminating the need for charge pumps and high voltage devices, resulting in a zero-transistor and one-resistor (0T1R) RRAM array.

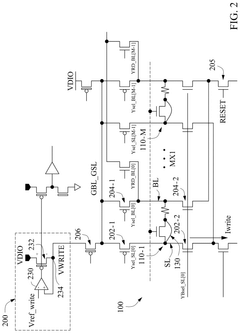

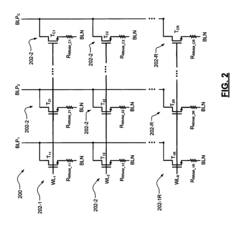

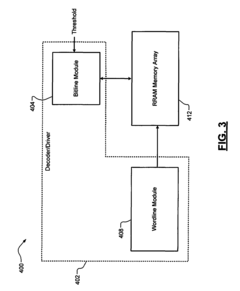

Systems and methods for increasing the read sensitivity of a resistive random access memory (RRAM)

PatentInactiveUS9275731B1

Innovation

- Configuring RRAM memory cells with a common gate configuration and using only one polarity of current flow during read operations to improve sensitivity and reduce read disturbance, while naturally limiting voltage across the cells without additional circuit components.

Interoperability and Compatibility Frameworks

Interoperability and compatibility frameworks represent critical infrastructure for the widespread adoption of Resistive RAM (ReRAM) technology. These frameworks establish standardized protocols and interfaces that enable ReRAM components to function seamlessly across diverse hardware platforms, operating systems, and application environments. The development of such frameworks requires collaborative efforts between industry stakeholders, academic institutions, and standards organizations.

The JEDEC Solid State Technology Association has emerged as a pivotal entity in establishing ReRAM compatibility standards, particularly through its JC-42.4 Subcommittee focused on nonvolatile memory technologies. Their specifications address critical aspects such as electrical interfaces, command sets, and physical form factors, ensuring that ReRAM modules from different manufacturers can operate interchangeably within compliant systems.

Similarly, the IEEE has contributed significantly through working groups dedicated to emerging memory technologies, establishing reference architectures that facilitate integration between ReRAM and conventional memory hierarchies. These standards define communication protocols, timing parameters, and error handling mechanisms essential for reliable operation across heterogeneous computing environments.

Open-source initiatives have also gained traction in the ReRAM ecosystem, with frameworks like OpenMemory providing vendor-neutral APIs that abstract hardware-specific implementations. This approach enables software developers to leverage ReRAM capabilities without being locked into proprietary solutions, thereby accelerating adoption across diverse application domains.

Cross-platform compatibility remains a significant challenge, particularly regarding the integration of ReRAM with established memory technologies such as DRAM and NAND flash. Hybrid memory controllers that can efficiently manage these disparate technologies require standardized interfaces for memory allocation, addressing, and power management. The SNIA Non-Volatile Memory Programming Model offers valuable guidance in this regard, defining consistent abstractions for persistent memory operations.

Security and data integrity frameworks constitute another crucial dimension of ReRAM standardization efforts. The Trusted Computing Group's specifications for secure storage technologies have been extended to address the unique characteristics of ReRAM, including its vulnerability to read disturb effects and potential side-channel attacks. These frameworks establish protocols for secure erase operations, authentication mechanisms, and encryption methodologies tailored to ReRAM's operational parameters.

Looking forward, the evolution of these interoperability frameworks will likely emphasize scalability across computing tiers, from edge devices to data centers, ensuring that ReRAM's benefits can be realized consistently throughout heterogeneous computing environments.

The JEDEC Solid State Technology Association has emerged as a pivotal entity in establishing ReRAM compatibility standards, particularly through its JC-42.4 Subcommittee focused on nonvolatile memory technologies. Their specifications address critical aspects such as electrical interfaces, command sets, and physical form factors, ensuring that ReRAM modules from different manufacturers can operate interchangeably within compliant systems.

Similarly, the IEEE has contributed significantly through working groups dedicated to emerging memory technologies, establishing reference architectures that facilitate integration between ReRAM and conventional memory hierarchies. These standards define communication protocols, timing parameters, and error handling mechanisms essential for reliable operation across heterogeneous computing environments.

Open-source initiatives have also gained traction in the ReRAM ecosystem, with frameworks like OpenMemory providing vendor-neutral APIs that abstract hardware-specific implementations. This approach enables software developers to leverage ReRAM capabilities without being locked into proprietary solutions, thereby accelerating adoption across diverse application domains.

Cross-platform compatibility remains a significant challenge, particularly regarding the integration of ReRAM with established memory technologies such as DRAM and NAND flash. Hybrid memory controllers that can efficiently manage these disparate technologies require standardized interfaces for memory allocation, addressing, and power management. The SNIA Non-Volatile Memory Programming Model offers valuable guidance in this regard, defining consistent abstractions for persistent memory operations.

Security and data integrity frameworks constitute another crucial dimension of ReRAM standardization efforts. The Trusted Computing Group's specifications for secure storage technologies have been extended to address the unique characteristics of ReRAM, including its vulnerability to read disturb effects and potential side-channel attacks. These frameworks establish protocols for secure erase operations, authentication mechanisms, and encryption methodologies tailored to ReRAM's operational parameters.

Looking forward, the evolution of these interoperability frameworks will likely emphasize scalability across computing tiers, from edge devices to data centers, ensuring that ReRAM's benefits can be realized consistently throughout heterogeneous computing environments.

Regulatory Compliance and Certification Pathways

The regulatory landscape for Resistive RAM (ReRAM) technology is complex and evolving, requiring manufacturers and implementers to navigate multiple certification pathways to ensure market acceptance. Currently, ReRAM systems must comply with various international standards bodies including the International Electrotechnical Commission (IEC), JEDEC Solid State Technology Association, and IEEE. These organizations have established baseline requirements for memory technologies, though specific ReRAM standards remain in development stages.

For semiconductor manufacturers, compliance with ISO 9001 quality management systems and ISO 14001 environmental management standards represents the foundation of regulatory adherence. Additionally, product-specific certifications such as UL recognition for component safety and electromagnetic compatibility (EMC) testing under IEC 61000 series are mandatory for market entry in most regions.

The certification process for ReRAM technologies typically follows a multi-phase approach. Initially, manufacturers must conduct internal validation against published specifications and industry benchmarks. This is followed by third-party verification through accredited testing laboratories that assess performance metrics, reliability parameters, and safety characteristics. Final certification often requires submission of comprehensive technical documentation, test reports, and sometimes physical samples to regulatory authorities.

Regional variations in compliance requirements present significant challenges for global deployment of ReRAM systems. The European Union mandates CE marking with adherence to RoHS and REACH directives for hazardous substances. In contrast, the United States relies on FCC certification for electronic devices, while China implements the China Compulsory Certification (CCC) system with its unique testing protocols.

Emerging application areas for ReRAM, particularly in automotive and medical devices, introduce additional regulatory hurdles. Automotive-grade ReRAM must meet AEC-Q100 qualification requirements and ISO 26262 functional safety standards. Medical applications necessitate compliance with IEC 60601 for electrical medical equipment and potentially FDA approval in the US market.

Forward-looking standardization efforts are focusing on establishing ReRAM-specific performance benchmarks, reliability metrics, and interface protocols. Industry consortia like JEDEC JC-42.4 Subcommittee on Nonvolatile Memory and the Storage Networking Industry Association (SNIA) are developing technical specifications that will likely evolve into formal standards. These emerging frameworks will be crucial for market adoption by providing consistency in product evaluation and interoperability assurance across different manufacturers' implementations.

For semiconductor manufacturers, compliance with ISO 9001 quality management systems and ISO 14001 environmental management standards represents the foundation of regulatory adherence. Additionally, product-specific certifications such as UL recognition for component safety and electromagnetic compatibility (EMC) testing under IEC 61000 series are mandatory for market entry in most regions.

The certification process for ReRAM technologies typically follows a multi-phase approach. Initially, manufacturers must conduct internal validation against published specifications and industry benchmarks. This is followed by third-party verification through accredited testing laboratories that assess performance metrics, reliability parameters, and safety characteristics. Final certification often requires submission of comprehensive technical documentation, test reports, and sometimes physical samples to regulatory authorities.

Regional variations in compliance requirements present significant challenges for global deployment of ReRAM systems. The European Union mandates CE marking with adherence to RoHS and REACH directives for hazardous substances. In contrast, the United States relies on FCC certification for electronic devices, while China implements the China Compulsory Certification (CCC) system with its unique testing protocols.

Emerging application areas for ReRAM, particularly in automotive and medical devices, introduce additional regulatory hurdles. Automotive-grade ReRAM must meet AEC-Q100 qualification requirements and ISO 26262 functional safety standards. Medical applications necessitate compliance with IEC 60601 for electrical medical equipment and potentially FDA approval in the US market.

Forward-looking standardization efforts are focusing on establishing ReRAM-specific performance benchmarks, reliability metrics, and interface protocols. Industry consortia like JEDEC JC-42.4 Subcommittee on Nonvolatile Memory and the Storage Networking Industry Association (SNIA) are developing technical specifications that will likely evolve into formal standards. These emerging frameworks will be crucial for market adoption by providing consistency in product evaluation and interoperability assurance across different manufacturers' implementations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!