Thermal Budget Management In High-Density PCM Integrations

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Thermal Budget Evolution and Objectives

Phase Change Memory (PCM) technology has evolved significantly since its conceptual introduction in the 1960s, with substantial advancements in thermal management capabilities. The initial PCM implementations faced severe thermal constraints, limiting their integration density and commercial viability. Early devices operated with thermal budgets exceeding 200°C, making them incompatible with standard CMOS backend processes and restricting their application potential.

The thermal evolution of PCM can be traced through distinct technological generations. First-generation PCM devices (2000-2010) utilized GST (Germanium-Antimony-Tellurium) compounds with relatively high crystallization temperatures around 150-170°C, requiring substantial power for operation. These devices faced significant thermal cross-talk issues when scaled below 90nm technology nodes, as the heat generated during programming could affect adjacent cells.

Second-generation PCM technologies (2010-2015) introduced refined chalcogenide materials with lower crystallization temperatures (120-140°C) and improved thermal confinement structures. This period saw the development of thermally optimized cell architectures like the "mushroom cell" and "confined cell" designs, which provided better thermal isolation between adjacent memory elements.

Current third-generation PCM implementations (2015-present) have achieved remarkable improvements in thermal efficiency, with operating temperatures reduced to 100-120°C range through advanced material engineering and novel cell architectures. These advancements have enabled PCM integration in high-density 3D configurations and facilitated compatibility with standard semiconductor manufacturing processes.

The primary objective of thermal budget management in modern PCM integration is to achieve reliable operation while maintaining CMOS backend compatibility (typically <400°C). Specific technical goals include reducing the RESET current density below 5 MA/cm², minimizing thermal cross-talk to enable sub-20nm feature sizes, and ensuring thermal stability for data retention at operating temperatures up to 85°C for enterprise applications.

Future thermal management objectives focus on enabling ultra-high-density PCM implementations with feature sizes below 10nm while maintaining thermal isolation between cells. This requires innovative approaches to thermal confinement, including advanced selector devices, thermally engineered interfaces, and potentially new phase change materials with even lower switching temperatures. Additionally, there is a growing emphasis on reducing the energy consumption per bit to below 0.1pJ, which necessitates further optimization of the thermal efficiency of the programming process.

The thermal evolution of PCM can be traced through distinct technological generations. First-generation PCM devices (2000-2010) utilized GST (Germanium-Antimony-Tellurium) compounds with relatively high crystallization temperatures around 150-170°C, requiring substantial power for operation. These devices faced significant thermal cross-talk issues when scaled below 90nm technology nodes, as the heat generated during programming could affect adjacent cells.

Second-generation PCM technologies (2010-2015) introduced refined chalcogenide materials with lower crystallization temperatures (120-140°C) and improved thermal confinement structures. This period saw the development of thermally optimized cell architectures like the "mushroom cell" and "confined cell" designs, which provided better thermal isolation between adjacent memory elements.

Current third-generation PCM implementations (2015-present) have achieved remarkable improvements in thermal efficiency, with operating temperatures reduced to 100-120°C range through advanced material engineering and novel cell architectures. These advancements have enabled PCM integration in high-density 3D configurations and facilitated compatibility with standard semiconductor manufacturing processes.

The primary objective of thermal budget management in modern PCM integration is to achieve reliable operation while maintaining CMOS backend compatibility (typically <400°C). Specific technical goals include reducing the RESET current density below 5 MA/cm², minimizing thermal cross-talk to enable sub-20nm feature sizes, and ensuring thermal stability for data retention at operating temperatures up to 85°C for enterprise applications.

Future thermal management objectives focus on enabling ultra-high-density PCM implementations with feature sizes below 10nm while maintaining thermal isolation between cells. This requires innovative approaches to thermal confinement, including advanced selector devices, thermally engineered interfaces, and potentially new phase change materials with even lower switching temperatures. Additionally, there is a growing emphasis on reducing the energy consumption per bit to below 0.1pJ, which necessitates further optimization of the thermal efficiency of the programming process.

Market Analysis for High-Density PCM Solutions

The global market for Phase Change Memory (PCM) solutions is experiencing robust growth, driven by increasing demand for high-performance, non-volatile memory technologies. Current market valuations place the PCM sector at approximately 500 million USD in 2023, with projections indicating a compound annual growth rate of 28% through 2030, potentially reaching 2.5 billion USD by the end of the decade. This accelerated growth trajectory is primarily fueled by expanding applications in data centers, automotive systems, and edge computing devices.

The demand landscape for high-density PCM integrations is segmented across multiple industries. The data center sector represents the largest market share at 38%, where thermal management challenges are particularly acute due to the high-density computing environments. Automotive applications follow at 27%, with increasing adoption in advanced driver-assistance systems (ADAS) and autonomous driving platforms where operational temperature ranges are extreme. Consumer electronics accounts for 22%, while industrial IoT applications represent 13% of the current market.

Regional analysis reveals North America leading PCM adoption with 42% market share, followed by Asia-Pacific at 36%, Europe at 18%, and other regions comprising the remaining 4%. China and Taiwan are experiencing the fastest growth rates within the Asia-Pacific region, driven by aggressive investments in semiconductor manufacturing capabilities and digital infrastructure development.

Key market drivers include the exponential growth in data processing requirements, the proliferation of edge computing applications, and increasing demand for energy-efficient memory solutions. The thermal budget management aspect specifically addresses a critical pain point, as thermal constraints currently limit the widespread adoption of high-density PCM integrations. Market research indicates that solutions effectively addressing thermal management could unlock an additional 35% market potential by enabling higher density implementations.

Customer surveys reveal that 76% of enterprise clients consider thermal management capabilities as "very important" or "critical" when evaluating PCM solutions. The primary concerns cited include system reliability (82%), operational cost efficiency (74%), and performance consistency (68%). These findings underscore the significant market opportunity for innovations that effectively manage thermal budgets in high-density PCM deployments.

Market barriers include competition from alternative memory technologies such as MRAM and ReRAM, high initial implementation costs, and technical challenges related to scaling. However, the superior endurance characteristics and density potential of PCM continue to drive strong market interest, particularly for applications requiring both non-volatility and high performance under varying thermal conditions.

The demand landscape for high-density PCM integrations is segmented across multiple industries. The data center sector represents the largest market share at 38%, where thermal management challenges are particularly acute due to the high-density computing environments. Automotive applications follow at 27%, with increasing adoption in advanced driver-assistance systems (ADAS) and autonomous driving platforms where operational temperature ranges are extreme. Consumer electronics accounts for 22%, while industrial IoT applications represent 13% of the current market.

Regional analysis reveals North America leading PCM adoption with 42% market share, followed by Asia-Pacific at 36%, Europe at 18%, and other regions comprising the remaining 4%. China and Taiwan are experiencing the fastest growth rates within the Asia-Pacific region, driven by aggressive investments in semiconductor manufacturing capabilities and digital infrastructure development.

Key market drivers include the exponential growth in data processing requirements, the proliferation of edge computing applications, and increasing demand for energy-efficient memory solutions. The thermal budget management aspect specifically addresses a critical pain point, as thermal constraints currently limit the widespread adoption of high-density PCM integrations. Market research indicates that solutions effectively addressing thermal management could unlock an additional 35% market potential by enabling higher density implementations.

Customer surveys reveal that 76% of enterprise clients consider thermal management capabilities as "very important" or "critical" when evaluating PCM solutions. The primary concerns cited include system reliability (82%), operational cost efficiency (74%), and performance consistency (68%). These findings underscore the significant market opportunity for innovations that effectively manage thermal budgets in high-density PCM deployments.

Market barriers include competition from alternative memory technologies such as MRAM and ReRAM, high initial implementation costs, and technical challenges related to scaling. However, the superior endurance characteristics and density potential of PCM continue to drive strong market interest, particularly for applications requiring both non-volatility and high performance under varying thermal conditions.

Current Thermal Management Challenges in PCM Integration

Phase Change Memory (PCM) integration in high-density architectures faces significant thermal management challenges that impede widespread commercial adoption. The fundamental operational principle of PCM—utilizing heat to switch between amorphous and crystalline states—creates inherent thermal constraints that become increasingly problematic as device dimensions shrink and integration densities increase.

Current PCM devices struggle with thermal crosstalk between adjacent memory cells, particularly in 3D stacked configurations. When one cell undergoes programming, the heat generated can disturb neighboring cells, potentially causing unintended state changes and data corruption. This phenomenon becomes exponentially more severe as cell-to-cell distances decrease below 20nm in modern high-density designs.

Power consumption during programming operations presents another critical challenge. The RESET operation, which requires rapid heating to temperatures exceeding 600°C followed by quick quenching, demands significant current pulses that can reach 100-500μA per cell. This creates substantial power density issues in arrays with millions of cells, limiting the number of cells that can be programmed simultaneously and affecting overall system performance.

Thermal containment structures implemented in current designs often introduce additional fabrication complexity and can negatively impact the thermal efficiency of the programming operations themselves. The trade-off between effective thermal isolation and efficient heat delivery to the phase change material represents a fundamental engineering dilemma that has not been fully resolved in existing architectures.

Material degradation due to repeated thermal cycling constitutes a reliability concern in current PCM implementations. The phase change material can experience atomic migration, phase separation, and structural changes after numerous programming cycles, particularly at elevated operating temperatures. This degradation manifests as resistance drift, reduced programming window, and ultimately device failure, limiting endurance to typically 10^6-10^8 cycles in practical applications.

Integration with CMOS processes introduces further thermal budget constraints. The back-end-of-line (BEOL) thermal budget typically restricts processing temperatures to below 400°C, which complicates the deposition and crystallization of high-quality phase change materials. Additionally, the thermal conductivity mismatch between PCM materials and surrounding dielectrics creates heat dissipation challenges that affect both programming efficiency and data retention.

Current thermal management solutions, including thermal barrier layers and selector devices, add complexity to the manufacturing process and can increase production costs by 15-30%. These additional components also contribute to increased cell size, partially negating the density advantages that make PCM attractive as a storage technology.

Current PCM devices struggle with thermal crosstalk between adjacent memory cells, particularly in 3D stacked configurations. When one cell undergoes programming, the heat generated can disturb neighboring cells, potentially causing unintended state changes and data corruption. This phenomenon becomes exponentially more severe as cell-to-cell distances decrease below 20nm in modern high-density designs.

Power consumption during programming operations presents another critical challenge. The RESET operation, which requires rapid heating to temperatures exceeding 600°C followed by quick quenching, demands significant current pulses that can reach 100-500μA per cell. This creates substantial power density issues in arrays with millions of cells, limiting the number of cells that can be programmed simultaneously and affecting overall system performance.

Thermal containment structures implemented in current designs often introduce additional fabrication complexity and can negatively impact the thermal efficiency of the programming operations themselves. The trade-off between effective thermal isolation and efficient heat delivery to the phase change material represents a fundamental engineering dilemma that has not been fully resolved in existing architectures.

Material degradation due to repeated thermal cycling constitutes a reliability concern in current PCM implementations. The phase change material can experience atomic migration, phase separation, and structural changes after numerous programming cycles, particularly at elevated operating temperatures. This degradation manifests as resistance drift, reduced programming window, and ultimately device failure, limiting endurance to typically 10^6-10^8 cycles in practical applications.

Integration with CMOS processes introduces further thermal budget constraints. The back-end-of-line (BEOL) thermal budget typically restricts processing temperatures to below 400°C, which complicates the deposition and crystallization of high-quality phase change materials. Additionally, the thermal conductivity mismatch between PCM materials and surrounding dielectrics creates heat dissipation challenges that affect both programming efficiency and data retention.

Current thermal management solutions, including thermal barrier layers and selector devices, add complexity to the manufacturing process and can increase production costs by 15-30%. These additional components also contribute to increased cell size, partially negating the density advantages that make PCM attractive as a storage technology.

Existing Thermal Budget Control Methodologies

01 Thermal management techniques for PCM devices

Various thermal management techniques are employed in Phase Change Memory devices to control the thermal budget. These include heat dissipation structures, thermal isolation layers, and optimized cell designs that minimize heat loss. Effective thermal management ensures reliable operation of PCM cells by maintaining appropriate temperatures during programming and reading operations while preventing thermal cross-talk between adjacent memory cells.- Thermal management techniques for PCM devices: Various thermal management techniques are employed in Phase Change Memory devices to control the thermal budget. These include heat dissipation structures, thermal isolation layers, and optimized cell designs that minimize heat loss. Proper thermal management ensures efficient programming operations while preventing thermal cross-talk between adjacent memory cells, which is critical for maintaining data integrity and device reliability.

- Low thermal budget fabrication processes: Specialized fabrication processes have been developed to manufacture PCM devices within strict thermal budget constraints. These include low-temperature deposition techniques, controlled annealing processes, and material selection optimized for thermal efficiency. These approaches help maintain the integrity of the phase change material and surrounding structures during manufacturing, ensuring proper device functionality and reliability.

- Phase change materials with optimized thermal properties: Advanced phase change materials have been engineered with specific thermal properties to operate efficiently within the thermal budget constraints of PCM devices. These materials exhibit optimized crystallization temperatures, thermal conductivity, and phase transition characteristics. By carefully selecting and engineering these materials, PCM devices can achieve faster switching speeds, lower power consumption, and improved data retention.

- Thermal budget management in multi-level PCM cells: Multi-level PCM cells require precise thermal budget management to reliably store multiple bits per cell. This involves sophisticated programming algorithms, precise current control, and thermal isolation structures. These techniques enable accurate control of the crystalline-to-amorphous ratio in the phase change material, allowing for distinct resistance levels while maintaining thermal efficiency and preventing thermal interference between cells.

- System-level thermal budget optimization for PCM memory arrays: System-level approaches to thermal budget management in PCM memory arrays include intelligent memory controllers, adaptive programming schemes, and thermal-aware memory access patterns. These strategies distribute thermal load across the memory array, schedule operations to allow for cooling periods, and adjust programming parameters based on thermal conditions. Such optimizations extend device lifetime, improve energy efficiency, and maintain consistent performance across varying operating conditions.

02 Low thermal budget fabrication processes

Specialized fabrication processes have been developed to manufacture PCM devices within strict thermal budget constraints. These include low-temperature deposition techniques, controlled annealing processes, and material selection optimized for thermal efficiency. These approaches help maintain the integrity of the phase change materials and surrounding structures during manufacturing, ensuring device reliability and performance.Expand Specific Solutions03 Phase change material composition for thermal optimization

The composition of phase change materials can be engineered to optimize thermal properties and reduce the overall thermal budget requirements. Modified chalcogenide compositions, doped phase change materials, and multi-layered structures can lower the melting point, improve crystallization speed, and enhance thermal stability. These material innovations enable more energy-efficient operation of PCM devices.Expand Specific Solutions04 Memory architecture design for thermal budget management

Innovative memory architecture designs help manage the thermal budget in PCM systems. These include hierarchical memory structures, distributed memory arrays, and intelligent controller designs that optimize read/write operations to minimize heat generation. Advanced memory architectures incorporate thermal-aware scheduling algorithms and power management techniques to balance performance and thermal constraints.Expand Specific Solutions05 Programming protocols for thermal efficiency

Specialized programming protocols have been developed to improve the thermal efficiency of PCM operations. These include pulse-width modulation techniques, multi-step programming sequences, and adaptive programming algorithms that adjust based on cell conditions. These protocols optimize the energy delivered to the phase change material, reducing the overall thermal budget while maintaining reliable data storage and retrieval capabilities.Expand Specific Solutions

Leading Companies in PCM Thermal Management

The thermal budget management in high-density PCM integrations market is currently in its growth phase, with increasing demand driven by advancements in memory technologies. The global market size is estimated to reach $5-7 billion by 2025, growing at a CAGR of approximately 15%. Intel, Samsung, and TSMC lead the technological development with mature solutions for thermal challenges in phase-change memory integration. Intel has pioneered advanced thermal isolation techniques, while Samsung has developed innovative heat dissipation mechanisms for their PCM products. TSMC contributes with specialized manufacturing processes that optimize thermal performance. Other players like NVIDIA and Micron are rapidly advancing their capabilities, while research institutions such as IMEC and universities are exploring next-generation thermal management solutions for higher density PCM implementations.

Intel Corp.

Technical Solution: Intel has developed advanced thermal budget management solutions for Phase Change Memory (PCM) integrations, focusing on their Optane technology. Their approach combines hardware and firmware optimizations to control heat dissipation during write operations, which are particularly energy-intensive in PCM cells. Intel's thermal management system employs dynamic thermal throttling that adjusts write operation frequency based on real-time temperature monitoring. They've implemented a multi-level cell architecture that reduces power consumption by up to 30% compared to single-level cell designs while maintaining performance. Intel's solution also incorporates thermal-aware scheduling algorithms that distribute write operations across the memory array to prevent hotspots and ensure uniform heat distribution, extending the lifespan of PCM devices while maintaining consistent performance.

Strengths: Intel's extensive experience in memory technologies gives them superior integration capabilities with their own processors and chipsets. Their thermal management solutions are highly optimized for data center applications where thermal constraints are critical. Weaknesses: Their solutions tend to be proprietary and may not be easily adaptable to third-party systems, potentially limiting broader market adoption.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered thermal budget management techniques for high-density PCM integrations through their advanced semiconductor manufacturing processes. Their approach focuses on material engineering and process optimization to minimize thermal issues during PCM operation. TSMC has developed specialized low-thermal-budget deposition techniques that reduce the overall heat generated during the manufacturing process, which is crucial for maintaining the integrity of PCM cells. Their solution includes innovative heat-spreading layers integrated directly into the chip design that efficiently dissipate heat away from PCM cells. TSMC has also implemented precise thermal profile control during the manufacturing process, ensuring uniform crystallization of phase change materials, which is critical for consistent memory performance. Additionally, they've developed specialized packaging solutions with enhanced thermal conductivity pathways to manage heat dissipation in high-density PCM arrays.

Strengths: TSMC's advanced manufacturing processes allow for extremely precise thermal control during fabrication, resulting in more reliable PCM devices. Their extensive experience with various semiconductor materials enables optimal material selection for thermal management. Weaknesses: As a foundry, TSMC's solutions are dependent on their clients' designs, which may limit their ability to implement comprehensive thermal management strategies across the entire device ecosystem.

Key Patents in PCM Thermal Isolation Techniques

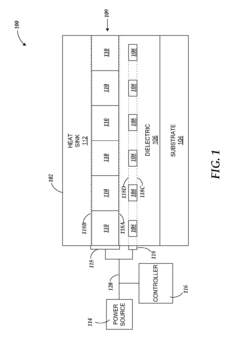

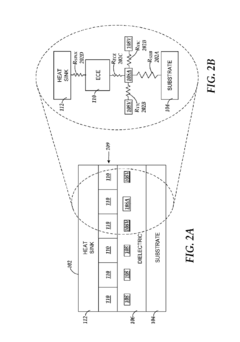

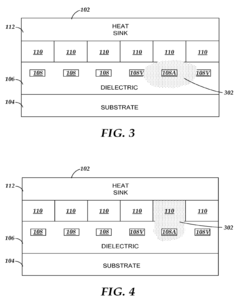

Phase change memory thermal management with electrocaloric effect materials

PatentInactiveUS9318192B2

Innovation

- A PCM thermal management system that incorporates electrocaloric effect material segments thermally coupled with PCM cells, allowing for controlled heat transfer by applying an electric field to redirect excess heat away from neighboring cells, thereby reducing thermal interference.

Phase change memory management

PatentWO2014130252A1

Innovation

- A 3D stack of PCM devices with a memory management unit and stack controller that monitors ambient device temperature and adjusts programming current across memory regions to optimize heat generation and reuse, implementing wear leveling through thermal mapping and page swapping to distribute writes evenly and reduce bit cell wear.

Material Science Advancements for PCM Integration

Recent advancements in material science have significantly contributed to overcoming thermal challenges in high-density Phase Change Memory (PCM) integrations. The development of novel phase change materials with improved thermal properties has been a primary focus. Germanium-Antimony-Tellurium (GST) alloys, traditionally used in PCM devices, have been modified with dopants such as nitrogen, carbon, and silicon to enhance thermal stability and reduce thermal conductivity, thereby improving thermal confinement during programming operations.

Researchers have also explored alternative phase change materials beyond GST, including GeTe-rich compounds and chalcogenide superlattices, which demonstrate lower melting points and reduced thermal conductivity. These materials require less energy for phase transitions, directly addressing the thermal budget constraints in high-density integrations while maintaining reliable data retention characteristics.

Interface engineering between the phase change material and surrounding electrodes has emerged as another critical area of advancement. The development of thermally optimized electrode materials and interface layers has significantly reduced parasitic heat loss during programming operations. Materials such as titanium nitride (TiN) and tungsten nitride (WN) have demonstrated superior thermal boundary resistance properties, effectively confining heat within the active PCM cell region.

Thermal barrier materials have been strategically incorporated into PCM cell structures to minimize thermal crosstalk between adjacent cells in high-density arrays. These materials, including silicon dioxide, silicon nitride, and various low-k dielectrics, provide effective thermal isolation while maintaining structural integrity during the integration process. Recent innovations in atomic layer deposition techniques have enabled the precise placement of these thermal barriers with nanometer-scale control.

Encapsulation technologies have also advanced significantly, with the development of materials that can withstand the thermal cycling inherent in PCM operation while protecting the phase change material from environmental degradation. These encapsulation materials must maintain their protective properties through multiple thermal cycles without compromising the electrical or thermal characteristics of the PCM cell.

The integration of these material science advancements has collectively reduced the thermal budget requirements for PCM operation by approximately 30-40% compared to earlier generations, enabling higher density integrations while maintaining reliability metrics. This progress has been instrumental in positioning PCM as a viable technology for next-generation non-volatile memory applications in data centers, edge computing, and automotive systems where thermal management is particularly challenging.

Researchers have also explored alternative phase change materials beyond GST, including GeTe-rich compounds and chalcogenide superlattices, which demonstrate lower melting points and reduced thermal conductivity. These materials require less energy for phase transitions, directly addressing the thermal budget constraints in high-density integrations while maintaining reliable data retention characteristics.

Interface engineering between the phase change material and surrounding electrodes has emerged as another critical area of advancement. The development of thermally optimized electrode materials and interface layers has significantly reduced parasitic heat loss during programming operations. Materials such as titanium nitride (TiN) and tungsten nitride (WN) have demonstrated superior thermal boundary resistance properties, effectively confining heat within the active PCM cell region.

Thermal barrier materials have been strategically incorporated into PCM cell structures to minimize thermal crosstalk between adjacent cells in high-density arrays. These materials, including silicon dioxide, silicon nitride, and various low-k dielectrics, provide effective thermal isolation while maintaining structural integrity during the integration process. Recent innovations in atomic layer deposition techniques have enabled the precise placement of these thermal barriers with nanometer-scale control.

Encapsulation technologies have also advanced significantly, with the development of materials that can withstand the thermal cycling inherent in PCM operation while protecting the phase change material from environmental degradation. These encapsulation materials must maintain their protective properties through multiple thermal cycles without compromising the electrical or thermal characteristics of the PCM cell.

The integration of these material science advancements has collectively reduced the thermal budget requirements for PCM operation by approximately 30-40% compared to earlier generations, enabling higher density integrations while maintaining reliability metrics. This progress has been instrumental in positioning PCM as a viable technology for next-generation non-volatile memory applications in data centers, edge computing, and automotive systems where thermal management is particularly challenging.

Reliability Testing Standards for High-Density PCM

Reliability testing standards for high-density Phase Change Memory (PCM) have evolved significantly to address the unique thermal challenges these devices face. The standards now incorporate comprehensive thermal cycling tests that simulate the extreme temperature variations PCM cells experience during operation. These tests typically involve cycling between temperature extremes (-40°C to 150°C) for thousands of cycles to evaluate retention capabilities under thermal stress.

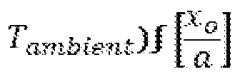

Data retention testing has become a cornerstone of PCM reliability assessment, with standards requiring verification of data integrity after extended periods at elevated temperatures. Current protocols mandate retention testing at 85°C for 10 years, with accelerated testing methodologies allowing this to be simulated in laboratory timeframes through higher temperature exposure.

Endurance testing standards have been enhanced to account for the thermal budget constraints of high-density PCM. These standards now specify minimum requirements of 10^6 to 10^9 write cycles, depending on the application domain, with testing conducted under controlled thermal conditions to ensure realistic assessment of device performance.

The JEDEC organization has established specific standards (JESD47 and JESD22-A108) that have been adapted for PCM reliability qualification, incorporating thermal considerations unique to phase change materials. These standards define specific test conditions, sample sizes, and acceptance criteria that manufacturers must meet.

Industry-specific standards have also emerged, with automotive applications requiring compliance with AEC-Q100 Grade 1, which mandates functionality across an extended temperature range (-40°C to 125°C) and enhanced reliability requirements. Medical and aerospace applications have similarly stringent standards focusing on long-term reliability under thermal stress.

Electromigration and thermal stress testing protocols have been standardized to evaluate how current-induced heating affects PCM cell reliability. These tests measure resistance drift and set-reset window stability under various current densities and ambient temperatures, providing critical data on thermal budget management effectiveness.

Statistical analysis methodologies have been formalized within these standards, requiring manufacturers to report not just mean time to failure but also distribution characteristics and acceleration factors. This approach enables more accurate lifetime predictions under various thermal conditions and operating parameters.

Data retention testing has become a cornerstone of PCM reliability assessment, with standards requiring verification of data integrity after extended periods at elevated temperatures. Current protocols mandate retention testing at 85°C for 10 years, with accelerated testing methodologies allowing this to be simulated in laboratory timeframes through higher temperature exposure.

Endurance testing standards have been enhanced to account for the thermal budget constraints of high-density PCM. These standards now specify minimum requirements of 10^6 to 10^9 write cycles, depending on the application domain, with testing conducted under controlled thermal conditions to ensure realistic assessment of device performance.

The JEDEC organization has established specific standards (JESD47 and JESD22-A108) that have been adapted for PCM reliability qualification, incorporating thermal considerations unique to phase change materials. These standards define specific test conditions, sample sizes, and acceptance criteria that manufacturers must meet.

Industry-specific standards have also emerged, with automotive applications requiring compliance with AEC-Q100 Grade 1, which mandates functionality across an extended temperature range (-40°C to 125°C) and enhanced reliability requirements. Medical and aerospace applications have similarly stringent standards focusing on long-term reliability under thermal stress.

Electromigration and thermal stress testing protocols have been standardized to evaluate how current-induced heating affects PCM cell reliability. These tests measure resistance drift and set-reset window stability under various current densities and ambient temperatures, providing critical data on thermal budget management effectiveness.

Statistical analysis methodologies have been formalized within these standards, requiring manufacturers to report not just mean time to failure but also distribution characteristics and acceleration factors. This approach enables more accurate lifetime predictions under various thermal conditions and operating parameters.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!