Advances In Wafer Manufacturing For SiC MOSFET Devices

SEP 5, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SiC MOSFET Wafer Evolution and Objectives

Silicon carbide (SiC) has emerged as a revolutionary material in power electronics, offering superior properties compared to traditional silicon. The evolution of SiC wafer manufacturing technology represents a critical enabler for high-performance MOSFET devices that can operate at higher voltages, temperatures, and switching frequencies while maintaining excellent efficiency.

The journey of SiC wafer development began in the early 1990s with small-diameter wafers plagued by high defect densities. Initial 2-inch wafers suffered from micropipes, dislocations, and polytype inclusions that severely limited device performance and yield. By the early 2000s, improvements in physical vapor transport (PVT) growth techniques enabled the production of 3-inch wafers with reduced defect densities, marking the first significant milestone in commercial viability.

The period from 2010 to 2015 witnessed the transition to 4-inch (100mm) wafers, accompanied by substantial improvements in crystal quality. This era saw micropipe densities decrease from hundreds per square centimeter to nearly zero, while other defects such as basal plane dislocations were significantly reduced. These advancements enabled the first generation of commercially successful SiC power devices.

Recent years have seen the industry standard progress to 6-inch (150mm) wafers, with leading manufacturers now transitioning to 8-inch (200mm) platforms. This scaling has been crucial for cost reduction, as larger wafers allow more devices per manufacturing cycle while leveraging existing silicon processing infrastructure. The cost per square millimeter of SiC wafer has decreased by approximately 40% with each diameter increase.

The primary technical objective in SiC wafer manufacturing is achieving zero-defect, large-diameter wafers at competitive costs. Current efforts focus on eliminating basal plane dislocations and stacking faults that cause forward voltage drift in SiC MOSFETs. Additionally, reducing surface roughness below 1nm RMS is critical for improving channel mobility and oxide reliability.

Looking forward, the industry aims to establish 8-inch wafer production as the new standard by 2025, with exploratory work on 12-inch wafers already underway. Parallel objectives include reducing wafer bow and warp to below 10μm, enhancing crystal purity to reduce deep-level traps, and developing advanced epitaxial growth techniques for precisely controlled doping profiles.

The ultimate goal is to achieve manufacturing maturity comparable to silicon, enabling SiC MOSFETs to reach price parity with silicon IGBTs on a performance-adjusted basis. This would catalyze widespread adoption across electric vehicles, renewable energy systems, and industrial applications, fundamentally transforming power electronics and accelerating the global transition to more efficient energy systems.

The journey of SiC wafer development began in the early 1990s with small-diameter wafers plagued by high defect densities. Initial 2-inch wafers suffered from micropipes, dislocations, and polytype inclusions that severely limited device performance and yield. By the early 2000s, improvements in physical vapor transport (PVT) growth techniques enabled the production of 3-inch wafers with reduced defect densities, marking the first significant milestone in commercial viability.

The period from 2010 to 2015 witnessed the transition to 4-inch (100mm) wafers, accompanied by substantial improvements in crystal quality. This era saw micropipe densities decrease from hundreds per square centimeter to nearly zero, while other defects such as basal plane dislocations were significantly reduced. These advancements enabled the first generation of commercially successful SiC power devices.

Recent years have seen the industry standard progress to 6-inch (150mm) wafers, with leading manufacturers now transitioning to 8-inch (200mm) platforms. This scaling has been crucial for cost reduction, as larger wafers allow more devices per manufacturing cycle while leveraging existing silicon processing infrastructure. The cost per square millimeter of SiC wafer has decreased by approximately 40% with each diameter increase.

The primary technical objective in SiC wafer manufacturing is achieving zero-defect, large-diameter wafers at competitive costs. Current efforts focus on eliminating basal plane dislocations and stacking faults that cause forward voltage drift in SiC MOSFETs. Additionally, reducing surface roughness below 1nm RMS is critical for improving channel mobility and oxide reliability.

Looking forward, the industry aims to establish 8-inch wafer production as the new standard by 2025, with exploratory work on 12-inch wafers already underway. Parallel objectives include reducing wafer bow and warp to below 10μm, enhancing crystal purity to reduce deep-level traps, and developing advanced epitaxial growth techniques for precisely controlled doping profiles.

The ultimate goal is to achieve manufacturing maturity comparable to silicon, enabling SiC MOSFETs to reach price parity with silicon IGBTs on a performance-adjusted basis. This would catalyze widespread adoption across electric vehicles, renewable energy systems, and industrial applications, fundamentally transforming power electronics and accelerating the global transition to more efficient energy systems.

Market Demand Analysis for SiC Power Devices

The Silicon Carbide (SiC) power device market is experiencing unprecedented growth, driven primarily by the global shift towards electrification and energy efficiency. Current market valuations place the SiC power device sector at approximately $1.1 billion in 2023, with projections indicating a compound annual growth rate (CAGR) of 34% through 2028, potentially reaching $4.5 billion by the end of this forecast period.

Electric vehicles (EVs) represent the most significant demand driver, accounting for nearly 60% of the total SiC power device market. The automotive sector's adoption is accelerating as manufacturers seek to extend vehicle range, reduce charging times, and improve overall efficiency. Tesla's pioneering use of SiC MOSFETs in their Model 3 inverters established a precedent that other major automotive manufacturers are now following, including Volkswagen, BYD, and General Motors.

Industrial applications constitute the second-largest market segment at 22%, with particular growth in motor drives, uninterruptible power supplies, and industrial automation systems. The renewable energy sector, especially solar inverters and wind power systems, represents 15% of current demand but is expected to grow at a faster rate than the overall market due to global renewable energy initiatives.

Regional analysis reveals that Asia-Pacific currently dominates with 45% market share, led by China's aggressive push in both EV production and renewable energy deployment. North America follows at 30%, while Europe accounts for 20% of the global market with particularly strong growth in automotive applications.

The demand-supply gap remains a critical market challenge. Current SiC wafer manufacturing capacity struggles to meet rapidly increasing demand, resulting in extended lead times of 20-30 weeks for some device categories. This supply constraint is driving substantial investments in manufacturing capacity expansion, with major players announcing multi-billion dollar facility investments over the next five years.

Price sensitivity varies significantly by application segment. While consumer electronics remain highly price-sensitive, automotive and industrial applications demonstrate greater willingness to absorb premium pricing for performance advantages. Current SiC MOSFET pricing carries a 2.5-3x premium over silicon alternatives, though this gap is narrowing as manufacturing scales improve.

Market forecasts indicate that the transition from 150mm to 200mm wafers will be a crucial inflection point, potentially reducing device costs by 25-30% when fully implemented at scale. This cost reduction is expected to accelerate adoption in price-sensitive segments and expand the total addressable market significantly beyond current projections.

Electric vehicles (EVs) represent the most significant demand driver, accounting for nearly 60% of the total SiC power device market. The automotive sector's adoption is accelerating as manufacturers seek to extend vehicle range, reduce charging times, and improve overall efficiency. Tesla's pioneering use of SiC MOSFETs in their Model 3 inverters established a precedent that other major automotive manufacturers are now following, including Volkswagen, BYD, and General Motors.

Industrial applications constitute the second-largest market segment at 22%, with particular growth in motor drives, uninterruptible power supplies, and industrial automation systems. The renewable energy sector, especially solar inverters and wind power systems, represents 15% of current demand but is expected to grow at a faster rate than the overall market due to global renewable energy initiatives.

Regional analysis reveals that Asia-Pacific currently dominates with 45% market share, led by China's aggressive push in both EV production and renewable energy deployment. North America follows at 30%, while Europe accounts for 20% of the global market with particularly strong growth in automotive applications.

The demand-supply gap remains a critical market challenge. Current SiC wafer manufacturing capacity struggles to meet rapidly increasing demand, resulting in extended lead times of 20-30 weeks for some device categories. This supply constraint is driving substantial investments in manufacturing capacity expansion, with major players announcing multi-billion dollar facility investments over the next five years.

Price sensitivity varies significantly by application segment. While consumer electronics remain highly price-sensitive, automotive and industrial applications demonstrate greater willingness to absorb premium pricing for performance advantages. Current SiC MOSFET pricing carries a 2.5-3x premium over silicon alternatives, though this gap is narrowing as manufacturing scales improve.

Market forecasts indicate that the transition from 150mm to 200mm wafers will be a crucial inflection point, potentially reducing device costs by 25-30% when fully implemented at scale. This cost reduction is expected to accelerate adoption in price-sensitive segments and expand the total addressable market significantly beyond current projections.

Current SiC Wafer Manufacturing Challenges

Despite significant advancements in Silicon Carbide (SiC) technology, the manufacturing of high-quality SiC wafers continues to face substantial challenges that impede widespread adoption. The primary obstacle remains the high defect density in SiC crystals, particularly micropipes, dislocations, and basal plane defects, which significantly impact device performance and reliability. These defects originate during crystal growth and can propagate through subsequent processing steps, ultimately reducing yield rates and increasing production costs.

The physical growth of SiC crystals presents unique difficulties due to the extremely high temperatures required (over 2000°C) and the need for precise control of thermal gradients. Unlike silicon wafer production, which benefits from decades of process optimization, SiC crystal growth still struggles with issues of uniformity and scalability. Current manufacturing methods predominantly rely on physical vapor transport (PVT), which faces limitations in achieving consistent quality across larger diameter wafers.

Wafer size remains a critical constraint in SiC manufacturing. While silicon technology has progressed to 300mm wafers, commercial SiC wafers are primarily limited to 150mm (6-inch) diameter, with 200mm (8-inch) wafers still in early development stages. This size limitation restricts economies of scale and integration with existing semiconductor manufacturing infrastructure, which is increasingly optimized for larger wafer sizes.

Surface preparation and polishing of SiC wafers present additional challenges due to the material's extreme hardness (9.5 on the Mohs scale). Conventional polishing techniques used for silicon are inadequate, necessitating specialized chemical-mechanical polishing (CMP) processes that are time-consuming and expensive. The resulting surface quality directly impacts epitaxial growth quality and subsequent device performance.

Epitaxial growth on SiC substrates faces its own set of challenges, including maintaining uniform thickness, controlling doping profiles, and minimizing defect propagation from the substrate. The high temperatures required for epitaxial growth (typically 1500-1700°C) demand specialized equipment and precise process control to achieve the desired material properties.

Cost remains perhaps the most significant barrier to widespread adoption. SiC wafers typically cost 5-10 times more than silicon wafers of comparable size, primarily due to complex manufacturing processes, lower yields, and smaller production volumes. This cost differential significantly impacts the economic viability of SiC-based devices, particularly in price-sensitive applications.

Material purity and consistency represent ongoing challenges, with variations in dopant concentration, crystal quality, and surface properties affecting device performance. Establishing robust quality control metrics and standardization across the industry remains a work in progress, complicating supply chain management for device manufacturers.

The physical growth of SiC crystals presents unique difficulties due to the extremely high temperatures required (over 2000°C) and the need for precise control of thermal gradients. Unlike silicon wafer production, which benefits from decades of process optimization, SiC crystal growth still struggles with issues of uniformity and scalability. Current manufacturing methods predominantly rely on physical vapor transport (PVT), which faces limitations in achieving consistent quality across larger diameter wafers.

Wafer size remains a critical constraint in SiC manufacturing. While silicon technology has progressed to 300mm wafers, commercial SiC wafers are primarily limited to 150mm (6-inch) diameter, with 200mm (8-inch) wafers still in early development stages. This size limitation restricts economies of scale and integration with existing semiconductor manufacturing infrastructure, which is increasingly optimized for larger wafer sizes.

Surface preparation and polishing of SiC wafers present additional challenges due to the material's extreme hardness (9.5 on the Mohs scale). Conventional polishing techniques used for silicon are inadequate, necessitating specialized chemical-mechanical polishing (CMP) processes that are time-consuming and expensive. The resulting surface quality directly impacts epitaxial growth quality and subsequent device performance.

Epitaxial growth on SiC substrates faces its own set of challenges, including maintaining uniform thickness, controlling doping profiles, and minimizing defect propagation from the substrate. The high temperatures required for epitaxial growth (typically 1500-1700°C) demand specialized equipment and precise process control to achieve the desired material properties.

Cost remains perhaps the most significant barrier to widespread adoption. SiC wafers typically cost 5-10 times more than silicon wafers of comparable size, primarily due to complex manufacturing processes, lower yields, and smaller production volumes. This cost differential significantly impacts the economic viability of SiC-based devices, particularly in price-sensitive applications.

Material purity and consistency represent ongoing challenges, with variations in dopant concentration, crystal quality, and surface properties affecting device performance. Establishing robust quality control metrics and standardization across the industry remains a work in progress, complicating supply chain management for device manufacturers.

Current SiC Wafer Production Methodologies

01 Epitaxial growth techniques for SiC wafers

Advanced epitaxial growth methods have been developed to improve the quality of SiC wafers for MOSFET manufacturing. These techniques focus on controlling crystal orientation, reducing defects, and ensuring uniform growth across the wafer surface. Improved epitaxial processes lead to better carrier mobility and reduced interface traps in the final devices, which are critical for high-performance SiC MOSFETs.- SiC Wafer Processing Techniques: Advanced processing techniques for silicon carbide wafers have been developed to improve the quality and performance of SiC MOSFETs. These techniques include specialized etching methods, surface preparation processes, and defect reduction strategies that enhance the crystalline quality of the wafer. Improved wafer processing leads to better device characteristics, higher yield rates, and more consistent performance in the final MOSFET devices.

- Gate Oxide Formation and Interface Optimization: Innovations in gate oxide formation for SiC MOSFETs focus on reducing interface trap density and improving channel mobility. Advanced techniques include specialized thermal oxidation processes, nitridation treatments, and post-oxidation annealing steps. These manufacturing advances result in enhanced gate oxide reliability, reduced threshold voltage instability, and improved channel carrier mobility, which are critical for high-performance SiC power devices.

- Epitaxial Growth Advancements: Significant manufacturing advances have been made in epitaxial growth techniques for SiC MOSFET wafers. These include improved chemical vapor deposition methods, controlled doping profiles, and reduced defect density in epitaxial layers. Enhanced epitaxial growth processes enable better control of layer thickness, doping concentration, and uniformity across the wafer, resulting in improved device performance and reliability.

- Implantation and Activation Processes: Advanced ion implantation and post-implantation activation techniques have been developed for SiC MOSFET manufacturing. These processes include precise control of implantation energy and dose, high-temperature annealing methods, and specialized activation sequences. These manufacturing advances enable better control of doping profiles, reduced implantation damage, and improved electrical characteristics in the finished devices.

- Metallization and Contact Formation: Innovations in metallization and contact formation for SiC MOSFETs include advanced metal deposition techniques, optimized annealing processes, and novel contact structures. These manufacturing advances focus on reducing contact resistance, improving adhesion, and enhancing thermal stability of metal contacts. Improved metallization processes result in better current handling capability, reduced power losses, and enhanced reliability of SiC MOSFET devices.

02 Channel and gate oxide formation innovations

Recent manufacturing advances focus on improving the channel region and gate oxide interface in SiC MOSFETs. These innovations include novel oxidation processes, post-oxidation annealing techniques, and interface passivation methods to reduce interface trap density. Enhanced gate oxide reliability and channel mobility are achieved through precise control of the oxidation environment and temperature profiles during manufacturing.Expand Specific Solutions03 Wafer processing and defect reduction methods

Manufacturing advances in SiC MOSFET wafer processing have focused on reducing defects such as micropipes, dislocations, and basal plane defects. Techniques include optimized wafer slicing, polishing processes, and defect screening methodologies. These improvements lead to higher yield rates and more reliable devices, enabling larger diameter wafers to be processed successfully for commercial applications.Expand Specific Solutions04 Doping and implantation techniques

Advanced doping and ion implantation methods have been developed specifically for SiC MOSFET manufacturing. These techniques address the challenges of achieving precise dopant profiles in the hard SiC crystal structure. Innovations include high-temperature implantation, specialized annealing processes for dopant activation, and novel approaches to creating well-defined p-n junctions with minimal lattice damage.Expand Specific Solutions05 High-volume manufacturing and scaling solutions

Manufacturing advances have enabled the transition from small-scale to high-volume production of SiC MOSFETs. These innovations include automated handling systems, standardized process flows, and equipment specifically designed for SiC wafer processing. Larger wafer diameters (150mm and 200mm) are now being processed with improved uniformity and yield, reducing the cost per die and making SiC MOSFETs more commercially viable for power electronics applications.Expand Specific Solutions

Key SiC Wafer Manufacturers and Competitors

The SiC MOSFET wafer manufacturing landscape is currently in a growth phase, with the market expanding rapidly due to increasing demand in electric vehicles, renewable energy, and industrial applications. The global market size is projected to reach several billion dollars by 2025, driven by the superior performance of SiC over traditional silicon in high-power applications. Technologically, the field is transitioning from early maturity to mainstream adoption, with key players at different development stages. Established leaders like Wolfspeed, STMicroelectronics, and Sumitomo Electric have advanced manufacturing capabilities and extensive IP portfolios, while DENSO, Microchip, and GLOBALFOUNDRIES are making significant investments. Emerging competitors from China, including BYD Semiconductor and Anhui Xinta, are rapidly developing capabilities to challenge traditional market dominance, particularly in domestic applications.

Stmicroelectronics Srl

Technical Solution: STMicroelectronics采用创新的多晶圆尺寸(150mm和200mm)制造策略,通过其专有的"第三代"SiC MOSFET技术平台实现了更高的性能和可靠性。公司开发了先进的沟槽栅极结构(trench-gate)工艺,相比平面结构可降低30%的导通电阻。ST还实施了优化的离子注入和激活工艺,减少了界面缺陷,提高了沟道迁移率。其独特的终端结构设计提高了器件的击穿电压稳定性,同时减小了芯片面积。ST的制造工艺采用了改进的氧化工艺和钝化技术,显著提高了栅极氧化层质量和长期可靠性。公司还开发了专用的金属化系统,优化了欧姆接触电阻,进一步降低了器件的总体损耗。

优势:拥有完整的SiC MOSFET产品组合,从650V到1700V覆盖多种应用;制造工艺成熟度高,已实现大规模量产;缺点:在极高电压(>3.3kV)SiC器件领域的布局相对较少;对SiC衬底供应链的依赖性较高,需要进一步加强垂直整合。

Wolfspeed, Inc.

Technical Solution: Wolfspeed采用150mm和200mm SiC晶圆制造技术,通过专有的高温CVD外延生长工艺实现高质量SiC外延层。其创新的晶圆处理技术包括优化的离子注入工艺和高温退火技术,有效减少了缺陷密度。Wolfspeed还开发了专用的栅氧化工艺,能在高温下形成高质量的二氧化硅层,显著提高了器件的可靠性。公司实施了先进的金属化和钝化技术,采用多层金属互连结构,增强了器件的电流承载能力。Wolfspeed的制造工艺实现了业界领先的导通电阻,其第四代SiC MOSFET器件比前代产品降低了40%的导通电阻,同时提高了开关性能和可靠性。

优势:拥有垂直整合的SiC供应链,从衬底到器件全流程控制;在150mm和200mm晶圆技术上处于领先地位;缺点:制造成本仍然较高,需要进一步优化以实现更广泛的市场渗透;大规模生产良率挑战仍然存在。

Critical Patents in SiC Wafer Manufacturing

Silicon carbide power mos field effect transistors and manufacturing methods

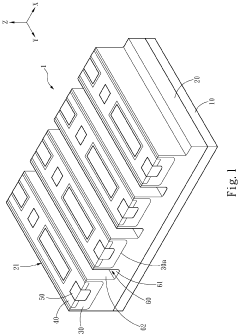

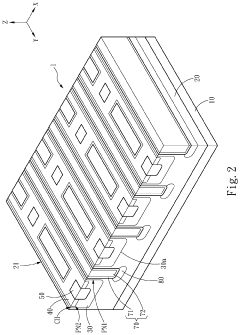

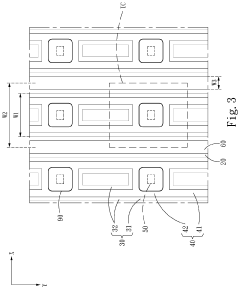

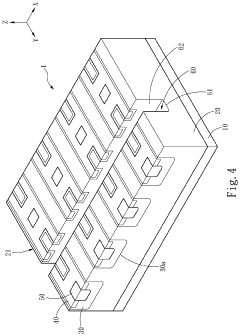

PatentInactiveEP1576672A2

Innovation

- The implementation of an n-type silicon carbide limiting region with a higher carrier concentration than the drift layer, positioned between the drift layer and the p-type silicon carbide region, reduces the depletion region and on-state resistance by creating a shorter current path, and the use of an epitaxial layer or implanted regions to define the limiting region.

Silicon carbide semiconductor device

PatentPendingUS20240234569A9

Innovation

- A silicon carbide semiconductor device with a hybrid gate structure featuring a trench gate configuration that reduces JFET resistance and parasitic gate-to-drain capacitance, enhancing switching performance by increasing channel width density and optimizing the layout of doped regions and trenches.

Supply Chain Considerations for SiC Materials

The SiC MOSFET supply chain presents unique challenges and opportunities that significantly impact the advancement of wafer manufacturing technologies. The supply chain for SiC materials begins with raw silicon and carbon sources, which must meet extremely high purity standards to ensure device performance. Currently, the global supply of semiconductor-grade SiC is concentrated among a limited number of suppliers, creating potential bottlenecks as demand continues to grow exponentially with the expansion of electric vehicle and renewable energy markets.

Material sourcing represents a critical vulnerability in the SiC supply chain. High-quality silicon carbide substrates require specialized manufacturing processes that few companies have mastered at scale. The geographical concentration of these capabilities—primarily in the United States, Japan, and Europe—introduces geopolitical risks that could disrupt availability and pricing stability. Recent initiatives to diversify supply sources have emerged in China and South Korea, though quality consistency remains a challenge for newer market entrants.

Vertical integration strategies have become increasingly prevalent among major SiC device manufacturers. Companies like Wolfspeed, Infineon, and STMicroelectronics have made significant investments to control multiple stages of the supply chain, from substrate production to epitaxial growth and device fabrication. This approach helps mitigate supply uncertainties but requires substantial capital investment that smaller players cannot easily match.

The equipment supply chain for SiC wafer manufacturing presents another layer of complexity. Specialized furnaces for crystal growth, precision cutting equipment for wafer slicing, and advanced polishing systems all require different suppliers with unique expertise. The transition to larger wafer diameters (from 4-inch to 6-inch and now 8-inch) has necessitated new equipment development, creating temporary misalignments between equipment availability and production needs.

Sustainability considerations are increasingly influencing supply chain decisions. The energy-intensive nature of SiC crystal growth has prompted manufacturers to locate facilities in regions with access to renewable energy sources. Additionally, recycling programs for SiC manufacturing byproducts are being developed to reduce waste and recover valuable materials, though these initiatives remain in early stages of implementation.

Collaborative ecosystem development has emerged as a strategy to address supply chain vulnerabilities. Industry consortia, university partnerships, and government-sponsored research initiatives are working to expand the supplier base and develop alternative production methods. These collaborations aim to standardize material specifications, improve yield rates, and reduce the overall cost structure of the SiC supply chain.

Material sourcing represents a critical vulnerability in the SiC supply chain. High-quality silicon carbide substrates require specialized manufacturing processes that few companies have mastered at scale. The geographical concentration of these capabilities—primarily in the United States, Japan, and Europe—introduces geopolitical risks that could disrupt availability and pricing stability. Recent initiatives to diversify supply sources have emerged in China and South Korea, though quality consistency remains a challenge for newer market entrants.

Vertical integration strategies have become increasingly prevalent among major SiC device manufacturers. Companies like Wolfspeed, Infineon, and STMicroelectronics have made significant investments to control multiple stages of the supply chain, from substrate production to epitaxial growth and device fabrication. This approach helps mitigate supply uncertainties but requires substantial capital investment that smaller players cannot easily match.

The equipment supply chain for SiC wafer manufacturing presents another layer of complexity. Specialized furnaces for crystal growth, precision cutting equipment for wafer slicing, and advanced polishing systems all require different suppliers with unique expertise. The transition to larger wafer diameters (from 4-inch to 6-inch and now 8-inch) has necessitated new equipment development, creating temporary misalignments between equipment availability and production needs.

Sustainability considerations are increasingly influencing supply chain decisions. The energy-intensive nature of SiC crystal growth has prompted manufacturers to locate facilities in regions with access to renewable energy sources. Additionally, recycling programs for SiC manufacturing byproducts are being developed to reduce waste and recover valuable materials, though these initiatives remain in early stages of implementation.

Collaborative ecosystem development has emerged as a strategy to address supply chain vulnerabilities. Industry consortia, university partnerships, and government-sponsored research initiatives are working to expand the supplier base and develop alternative production methods. These collaborations aim to standardize material specifications, improve yield rates, and reduce the overall cost structure of the SiC supply chain.

Environmental Impact of SiC Manufacturing Processes

The manufacturing of Silicon Carbide (SiC) MOSFETs, while offering significant energy efficiency benefits in end applications, presents notable environmental challenges throughout its production lifecycle. The environmental footprint of SiC manufacturing processes is considerably larger than traditional silicon semiconductor fabrication, primarily due to higher energy requirements and more complex processing steps.

SiC wafer production demands temperatures exceeding 2000°C for crystal growth, consuming approximately 5-7 times more energy than silicon wafer manufacturing. This intensive energy consumption translates to higher carbon emissions, particularly in regions where electricity generation relies heavily on fossil fuels. Studies indicate that a typical SiC wafer fabrication facility may generate 2-3 times the greenhouse gas emissions of a comparable silicon facility on a per-wafer basis.

Water usage represents another significant environmental concern. SiC manufacturing requires substantial quantities of ultra-pure water for cleaning and processing steps, with estimates suggesting consumption of 5,000-7,000 gallons per wafer—approximately 30% higher than silicon wafer production. The resulting wastewater contains various chemical compounds including hydrofluoric acid, heavy metals, and suspended solids that require specialized treatment before discharge.

Chemical utilization in SiC processing introduces additional environmental challenges. The etching and cleaning processes employ hazardous substances including hydrogen chloride, sulfuric acid, and various solvents. These chemicals present potential risks to local ecosystems if not properly managed, and their production and transportation contribute to the overall environmental impact of SiC device manufacturing.

Waste generation constitutes a further environmental consideration. SiC manufacturing produces silicon carbide slurry waste, spent chemicals, and damaged wafers that require proper disposal or recycling. The hardness of SiC materials also accelerates tool wear, generating additional solid waste in the form of worn polishing pads and grinding wheels.

Recent industry initiatives have focused on mitigating these environmental impacts through technological innovations and process optimizations. These include closed-loop water recycling systems that can reduce freshwater consumption by up to 50%, energy recovery systems capturing waste heat from high-temperature processes, and advanced abatement systems for reducing harmful emissions. Additionally, several leading manufacturers have implemented chemical recovery and recycling programs that significantly reduce hazardous waste generation.

The industry is gradually transitioning toward more sustainable manufacturing practices, with increasing adoption of renewable energy sources to power production facilities and development of less environmentally harmful chemical processes. These improvements are essential as SiC device production volumes continue to scale to meet growing demand in electric vehicles, renewable energy systems, and industrial applications.

SiC wafer production demands temperatures exceeding 2000°C for crystal growth, consuming approximately 5-7 times more energy than silicon wafer manufacturing. This intensive energy consumption translates to higher carbon emissions, particularly in regions where electricity generation relies heavily on fossil fuels. Studies indicate that a typical SiC wafer fabrication facility may generate 2-3 times the greenhouse gas emissions of a comparable silicon facility on a per-wafer basis.

Water usage represents another significant environmental concern. SiC manufacturing requires substantial quantities of ultra-pure water for cleaning and processing steps, with estimates suggesting consumption of 5,000-7,000 gallons per wafer—approximately 30% higher than silicon wafer production. The resulting wastewater contains various chemical compounds including hydrofluoric acid, heavy metals, and suspended solids that require specialized treatment before discharge.

Chemical utilization in SiC processing introduces additional environmental challenges. The etching and cleaning processes employ hazardous substances including hydrogen chloride, sulfuric acid, and various solvents. These chemicals present potential risks to local ecosystems if not properly managed, and their production and transportation contribute to the overall environmental impact of SiC device manufacturing.

Waste generation constitutes a further environmental consideration. SiC manufacturing produces silicon carbide slurry waste, spent chemicals, and damaged wafers that require proper disposal or recycling. The hardness of SiC materials also accelerates tool wear, generating additional solid waste in the form of worn polishing pads and grinding wheels.

Recent industry initiatives have focused on mitigating these environmental impacts through technological innovations and process optimizations. These include closed-loop water recycling systems that can reduce freshwater consumption by up to 50%, energy recovery systems capturing waste heat from high-temperature processes, and advanced abatement systems for reducing harmful emissions. Additionally, several leading manufacturers have implemented chemical recovery and recycling programs that significantly reduce hazardous waste generation.

The industry is gradually transitioning toward more sustainable manufacturing practices, with increasing adoption of renewable energy sources to power production facilities and development of less environmentally harmful chemical processes. These improvements are essential as SiC device production volumes continue to scale to meet growing demand in electric vehicles, renewable energy systems, and industrial applications.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!