Parallel Operation Of SiC MOSFETs: Challenges And Solutions

SEP 5, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SiC MOSFET Parallel Operation Background and Objectives

Silicon Carbide (SiC) MOSFETs have emerged as revolutionary power semiconductor devices, offering significant advantages over traditional silicon-based counterparts. The evolution of SiC technology began in the early 2000s, with substantial advancements occurring over the past decade as manufacturing processes matured and costs decreased. This technological progression has been driven by increasing demands for higher efficiency, power density, and temperature capability in power electronic systems across various industries including automotive, renewable energy, and industrial applications.

The parallel operation of SiC MOSFETs represents a critical approach to scaling power handling capabilities beyond what single devices can achieve. This technique allows system designers to distribute current across multiple devices, enabling higher power throughput while maintaining the superior switching performance characteristic of SiC technology. The historical trajectory shows a transition from simple paralleling methods borrowed from silicon MOSFET applications to more sophisticated approaches specifically optimized for SiC's unique characteristics.

Current technological trends indicate accelerating adoption of SiC MOSFETs in parallel configurations, particularly as electric vehicle markets expand and renewable energy systems require increasingly efficient power conversion. The inherent properties of SiC—including higher breakdown field strength, thermal conductivity, and switching speed—create both opportunities and challenges when implementing parallel architectures that must be carefully addressed.

The primary objectives of parallel SiC MOSFET implementation include achieving uniform current distribution among paralleled devices, minimizing switching losses during high-frequency operation, maintaining thermal balance across the power module, and ensuring reliable long-term operation under dynamic loading conditions. These objectives must be met while preserving the fundamental advantages that make SiC technology attractive in the first place.

Technical goals for advancing parallel SiC MOSFET operation include developing optimized gate drive architectures that account for the faster switching speeds and unique parasitic elements of SiC devices, creating packaging solutions that minimize inductance imbalances between paralleled dies, implementing effective current sharing methodologies that remain stable across temperature variations, and establishing design guidelines that enable predictable performance scaling as more devices are added in parallel.

The evolution of these parallel operation techniques is expected to continue as SiC device technology itself advances, with newer generations offering improved characteristics that may alleviate some current challenges while potentially introducing new considerations. Understanding this technological trajectory is essential for developing robust solutions that will enable the full potential of paralleled SiC MOSFETs to be realized in next-generation power electronic systems.

The parallel operation of SiC MOSFETs represents a critical approach to scaling power handling capabilities beyond what single devices can achieve. This technique allows system designers to distribute current across multiple devices, enabling higher power throughput while maintaining the superior switching performance characteristic of SiC technology. The historical trajectory shows a transition from simple paralleling methods borrowed from silicon MOSFET applications to more sophisticated approaches specifically optimized for SiC's unique characteristics.

Current technological trends indicate accelerating adoption of SiC MOSFETs in parallel configurations, particularly as electric vehicle markets expand and renewable energy systems require increasingly efficient power conversion. The inherent properties of SiC—including higher breakdown field strength, thermal conductivity, and switching speed—create both opportunities and challenges when implementing parallel architectures that must be carefully addressed.

The primary objectives of parallel SiC MOSFET implementation include achieving uniform current distribution among paralleled devices, minimizing switching losses during high-frequency operation, maintaining thermal balance across the power module, and ensuring reliable long-term operation under dynamic loading conditions. These objectives must be met while preserving the fundamental advantages that make SiC technology attractive in the first place.

Technical goals for advancing parallel SiC MOSFET operation include developing optimized gate drive architectures that account for the faster switching speeds and unique parasitic elements of SiC devices, creating packaging solutions that minimize inductance imbalances between paralleled dies, implementing effective current sharing methodologies that remain stable across temperature variations, and establishing design guidelines that enable predictable performance scaling as more devices are added in parallel.

The evolution of these parallel operation techniques is expected to continue as SiC device technology itself advances, with newer generations offering improved characteristics that may alleviate some current challenges while potentially introducing new considerations. Understanding this technological trajectory is essential for developing robust solutions that will enable the full potential of paralleled SiC MOSFETs to be realized in next-generation power electronic systems.

Market Demand Analysis for Parallel SiC MOSFET Applications

The global market for Silicon Carbide (SiC) MOSFETs is experiencing unprecedented growth, driven primarily by the rapid expansion of electric vehicles (EVs), renewable energy systems, and industrial power applications. Market research indicates that the SiC power device market is projected to grow at a CAGR of 30% through 2026, reaching a market value of $2.5 billion, with parallel operation applications representing a significant portion of this growth.

The demand for parallel SiC MOSFET configurations stems from high-power applications requiring current capabilities beyond what single devices can deliver. Electric vehicle inverters represent the largest market segment, with requirements for power modules capable of handling 250-800A continuous current while maintaining high efficiency. This segment alone is expected to grow by 35% annually as automotive manufacturers transition from silicon to SiC technology in their drivetrain designs.

Renewable energy systems, particularly solar inverters and wind power converters, constitute the second-largest market segment. These applications demand parallel SiC MOSFETs to handle increasing power densities while reducing system size and weight. Industry data shows that SiC-based solar inverters can achieve 99% efficiency, significantly outperforming traditional silicon-based solutions, which translates to substantial energy savings over system lifetime.

Industrial motor drives and power supplies represent another significant market segment, with requirements for higher switching frequencies and reduced cooling needs that parallel SiC MOSFETs can provide. The industrial sector values the reduced system size and increased reliability, with estimates suggesting a 30% reduction in overall system costs when accounting for smaller passive components and simplified thermal management.

Data center power supplies are emerging as a rapidly growing application area, driven by the need for higher efficiency and power density. The parallel operation of SiC MOSFETs enables power supplies to achieve titanium efficiency standards (96%+) while reducing form factors by up to 40% compared to silicon-based alternatives.

Market analysis reveals that current parallel SiC MOSFET applications face several challenges that limit wider adoption. Current balancing issues, parasitic inductance effects, and gate driver complexity are cited by 65% of system designers as significant barriers to implementation. Additionally, the cost premium of SiC devices (currently 2.5-3x higher than silicon equivalents) remains a concern, though this gap is narrowing by approximately 8-10% annually as manufacturing scales.

Customer surveys indicate that improved thermal management solutions, standardized design methodologies for parallel operation, and more integrated driver solutions would accelerate market adoption. The industry is responding with new packaging technologies and integrated modules specifically designed for parallel operation, which are expected to capture 45% of the SiC power module market by 2025.

The demand for parallel SiC MOSFET configurations stems from high-power applications requiring current capabilities beyond what single devices can deliver. Electric vehicle inverters represent the largest market segment, with requirements for power modules capable of handling 250-800A continuous current while maintaining high efficiency. This segment alone is expected to grow by 35% annually as automotive manufacturers transition from silicon to SiC technology in their drivetrain designs.

Renewable energy systems, particularly solar inverters and wind power converters, constitute the second-largest market segment. These applications demand parallel SiC MOSFETs to handle increasing power densities while reducing system size and weight. Industry data shows that SiC-based solar inverters can achieve 99% efficiency, significantly outperforming traditional silicon-based solutions, which translates to substantial energy savings over system lifetime.

Industrial motor drives and power supplies represent another significant market segment, with requirements for higher switching frequencies and reduced cooling needs that parallel SiC MOSFETs can provide. The industrial sector values the reduced system size and increased reliability, with estimates suggesting a 30% reduction in overall system costs when accounting for smaller passive components and simplified thermal management.

Data center power supplies are emerging as a rapidly growing application area, driven by the need for higher efficiency and power density. The parallel operation of SiC MOSFETs enables power supplies to achieve titanium efficiency standards (96%+) while reducing form factors by up to 40% compared to silicon-based alternatives.

Market analysis reveals that current parallel SiC MOSFET applications face several challenges that limit wider adoption. Current balancing issues, parasitic inductance effects, and gate driver complexity are cited by 65% of system designers as significant barriers to implementation. Additionally, the cost premium of SiC devices (currently 2.5-3x higher than silicon equivalents) remains a concern, though this gap is narrowing by approximately 8-10% annually as manufacturing scales.

Customer surveys indicate that improved thermal management solutions, standardized design methodologies for parallel operation, and more integrated driver solutions would accelerate market adoption. The industry is responding with new packaging technologies and integrated modules specifically designed for parallel operation, which are expected to capture 45% of the SiC power module market by 2025.

Technical Challenges in SiC MOSFET Parallel Operation

Silicon Carbide (SiC) MOSFETs have emerged as superior alternatives to silicon-based power devices due to their wide bandgap properties, offering higher breakdown voltage, faster switching speeds, and better thermal conductivity. However, the parallel operation of SiC MOSFETs presents significant technical challenges that must be addressed to fully leverage their advantages in high-power applications.

Current threshold voltage variations among SiC MOSFETs represent a primary challenge, with typical variations ranging from ±0.5V to ±1.0V even within the same manufacturing batch. This variation leads to uneven current distribution during switching transitions, causing certain devices to carry disproportionate current loads, which accelerates degradation and reduces overall system reliability.

The extremely fast switching speeds of SiC MOSFETs (dv/dt rates exceeding 50V/ns) create substantial challenges in parallel configurations. These rapid transitions generate parasitic inductances in gate-drive loops and power loops, resulting in voltage spikes, oscillations, and electromagnetic interference (EMI). The uneven distribution of parasitic elements across parallel devices further exacerbates current imbalance issues.

Temperature sensitivity presents another significant challenge. SiC MOSFETs exhibit a positive temperature coefficient for on-resistance, which theoretically should help balance current distribution. However, this self-balancing mechanism only functions effectively during steady-state operation and not during critical switching transitions where most failures occur.

Gate drive design for parallel SiC MOSFETs requires special consideration. The lower gate threshold margin compared to silicon devices means that noise immunity is reduced, making parallel-connected devices more susceptible to parasitic turn-on effects. Additionally, the gate oxide in SiC MOSFETs is more vulnerable to damage from voltage spikes, necessitating precise gate voltage control across all parallel devices.

Layout and thermal management considerations become exponentially more complex with parallel configurations. The physical arrangement of devices significantly impacts current sharing, with asymmetrical layouts creating uneven current paths. Thermal coupling between adjacent devices can create hotspots that accelerate degradation in specific MOSFETs within the parallel array.

Dynamic current sharing during switching transients remains perhaps the most difficult challenge to overcome. While static current sharing can be managed through careful device selection and layout, transient current imbalances during turn-on and turn-off events are more difficult to control and can lead to device failure even when steady-state operation appears balanced.

Recent research has identified that the short-circuit capability of parallel-connected SiC MOSFETs is significantly reduced compared to single devices, with failure modes occurring at lower energy levels than would be predicted by simply scaling single-device specifications.

Current threshold voltage variations among SiC MOSFETs represent a primary challenge, with typical variations ranging from ±0.5V to ±1.0V even within the same manufacturing batch. This variation leads to uneven current distribution during switching transitions, causing certain devices to carry disproportionate current loads, which accelerates degradation and reduces overall system reliability.

The extremely fast switching speeds of SiC MOSFETs (dv/dt rates exceeding 50V/ns) create substantial challenges in parallel configurations. These rapid transitions generate parasitic inductances in gate-drive loops and power loops, resulting in voltage spikes, oscillations, and electromagnetic interference (EMI). The uneven distribution of parasitic elements across parallel devices further exacerbates current imbalance issues.

Temperature sensitivity presents another significant challenge. SiC MOSFETs exhibit a positive temperature coefficient for on-resistance, which theoretically should help balance current distribution. However, this self-balancing mechanism only functions effectively during steady-state operation and not during critical switching transitions where most failures occur.

Gate drive design for parallel SiC MOSFETs requires special consideration. The lower gate threshold margin compared to silicon devices means that noise immunity is reduced, making parallel-connected devices more susceptible to parasitic turn-on effects. Additionally, the gate oxide in SiC MOSFETs is more vulnerable to damage from voltage spikes, necessitating precise gate voltage control across all parallel devices.

Layout and thermal management considerations become exponentially more complex with parallel configurations. The physical arrangement of devices significantly impacts current sharing, with asymmetrical layouts creating uneven current paths. Thermal coupling between adjacent devices can create hotspots that accelerate degradation in specific MOSFETs within the parallel array.

Dynamic current sharing during switching transients remains perhaps the most difficult challenge to overcome. While static current sharing can be managed through careful device selection and layout, transient current imbalances during turn-on and turn-off events are more difficult to control and can lead to device failure even when steady-state operation appears balanced.

Recent research has identified that the short-circuit capability of parallel-connected SiC MOSFETs is significantly reduced compared to single devices, with failure modes occurring at lower energy levels than would be predicted by simply scaling single-device specifications.

Current Parallel Operation Solutions and Implementations

01 Current balancing techniques for parallel SiC MOSFETs

Various current balancing techniques are employed to ensure equal current distribution among parallel-connected SiC MOSFETs. These include gate resistance adjustment, source inductance balancing, and active current sharing circuits. These techniques help minimize thermal stress and prevent device failure due to current imbalance, which is critical for high-power applications where multiple SiC MOSFETs operate in parallel.- Current balancing techniques for parallel SiC MOSFETs: Various current balancing techniques are employed to ensure equal current distribution among parallel-connected SiC MOSFETs. These include gate resistance optimization, source inductance balancing, and active current sharing circuits. These techniques help minimize thermal stress and prevent device failure due to current imbalance, which is particularly important in high-power applications where multiple SiC MOSFETs are operated in parallel to handle large currents.

- Thermal management for parallel SiC MOSFETs: Effective thermal management is crucial for parallel operation of SiC MOSFETs to ensure reliable performance. This includes optimized heat sink designs, thermal interface materials, and layout considerations to achieve uniform temperature distribution. Advanced cooling techniques such as liquid cooling systems and phase-change materials are implemented to handle the high power density of SiC devices, preventing thermal runaway and extending device lifetime in parallel configurations.

- Gate drive optimization for parallel SiC MOSFETs: Specialized gate drive circuits are designed to address the unique requirements of parallel SiC MOSFETs. These include synchronized switching, optimized gate voltage levels, and controlled slew rates to ensure simultaneous operation. Advanced gate drivers incorporate features like desaturation protection, active Miller clamping, and temperature compensation to maintain balanced switching characteristics across multiple devices, improving overall system reliability and efficiency.

- Layout and packaging considerations for parallel SiC MOSFETs: Proper layout and packaging techniques are essential for successful parallel operation of SiC MOSFETs. Symmetrical layouts with matched trace lengths, minimized parasitic inductances, and optimized power loop designs help achieve balanced current sharing. Advanced packaging technologies such as direct bonded copper substrates, embedded die packages, and low-inductance laminated bus structures are employed to improve thermal performance and reduce parasitic effects in high-frequency switching applications.

- Reliability and failure mode analysis of parallel SiC MOSFETs: Comprehensive reliability testing and failure mode analysis are conducted for parallel SiC MOSFET configurations. This includes accelerated life testing, short-circuit capability assessment, and avalanche ruggedness evaluation. Advanced monitoring systems are implemented to detect early signs of degradation or imbalance among parallel devices. Understanding the failure mechanisms specific to parallel operation helps in developing robust design guidelines and protection strategies for high-power SiC MOSFET applications.

02 Thermal management for parallel SiC MOSFETs

Effective thermal management is crucial for parallel operation of SiC MOSFETs to ensure reliability and performance. This includes optimized heat sink designs, thermal interface materials, and cooling strategies to maintain uniform temperature distribution across parallel devices. Proper thermal management prevents thermal runaway and ensures balanced current sharing among parallel-connected SiC MOSFETs.Expand Specific Solutions03 Gate drive optimization for parallel SiC MOSFETs

Specialized gate drive circuits are designed to address the unique requirements of parallel SiC MOSFETs. These include synchronized gate signals, optimized gate resistance networks, and isolation techniques to ensure simultaneous switching and prevent parasitic oscillations. Advanced gate drive designs help minimize switching losses and improve the overall efficiency of parallel SiC MOSFET configurations.Expand Specific Solutions04 Layout and packaging considerations for parallel SiC MOSFETs

Optimized layout and packaging techniques are essential for successful parallel operation of SiC MOSFETs. These include symmetrical PCB layouts, minimized parasitic inductances, and balanced interconnections to ensure uniform current distribution. Advanced packaging solutions integrate multiple SiC MOSFETs with optimized thermal and electrical connections to enhance power density and reliability in high-power applications.Expand Specific Solutions05 Protection and monitoring systems for parallel SiC MOSFETs

Specialized protection and monitoring systems are implemented to ensure safe operation of parallel SiC MOSFETs. These include overcurrent protection, short-circuit detection, temperature monitoring, and fault management strategies. Advanced monitoring systems can detect imbalances in current sharing or thermal distribution among parallel devices and take corrective actions to prevent catastrophic failures in high-power applications.Expand Specific Solutions

Key Industry Players in SiC Power Semiconductor Market

The parallel operation of SiC MOSFETs is currently in a growth phase, with the market expanding rapidly due to increasing demand for high-efficiency power electronics. The global market size is projected to reach significant volumes as industries transition to wide bandgap semiconductors. Technologically, the field shows moderate maturity with ongoing challenges in current sharing and switching synchronization. Leading players include academic institutions like Tsinghua University and Hunan University conducting fundamental research, while companies such as ROHM, Bosch, and Sirius Semiconductor are commercializing solutions. State Grid entities and LG Electronics are driving application development, creating a competitive landscape where collaboration between research institutions and industrial manufacturers is essential for addressing thermal management and reliability challenges.

Robert Bosch GmbH

Technical Solution: Bosch has engineered a comprehensive parallel SiC MOSFET solution focused on automotive and industrial applications. Their technology employs dynamic gate resistance adjustment that adapts in real-time to switching conditions, ensuring balanced current distribution across parallel devices[1]. Bosch's approach includes proprietary screening and matching processes for SiC MOSFETs to minimize parameter variations that cause current imbalance. Their system incorporates integrated current sensing with feedback control loops that actively compensate for device parameter drift over temperature and aging[2]. Bosch has also developed specialized gate driver ICs with independently adjustable output channels specifically designed for parallel operation, allowing precise control of each MOSFET's switching behavior. Their solution addresses thermal management through advanced packaging technology that ensures uniform temperature distribution across parallel devices[3].

Strengths: Exceptional reliability under extreme automotive conditions; sophisticated parameter matching process; integrated system approach combining hardware and software solutions. Weaknesses: Higher initial cost; requires specialized components that may limit design flexibility; more complex implementation compared to traditional solutions.

ROHM Co., Ltd.

Technical Solution: ROHM has developed advanced parallel operation solutions for SiC MOSFETs that address current sharing challenges through innovative gate driver designs. Their approach includes precise gate timing control technology that synchronizes switching operations within nanoseconds to minimize current imbalance[1]. ROHM's solution incorporates active current balancing circuits that continuously monitor and adjust individual MOSFET performance in parallel configurations. Their SiC MOSFET modules feature matched thermal characteristics and integrated temperature sensors to prevent thermal runaway during parallel operation[2]. Additionally, ROHM has implemented specialized layout techniques in their power modules that minimize parasitic inductance differences between parallel paths, which is critical for balanced current distribution during high-frequency switching operations[3].

Strengths: Superior current balancing capability through advanced gate driver technology; excellent thermal management integration; proven reliability in high-power applications. Weaknesses: Higher implementation cost compared to conventional solutions; requires more complex control systems; limited compatibility with third-party components.

Critical Patents and Research in SiC MOSFET Parallelization

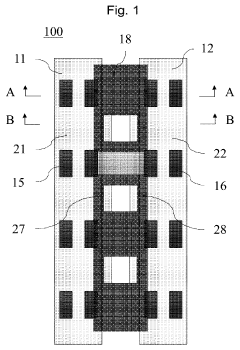

Silicon carbide metal oxide semiconductor field effect transistor and manufacturing method of silicon carbide metal oxide semiconductor field effect transistor

PatentPendingUS20230378341A1

Innovation

- The design incorporates alternating cells with specific well regions, source regions, and contact layers, including ohmic and Schottky contacts, to reduce channel density, enhance short-circuit tolerance, and minimize reverse leakage current and forward voltage drop, while maintaining the transistor's size and functionality.

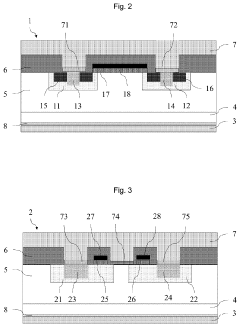

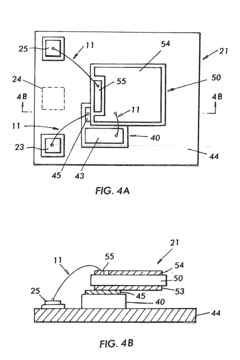

High power silicon carbide and silicon semiconductor device package

PatentInactiveUS20040130021A1

Innovation

- A hybrid transistor structure is created by co-packaging a silicon carbide field effect transistor (SiCFET) with a silicon MOSFET in a die-on-die configuration, where the SiCFET is mounted electrode-on-electrode with the MOSFET, allowing for shared thermal management and reduced footprint, with the SiCFET providing faster switching and improved thermal management through shared heat sinks.

Thermal Management Strategies for Parallel SiC Configurations

Effective thermal management is critical for parallel SiC MOSFET configurations due to their high power density and switching frequencies. The thermal challenges in parallel operation stem from the positive temperature coefficient of SiC devices, which can lead to thermal runaway if heat distribution is uneven. This characteristic, while beneficial for current sharing, requires sophisticated cooling solutions to maintain optimal performance and reliability.

Advanced cooling technologies have emerged as essential components for parallel SiC MOSFET systems. Direct liquid cooling methods, including cold plates and immersion cooling, offer superior thermal performance by directly removing heat from semiconductor junctions. These solutions achieve thermal resistances as low as 0.1°C/W, significantly outperforming traditional air-cooled systems which typically range from 0.5-1.0°C/W.

Phase-change materials (PCMs) represent another innovative approach, providing thermal buffering during transient power spikes. PCMs can absorb substantial heat energy during phase transitions, maintaining more stable junction temperatures during variable load conditions that are common in applications like electric vehicle inverters and renewable energy converters.

Thermal interface materials (TIMs) play a crucial role in the thermal management stack. Advanced ceramic-filled polymers and metal-based TIMs with thermal conductivities exceeding 10 W/m·K are increasingly replacing conventional thermal greases (2-5 W/m·K) to minimize thermal resistance between SiC devices and cooling systems.

Integrated thermal sensors and dynamic thermal management systems enable real-time monitoring and adjustment of operating parameters. These systems can detect temperature imbalances between parallel devices and implement corrective measures such as adjusting gate drive signals or activating supplementary cooling mechanisms before thermal issues become critical.

3D thermal modeling and computational fluid dynamics (CFD) simulations have become essential design tools for optimizing thermal management in parallel SiC configurations. These advanced simulation techniques allow engineers to identify potential hotspots and thermal coupling effects between adjacent devices, enabling more effective cooling system designs and device layouts.

The industry trend is moving toward holistic thermal management approaches that combine multiple cooling technologies with intelligent thermal control systems. This integration is particularly important for high-density applications where parallel SiC MOSFETs must operate reliably under variable environmental conditions and dynamic load profiles.

Advanced cooling technologies have emerged as essential components for parallel SiC MOSFET systems. Direct liquid cooling methods, including cold plates and immersion cooling, offer superior thermal performance by directly removing heat from semiconductor junctions. These solutions achieve thermal resistances as low as 0.1°C/W, significantly outperforming traditional air-cooled systems which typically range from 0.5-1.0°C/W.

Phase-change materials (PCMs) represent another innovative approach, providing thermal buffering during transient power spikes. PCMs can absorb substantial heat energy during phase transitions, maintaining more stable junction temperatures during variable load conditions that are common in applications like electric vehicle inverters and renewable energy converters.

Thermal interface materials (TIMs) play a crucial role in the thermal management stack. Advanced ceramic-filled polymers and metal-based TIMs with thermal conductivities exceeding 10 W/m·K are increasingly replacing conventional thermal greases (2-5 W/m·K) to minimize thermal resistance between SiC devices and cooling systems.

Integrated thermal sensors and dynamic thermal management systems enable real-time monitoring and adjustment of operating parameters. These systems can detect temperature imbalances between parallel devices and implement corrective measures such as adjusting gate drive signals or activating supplementary cooling mechanisms before thermal issues become critical.

3D thermal modeling and computational fluid dynamics (CFD) simulations have become essential design tools for optimizing thermal management in parallel SiC configurations. These advanced simulation techniques allow engineers to identify potential hotspots and thermal coupling effects between adjacent devices, enabling more effective cooling system designs and device layouts.

The industry trend is moving toward holistic thermal management approaches that combine multiple cooling technologies with intelligent thermal control systems. This integration is particularly important for high-density applications where parallel SiC MOSFETs must operate reliably under variable environmental conditions and dynamic load profiles.

Reliability and Lifetime Assessment of Parallel SiC Systems

The reliability and lifetime assessment of parallel SiC MOSFET systems represents a critical aspect of power electronics design that directly impacts system performance, maintenance schedules, and total cost of ownership. When multiple SiC MOSFETs operate in parallel, their collective reliability characteristics differ significantly from single-device implementations, necessitating specialized evaluation methodologies.

Accelerated life testing has emerged as a fundamental approach for evaluating the long-term reliability of parallel SiC systems. These tests subject devices to elevated stress conditions—including temperature cycling, power cycling, and voltage stress—to induce failure mechanisms that would typically manifest over years of normal operation. The resulting data enables the development of lifetime models that can predict system behavior under various operating conditions.

Failure mode analysis reveals that parallel-connected SiC MOSFETs exhibit unique degradation patterns compared to standalone devices. The most prevalent failure mechanisms include gate oxide degradation, threshold voltage shifts, and die-attach solder fatigue. These issues are often exacerbated by current imbalances between parallel devices, creating localized hotspots that accelerate degradation in specific components.

Statistical lifetime distribution models, particularly Weibull analysis, have proven effective for characterizing the reliability of parallel SiC systems. These models account for both infant mortality failures and wear-out mechanisms, providing comprehensive reliability projections. Recent research indicates that parallel SiC MOSFET systems typically demonstrate Weibull shape parameters between 2.3 and 3.1, suggesting wear-out as the dominant failure mode.

Condition monitoring techniques have advanced significantly, enabling real-time assessment of parallel SiC system health. Key parameters monitored include on-state resistance, switching characteristics, thermal impedance, and gate leakage current. Modern monitoring systems employ machine learning algorithms to detect subtle changes in these parameters, allowing for predictive maintenance before catastrophic failures occur.

Lifetime enhancement strategies focus on addressing the root causes of premature failures in parallel systems. Advanced thermal management solutions, including phase-change materials and liquid cooling, have demonstrated the potential to extend system lifetime by 30-40% by maintaining more uniform temperature distribution across parallel devices. Additionally, active gate driving techniques that dynamically adjust switching parameters based on real-time monitoring data have shown promise in balancing current distribution and reducing stress on individual devices.

Accelerated life testing has emerged as a fundamental approach for evaluating the long-term reliability of parallel SiC systems. These tests subject devices to elevated stress conditions—including temperature cycling, power cycling, and voltage stress—to induce failure mechanisms that would typically manifest over years of normal operation. The resulting data enables the development of lifetime models that can predict system behavior under various operating conditions.

Failure mode analysis reveals that parallel-connected SiC MOSFETs exhibit unique degradation patterns compared to standalone devices. The most prevalent failure mechanisms include gate oxide degradation, threshold voltage shifts, and die-attach solder fatigue. These issues are often exacerbated by current imbalances between parallel devices, creating localized hotspots that accelerate degradation in specific components.

Statistical lifetime distribution models, particularly Weibull analysis, have proven effective for characterizing the reliability of parallel SiC systems. These models account for both infant mortality failures and wear-out mechanisms, providing comprehensive reliability projections. Recent research indicates that parallel SiC MOSFET systems typically demonstrate Weibull shape parameters between 2.3 and 3.1, suggesting wear-out as the dominant failure mode.

Condition monitoring techniques have advanced significantly, enabling real-time assessment of parallel SiC system health. Key parameters monitored include on-state resistance, switching characteristics, thermal impedance, and gate leakage current. Modern monitoring systems employ machine learning algorithms to detect subtle changes in these parameters, allowing for predictive maintenance before catastrophic failures occur.

Lifetime enhancement strategies focus on addressing the root causes of premature failures in parallel systems. Advanced thermal management solutions, including phase-change materials and liquid cooling, have demonstrated the potential to extend system lifetime by 30-40% by maintaining more uniform temperature distribution across parallel devices. Additionally, active gate driving techniques that dynamically adjust switching parameters based on real-time monitoring data have shown promise in balancing current distribution and reducing stress on individual devices.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!