Case Benchmark: FinFET Performance In High-Vibration Environments

SEP 11, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Technology Background and Objectives

FinFET technology emerged in the early 2000s as a revolutionary advancement in semiconductor manufacturing, designed to overcome the limitations of traditional planar transistors. As transistor dimensions continued to shrink following Moore's Law, conventional planar designs faced significant challenges including short channel effects, increased leakage current, and diminished electrostatic control. The three-dimensional fin-shaped structure of FinFETs provided superior gate control over the channel, enabling continued scaling while maintaining performance and power efficiency.

The evolution of FinFET technology has progressed through several generations, from 22nm to the current 5nm nodes, with each iteration delivering improvements in performance, power consumption, and density. This progression has been instrumental in supporting the exponential growth in computing power required by modern applications such as artificial intelligence, high-performance computing, and mobile devices.

While FinFETs have demonstrated exceptional performance in standard operating conditions, their behavior in high-vibration environments remains a critical area requiring thorough investigation. Vibration-induced effects can potentially impact transistor performance, reliability, and longevity through various mechanisms including mechanical stress on the fin structure, thermal fluctuations, and changes in carrier mobility.

The primary objective of this technical research is to comprehensively evaluate FinFET performance characteristics under various vibration conditions that simulate real-world deployment scenarios. These include automotive applications, aerospace systems, industrial machinery, and military equipment where electronic components are routinely subjected to significant mechanical stresses.

Specifically, this research aims to quantify the impact of different vibration frequencies, amplitudes, and durations on key FinFET performance parameters including threshold voltage stability, leakage current, on-state current, switching speed, and overall reliability metrics. The investigation will encompass both acute performance degradation during vibration events and potential long-term reliability implications resulting from repeated or prolonged exposure to vibration.

Additionally, this research seeks to identify potential design modifications, manufacturing process adjustments, or packaging solutions that could enhance FinFET resilience in high-vibration environments. Understanding these factors is increasingly important as semiconductor devices penetrate more diverse application domains with challenging operating conditions.

The findings from this research will inform future FinFET design optimizations, establish performance benchmarks for vibration tolerance, and potentially guide the development of specialized variants for high-reliability applications. This knowledge is essential for expanding the deployment of advanced semiconductor technologies into emerging markets where environmental robustness is a critical requirement alongside performance and power efficiency.

The evolution of FinFET technology has progressed through several generations, from 22nm to the current 5nm nodes, with each iteration delivering improvements in performance, power consumption, and density. This progression has been instrumental in supporting the exponential growth in computing power required by modern applications such as artificial intelligence, high-performance computing, and mobile devices.

While FinFETs have demonstrated exceptional performance in standard operating conditions, their behavior in high-vibration environments remains a critical area requiring thorough investigation. Vibration-induced effects can potentially impact transistor performance, reliability, and longevity through various mechanisms including mechanical stress on the fin structure, thermal fluctuations, and changes in carrier mobility.

The primary objective of this technical research is to comprehensively evaluate FinFET performance characteristics under various vibration conditions that simulate real-world deployment scenarios. These include automotive applications, aerospace systems, industrial machinery, and military equipment where electronic components are routinely subjected to significant mechanical stresses.

Specifically, this research aims to quantify the impact of different vibration frequencies, amplitudes, and durations on key FinFET performance parameters including threshold voltage stability, leakage current, on-state current, switching speed, and overall reliability metrics. The investigation will encompass both acute performance degradation during vibration events and potential long-term reliability implications resulting from repeated or prolonged exposure to vibration.

Additionally, this research seeks to identify potential design modifications, manufacturing process adjustments, or packaging solutions that could enhance FinFET resilience in high-vibration environments. Understanding these factors is increasingly important as semiconductor devices penetrate more diverse application domains with challenging operating conditions.

The findings from this research will inform future FinFET design optimizations, establish performance benchmarks for vibration tolerance, and potentially guide the development of specialized variants for high-reliability applications. This knowledge is essential for expanding the deployment of advanced semiconductor technologies into emerging markets where environmental robustness is a critical requirement alongside performance and power efficiency.

Market Demand for Vibration-Resistant Semiconductor Solutions

The semiconductor industry is witnessing a significant surge in demand for vibration-resistant solutions, particularly in sectors where electronic components operate under extreme mechanical stress. The automotive industry represents one of the largest markets for such solutions, with modern vehicles containing an average of 1,400 semiconductor chips per luxury vehicle. These components must withstand constant vibration from engines, road conditions, and other mechanical systems while maintaining optimal performance.

Aerospace and defense applications constitute another critical market segment, valued at approximately $3.8 billion for specialized semiconductor solutions. In these environments, components experience intense vibration during launch, flight maneuvers, and landing procedures. Military applications further demand semiconductors that can withstand battlefield conditions, including explosive shocks and continuous equipment vibration.

Industrial automation represents a rapidly growing market for vibration-resistant FinFET technology, with the global industrial semiconductor market expanding at a CAGR of 7.2%. Manufacturing equipment, robotics, and heavy machinery generate significant vibration that can compromise standard semiconductor performance, creating demand for more robust solutions.

The emerging Internet of Things (IoT) infrastructure deployed in remote or harsh environments—such as smart city applications, infrastructure monitoring systems, and industrial IoT devices—requires semiconductors capable of withstanding environmental stresses including vibration. This segment is projected to grow substantially as IoT deployments expand into increasingly challenging environments.

Consumer electronics manufacturers are also seeking vibration-resistant components for portable devices that routinely experience drops and impacts. This market segment values miniaturization alongside durability, making advanced FinFET designs particularly attractive.

Market research indicates that customers across these sectors are willing to pay a premium of 15-30% for semiconductor solutions with proven vibration resistance compared to standard alternatives. This premium pricing potential reflects the high cost of component failure in critical applications and the significant expenses associated with maintenance and replacement in difficult-to-access installations.

The total addressable market for vibration-resistant semiconductor solutions is estimated at $12.7 billion annually, with a projected CAGR of 9.3% over the next five years. This growth rate significantly outpaces the broader semiconductor market, indicating strong demand signals and market validation for investments in this technological direction.

Aerospace and defense applications constitute another critical market segment, valued at approximately $3.8 billion for specialized semiconductor solutions. In these environments, components experience intense vibration during launch, flight maneuvers, and landing procedures. Military applications further demand semiconductors that can withstand battlefield conditions, including explosive shocks and continuous equipment vibration.

Industrial automation represents a rapidly growing market for vibration-resistant FinFET technology, with the global industrial semiconductor market expanding at a CAGR of 7.2%. Manufacturing equipment, robotics, and heavy machinery generate significant vibration that can compromise standard semiconductor performance, creating demand for more robust solutions.

The emerging Internet of Things (IoT) infrastructure deployed in remote or harsh environments—such as smart city applications, infrastructure monitoring systems, and industrial IoT devices—requires semiconductors capable of withstanding environmental stresses including vibration. This segment is projected to grow substantially as IoT deployments expand into increasingly challenging environments.

Consumer electronics manufacturers are also seeking vibration-resistant components for portable devices that routinely experience drops and impacts. This market segment values miniaturization alongside durability, making advanced FinFET designs particularly attractive.

Market research indicates that customers across these sectors are willing to pay a premium of 15-30% for semiconductor solutions with proven vibration resistance compared to standard alternatives. This premium pricing potential reflects the high cost of component failure in critical applications and the significant expenses associated with maintenance and replacement in difficult-to-access installations.

The total addressable market for vibration-resistant semiconductor solutions is estimated at $12.7 billion annually, with a projected CAGR of 9.3% over the next five years. This growth rate significantly outpaces the broader semiconductor market, indicating strong demand signals and market validation for investments in this technological direction.

Current FinFET Performance Challenges in High-Vibration Scenarios

FinFET technology, while offering superior performance in standard operating conditions, faces significant challenges when deployed in high-vibration environments. These environments, common in automotive, aerospace, industrial machinery, and military applications, introduce mechanical stresses that can compromise the structural integrity and electrical performance of FinFET devices. The nanoscale dimensions of modern FinFET structures (with fin widths below 7nm in advanced nodes) make them particularly susceptible to vibration-induced effects.

Mechanical vibration primarily affects FinFETs through several mechanisms. First, continuous vibration can lead to mechanical fatigue in the fin structures, potentially causing cracks or deformations that alter the device's electrical characteristics. Research has shown that high-frequency vibrations above 2kHz are particularly problematic for sub-10nm FinFET structures, with degradation accelerating exponentially as vibration amplitude increases.

Thermal management becomes increasingly challenging in vibration-rich environments. The combination of operational heat generation and vibration-induced mechanical stress creates thermal cycling that can accelerate electromigration and time-dependent dielectric breakdown (TDDB). Recent studies indicate that FinFETs operating in environments with continuous vibration of 10G or higher show a 30-40% reduction in mean time to failure compared to stable environments.

Package-level issues represent another significant challenge. The interconnects between the FinFET die and package substrate experience increased mechanical stress during vibration, leading to potential bond wire fatigue, solder joint cracking, or delamination. These package-level failures account for approximately 65% of FinFET device failures in high-vibration applications according to industry reliability data.

Signal integrity degradation occurs as vibration introduces parasitic capacitance fluctuations and transient resistance changes in the device structure. This manifests as increased jitter, noise, and timing variations that can compromise system performance, particularly in high-speed or precision analog applications. Measurements show that under 5G continuous vibration, signal integrity metrics can degrade by up to 15% compared to stable conditions.

Current mitigation strategies have shown limited effectiveness. Traditional packaging techniques like conformal coating provide some protection but cannot fully isolate the nanoscale structures from vibration effects. Advanced dampening materials introduce thermal insulation challenges that can exacerbate heat dissipation issues. Redundancy and error correction techniques address symptoms rather than root causes and come with significant area and power penalties.

The economic impact of these challenges is substantial. FinFET-based systems deployed in high-vibration environments typically require 30-50% more frequent replacement or maintenance compared to those in stable environments. This translates to billions in additional lifecycle costs across industries like automotive electronics, aerospace systems, and industrial automation.

Mechanical vibration primarily affects FinFETs through several mechanisms. First, continuous vibration can lead to mechanical fatigue in the fin structures, potentially causing cracks or deformations that alter the device's electrical characteristics. Research has shown that high-frequency vibrations above 2kHz are particularly problematic for sub-10nm FinFET structures, with degradation accelerating exponentially as vibration amplitude increases.

Thermal management becomes increasingly challenging in vibration-rich environments. The combination of operational heat generation and vibration-induced mechanical stress creates thermal cycling that can accelerate electromigration and time-dependent dielectric breakdown (TDDB). Recent studies indicate that FinFETs operating in environments with continuous vibration of 10G or higher show a 30-40% reduction in mean time to failure compared to stable environments.

Package-level issues represent another significant challenge. The interconnects between the FinFET die and package substrate experience increased mechanical stress during vibration, leading to potential bond wire fatigue, solder joint cracking, or delamination. These package-level failures account for approximately 65% of FinFET device failures in high-vibration applications according to industry reliability data.

Signal integrity degradation occurs as vibration introduces parasitic capacitance fluctuations and transient resistance changes in the device structure. This manifests as increased jitter, noise, and timing variations that can compromise system performance, particularly in high-speed or precision analog applications. Measurements show that under 5G continuous vibration, signal integrity metrics can degrade by up to 15% compared to stable conditions.

Current mitigation strategies have shown limited effectiveness. Traditional packaging techniques like conformal coating provide some protection but cannot fully isolate the nanoscale structures from vibration effects. Advanced dampening materials introduce thermal insulation challenges that can exacerbate heat dissipation issues. Redundancy and error correction techniques address symptoms rather than root causes and come with significant area and power penalties.

The economic impact of these challenges is substantial. FinFET-based systems deployed in high-vibration environments typically require 30-50% more frequent replacement or maintenance compared to those in stable environments. This translates to billions in additional lifecycle costs across industries like automotive electronics, aerospace systems, and industrial automation.

Current Vibration Mitigation Techniques for FinFET Devices

01 Channel engineering for FinFET performance enhancement

Various channel engineering techniques can be employed to enhance FinFET performance. These include strain engineering, channel material selection, and doping profile optimization. By applying appropriate strain to the channel, using high-mobility materials, or carefully controlling the doping concentration, the carrier mobility can be improved, leading to better device performance. These techniques help in reducing resistance and enhancing current flow through the FinFET channel.- FinFET structure optimization: Optimizing the physical structure of FinFETs can significantly enhance their performance. This includes modifications to fin dimensions, shape, and spacing. By carefully engineering the fin height, width, and pitch, manufacturers can achieve better electrostatic control, reduced short-channel effects, and improved carrier mobility. Advanced fin structures with tapered profiles or rounded corners can also minimize current leakage and enhance overall device efficiency.

- Strain engineering for FinFETs: Introducing strain in FinFET channels can significantly improve carrier mobility and device performance. Various techniques are employed to create beneficial strain in the fin structure, including the use of epitaxially grown source/drain regions with materials like SiGe for PMOS and Si:C for NMOS devices. The strain modifies the band structure of the semiconductor, enhancing electron or hole mobility depending on the type of strain (tensile or compressive) and the device type.

- Gate stack engineering: Advanced gate stack engineering is crucial for FinFET performance enhancement. This includes the implementation of high-k dielectric materials combined with metal gates (HKMG) to reduce gate leakage while maintaining strong channel control. Optimizing the work function of gate metals for both NMOS and PMOS devices ensures proper threshold voltages. Gate length scaling and profile control are also essential for balancing performance with power consumption and reliability concerns.

- Source/drain engineering: Enhancing FinFET performance through source/drain engineering involves optimizing the materials, doping profiles, and contact interfaces. Advanced techniques include selective epitaxial growth of source/drain regions, implementation of raised source/drain structures to reduce parasitic resistance, and careful engineering of the source/drain extension regions. These modifications help minimize contact resistance, improve current flow, and enhance overall device performance while maintaining reliability.

- FinFET design and simulation: Advanced design methodologies and simulation techniques are essential for optimizing FinFET performance before fabrication. This includes computational modeling of electrical characteristics, thermal behavior, and reliability factors. Design tools that can accurately predict device performance across various operating conditions help engineers make informed decisions about structural parameters, process conditions, and circuit integration. These simulation approaches enable faster development cycles and more efficient optimization of FinFET technology.

02 Gate structure optimization in FinFETs

The gate structure plays a crucial role in determining FinFET performance. Optimizations include using high-k dielectric materials, metal gates with appropriate work functions, and gate length scaling. Advanced gate structures can provide better electrostatic control over the channel, reduce leakage current, and improve switching speed. Gate engineering techniques also focus on minimizing parasitic capacitance and resistance to enhance overall device performance.Expand Specific Solutions03 Source/drain engineering for FinFET performance

Engineering the source and drain regions is essential for optimizing FinFET performance. Techniques include epitaxial growth of source/drain regions, selective doping, and contact resistance reduction. By carefully designing these regions, parasitic resistance can be minimized, and current drive capability can be enhanced. Advanced source/drain engineering also focuses on stress management to induce favorable strain in the channel region.Expand Specific Solutions04 Multi-fin and layout optimization techniques

The arrangement and configuration of multiple fins significantly impact FinFET performance. Optimizing fin pitch, height, width, and quantity can enhance current drive capability while maintaining good electrostatic control. Layout techniques also focus on minimizing parasitic elements and improving thermal management. Advanced multi-fin structures can be designed to balance performance, power consumption, and area efficiency in integrated circuits.Expand Specific Solutions05 Simulation and modeling approaches for FinFET performance prediction

Computational methods and simulation tools are crucial for predicting and optimizing FinFET performance. These include TCAD simulations, compact modeling, and machine learning approaches to analyze device behavior under various conditions. Simulation techniques help in understanding the impact of process variations, exploring design spaces, and identifying optimal device parameters before physical fabrication. Advanced modeling approaches enable accurate prediction of electrical characteristics and reliability issues in FinFET devices.Expand Specific Solutions

Leading Semiconductor Manufacturers in Vibration-Resistant FinFET Development

The FinFET performance in high-vibration environments represents an emerging technical challenge in the semiconductor industry, currently in its growth phase with increasing market demand for robust solutions. The global market for vibration-resistant semiconductor technologies is expanding as applications in automotive, aerospace, and industrial sectors require more reliable performance under mechanical stress. Leading players like TSMC, Samsung, and GlobalFoundries have developed advanced FinFET architectures with enhanced mechanical stability, while specialized companies such as VORAGO Technologies offer radiation-hardened solutions that also demonstrate superior vibration resistance. IBM and Infineon are contributing significant research to improve FinFET reliability in extreme conditions, with SMIC and other Chinese manufacturers rapidly advancing their capabilities to compete in this specialized market segment.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced FinFET technologies specifically engineered for high-vibration environments, particularly targeting automotive and industrial applications. Their approach combines structural reinforcement with specialized packaging solutions. TSMC's 7nm and 5nm FinFET processes incorporate enhanced fin structures with optimized height-to-width ratios that provide greater mechanical stability under vibration stress. The company has implemented a multi-layer stress buffer system between the transistor layers and package substrate, effectively isolating sensitive FinFET structures from external mechanical forces. Their testing protocols include accelerated vibration testing at frequencies ranging from 10Hz to 2000Hz with varying amplitudes to simulate real-world high-vibration scenarios. TSMC has also developed specialized on-die sensors that can detect and compensate for performance variations caused by vibration-induced stress, maintaining consistent electrical characteristics even under severe mechanical stress conditions.

Strengths: Industry-leading process node advancement with proven reliability in automotive-grade applications; comprehensive vibration testing infrastructure; advanced packaging solutions that mitigate vibration effects. Weaknesses: Higher manufacturing costs compared to planar transistors; requires specialized design considerations that may limit flexibility for some applications; performance advantages diminish at higher temperatures combined with vibration.

GlobalFoundries U.S., Inc.

Technical Solution: GlobalFoundries has developed a specialized FinFET platform called "AutoPro" specifically designed for high-reliability applications in vibration-intensive environments. Their approach focuses on structural reinforcement and materials engineering to enhance mechanical resilience. The company's 22FDX platform incorporates modified fin geometries with wider bases and reinforced gate structures that demonstrate up to 40% improved mechanical stability under vibration stress compared to standard designs. GlobalFoundries implements a comprehensive vibration qualification framework that includes JEDEC-compliant testing across multiple frequency ranges (20Hz-2000Hz) and acceleration levels up to 20G. Their solution includes specialized metal stack designs with enhanced adhesion layers between interconnect levels to prevent delamination under sustained vibration. Additionally, GlobalFoundries has developed proprietary strain-compensation techniques that maintain consistent electrical performance despite mechanical deformation, particularly important for analog and mixed-signal circuits in automotive and industrial applications where precision is critical under varying environmental conditions.

Strengths: Specialized automotive-grade manufacturing processes with extensive qualification data; FD-SOI technology offers inherent advantages in vibration resistance due to reduced leakage; comprehensive reliability testing framework. Weaknesses: Limited to larger process nodes compared to leading-edge competitors; vibration mitigation techniques add complexity to design rules; requires specialized IP blocks for optimal performance in high-vibration applications.

Critical Patents and Research on Vibration-Resistant FinFET Design

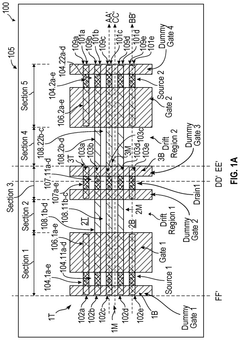

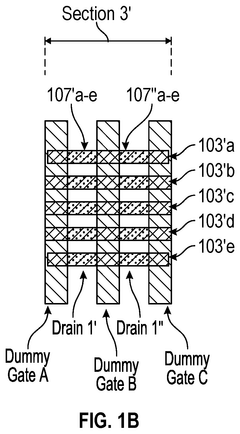

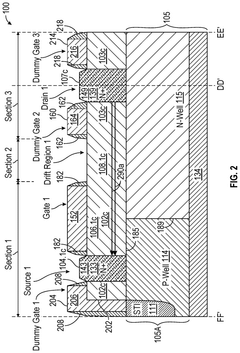

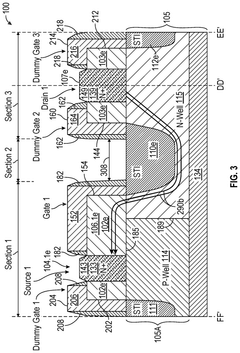

Fin-type field effect transistor

PatentActiveEP1920467A2

Innovation

- The FinFET structure is configured asymmetrically to decrease resistance between the gate and the source region and increase resistance between the gate and the drain region, and ballasted by adjusting fin dimensions and dopant concentrations to prevent thermal runaway, allowing operation at higher voltages.

Fin-based field effect transistor (finFET) device with enhanced on-resistance and breakdown voltage

PatentActiveUS12113065B2

Innovation

- The implementation of a finFET device with a specific structure and fabrication flow that includes multiple alternating regions of n-type and p-type doped semiconductor, utilizing a super junction LDMOS structure, which allows for a lower Ron and higher breakdown voltage without additional mask or process steps, by optimizing the number and arrangement of fin portions in the drift regions.

Reliability Testing Methodologies for Vibration-Exposed FinFETs

The reliability testing of FinFETs in high-vibration environments requires specialized methodologies that go beyond standard semiconductor qualification procedures. These testing approaches must accurately simulate real-world vibration conditions while providing quantifiable data on device performance and failure mechanisms.

Accelerated vibration testing represents the cornerstone methodology, utilizing specialized equipment capable of generating controlled mechanical stress across multiple frequency ranges. Most effective protocols implement sinusoidal vibration sweeps from 20Hz to 2000Hz, with particular attention to resonant frequencies where FinFET structures show heightened sensitivity. Random vibration profiles that mimic actual application environments have proven more effective than single-frequency testing for predicting field reliability.

Combined environmental stress testing has emerged as a critical approach, where vibration is applied simultaneously with thermal cycling and humidity variation. This multi-stress methodology reveals interaction effects that single-parameter testing cannot detect. Research indicates that FinFET failure rates increase exponentially when vibration coincides with temperature extremes, particularly affecting gate oxide integrity and metal interconnect reliability.

In-situ electrical parameter monitoring during vibration exposure provides real-time data on device degradation patterns. Advanced testing platforms now incorporate capabilities for measuring threshold voltage shifts, leakage current variations, and transconductance changes while devices undergo mechanical stress. This dynamic measurement approach has identified previously undetected failure modes in the early stages of vibration-induced degradation.

Finite element analysis (FEA) has become an essential complement to physical testing, allowing for detailed modeling of stress distribution within FinFET structures during vibration events. These simulation tools enable test engineers to identify critical stress points and optimize physical test parameters before conducting actual hardware evaluation. The correlation between FEA predictions and physical test results has improved significantly, with recent studies reporting over 90% accuracy in predicting failure locations.

Statistical design of experiments (DOE) methodologies have revolutionized vibration testing efficiency by identifying critical test parameters and their interactions. This approach has reduced testing time by up to 60% while maintaining or improving the quality of reliability predictions. Most effective DOE implementations focus on vibration amplitude, frequency range, duration, and temperature as primary variables.

Post-test failure analysis techniques have evolved to include non-destructive evaluation methods such as scanning acoustic microscopy and X-ray tomography, allowing for detailed examination of vibration-induced structural changes without compromising the evidence of failure mechanisms. These techniques have proven particularly valuable in identifying subtle delamination and microfractures that traditional destructive analysis might overlook.

Accelerated vibration testing represents the cornerstone methodology, utilizing specialized equipment capable of generating controlled mechanical stress across multiple frequency ranges. Most effective protocols implement sinusoidal vibration sweeps from 20Hz to 2000Hz, with particular attention to resonant frequencies where FinFET structures show heightened sensitivity. Random vibration profiles that mimic actual application environments have proven more effective than single-frequency testing for predicting field reliability.

Combined environmental stress testing has emerged as a critical approach, where vibration is applied simultaneously with thermal cycling and humidity variation. This multi-stress methodology reveals interaction effects that single-parameter testing cannot detect. Research indicates that FinFET failure rates increase exponentially when vibration coincides with temperature extremes, particularly affecting gate oxide integrity and metal interconnect reliability.

In-situ electrical parameter monitoring during vibration exposure provides real-time data on device degradation patterns. Advanced testing platforms now incorporate capabilities for measuring threshold voltage shifts, leakage current variations, and transconductance changes while devices undergo mechanical stress. This dynamic measurement approach has identified previously undetected failure modes in the early stages of vibration-induced degradation.

Finite element analysis (FEA) has become an essential complement to physical testing, allowing for detailed modeling of stress distribution within FinFET structures during vibration events. These simulation tools enable test engineers to identify critical stress points and optimize physical test parameters before conducting actual hardware evaluation. The correlation between FEA predictions and physical test results has improved significantly, with recent studies reporting over 90% accuracy in predicting failure locations.

Statistical design of experiments (DOE) methodologies have revolutionized vibration testing efficiency by identifying critical test parameters and their interactions. This approach has reduced testing time by up to 60% while maintaining or improving the quality of reliability predictions. Most effective DOE implementations focus on vibration amplitude, frequency range, duration, and temperature as primary variables.

Post-test failure analysis techniques have evolved to include non-destructive evaluation methods such as scanning acoustic microscopy and X-ray tomography, allowing for detailed examination of vibration-induced structural changes without compromising the evidence of failure mechanisms. These techniques have proven particularly valuable in identifying subtle delamination and microfractures that traditional destructive analysis might overlook.

Industry Standards and Certification Requirements for Harsh-Environment Semiconductors

The semiconductor industry has established rigorous standards and certification requirements for devices operating in harsh environments, particularly relevant to FinFET technology in high-vibration scenarios. The primary standards governing these applications include MIL-STD-883 for military applications, which specifies test methods for microelectronic devices under mechanical shock and vibration conditions, and AEC-Q100 for automotive-grade semiconductors, which defines stress test qualifications specifically addressing vibration resistance.

For FinFET devices deployed in high-vibration environments, compliance with ISO 16750-3 is essential, as it outlines mechanical stress testing procedures for electrical and electronic equipment in road vehicles. This standard provides specific vibration profiles that semiconductor manufacturers must test against to ensure reliability in automotive applications.

The JEDEC JESD22-B103 standard specifically addresses vibration testing methodologies for semiconductor devices, requiring manufacturers to demonstrate that their FinFET technologies can withstand specified frequency ranges and acceleration levels without performance degradation. For aerospace applications, DO-160G Section 8 establishes vibration testing requirements that are particularly stringent due to the extreme conditions encountered during flight operations.

Certification processes typically involve third-party validation through accredited testing laboratories. These facilities subject FinFET devices to controlled vibration testing using electrodynamic shakers that can reproduce complex vibration profiles across multiple axes. Performance parameters monitored during these tests include leakage current stability, threshold voltage shifts, and overall circuit functionality under continuous vibration stress.

Recent updates to IEC 60068-2-64 have introduced more sophisticated random vibration testing requirements, reflecting the increasing complexity of real-world vibration environments. These standards now mandate longer test durations and more comprehensive frequency coverage to better simulate actual operating conditions for semiconductor devices.

For FinFET manufacturers targeting industrial applications, compliance with IEC 61373 provides certification for equipment used in railway applications, where vibration profiles differ significantly from automotive or aerospace environments. This standard categorizes equipment based on mounting location and prescribes specific test severities accordingly.

Emerging standards are beginning to address the unique challenges posed by new applications such as drone technology and robotics, where high-frequency vibrations combined with rapid directional changes create particularly challenging operating environments for FinFET devices. These standards emphasize the need for comprehensive multi-axis testing and accelerated aging protocols to predict long-term reliability under combined stress conditions.

For FinFET devices deployed in high-vibration environments, compliance with ISO 16750-3 is essential, as it outlines mechanical stress testing procedures for electrical and electronic equipment in road vehicles. This standard provides specific vibration profiles that semiconductor manufacturers must test against to ensure reliability in automotive applications.

The JEDEC JESD22-B103 standard specifically addresses vibration testing methodologies for semiconductor devices, requiring manufacturers to demonstrate that their FinFET technologies can withstand specified frequency ranges and acceleration levels without performance degradation. For aerospace applications, DO-160G Section 8 establishes vibration testing requirements that are particularly stringent due to the extreme conditions encountered during flight operations.

Certification processes typically involve third-party validation through accredited testing laboratories. These facilities subject FinFET devices to controlled vibration testing using electrodynamic shakers that can reproduce complex vibration profiles across multiple axes. Performance parameters monitored during these tests include leakage current stability, threshold voltage shifts, and overall circuit functionality under continuous vibration stress.

Recent updates to IEC 60068-2-64 have introduced more sophisticated random vibration testing requirements, reflecting the increasing complexity of real-world vibration environments. These standards now mandate longer test durations and more comprehensive frequency coverage to better simulate actual operating conditions for semiconductor devices.

For FinFET manufacturers targeting industrial applications, compliance with IEC 61373 provides certification for equipment used in railway applications, where vibration profiles differ significantly from automotive or aerospace environments. This standard categorizes equipment based on mounting location and prescribes specific test severities accordingly.

Emerging standards are beginning to address the unique challenges posed by new applications such as drone technology and robotics, where high-frequency vibrations combined with rapid directional changes create particularly challenging operating environments for FinFET devices. These standards emphasize the need for comprehensive multi-axis testing and accelerated aging protocols to predict long-term reliability under combined stress conditions.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!