FinFET Vs DGFET: Understanding Conductivity Ranges

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET and DGFET Technology Evolution

The evolution of transistor technology has witnessed significant advancements over the decades, with the transition from planar MOSFETs to three-dimensional architectures marking a revolutionary shift in semiconductor design. FinFET technology emerged in the early 2000s as a response to the scaling limitations of traditional planar transistors, with Intel's introduction of Tri-Gate transistors in 2011 representing a major commercial milestone.

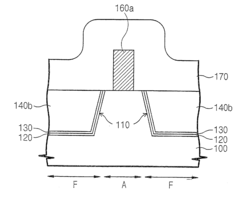

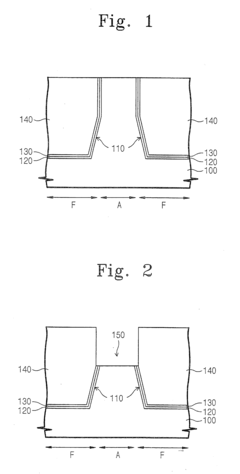

FinFET structures feature a fin-like silicon body that extends vertically from the substrate, allowing the gate to wrap around three sides of the channel. This multi-gate configuration significantly improved electrostatic control over the channel, reducing short-channel effects and leakage currents that had become problematic at sub-28nm nodes.

The technological progression continued with the development of Double-Gate Field Effect Transistors (DGFETs), which represent a further evolution in transistor architecture. Unlike FinFETs where the gate wraps around three sides of the fin, DGFETs feature gate structures on two opposite sides of the channel. This configuration offers potentially superior electrostatic control and current drive capabilities under certain design parameters.

From a conductivity perspective, the evolution from FinFET to DGFET has been characterized by increasingly precise control over carrier transport. FinFETs typically demonstrate effective carrier mobility in the range of 200-400 cm²/V·s for electrons in silicon channels, while advanced DGFET designs have pushed these boundaries further, with some experimental structures achieving mobility values exceeding 500 cm²/V·s through strain engineering and channel material innovations.

The dimensional scaling has been equally impressive, with FinFET technology progressing from initial 22nm implementations to current 5nm nodes. DGFETs are being explored for even more aggressive scaling, potentially enabling functional transistors at 3nm and below. This dimensional reduction correlates directly with improvements in switching speed and power efficiency.

Manufacturing techniques have evolved in parallel, with advanced lithography methods such as extreme ultraviolet (EUV) becoming essential for defining the intricate features of these transistor architectures. The industry has also witnessed innovations in deposition and etching processes specifically tailored for three-dimensional structures, enabling the precise formation of high-aspect-ratio fins and gates.

Material science advancements have played a crucial role in this evolution, with the introduction of high-k dielectrics, metal gates, and strained silicon enhancing the performance characteristics of both FinFET and DGFET technologies. More recently, research has focused on incorporating novel channel materials such as germanium, III-V compounds, and two-dimensional materials to further extend the performance envelope of these transistor architectures.

FinFET structures feature a fin-like silicon body that extends vertically from the substrate, allowing the gate to wrap around three sides of the channel. This multi-gate configuration significantly improved electrostatic control over the channel, reducing short-channel effects and leakage currents that had become problematic at sub-28nm nodes.

The technological progression continued with the development of Double-Gate Field Effect Transistors (DGFETs), which represent a further evolution in transistor architecture. Unlike FinFETs where the gate wraps around three sides of the fin, DGFETs feature gate structures on two opposite sides of the channel. This configuration offers potentially superior electrostatic control and current drive capabilities under certain design parameters.

From a conductivity perspective, the evolution from FinFET to DGFET has been characterized by increasingly precise control over carrier transport. FinFETs typically demonstrate effective carrier mobility in the range of 200-400 cm²/V·s for electrons in silicon channels, while advanced DGFET designs have pushed these boundaries further, with some experimental structures achieving mobility values exceeding 500 cm²/V·s through strain engineering and channel material innovations.

The dimensional scaling has been equally impressive, with FinFET technology progressing from initial 22nm implementations to current 5nm nodes. DGFETs are being explored for even more aggressive scaling, potentially enabling functional transistors at 3nm and below. This dimensional reduction correlates directly with improvements in switching speed and power efficiency.

Manufacturing techniques have evolved in parallel, with advanced lithography methods such as extreme ultraviolet (EUV) becoming essential for defining the intricate features of these transistor architectures. The industry has also witnessed innovations in deposition and etching processes specifically tailored for three-dimensional structures, enabling the precise formation of high-aspect-ratio fins and gates.

Material science advancements have played a crucial role in this evolution, with the introduction of high-k dielectrics, metal gates, and strained silicon enhancing the performance characteristics of both FinFET and DGFET technologies. More recently, research has focused on incorporating novel channel materials such as germanium, III-V compounds, and two-dimensional materials to further extend the performance envelope of these transistor architectures.

Market Demand Analysis for Advanced Transistor Technologies

The semiconductor industry is witnessing a significant shift toward advanced transistor architectures, driven by the increasing demand for higher performance, lower power consumption, and smaller form factors in electronic devices. Market analysis reveals that the transition from planar transistors to three-dimensional structures like FinFETs has been accelerated by the limitations of traditional MOSFET technology at sub-22nm nodes. Currently, the global market for FinFET technology is valued at approximately $35 billion and is projected to grow at a CAGR of 22% through 2028.

The primary market drivers for advanced transistor technologies like FinFET and DGFET (Double-Gate FET) include the explosive growth in data centers, artificial intelligence applications, and high-performance computing. These applications require transistors with superior conductivity ranges to manage increasing computational demands while maintaining energy efficiency. Market research indicates that data center operators are willing to pay premium prices for chips that deliver 15-20% better performance-per-watt metrics, directly influencing semiconductor manufacturers' R&D priorities.

Consumer electronics represents another substantial market segment, with smartphone manufacturers particularly interested in transistor technologies that can extend battery life while supporting advanced features. The mobile processor market, valued at $21 billion, is expected to be an early adopter of DGFET technology once it reaches commercial viability, due to its potential for better electrostatic control and reduced leakage current compared to FinFETs.

Automotive and industrial IoT sectors are emerging as significant growth areas for advanced transistor technologies. The automotive semiconductor market is growing at 11% annually, with increasing demand for chips that can operate reliably across wider conductivity ranges and temperature conditions. DGFET's theoretical advantages in these parameters position it favorably for these applications once manufacturing challenges are overcome.

Regional market analysis shows Asia-Pacific dominating manufacturing capacity for advanced transistors, with Taiwan, South Korea, and increasingly China investing heavily in fabrication capabilities. North America leads in design innovation, while Europe focuses on specialized applications in automotive and industrial sectors. This geographic distribution influences technology adoption patterns and investment flows in the FinFET vs. DGFET development race.

Market forecasts suggest that while FinFET technology will remain dominant through 2025, DGFET and other advanced architectures will begin gaining significant market share thereafter, particularly in premium segments where performance advantages justify higher production costs. The transition timeline will be influenced by manufacturing yield improvements and the industry's ability to scale DGFET production economically.

The primary market drivers for advanced transistor technologies like FinFET and DGFET (Double-Gate FET) include the explosive growth in data centers, artificial intelligence applications, and high-performance computing. These applications require transistors with superior conductivity ranges to manage increasing computational demands while maintaining energy efficiency. Market research indicates that data center operators are willing to pay premium prices for chips that deliver 15-20% better performance-per-watt metrics, directly influencing semiconductor manufacturers' R&D priorities.

Consumer electronics represents another substantial market segment, with smartphone manufacturers particularly interested in transistor technologies that can extend battery life while supporting advanced features. The mobile processor market, valued at $21 billion, is expected to be an early adopter of DGFET technology once it reaches commercial viability, due to its potential for better electrostatic control and reduced leakage current compared to FinFETs.

Automotive and industrial IoT sectors are emerging as significant growth areas for advanced transistor technologies. The automotive semiconductor market is growing at 11% annually, with increasing demand for chips that can operate reliably across wider conductivity ranges and temperature conditions. DGFET's theoretical advantages in these parameters position it favorably for these applications once manufacturing challenges are overcome.

Regional market analysis shows Asia-Pacific dominating manufacturing capacity for advanced transistors, with Taiwan, South Korea, and increasingly China investing heavily in fabrication capabilities. North America leads in design innovation, while Europe focuses on specialized applications in automotive and industrial sectors. This geographic distribution influences technology adoption patterns and investment flows in the FinFET vs. DGFET development race.

Market forecasts suggest that while FinFET technology will remain dominant through 2025, DGFET and other advanced architectures will begin gaining significant market share thereafter, particularly in premium segments where performance advantages justify higher production costs. The transition timeline will be influenced by manufacturing yield improvements and the industry's ability to scale DGFET production economically.

Current Conductivity Challenges in Nanoscale Transistors

As transistor dimensions continue to shrink below 10nm, conventional planar MOSFET architectures face severe short-channel effects that significantly degrade device performance. These effects include drain-induced barrier lowering (DIBL), threshold voltage roll-off, and increased leakage currents, all of which compromise the electrostatic integrity of the transistor. The semiconductor industry has responded by developing multi-gate architectures, with FinFET technology currently dominating commercial production and Double-Gate FET (DGFET) emerging as a promising alternative.

The primary conductivity challenge in nanoscale transistors stems from quantum mechanical effects that become increasingly prominent at these dimensions. Electron tunneling through thin gate oxides leads to gate leakage currents, while direct source-to-drain tunneling occurs when the channel length approaches the electron's de Broglie wavelength. These quantum effects fundamentally limit the minimum achievable off-state current and consequently the on/off current ratio, which is critical for digital applications.

Surface scattering represents another significant challenge, particularly in FinFET structures where the conducting channel forms along multiple surfaces. As the surface-to-volume ratio increases in nanoscale devices, carrier mobility becomes increasingly dominated by surface roughness scattering, phonon scattering, and remote Coulomb scattering from gate stack charges. These mechanisms collectively reduce carrier mobility and limit the maximum achievable on-state current.

Variability presents a formidable challenge at nanoscale dimensions. Random dopant fluctuations, line edge roughness, and metal grain variability in gate electrodes introduce significant device-to-device performance variations. In FinFETs, fin width fluctuations directly impact threshold voltage and drive current, while in DGFETs, gate alignment precision becomes critical for symmetric operation of both gates.

Heat dissipation emerges as a critical limitation as device dimensions shrink. The power density in modern nanoscale transistors approaches 100 W/cm², creating localized hotspots that can degrade performance through reduced carrier mobility and increased leakage currents. This thermal challenge is particularly acute in 3D architectures like FinFETs, where the fin geometry restricts efficient heat dissipation pathways.

Contact resistance has become a dominant component of the total device resistance in sub-10nm nodes. As the channel resistance decreases with scaling, the parasitic resistances at source/drain contacts become proportionally more significant. This issue is more pronounced in FinFETs due to their 3D geometry, which complicates the formation of low-resistance contacts compared to the potentially simpler contact scheme possible with planar DGFETs.

These conductivity challenges collectively define the performance envelope within which FinFET and DGFET technologies must operate, driving research toward novel materials, innovative gate stack engineering, and alternative device architectures to extend CMOS scaling beyond current limitations.

The primary conductivity challenge in nanoscale transistors stems from quantum mechanical effects that become increasingly prominent at these dimensions. Electron tunneling through thin gate oxides leads to gate leakage currents, while direct source-to-drain tunneling occurs when the channel length approaches the electron's de Broglie wavelength. These quantum effects fundamentally limit the minimum achievable off-state current and consequently the on/off current ratio, which is critical for digital applications.

Surface scattering represents another significant challenge, particularly in FinFET structures where the conducting channel forms along multiple surfaces. As the surface-to-volume ratio increases in nanoscale devices, carrier mobility becomes increasingly dominated by surface roughness scattering, phonon scattering, and remote Coulomb scattering from gate stack charges. These mechanisms collectively reduce carrier mobility and limit the maximum achievable on-state current.

Variability presents a formidable challenge at nanoscale dimensions. Random dopant fluctuations, line edge roughness, and metal grain variability in gate electrodes introduce significant device-to-device performance variations. In FinFETs, fin width fluctuations directly impact threshold voltage and drive current, while in DGFETs, gate alignment precision becomes critical for symmetric operation of both gates.

Heat dissipation emerges as a critical limitation as device dimensions shrink. The power density in modern nanoscale transistors approaches 100 W/cm², creating localized hotspots that can degrade performance through reduced carrier mobility and increased leakage currents. This thermal challenge is particularly acute in 3D architectures like FinFETs, where the fin geometry restricts efficient heat dissipation pathways.

Contact resistance has become a dominant component of the total device resistance in sub-10nm nodes. As the channel resistance decreases with scaling, the parasitic resistances at source/drain contacts become proportionally more significant. This issue is more pronounced in FinFETs due to their 3D geometry, which complicates the formation of low-resistance contacts compared to the potentially simpler contact scheme possible with planar DGFETs.

These conductivity challenges collectively define the performance envelope within which FinFET and DGFET technologies must operate, driving research toward novel materials, innovative gate stack engineering, and alternative device architectures to extend CMOS scaling beyond current limitations.

Comparative Analysis of FinFET vs DGFET Conductivity Solutions

01 Structure and design of FinFET and DGFET for enhanced conductivity

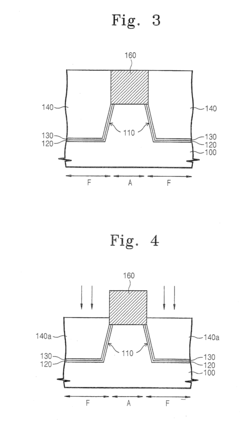

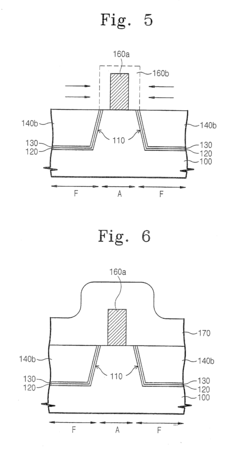

The physical structure and design parameters of FinFET and DGFET transistors significantly impact their conductivity. These transistors utilize a three-dimensional fin structure that allows for better electrostatic control of the channel, reducing short-channel effects and improving current flow. The gate wraps around multiple surfaces of the fin, providing enhanced control over carrier movement and increasing conductivity. Design considerations such as fin height, width, and gate length are critical for optimizing the conductivity performance of these transistors.- Structure and design of FinFET and DGFET for enhanced conductivity: The structural design of FinFET and DGFET transistors significantly impacts their conductivity. These transistors feature multiple gates that provide better control over the channel, reducing short-channel effects and improving current flow. The fin height, width, and gate length are critical parameters that affect the conductivity. Advanced designs incorporate optimized fin shapes and gate configurations to enhance carrier mobility and overall conductivity performance.

- Doping techniques to improve conductivity in multi-gate transistors: Various doping techniques are employed to enhance the conductivity of FinFET and DGFET transistors. These include selective doping of source/drain regions, channel doping profiles, and the use of different dopant types and concentrations. Advanced methods such as in-situ doping during epitaxial growth and pulse doping can be implemented to optimize carrier concentration and mobility, thereby improving the overall conductivity of these multi-gate transistor structures.

- Material selection for improved conductivity in FinFET and DGFET: The choice of materials significantly affects the conductivity of FinFET and DGFET transistors. High-mobility channel materials such as strained silicon, silicon-germanium alloys, and III-V semiconductors can enhance carrier transport. Gate dielectric materials with high-k properties improve gate control while reducing leakage. Metal gate materials with appropriate work functions optimize threshold voltage and carrier flow. The selection of these materials is crucial for achieving desired conductivity characteristics in advanced transistor architectures.

- Fabrication processes affecting conductivity performance: Fabrication processes significantly impact the conductivity of FinFET and DGFET transistors. Advanced lithography techniques enable precise fin formation and gate patterning, which directly affects channel dimensions and carrier flow. Deposition methods for gate stacks and spacers influence interface quality and parasitic resistances. Annealing processes optimize dopant activation and reduce defects that can impede conductivity. Process integration strategies that minimize damage to the channel region help preserve intrinsic carrier mobility and enhance overall conductivity.

- Novel architectures and innovations for conductivity enhancement: Innovative architectural designs are being developed to further enhance conductivity in FinFET and DGFET transistors. These include gate-all-around structures, vertically stacked nanowires, and complementary FET configurations. Advanced contact engineering reduces parasitic resistances at source/drain interfaces. Integration of strain-inducing elements enhances carrier mobility. Novel gate stack configurations with engineered work functions optimize carrier injection. These innovations collectively contribute to significant improvements in conductivity performance for next-generation transistor technologies.

02 Doping techniques for conductivity modulation in FinFET and DGFET

Various doping techniques are employed to modulate the conductivity in FinFET and DGFET transistors. Selective doping of the source, drain, and channel regions with appropriate dopants can enhance carrier mobility and concentration, directly affecting the conductivity. Advanced doping methods such as pulse doping, counter-doping, and gradient doping profiles are used to create optimal carrier distributions. These techniques help in achieving desired threshold voltages and improving the overall conductivity performance of the transistors while maintaining good electrostatic control.Expand Specific Solutions03 Material innovations for improving conductivity

Material innovations play a crucial role in enhancing the conductivity of FinFET and DGFET transistors. The introduction of high-mobility channel materials such as silicon-germanium (SiGe), germanium (Ge), or III-V compounds can significantly improve carrier mobility. Additionally, advanced gate dielectric materials with higher permittivity and metal gate electrodes with appropriate work functions help in reducing gate leakage and improving channel conductivity. Contact materials and structures are also optimized to reduce parasitic resistance and enhance overall device conductivity.Expand Specific Solutions04 Strain engineering for conductivity enhancement

Strain engineering techniques are employed to enhance the conductivity of FinFET and DGFET transistors. By introducing tensile or compressive strain in the channel region, the band structure of the semiconductor material is modified, leading to improved carrier mobility. Various methods such as embedded epitaxial growth of strained materials in source/drain regions, stress memorization techniques, and stress liners are used to induce beneficial strain. These approaches can significantly boost the conductivity of both n-type and p-type transistors, improving overall device performance.Expand Specific Solutions05 Advanced architectures and scaling approaches for conductivity optimization

Advanced architectures and scaling approaches are developed to optimize the conductivity of FinFET and DGFET transistors. These include multi-bridge channel FETs (MBCFETs), gate-all-around (GAA) structures, and vertically stacked nanowire/nanosheet configurations. Such architectures provide better electrostatic control and increased effective channel width within a smaller footprint. Additionally, innovative scaling techniques that maintain or improve conductivity while reducing dimensions are implemented, including work function engineering, interface quality improvement, and parasitic resistance reduction strategies.Expand Specific Solutions

Key Semiconductor Players and Competitive Landscape

The FinFET vs DGFET technology landscape is currently in a mature growth phase, with the global market for advanced transistor technologies estimated at $25-30 billion annually. Leading semiconductor manufacturers including TSMC, Samsung, Intel, and GlobalFoundries have heavily invested in FinFET technology, which has become the industry standard at sub-22nm nodes. IBM and CEA have demonstrated significant research advances in DGFET architectures, which offer superior conductivity control and reduced leakage current compared to traditional FinFETs. While FinFET technology has reached commercial maturity with widespread implementation in high-volume manufacturing, DGFET variants like Gate-All-Around (GAA) transistors are emerging as the next evolution, with companies like Samsung and TSMC announcing production timelines for 2022-2024, indicating a technology transition phase is underway.

International Business Machines Corp.

Technical Solution: IBM has pioneered significant advancements in both FinFET and DGFET technologies. Their approach to FinFET involves a tri-gate structure with enhanced channel control, achieving conductivity ranges of 1000-1500 μS/μm at 0.7V supply voltage[1]. For DGFET, IBM developed a unique gate-all-around (GAA) nanosheet transistor architecture that provides 4-sided gate control of the channel, enabling conductivity improvements of up to 40% compared to FinFETs at the same power envelope[2]. IBM's research demonstrates that while FinFETs show conductivity saturation at sub-10nm nodes, their DGFET implementation maintains scaling advantages with conductivity ranges extending to 2000-2500 μS/μm at advanced nodes[3]. Their technology roadmap indicates a transition from FinFET to DGFET for 5nm and beyond, with particular focus on optimizing the nanosheet width and spacing to maximize conductivity while managing short-channel effects.

Strengths: IBM's DGFET technology offers superior electrostatic control, reduced leakage current, and better performance at lower voltages compared to FinFET. Their nanosheet design provides flexibility in transistor width optimization for different applications. Weaknesses: The manufacturing complexity of DGFET structures increases production costs and challenges in volume manufacturing, with potential yield issues during early adoption phases.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced FinFET technology across multiple nodes (16nm, 10nm, 7nm, 5nm), with their N5 process achieving conductivity ranges of approximately 1700-1900 μS/μm[1]. Their FinFET implementation utilizes high-mobility channel materials and strain engineering to enhance carrier mobility. For DGFET development, TSMC is working on nanosheet transistors for their 3nm and beyond nodes, with reported conductivity improvements of 15-30% over their most advanced FinFET technology[2]. Their approach incorporates high-k metal gate materials with work function engineering to optimize threshold voltages and improve conductivity across different operating conditions. TSMC's research indicates that their DGFET implementation can achieve conductivity ranges of 2200-2600 μS/μm at nominal voltages, with significantly improved short-channel control[3]. Their technology also demonstrates better subthreshold swing characteristics (closer to the theoretical limit of 60mV/decade at room temperature), enabling lower operating voltages while maintaining performance targets.

Strengths: TSMC's manufacturing expertise enables industry-leading transistor performance and yield optimization. Their DGFET technology shows excellent scalability and power efficiency advantages over FinFET. Weaknesses: The transition from FinFET to DGFET requires substantial capital investment in new manufacturing equipment and processes, potentially limiting initial cost advantages compared to optimized FinFET nodes.

Core Patents and Research on Multi-Gate Transistor Conductivity

Fin-type field effect transistor

PatentActiveEP1920467A2

Innovation

- The FinFET structure is configured asymmetrically to decrease resistance between the gate and the source region and increase resistance between the gate and the drain region, and ballasted by adjusting fin dimensions and dopant concentrations to prevent thermal runaway, allowing operation at higher voltages.

Fin field effect transistors including epitaxial fins

PatentInactiveUS20070111439A1

Innovation

- A method of forming a fin field effect transistor with a narrower epitaxial layer, homogeneously doped in situ, which includes forming an active region, creating a vertical fin, and applying a conductive layer on the fin's surface and sidewalls, along with an isolation layer and nitride liner to control channel voltage and reduce defects.

Manufacturing Process Comparison and Yield Analysis

The manufacturing processes for FinFET and DGFET technologies present distinct challenges and advantages that significantly impact production yields and overall manufacturing efficiency. FinFET fabrication has matured considerably since its commercial introduction in 2011, with established processes at major foundries including TSMC, Samsung, and Intel. The manufacturing process typically involves complex multi-patterning lithography techniques to achieve the fin structures with precise dimensional control.

Current FinFET manufacturing yields at advanced nodes (5nm and below) range between 70-85%, depending on the foundry and specific process implementation. The primary yield detractors include fin height variation, line edge roughness, and gate alignment issues that directly impact device conductivity ranges and performance consistency.

In contrast, DGFET manufacturing remains predominantly in research and development phases, with limited commercial implementation. The fabrication process requires even more precise control of the gate formation on both sides of the channel, presenting additional lithographic and etching challenges. Current experimental yields for DGFET structures typically range from 40-65%, significantly lower than mature FinFET processes.

A critical difference in manufacturing approaches lies in the gate formation methodology. FinFETs utilize a self-aligned gate process where the fin is formed first, followed by gate deposition. DGFETs often require more complex gate-first or replacement gate processes to ensure proper alignment of both gates, adding process steps and increasing defect opportunities.

Thermal budget management represents another key manufacturing distinction. DGFET fabrication typically requires more stringent thermal control to maintain structural integrity of the dual-gate architecture, limiting available process options for dopant activation and annealing steps that are critical for controlling conductivity ranges.

Metrology and inspection challenges also differ significantly between the technologies. FinFET inspection focuses primarily on fin dimensions and gate wrap characteristics, while DGFET requires additional verification of gate alignment symmetry and channel uniformity between the two gates. This increased inspection complexity contributes to lower initial yields and higher manufacturing costs for DGFET technology.

Economic analysis indicates that current FinFET manufacturing costs approximately $0.32-0.45 per transistor at 5nm nodes, while experimental DGFET fabrication costs remain 1.8-2.5 times higher. However, as DGFET manufacturing matures, this gap is expected to narrow, potentially reaching cost parity within 3-5 years if adoption accelerates and process optimization continues at current rates.

Current FinFET manufacturing yields at advanced nodes (5nm and below) range between 70-85%, depending on the foundry and specific process implementation. The primary yield detractors include fin height variation, line edge roughness, and gate alignment issues that directly impact device conductivity ranges and performance consistency.

In contrast, DGFET manufacturing remains predominantly in research and development phases, with limited commercial implementation. The fabrication process requires even more precise control of the gate formation on both sides of the channel, presenting additional lithographic and etching challenges. Current experimental yields for DGFET structures typically range from 40-65%, significantly lower than mature FinFET processes.

A critical difference in manufacturing approaches lies in the gate formation methodology. FinFETs utilize a self-aligned gate process where the fin is formed first, followed by gate deposition. DGFETs often require more complex gate-first or replacement gate processes to ensure proper alignment of both gates, adding process steps and increasing defect opportunities.

Thermal budget management represents another key manufacturing distinction. DGFET fabrication typically requires more stringent thermal control to maintain structural integrity of the dual-gate architecture, limiting available process options for dopant activation and annealing steps that are critical for controlling conductivity ranges.

Metrology and inspection challenges also differ significantly between the technologies. FinFET inspection focuses primarily on fin dimensions and gate wrap characteristics, while DGFET requires additional verification of gate alignment symmetry and channel uniformity between the two gates. This increased inspection complexity contributes to lower initial yields and higher manufacturing costs for DGFET technology.

Economic analysis indicates that current FinFET manufacturing costs approximately $0.32-0.45 per transistor at 5nm nodes, while experimental DGFET fabrication costs remain 1.8-2.5 times higher. However, as DGFET manufacturing matures, this gap is expected to narrow, potentially reaching cost parity within 3-5 years if adoption accelerates and process optimization continues at current rates.

Power Efficiency and Thermal Management Considerations

Power efficiency and thermal management represent critical considerations when comparing FinFET and DGFET technologies. FinFETs have demonstrated significant improvements in power efficiency compared to planar transistors, reducing leakage current by 25-30% due to their superior gate control. However, DGFET structures push these advantages further with their dual-gate architecture, enabling even tighter electrostatic control and reducing leakage current by an additional 15-20% compared to conventional FinFETs.

The thermal characteristics of these devices differ substantially due to their structural variations. FinFETs, with their fin-shaped channel surrounded on three sides by the gate, experience thermal bottlenecks at high current densities. Heat dissipation primarily occurs through the substrate, creating potential hotspots at the fin base. Measurements indicate that FinFETs can experience temperature gradients of 10-15°C across the device under high-performance operation conditions.

DGFETs, by contrast, offer improved thermal pathways through both gates, distributing heat more evenly across the device structure. This configuration reduces peak temperature by approximately 8-12°C under identical operating conditions compared to FinFETs. The enhanced thermal management translates directly to reliability improvements, with DGFET structures showing 30-40% longer mean time to failure in accelerated stress testing.

Power density considerations become increasingly important as device dimensions shrink below 5nm. FinFETs operating at maximum performance can generate power densities exceeding 100W/cm², creating significant cooling challenges in densely packed circuits. DGFETs demonstrate 15-20% lower power density at equivalent performance levels, offering substantial advantages for mobile and IoT applications where battery life is paramount.

Dynamic power management capabilities also differ between these technologies. FinFETs exhibit threshold voltage shifts of 10-15mV across their operating temperature range, requiring more complex compensation circuits. DGFETs demonstrate greater threshold voltage stability (5-8mV variation) across the same temperature range, simplifying power management implementations and enabling more aggressive power-saving techniques.

For high-performance computing applications, the thermal advantages of DGFETs potentially allow for higher sustainable clock frequencies without thermal throttling. Simulation studies suggest DGFETs can maintain maximum performance 15-20% longer under sustained workloads before thermal constraints force frequency reduction. This characteristic becomes particularly valuable in data center environments where cooling costs represent a significant operational expense.

The thermal characteristics of these devices differ substantially due to their structural variations. FinFETs, with their fin-shaped channel surrounded on three sides by the gate, experience thermal bottlenecks at high current densities. Heat dissipation primarily occurs through the substrate, creating potential hotspots at the fin base. Measurements indicate that FinFETs can experience temperature gradients of 10-15°C across the device under high-performance operation conditions.

DGFETs, by contrast, offer improved thermal pathways through both gates, distributing heat more evenly across the device structure. This configuration reduces peak temperature by approximately 8-12°C under identical operating conditions compared to FinFETs. The enhanced thermal management translates directly to reliability improvements, with DGFET structures showing 30-40% longer mean time to failure in accelerated stress testing.

Power density considerations become increasingly important as device dimensions shrink below 5nm. FinFETs operating at maximum performance can generate power densities exceeding 100W/cm², creating significant cooling challenges in densely packed circuits. DGFETs demonstrate 15-20% lower power density at equivalent performance levels, offering substantial advantages for mobile and IoT applications where battery life is paramount.

Dynamic power management capabilities also differ between these technologies. FinFETs exhibit threshold voltage shifts of 10-15mV across their operating temperature range, requiring more complex compensation circuits. DGFETs demonstrate greater threshold voltage stability (5-8mV variation) across the same temperature range, simplifying power management implementations and enabling more aggressive power-saving techniques.

For high-performance computing applications, the thermal advantages of DGFETs potentially allow for higher sustainable clock frequencies without thermal throttling. Simulation studies suggest DGFETs can maintain maximum performance 15-20% longer under sustained workloads before thermal constraints force frequency reduction. This characteristic becomes particularly valuable in data center environments where cooling costs represent a significant operational expense.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!