FinFET Vs Planar Transistors: Switching Speed Analysis

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET and Planar Transistor Evolution

The evolution of transistor technology has witnessed a significant paradigm shift from traditional planar transistors to FinFET (Fin Field-Effect Transistor) architecture. This transition represents one of the most important developments in semiconductor manufacturing over the past two decades, fundamentally changing how integrated circuits are designed and fabricated.

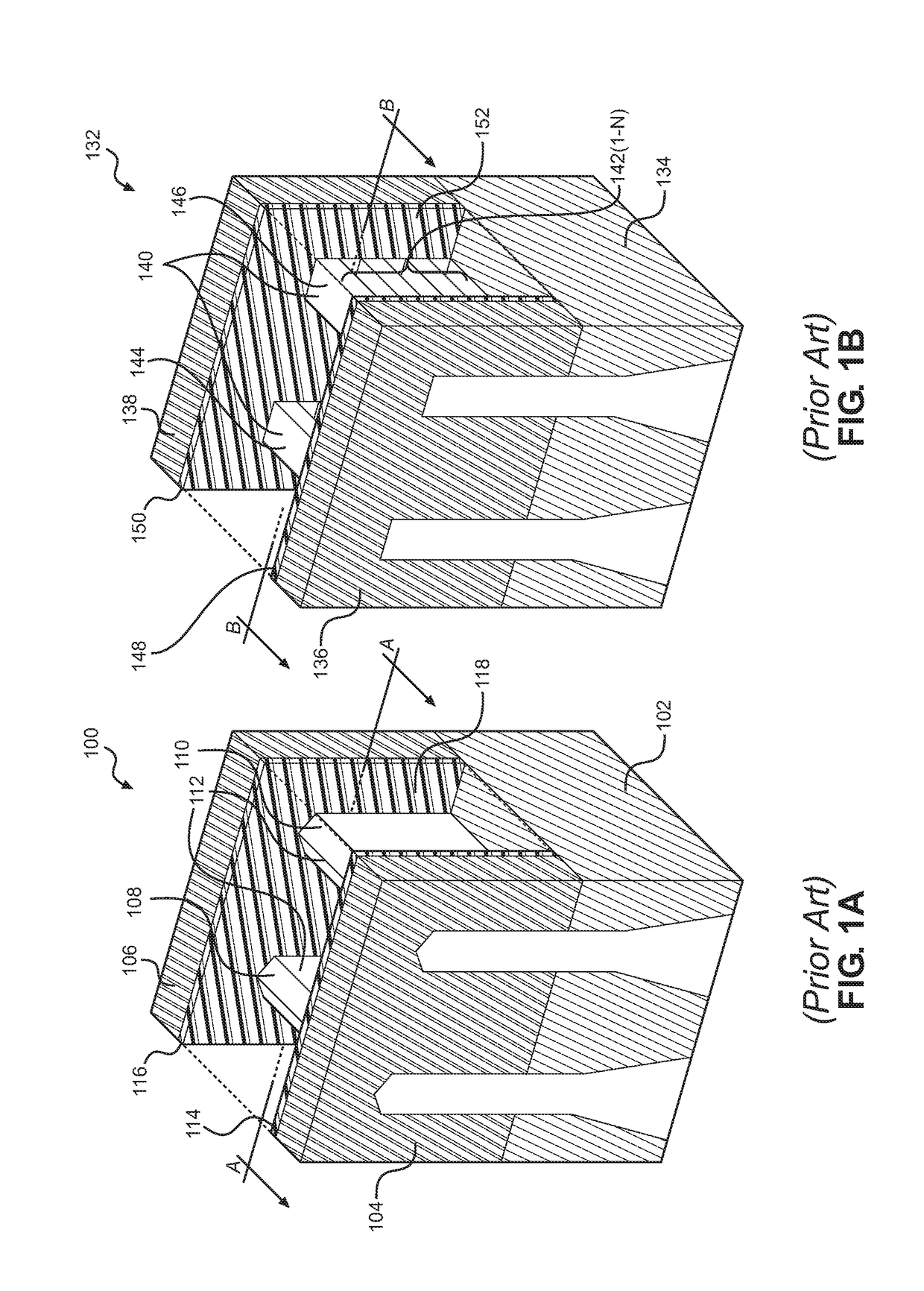

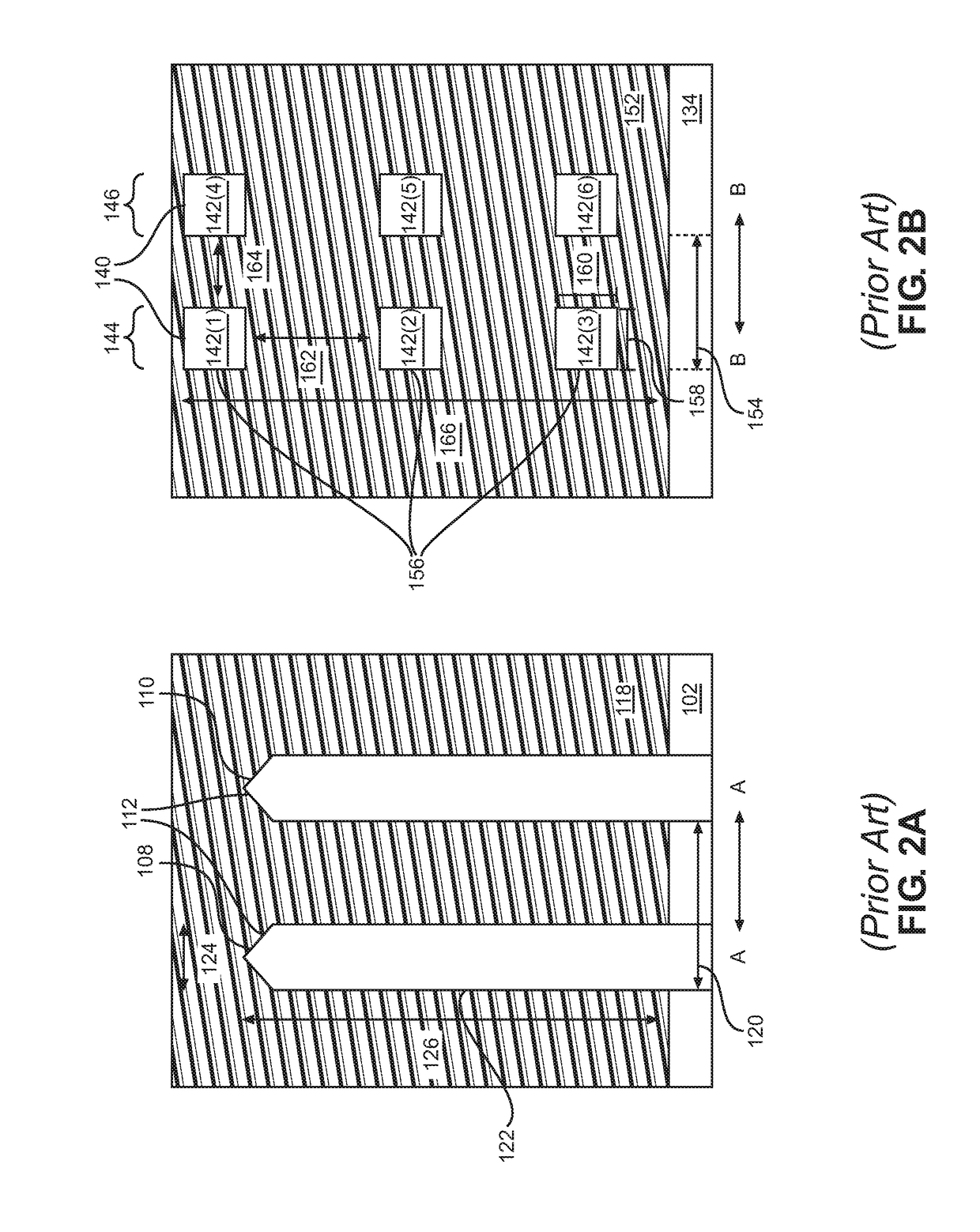

Planar transistors, which dominated semiconductor manufacturing since the 1960s, feature a flat structure where the gate is positioned on top of a single conducting channel between source and drain terminals. This design served the industry well through numerous generations of Moore's Law scaling, enabling continuous improvements in performance and power efficiency while reducing costs.

By the early 2000s, as transistor dimensions approached sub-45nm nodes, planar transistors began encountering severe physical limitations. Short-channel effects, gate leakage, and increasing power density emerged as critical challenges that threatened further scaling. The semiconductor industry faced a potential roadblock to continued performance improvements using conventional planar technology.

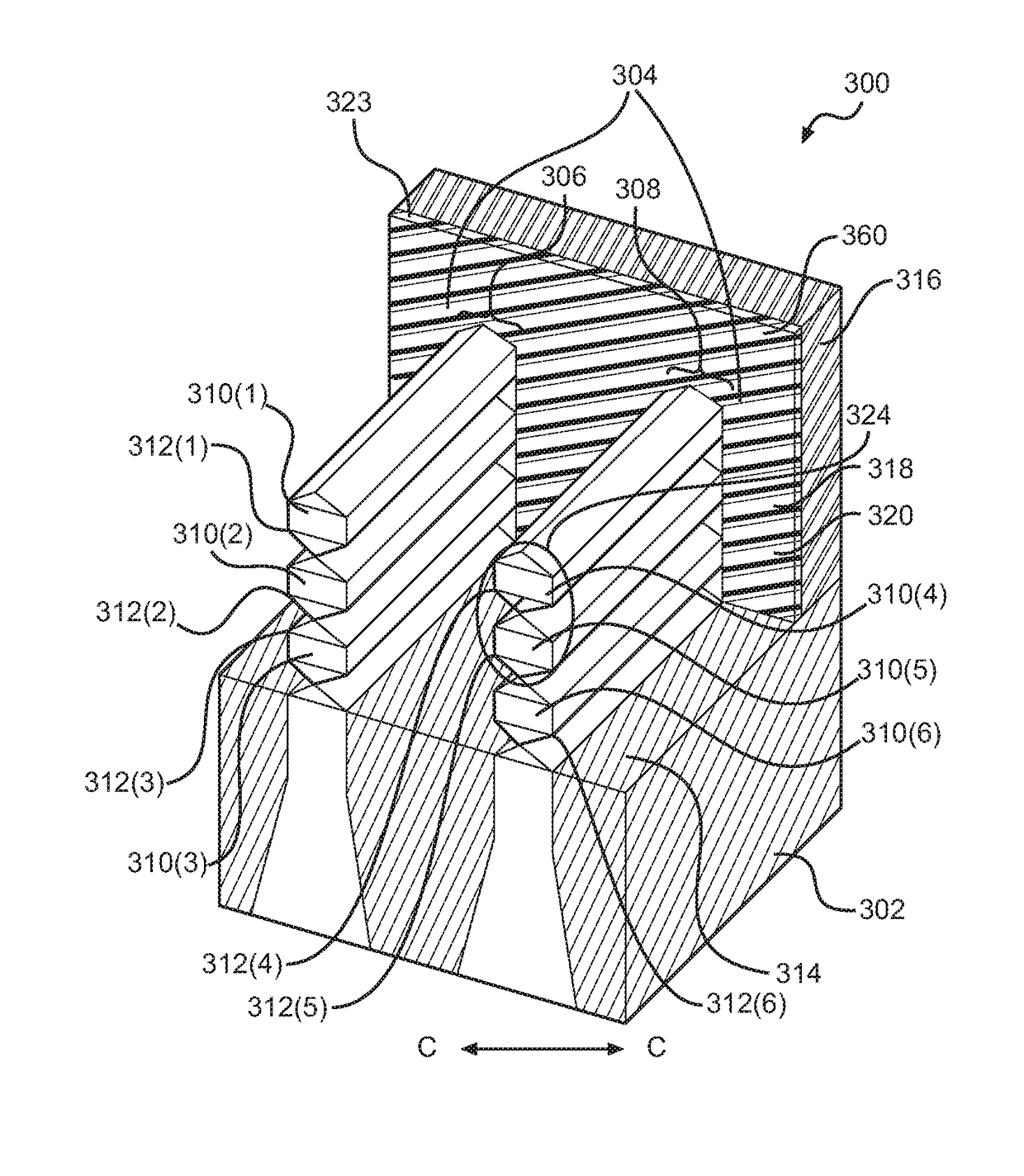

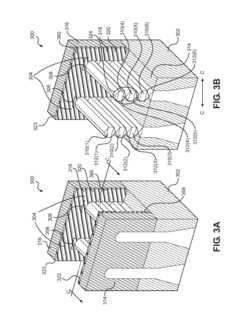

The introduction of FinFET architecture around 2011 marked a revolutionary departure from the traditional planar design. Instead of a flat channel, FinFETs feature a thin silicon fin that rises vertically from the substrate, with the gate wrapped around three sides of the fin. This three-dimensional structure provides significantly better electrostatic control of the channel, effectively addressing many of the short-channel effects that plagued planar designs.

Intel pioneered commercial FinFET technology with its 22nm Tri-Gate transistors, demonstrating substantial improvements in switching speed and power efficiency. Other major foundries, including TSMC and Samsung, followed with their own FinFET implementations at 16/14nm nodes and beyond, cementing the technology's position as the industry standard for high-performance applications.

The superior switching characteristics of FinFETs derive from their improved channel control, which allows for steeper subthreshold slopes and reduced leakage currents. This translates directly to faster switching speeds at lower operating voltages, enabling both performance gains and power savings that were unattainable with planar designs at equivalent technology nodes.

As manufacturing processes advanced to 10nm, 7nm, and now 5nm nodes, FinFET technology has continued to evolve with taller, thinner fins and more sophisticated gate structures. Multi-fin designs have become common, allowing for further performance scaling while maintaining the fundamental advantages of the FinFET architecture.

Looking toward the future, the industry is now exploring potential successors to FinFETs, including Gate-All-Around (GAA) and nanosheet transistors, which represent the next evolutionary step in three-dimensional transistor design. However, FinFET technology remains the backbone of current high-performance semiconductor manufacturing, representing a critical inflection point in the history of transistor development.

Planar transistors, which dominated semiconductor manufacturing since the 1960s, feature a flat structure where the gate is positioned on top of a single conducting channel between source and drain terminals. This design served the industry well through numerous generations of Moore's Law scaling, enabling continuous improvements in performance and power efficiency while reducing costs.

By the early 2000s, as transistor dimensions approached sub-45nm nodes, planar transistors began encountering severe physical limitations. Short-channel effects, gate leakage, and increasing power density emerged as critical challenges that threatened further scaling. The semiconductor industry faced a potential roadblock to continued performance improvements using conventional planar technology.

The introduction of FinFET architecture around 2011 marked a revolutionary departure from the traditional planar design. Instead of a flat channel, FinFETs feature a thin silicon fin that rises vertically from the substrate, with the gate wrapped around three sides of the fin. This three-dimensional structure provides significantly better electrostatic control of the channel, effectively addressing many of the short-channel effects that plagued planar designs.

Intel pioneered commercial FinFET technology with its 22nm Tri-Gate transistors, demonstrating substantial improvements in switching speed and power efficiency. Other major foundries, including TSMC and Samsung, followed with their own FinFET implementations at 16/14nm nodes and beyond, cementing the technology's position as the industry standard for high-performance applications.

The superior switching characteristics of FinFETs derive from their improved channel control, which allows for steeper subthreshold slopes and reduced leakage currents. This translates directly to faster switching speeds at lower operating voltages, enabling both performance gains and power savings that were unattainable with planar designs at equivalent technology nodes.

As manufacturing processes advanced to 10nm, 7nm, and now 5nm nodes, FinFET technology has continued to evolve with taller, thinner fins and more sophisticated gate structures. Multi-fin designs have become common, allowing for further performance scaling while maintaining the fundamental advantages of the FinFET architecture.

Looking toward the future, the industry is now exploring potential successors to FinFETs, including Gate-All-Around (GAA) and nanosheet transistors, which represent the next evolutionary step in three-dimensional transistor design. However, FinFET technology remains the backbone of current high-performance semiconductor manufacturing, representing a critical inflection point in the history of transistor development.

Market Demand for High-Speed Transistors

The semiconductor industry has witnessed a significant shift in market demand towards high-speed transistors, primarily driven by the exponential growth in data processing requirements across multiple sectors. The transition from planar transistors to FinFET architecture represents a critical response to this demand, as traditional planar designs reached their physical limitations in delivering the necessary switching speeds for contemporary applications.

Consumer electronics, particularly smartphones and tablets, constitute the largest market segment demanding enhanced transistor performance. With over 1.5 billion smartphones shipped annually, manufacturers continuously seek components that deliver superior processing capabilities while maintaining energy efficiency. The average consumer now expects applications to launch instantaneously and process complex tasks without lag, creating immense pressure for faster transistor switching speeds.

Data centers represent another crucial market driver, with global spending on data center infrastructure exceeding $200 billion annually. As cloud computing services expand, the need for servers capable of handling massive parallel processing tasks has intensified the demand for high-speed transistors. Financial institutions specifically require transistors with minimal latency for high-frequency trading systems where nanoseconds can determine competitive advantage.

The automotive industry has emerged as a rapidly growing market for advanced transistors, particularly with the rise of electric vehicles and autonomous driving technologies. Modern vehicles incorporate dozens of microprocessors managing everything from engine performance to safety systems, creating demand for transistors that can process sensor data with minimal delay. The automotive semiconductor market has been growing at approximately 10% annually, significantly outpacing the broader semiconductor industry.

Telecommunications infrastructure, especially with the global rollout of 5G networks, represents another substantial market for high-speed transistors. Base stations and network equipment require increasingly powerful processing capabilities to handle the expanded bandwidth and lower latency promises of next-generation networks.

Market research indicates that manufacturers are willing to pay premium prices for transistor technologies that deliver measurable improvements in switching speed. The performance-to-cost ratio has become a critical decision factor, with many end-product manufacturers prioritizing performance gains even at moderately increased component costs.

The geographical distribution of demand shows particular concentration in East Asia, North America, and Europe, with emerging markets in India and Brazil showing accelerated growth rates. Industry forecasts suggest the market for high-performance transistors will continue expanding at a compound annual growth rate of 8% through 2028, reaching a market value exceeding $25 billion.

Consumer electronics, particularly smartphones and tablets, constitute the largest market segment demanding enhanced transistor performance. With over 1.5 billion smartphones shipped annually, manufacturers continuously seek components that deliver superior processing capabilities while maintaining energy efficiency. The average consumer now expects applications to launch instantaneously and process complex tasks without lag, creating immense pressure for faster transistor switching speeds.

Data centers represent another crucial market driver, with global spending on data center infrastructure exceeding $200 billion annually. As cloud computing services expand, the need for servers capable of handling massive parallel processing tasks has intensified the demand for high-speed transistors. Financial institutions specifically require transistors with minimal latency for high-frequency trading systems where nanoseconds can determine competitive advantage.

The automotive industry has emerged as a rapidly growing market for advanced transistors, particularly with the rise of electric vehicles and autonomous driving technologies. Modern vehicles incorporate dozens of microprocessors managing everything from engine performance to safety systems, creating demand for transistors that can process sensor data with minimal delay. The automotive semiconductor market has been growing at approximately 10% annually, significantly outpacing the broader semiconductor industry.

Telecommunications infrastructure, especially with the global rollout of 5G networks, represents another substantial market for high-speed transistors. Base stations and network equipment require increasingly powerful processing capabilities to handle the expanded bandwidth and lower latency promises of next-generation networks.

Market research indicates that manufacturers are willing to pay premium prices for transistor technologies that deliver measurable improvements in switching speed. The performance-to-cost ratio has become a critical decision factor, with many end-product manufacturers prioritizing performance gains even at moderately increased component costs.

The geographical distribution of demand shows particular concentration in East Asia, North America, and Europe, with emerging markets in India and Brazil showing accelerated growth rates. Industry forecasts suggest the market for high-performance transistors will continue expanding at a compound annual growth rate of 8% through 2028, reaching a market value exceeding $25 billion.

Current Challenges in Transistor Switching Speed

Despite significant advancements in transistor technology, several critical challenges persist in improving switching speed performance, particularly when comparing FinFET and planar transistor architectures. The fundamental limitation of short-channel effects (SCEs) continues to plague planar transistors as dimensions shrink below 22nm. These effects, including drain-induced barrier lowering (DIBL) and threshold voltage roll-off, significantly degrade switching performance and increase leakage current, ultimately limiting the maximum achievable switching frequency.

Power dissipation presents another major challenge, with dynamic power consumption increasing proportionally with switching frequency. As transistors operate at higher speeds, the power density rises dramatically, creating thermal management issues that can lead to reliability concerns and performance degradation. This challenge is particularly acute in planar designs where heat dissipation pathways are more limited compared to 3D FinFET structures.

Parasitic capacitance remains a significant obstacle to achieving optimal switching speeds. In planar transistors, the gate-to-source and gate-to-drain capacitances create RC delays that limit switching performance. While FinFETs offer improved electrostatic control, they introduce additional parasitic capacitances at the fin sidewalls and corners that must be carefully managed to maximize speed advantages.

Process variation and manufacturing consistency pose increasing challenges as dimensions continue to shrink. Small variations in channel length, gate oxide thickness, or doping profiles can lead to substantial device-to-device performance differences. FinFETs, while offering better performance, present more complex manufacturing challenges due to their 3D structure, requiring precise fin formation and uniform gate coverage around the fin.

Quantum mechanical effects become increasingly prominent at sub-10nm nodes, with electron tunneling and quantum confinement affecting carrier mobility and transport characteristics. These effects fundamentally alter device physics and require sophisticated modeling approaches to accurately predict switching behavior.

Material limitations also constrain switching speed improvements. Silicon's inherent carrier mobility limitations have prompted research into alternative channel materials like germanium, III-V compounds, and 2D materials. However, integrating these materials into existing manufacturing processes while maintaining reliability remains challenging.

Interface quality between the gate dielectric and channel significantly impacts carrier mobility and switching performance. Defects and traps at these interfaces cause scattering and degrade electron transport efficiency. This issue is magnified in FinFETs where the channel-dielectric interface exists on multiple planes.

As the industry pushes toward ever-faster switching speeds, interconnect delays increasingly dominate overall circuit performance, shifting the bottleneck from transistor switching to signal propagation through metal lines. This necessitates holistic optimization approaches that consider both transistor and interconnect design simultaneously.

Power dissipation presents another major challenge, with dynamic power consumption increasing proportionally with switching frequency. As transistors operate at higher speeds, the power density rises dramatically, creating thermal management issues that can lead to reliability concerns and performance degradation. This challenge is particularly acute in planar designs where heat dissipation pathways are more limited compared to 3D FinFET structures.

Parasitic capacitance remains a significant obstacle to achieving optimal switching speeds. In planar transistors, the gate-to-source and gate-to-drain capacitances create RC delays that limit switching performance. While FinFETs offer improved electrostatic control, they introduce additional parasitic capacitances at the fin sidewalls and corners that must be carefully managed to maximize speed advantages.

Process variation and manufacturing consistency pose increasing challenges as dimensions continue to shrink. Small variations in channel length, gate oxide thickness, or doping profiles can lead to substantial device-to-device performance differences. FinFETs, while offering better performance, present more complex manufacturing challenges due to their 3D structure, requiring precise fin formation and uniform gate coverage around the fin.

Quantum mechanical effects become increasingly prominent at sub-10nm nodes, with electron tunneling and quantum confinement affecting carrier mobility and transport characteristics. These effects fundamentally alter device physics and require sophisticated modeling approaches to accurately predict switching behavior.

Material limitations also constrain switching speed improvements. Silicon's inherent carrier mobility limitations have prompted research into alternative channel materials like germanium, III-V compounds, and 2D materials. However, integrating these materials into existing manufacturing processes while maintaining reliability remains challenging.

Interface quality between the gate dielectric and channel significantly impacts carrier mobility and switching performance. Defects and traps at these interfaces cause scattering and degrade electron transport efficiency. This issue is magnified in FinFETs where the channel-dielectric interface exists on multiple planes.

As the industry pushes toward ever-faster switching speeds, interconnect delays increasingly dominate overall circuit performance, shifting the bottleneck from transistor switching to signal propagation through metal lines. This necessitates holistic optimization approaches that consider both transistor and interconnect design simultaneously.

Comparative Switching Speed Solutions

01 FinFET structure advantages for switching speed

FinFET transistors offer superior switching speed compared to planar transistors due to their three-dimensional structure. The fin-shaped channel allows for better electrostatic control of the gate over the channel, reducing short-channel effects and leakage current. This improved gate control enables faster switching speeds, higher drive currents, and better performance at lower operating voltages, making FinFETs particularly advantageous for high-performance computing applications.- FinFET structure advantages for switching speed: FinFET transistors offer superior switching speed compared to planar transistors due to their three-dimensional structure. The fin-shaped channel allows for better electrostatic control of the gate over the channel, reducing short-channel effects and leakage current. This improved gate control enables faster switching speeds, higher drive currents, and better performance at lower operating voltages, making FinFETs particularly advantageous for high-performance computing applications.

- Multi-gate design impact on transistor performance: Multi-gate designs in FinFET architectures significantly enhance transistor performance and switching speeds. By wrapping the gate around multiple sides of the channel, these designs provide better control of the channel current, reducing off-state leakage and improving on-state drive capability. This configuration allows for steeper subthreshold slopes and faster transitions between on and off states, resulting in improved switching characteristics compared to conventional planar transistors.

- Channel engineering techniques for speed optimization: Advanced channel engineering techniques are employed to optimize the switching speed of both FinFET and planar transistors. These include strain engineering, channel material selection, and doping profile optimization. For FinFETs, the fin dimensions and shape are critical factors affecting carrier mobility and switching performance. Techniques such as incorporating silicon-germanium or III-V materials in the channel region can enhance carrier mobility, leading to faster switching speeds in both transistor architectures.

- Design and simulation methodologies for transistor comparison: Sophisticated design and simulation methodologies are essential for accurately comparing the switching speeds of FinFET and planar transistors. These methodologies involve advanced modeling techniques that account for quantum effects, carrier transport mechanisms, and parasitic elements. Circuit simulation tools enable designers to evaluate performance metrics such as propagation delay, power consumption, and frequency response under various operating conditions, facilitating the optimization of transistor designs for specific applications.

- Process technology scaling effects on switching performance: Process technology scaling has different effects on the switching performance of FinFET and planar transistors. As dimensions shrink below 22nm, planar transistors face significant challenges with short-channel effects and leakage currents, which degrade switching performance. FinFETs maintain better electrostatic integrity at smaller nodes, allowing them to achieve superior switching speeds with scaling. Advanced manufacturing processes, including high-k metal gates and strain engineering, further enhance the speed advantages of FinFETs in advanced technology nodes.

02 Design optimization techniques for transistor switching speed

Various design optimization techniques can be employed to enhance the switching speed of both FinFET and planar transistors. These include optimizing gate length, adjusting threshold voltage, implementing strain engineering, and refining doping profiles. Advanced simulation tools allow designers to model and predict transistor performance, enabling the creation of optimized designs that maximize switching speed while maintaining power efficiency and reliability.Expand Specific Solutions03 Multi-gate configurations and their impact on performance

Multi-gate configurations, including double-gate, tri-gate, and gate-all-around structures, significantly improve transistor switching performance compared to traditional planar designs. These configurations provide enhanced control over the channel, reducing leakage currents and improving subthreshold swing. The increased effective channel width in multi-gate designs also contributes to higher drive currents and faster switching speeds, making them suitable for high-performance and low-power applications.Expand Specific Solutions04 Scaling effects on transistor switching performance

As transistor dimensions scale down, the differences in switching performance between FinFET and planar technologies become more pronounced. Planar transistors face significant challenges at advanced nodes due to increased short-channel effects and leakage currents, which degrade switching speed. FinFETs maintain better performance at smaller nodes due to superior channel control. However, both technologies require innovative approaches to overcome quantum effects and other physical limitations that emerge at nanoscale dimensions.Expand Specific Solutions05 Material innovations for enhanced switching speed

Novel materials are being incorporated into both FinFET and planar transistor designs to enhance switching speeds. High-mobility channel materials such as silicon-germanium, germanium, and III-V compounds can significantly improve carrier mobility. Advanced gate dielectrics with higher dielectric constants enable thinner equivalent oxide thickness while maintaining low leakage. Metal gate materials with appropriate work functions optimize threshold voltages and reduce polysilicon depletion effects, collectively contributing to faster switching performance.Expand Specific Solutions

Leading Semiconductor Manufacturers Analysis

The FinFET vs Planar Transistor competition represents a pivotal transition in semiconductor technology, currently in the mature growth phase with FinFET dominating advanced nodes. The global market exceeds $400 billion, driven by increasing demand for high-performance computing. Technology maturity varies significantly among key players: TSMC, Samsung, and Intel lead with sub-10nm FinFET production capabilities, while GlobalFoundries, UMC, and SMIC offer competitive options at larger nodes. Qualcomm, NXP, and Synopsys leverage these advancements through fabless models. The switching speed advantage of FinFETs (30-50% faster than planar) has become critical for mobile and high-performance applications, though planar transistors remain relevant in legacy and cost-sensitive markets.

GlobalFoundries U.S., Inc.

Technical Solution: GlobalFoundries has developed a differentiated approach to FinFET technology with their 14nm and 12nm process nodes. Their FinFET implementation features a carefully optimized fin geometry with height-to-width ratios engineered for specific application targets. GlobalFoundries' 14nm FinFET technology demonstrates approximately 20% higher switching speeds compared to their 28nm planar technology, while consuming 40% less power. Their FinFET design incorporates high-k metal gate (HKMG) technology with optimized work function metals to achieve precise threshold voltage control. GlobalFoundries has implemented specialized strain engineering techniques to enhance carrier mobility in both NMOS and PMOS transistors. Their FinFET technology includes advanced source/drain epitaxy processes that reduce parasitic resistance, which is critical for maximizing switching performance. GlobalFoundries has also developed specialized FinFET variants optimized for RF applications, with improved linearity and noise characteristics compared to planar transistors.

Strengths: Strong focus on specialized process technologies tailored for specific applications like RF, automotive, and IoT, with good balance of performance and cost. Weaknesses: Limited to less advanced nodes compared to TSMC and Samsung, with less aggressive scaling roadmap, which impacts maximum achievable switching speeds.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered advanced FinFET technology with their 16nm, 10nm, 7nm, and 5nm process nodes. Their FinFET implementation utilizes a multi-gate 3D transistor structure where the gate wraps around three sides of the elevated fin-shaped channel. This design significantly reduces leakage current and allows for operation at lower voltages compared to planar transistors. TSMC's FinFET technology demonstrates 25-30% higher switching speeds at the same power consumption compared to planar transistors, or alternatively, 30-50% lower power consumption at the same performance level. Their 7nm FinFET technology shows switching speeds up to 40% faster than their 16nm planar technology, with a 65% reduction in power consumption. TSMC has also implemented strain engineering techniques to enhance carrier mobility in the channel, further improving switching performance.

Strengths: Industry-leading process technology with excellent electrostatic control, reduced short-channel effects, and superior power efficiency. TSMC's FinFET technology enables higher transistor density and better performance scaling. Weaknesses: Higher manufacturing complexity and cost compared to planar designs, with more stringent design rules that increase development time and expenses.

Key Patents in FinFET Technology

Methods of forming alternative channel materials on finfet semiconductor devices

PatentActiveUS20160064526A1

Innovation

- A method involving the formation of an initial fin structure, followed by recess etching, growth of epi semiconductor layers with varying germanium concentrations, and a thermal anneal process to create a substantially homogeneous defect-free SiGe replacement fin, which is then exposed and surrounded by a gate structure.

Nanowire channel structures of continuously stacked nanowires for complementary metal oxide semiconductor (CMOS) devices

PatentActiveUS20170110374A1

Innovation

- The implementation of continuously stacked nanowires with a greater width at the central portion than at the top and bottom end portions, eliminating the need for separation distances between nanowires, allowing for a higher number of nanowires while reducing parasitic capacitance and simplifying fabrication.

Power Efficiency vs. Switching Speed Trade-offs

The fundamental trade-off between power efficiency and switching speed represents a critical design consideration when comparing FinFET and planar transistor architectures. FinFETs demonstrate superior power efficiency due to their three-dimensional gate structure, which enables more effective channel control and significantly reduces leakage current. This reduction in leakage current translates directly to lower static power consumption, particularly important for battery-powered devices and high-density computing applications.

When examining switching speed characteristics, FinFETs exhibit faster switching capabilities than their planar counterparts at equivalent process nodes. This advantage stems from the improved electrostatic control of the channel, allowing for steeper subthreshold slopes and higher drive currents. Quantitative analyses indicate that FinFETs can achieve 25-30% higher switching speeds while simultaneously reducing power consumption by 30-50% compared to planar transistors at the same technology node.

However, this performance advantage comes with design complexity trade-offs. The three-dimensional structure of FinFETs introduces additional parasitic capacitances at the fin sidewalls, which can partially offset switching speed gains in certain circuit configurations. Engineers must carefully consider these parasitics during circuit design to fully leverage FinFET speed advantages.

Temperature sensitivity presents another dimension in the power-speed trade-off equation. Planar transistors typically demonstrate greater performance degradation at elevated temperatures, while FinFETs maintain more consistent switching characteristics across wider temperature ranges. This thermal stability provides FinFETs with a significant advantage in high-performance computing environments where thermal management is critical.

Supply voltage scaling further highlights the efficiency-speed relationship. FinFETs maintain performance advantages at lower operating voltages, enabling operation at 0.7-0.8V compared to the 0.9-1.0V typically required by planar transistors for comparable performance. This voltage scaling capability directly impacts the power consumption equation (P = CV²f), providing exponential power savings while maintaining switching speed targets.

For mobile and IoT applications, the power-speed trade-off manifests differently across active and standby operational modes. FinFETs excel in both scenarios, offering 60-70% lower standby power and 30-40% improved active power efficiency at equivalent performance levels. This dual advantage has accelerated FinFET adoption in mobile processors despite their higher manufacturing complexity and cost.

When examining switching speed characteristics, FinFETs exhibit faster switching capabilities than their planar counterparts at equivalent process nodes. This advantage stems from the improved electrostatic control of the channel, allowing for steeper subthreshold slopes and higher drive currents. Quantitative analyses indicate that FinFETs can achieve 25-30% higher switching speeds while simultaneously reducing power consumption by 30-50% compared to planar transistors at the same technology node.

However, this performance advantage comes with design complexity trade-offs. The three-dimensional structure of FinFETs introduces additional parasitic capacitances at the fin sidewalls, which can partially offset switching speed gains in certain circuit configurations. Engineers must carefully consider these parasitics during circuit design to fully leverage FinFET speed advantages.

Temperature sensitivity presents another dimension in the power-speed trade-off equation. Planar transistors typically demonstrate greater performance degradation at elevated temperatures, while FinFETs maintain more consistent switching characteristics across wider temperature ranges. This thermal stability provides FinFETs with a significant advantage in high-performance computing environments where thermal management is critical.

Supply voltage scaling further highlights the efficiency-speed relationship. FinFETs maintain performance advantages at lower operating voltages, enabling operation at 0.7-0.8V compared to the 0.9-1.0V typically required by planar transistors for comparable performance. This voltage scaling capability directly impacts the power consumption equation (P = CV²f), providing exponential power savings while maintaining switching speed targets.

For mobile and IoT applications, the power-speed trade-off manifests differently across active and standby operational modes. FinFETs excel in both scenarios, offering 60-70% lower standby power and 30-40% improved active power efficiency at equivalent performance levels. This dual advantage has accelerated FinFET adoption in mobile processors despite their higher manufacturing complexity and cost.

Semiconductor Fabrication Process Comparison

The fabrication processes for FinFET and planar transistors represent two distinct generations in semiconductor manufacturing technology. Planar transistors, the traditional approach used for decades, involve creating a flat channel between source and drain regions on the silicon substrate. This process typically utilizes 45nm to 28nm technology nodes and employs conventional photolithography techniques with relatively straightforward masking steps. The gate is positioned directly above the channel, controlling current flow in a two-dimensional manner.

In contrast, FinFET fabrication introduces significant complexity with its three-dimensional structure. The process begins with silicon fin formation through precise etching techniques, creating vertical fins that serve as the transistor channel. This approach requires advanced lithography methods such as immersion lithography or multi-patterning techniques to achieve the necessary resolution for 22nm nodes and below. The gate material wraps around three sides of the fin, necessitating more sophisticated deposition and etching steps compared to planar designs.

The critical dimension control in FinFET manufacturing presents substantial challenges, requiring atomic-level precision in fin width and height to ensure consistent electrical characteristics. This precision demands advanced metrology tools and tighter process controls throughout fabrication. Additionally, FinFET processes typically incorporate high-k metal gate (HKMG) technology, replacing traditional silicon dioxide gate dielectrics with materials having higher dielectric constants, further complicating the manufacturing sequence.

Thermal management during fabrication differs significantly between the two technologies. Planar transistors dissipate heat primarily through the substrate, while FinFETs must manage thermal issues in their three-dimensional structure, requiring careful consideration during process development. This affects annealing steps and thermal budget management throughout the manufacturing flow.

The mask count and process steps increase substantially for FinFET fabrication—typically 30-40% more than planar processes—directly impacting manufacturing costs and cycle time. This complexity extends to doping processes as well, with FinFETs requiring precisely controlled implantation angles to ensure uniform dopant distribution throughout the fin structure, compared to the relatively straightforward vertical implantation used for planar devices.

Yield management presents another significant difference, with FinFET processes generally demonstrating lower initial yields due to their complexity and sensitivity to process variations. However, as manufacturing techniques have matured, this gap has narrowed, though FinFET fabrication still commands a premium in production costs compared to legacy planar processes.

In contrast, FinFET fabrication introduces significant complexity with its three-dimensional structure. The process begins with silicon fin formation through precise etching techniques, creating vertical fins that serve as the transistor channel. This approach requires advanced lithography methods such as immersion lithography or multi-patterning techniques to achieve the necessary resolution for 22nm nodes and below. The gate material wraps around three sides of the fin, necessitating more sophisticated deposition and etching steps compared to planar designs.

The critical dimension control in FinFET manufacturing presents substantial challenges, requiring atomic-level precision in fin width and height to ensure consistent electrical characteristics. This precision demands advanced metrology tools and tighter process controls throughout fabrication. Additionally, FinFET processes typically incorporate high-k metal gate (HKMG) technology, replacing traditional silicon dioxide gate dielectrics with materials having higher dielectric constants, further complicating the manufacturing sequence.

Thermal management during fabrication differs significantly between the two technologies. Planar transistors dissipate heat primarily through the substrate, while FinFETs must manage thermal issues in their three-dimensional structure, requiring careful consideration during process development. This affects annealing steps and thermal budget management throughout the manufacturing flow.

The mask count and process steps increase substantially for FinFET fabrication—typically 30-40% more than planar processes—directly impacting manufacturing costs and cycle time. This complexity extends to doping processes as well, with FinFETs requiring precisely controlled implantation angles to ensure uniform dopant distribution throughout the fin structure, compared to the relatively straightforward vertical implantation used for planar devices.

Yield management presents another significant difference, with FinFET processes generally demonstrating lower initial yields due to their complexity and sensitivity to process variations. However, as manufacturing techniques have matured, this gap has narrowed, though FinFET fabrication still commands a premium in production costs compared to legacy planar processes.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!