HBM4 Power Delivery Networks: Inductance Control And Decap Strategy

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 PDN Technology Evolution and Objectives

High-Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with each generation bringing substantial improvements in bandwidth, capacity, and energy efficiency. The journey from HBM1 to HBM4 represents a remarkable technological progression driven by the increasing demands of data-intensive applications such as artificial intelligence, high-performance computing, and graphics processing. HBM4, as the latest iteration, aims to address the growing power delivery challenges that have become increasingly critical with each generation.

The evolution of HBM power delivery networks (PDNs) has been characterized by continuous refinement to accommodate higher bandwidth requirements while maintaining signal integrity. HBM1, introduced around 2013, featured a relatively simple PDN structure with limited bandwidth capabilities. HBM2, which followed in 2016, doubled the bandwidth while introducing more complex power delivery considerations. HBM2E further enhanced these capabilities, while HBM3, released in 2021, represented a significant leap forward with substantially increased bandwidth and more sophisticated power delivery requirements.

HBM4, currently under development, faces unprecedented challenges in power delivery as it aims to deliver bandwidth exceeding 8TB/s. This dramatic increase necessitates fundamental innovations in PDN design, particularly in the areas of inductance control and decoupling capacitor (decap) strategies. The power integrity requirements have become exponentially more demanding with each generation, making PDN optimization a critical factor in HBM4's success.

The primary technical objectives for HBM4 PDN development include minimizing power supply noise, reducing impedance across a wider frequency range, and maintaining signal integrity despite increasing data rates. These objectives must be achieved while adhering to strict thermal constraints and physical form factor limitations inherent to the 2.5D and 3D packaging technologies used in HBM implementations.

Industry trends indicate that future computing workloads will continue to demand ever-increasing memory bandwidth, making the development of efficient PDN solutions for HBM4 not just a technical challenge but a strategic necessity. The ability to deliver clean power to increasingly dense and high-performance memory stacks will be a key differentiator in next-generation computing platforms.

The technological trajectory suggests that innovations in materials science, particularly in the development of advanced substrate technologies and novel decoupling materials, will play a crucial role in meeting HBM4 PDN requirements. Additionally, co-design methodologies that consider power delivery networks from the earliest stages of system architecture development are becoming essential to achieving optimal performance.

The evolution of HBM power delivery networks (PDNs) has been characterized by continuous refinement to accommodate higher bandwidth requirements while maintaining signal integrity. HBM1, introduced around 2013, featured a relatively simple PDN structure with limited bandwidth capabilities. HBM2, which followed in 2016, doubled the bandwidth while introducing more complex power delivery considerations. HBM2E further enhanced these capabilities, while HBM3, released in 2021, represented a significant leap forward with substantially increased bandwidth and more sophisticated power delivery requirements.

HBM4, currently under development, faces unprecedented challenges in power delivery as it aims to deliver bandwidth exceeding 8TB/s. This dramatic increase necessitates fundamental innovations in PDN design, particularly in the areas of inductance control and decoupling capacitor (decap) strategies. The power integrity requirements have become exponentially more demanding with each generation, making PDN optimization a critical factor in HBM4's success.

The primary technical objectives for HBM4 PDN development include minimizing power supply noise, reducing impedance across a wider frequency range, and maintaining signal integrity despite increasing data rates. These objectives must be achieved while adhering to strict thermal constraints and physical form factor limitations inherent to the 2.5D and 3D packaging technologies used in HBM implementations.

Industry trends indicate that future computing workloads will continue to demand ever-increasing memory bandwidth, making the development of efficient PDN solutions for HBM4 not just a technical challenge but a strategic necessity. The ability to deliver clean power to increasingly dense and high-performance memory stacks will be a key differentiator in next-generation computing platforms.

The technological trajectory suggests that innovations in materials science, particularly in the development of advanced substrate technologies and novel decoupling materials, will play a crucial role in meeting HBM4 PDN requirements. Additionally, co-design methodologies that consider power delivery networks from the earliest stages of system architecture development are becoming essential to achieving optimal performance.

Market Demand Analysis for HBM4 Memory Solutions

The global market for High Bandwidth Memory (HBM) solutions is experiencing unprecedented growth, driven primarily by the explosive demand for artificial intelligence (AI) and machine learning (ML) applications. HBM4, as the next generation of this technology, is positioned to address critical performance bottlenecks in data-intensive computing environments where power delivery networks (PDNs) play a crucial role.

Market research indicates that the HBM memory market is projected to grow at a compound annual growth rate of over 30% through 2028, with particular acceleration in sectors requiring advanced computing capabilities. The AI/ML segment represents the largest demand driver, as training large language models and neural networks requires massive parallel processing capabilities supported by high-bandwidth, power-efficient memory solutions.

Data center operators are increasingly prioritizing memory solutions that offer superior performance per watt metrics, making HBM4's power delivery network innovations particularly valuable. Industry surveys reveal that power consumption has become the primary constraint in scaling AI infrastructure, with memory subsystems accounting for approximately 25% of total system power in high-performance computing environments.

The cloud service provider market segment demonstrates particularly strong demand for advanced HBM solutions, as these companies compete to offer the most efficient AI training and inference services. This market segment values the inductance control and decoupling capacitor strategies that enable stable power delivery at higher frequencies and lower voltages.

Telecommunications and edge computing applications represent emerging market opportunities for HBM4 technology. As 5G networks expand and edge AI capabilities become more sophisticated, the demand for compact, energy-efficient memory solutions with robust power delivery networks is growing significantly in these sectors.

Automotive and industrial automation sectors are also showing increased interest in HBM4 solutions, particularly for advanced driver-assistance systems (ADAS) and autonomous vehicle development. These applications require memory systems that can maintain performance integrity under varying power conditions while meeting strict reliability standards.

Geographically, North America and East Asia dominate the market demand for advanced HBM solutions, with particularly strong growth in regions with concentrated semiconductor manufacturing and AI research activities. However, European demand is accelerating as the region invests heavily in developing sovereign AI capabilities.

The market increasingly values memory solutions that can demonstrate measurable improvements in system-level energy efficiency. HBM4's advanced power delivery networks, with optimized inductance control and strategic decoupling capacitor placement, directly address this requirement by enabling higher performance at lower power envelopes.

Market research indicates that the HBM memory market is projected to grow at a compound annual growth rate of over 30% through 2028, with particular acceleration in sectors requiring advanced computing capabilities. The AI/ML segment represents the largest demand driver, as training large language models and neural networks requires massive parallel processing capabilities supported by high-bandwidth, power-efficient memory solutions.

Data center operators are increasingly prioritizing memory solutions that offer superior performance per watt metrics, making HBM4's power delivery network innovations particularly valuable. Industry surveys reveal that power consumption has become the primary constraint in scaling AI infrastructure, with memory subsystems accounting for approximately 25% of total system power in high-performance computing environments.

The cloud service provider market segment demonstrates particularly strong demand for advanced HBM solutions, as these companies compete to offer the most efficient AI training and inference services. This market segment values the inductance control and decoupling capacitor strategies that enable stable power delivery at higher frequencies and lower voltages.

Telecommunications and edge computing applications represent emerging market opportunities for HBM4 technology. As 5G networks expand and edge AI capabilities become more sophisticated, the demand for compact, energy-efficient memory solutions with robust power delivery networks is growing significantly in these sectors.

Automotive and industrial automation sectors are also showing increased interest in HBM4 solutions, particularly for advanced driver-assistance systems (ADAS) and autonomous vehicle development. These applications require memory systems that can maintain performance integrity under varying power conditions while meeting strict reliability standards.

Geographically, North America and East Asia dominate the market demand for advanced HBM solutions, with particularly strong growth in regions with concentrated semiconductor manufacturing and AI research activities. However, European demand is accelerating as the region invests heavily in developing sovereign AI capabilities.

The market increasingly values memory solutions that can demonstrate measurable improvements in system-level energy efficiency. HBM4's advanced power delivery networks, with optimized inductance control and strategic decoupling capacitor placement, directly address this requirement by enabling higher performance at lower power envelopes.

Current Challenges in HBM4 Power Delivery Networks

The power delivery network (PDN) for HBM4 faces unprecedented challenges due to the technology's increased bandwidth, higher operating frequencies, and more complex integration requirements. As HBM4 pushes memory bandwidth beyond 3.2 Gbps, the PDN must maintain stable voltage levels while managing significantly higher current demands. This creates a fundamental tension between power delivery requirements and signal integrity constraints that engineers must carefully balance.

A primary challenge is managing PDN impedance across a wide frequency range. The target impedance for HBM4 systems has decreased substantially compared to previous generations, requiring more sophisticated design approaches. The impedance profile must remain below critical thresholds from DC to several GHz to prevent voltage fluctuations that could compromise system reliability.

Loop inductance has emerged as a critical limiting factor in HBM4 PDN design. As operating frequencies increase, even small inductance values can create substantial voltage drops during transient current demands. The physical constraints of the interposer and package design limit options for reducing this parasitic inductance, particularly in the power delivery path between the voltage regulator modules and the HBM4 stacks.

Decoupling capacitor (decap) implementation faces severe space constraints in HBM4 designs. The high-density integration leaves minimal room for placing decaps, yet the demand for capacitance has increased. Engineers must develop novel decap placement strategies and utilize advanced capacitor technologies with higher capacitance density and lower equivalent series inductance (ESL).

Power integrity issues are further complicated by the thermal challenges inherent in HBM4 designs. Higher operating temperatures affect capacitor performance and can increase resistance in power delivery paths, creating a complex interdependency between thermal management and power delivery strategies.

The silicon interposer, which serves as the integration platform for HBM4, presents unique PDN design challenges. The limited metal layers and routing resources on the interposer constrain PDN design options, forcing engineers to make difficult tradeoffs between signal routing and power distribution networks.

Electromagnetic interference (EMI) and noise coupling have become more problematic with HBM4's higher operating frequencies. The dense integration of power and signal lines creates numerous opportunities for unwanted coupling, requiring sophisticated isolation techniques and careful analysis of return current paths.

Simulation and modeling of HBM4 PDNs present computational challenges due to the multi-scale nature of the problem, spanning from on-die power distribution to package-level networks. Accurate modeling requires consideration of frequency-dependent effects across multiple domains, significantly increasing simulation complexity and computational requirements.

A primary challenge is managing PDN impedance across a wide frequency range. The target impedance for HBM4 systems has decreased substantially compared to previous generations, requiring more sophisticated design approaches. The impedance profile must remain below critical thresholds from DC to several GHz to prevent voltage fluctuations that could compromise system reliability.

Loop inductance has emerged as a critical limiting factor in HBM4 PDN design. As operating frequencies increase, even small inductance values can create substantial voltage drops during transient current demands. The physical constraints of the interposer and package design limit options for reducing this parasitic inductance, particularly in the power delivery path between the voltage regulator modules and the HBM4 stacks.

Decoupling capacitor (decap) implementation faces severe space constraints in HBM4 designs. The high-density integration leaves minimal room for placing decaps, yet the demand for capacitance has increased. Engineers must develop novel decap placement strategies and utilize advanced capacitor technologies with higher capacitance density and lower equivalent series inductance (ESL).

Power integrity issues are further complicated by the thermal challenges inherent in HBM4 designs. Higher operating temperatures affect capacitor performance and can increase resistance in power delivery paths, creating a complex interdependency between thermal management and power delivery strategies.

The silicon interposer, which serves as the integration platform for HBM4, presents unique PDN design challenges. The limited metal layers and routing resources on the interposer constrain PDN design options, forcing engineers to make difficult tradeoffs between signal routing and power distribution networks.

Electromagnetic interference (EMI) and noise coupling have become more problematic with HBM4's higher operating frequencies. The dense integration of power and signal lines creates numerous opportunities for unwanted coupling, requiring sophisticated isolation techniques and careful analysis of return current paths.

Simulation and modeling of HBM4 PDNs present computational challenges due to the multi-scale nature of the problem, spanning from on-die power distribution to package-level networks. Accurate modeling requires consideration of frequency-dependent effects across multiple domains, significantly increasing simulation complexity and computational requirements.

Current Inductance Control and Decap Implementation Strategies

01 HBM4 Power Delivery Network Design Optimization

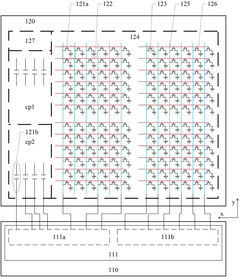

Design optimization techniques for HBM4 power delivery networks focus on reducing inductance through improved layout strategies. These approaches include optimizing power plane configurations, minimizing current path lengths, and implementing advanced routing techniques to enhance power integrity. The optimization process often involves simulation-based verification to ensure that the power delivery network meets the stringent requirements of high-bandwidth memory systems.- HBM4 Power Delivery Network Design Optimization: High Bandwidth Memory (HBM4) power delivery networks require careful design optimization to manage inductance issues. This includes strategic placement of power and ground planes, minimizing trace lengths, and implementing advanced routing techniques to reduce parasitic inductance. These design considerations help maintain signal integrity and power stability in high-performance computing applications that utilize HBM4 technology.

- Inductance Reduction Techniques in HBM4 Implementations: Various techniques can be employed to reduce inductance in HBM4 power delivery networks, including the use of decoupling capacitors, interposer technology, and advanced packaging solutions. These methods help minimize power supply noise, improve signal integrity, and enhance overall system performance by controlling the parasitic inductance that can negatively impact high-speed memory operations.

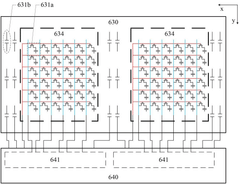

- 3D Integration and Interposer Solutions for HBM4: Three-dimensional integration and silicon interposer technologies are crucial for managing inductance in HBM4 power delivery networks. These approaches enable shorter vertical connections between memory stacks and processing units, significantly reducing the path length and associated inductance. Advanced interposer designs incorporate embedded capacitance and optimized power distribution to further mitigate inductance-related performance issues.

- Power Integrity Analysis for HBM4 Systems: Comprehensive power integrity analysis is essential for HBM4 implementations to identify and address inductance-related challenges. This includes simulation of power delivery networks, impedance profiling, and resonance analysis to ensure stable power delivery under various operating conditions. Advanced modeling techniques help designers predict and mitigate potential inductance issues before physical implementation.

- Thermal Management and Inductance Considerations in HBM4: Thermal management solutions for HBM4 must be designed with inductance considerations in mind. Heat dissipation structures can affect the electrical characteristics of power delivery networks, potentially introducing additional inductance. Integrated cooling solutions that maintain electrical performance while addressing thermal challenges are critical for high-performance HBM4 implementations, especially in data center and AI applications.

02 Inductance Reduction Techniques in HBM4 Implementations

Various techniques are employed to reduce inductance in HBM4 power delivery networks, including the use of decoupling capacitors, interposer technologies, and specialized packaging solutions. These methods help minimize voltage fluctuations and signal integrity issues in high-speed memory interfaces. Advanced materials and component placement strategies are also utilized to achieve lower inductance values and improve overall system performance.Expand Specific Solutions03 Power Integrity Analysis for HBM4 Systems

Comprehensive power integrity analysis is essential for HBM4 implementations to address inductance-related challenges. This involves advanced modeling techniques, electromagnetic simulations, and impedance analysis to identify potential issues in the power delivery network. The analysis typically includes evaluation of power/ground bounce, resonance effects, and transient response characteristics to ensure reliable operation under various loading conditions.Expand Specific Solutions04 3D Integration Technologies for HBM4 Power Delivery

Three-dimensional integration technologies offer significant advantages for HBM4 power delivery networks by enabling shorter vertical interconnects with reduced inductance. These technologies include through-silicon vias (TSVs), silicon interposers, and advanced packaging solutions that facilitate more efficient power distribution. The vertical integration approach helps minimize the physical distance between power sources and memory components, thereby reducing parasitic inductance.Expand Specific Solutions05 Electromagnetic Interference Management in HBM4 Systems

Managing electromagnetic interference is crucial in HBM4 power delivery networks to prevent inductance-related issues. This involves implementing shielding techniques, optimizing ground plane designs, and utilizing specialized filtering components to mitigate noise coupling. Advanced signal integrity solutions are also employed to ensure clean power delivery and minimize the impact of electromagnetic interference on high-speed memory operations.Expand Specific Solutions

Key Industry Players in HBM4 Ecosystem

The HBM4 Power Delivery Networks market is currently in an early growth phase, characterized by increasing demand for high-performance computing solutions requiring advanced memory interfaces. The market is projected to expand significantly as data centers, AI applications, and high-performance computing systems drive adoption. From a technical maturity perspective, the field is evolving rapidly with key players developing innovative approaches to inductance control and decoupling capacitor strategies. Intel, Micron Technology, and Qualcomm are leading semiconductor manufacturers advancing core technologies, while specialized interconnect providers like Molex contribute critical connection solutions. Research institutions including Xidian University, RWTH Aachen, and Industrial Technology Research Institute are pushing theoretical boundaries. The competitive landscape features collaboration between memory manufacturers, semiconductor companies, and research organizations to overcome the significant power delivery challenges inherent in next-generation HBM implementations.

Intel Corp.

Technical Solution: Intel's HBM4 power delivery network solution focuses on advanced inductance control through multi-layered silicon interposers with embedded capacitors. Their approach utilizes a combination of on-package and on-die decoupling capacitors strategically placed to minimize power distribution network (PDN) impedance. Intel has developed proprietary Through-Silicon Via (TSV) technology with reduced parasitic inductance, achieving sub-100pH values for critical power paths. Their decap strategy implements a hierarchical structure with deep trench capacitors on die, thin-film capacitors in the interposer, and high-density MLP (Multi-Layer Polymer) capacitors on package. Intel's PDN design incorporates advanced power modeling techniques that account for transient voltage droop under various workloads, ensuring stable voltage delivery even during peak computing demands. Recent implementations have demonstrated up to 40% reduction in PDN impedance compared to HBM3 solutions, enabling higher bandwidth operation while maintaining power integrity.

Strengths: Intel's extensive manufacturing infrastructure allows for tight integration between chip design and packaging technologies, enabling optimized PDN solutions. Their advanced modeling capabilities provide accurate power integrity simulations. Weaknesses: The complex multi-layer interposer technology increases manufacturing costs and may present yield challenges at high volume production.

Micron Technology, Inc.

Technical Solution: Micron's approach to HBM4 power delivery networks centers on their innovative "distributed power architecture" that disperses power delivery components throughout the memory stack. Their solution incorporates ultra-thin power distribution layers within the HBM stack itself, reducing the distance between power sources and consumption points. Micron has developed specialized low-inductance microbumps with <50pH inductance values for critical power connections between dies. Their decoupling strategy employs a multi-tiered approach with high-frequency MIMCAP (Metal-Insulator-Metal Capacitor) arrays integrated directly into memory dies, complemented by mid-frequency ceramic capacitors in the interposer layer. Micron's PDN design also features adaptive power management that dynamically adjusts decoupling capacitance based on real-time memory access patterns, optimizing power efficiency while maintaining signal integrity. Their latest test vehicles have demonstrated stable power delivery at frequencies exceeding 5GHz with voltage ripple maintained below 3% even during worst-case switching scenarios.

Strengths: Micron's vertical integration in memory manufacturing allows for customized power delivery solutions optimized specifically for memory workloads. Their distributed architecture minimizes power delivery distance. Weaknesses: The complex die stacking with integrated power components increases manufacturing complexity and may impact thermal management in high-performance applications.

Critical Patents and Research on HBM4 PDN Design

Memory and its stacking structure and logic chip stacking

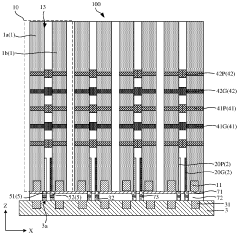

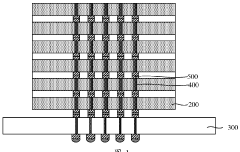

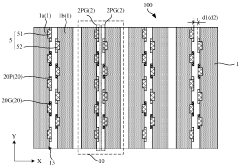

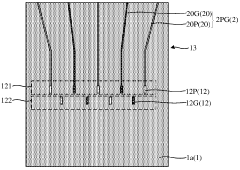

PatentPendingCN120456565A

Innovation

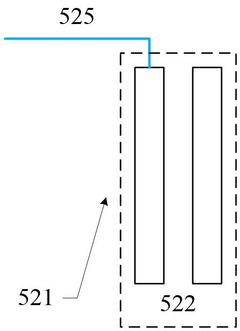

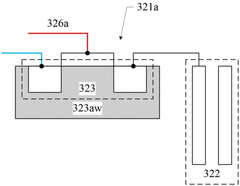

- The structure of stacking the magazine capacitor array chip and the logic chip is adopted. By connecting the magazine capacitor cells arranged in an array in the magazine capacitor array chip on the physical layer of the logic chip, the settings of the capacitors in the logic chip are reduced or eliminated.

Semiconductor structure, manufacturing method for semiconductor structure, and semiconductor device

PatentWO2024031774A1

Innovation

- Multiple memory chips are stacked in parallel on the upper surface of the logic chip. Wired power supply is realized through the electrical connection between the power supply wiring layer and the power supply signal line. The power supply is connected to the power supply port through welding bumps to simplify the power supply path to improve stability.

Thermal Management Considerations for HBM4 PDN

Thermal management represents a critical aspect of HBM4 Power Delivery Network (PDN) design due to the increased power density and performance requirements. As HBM4 technology pushes memory bandwidth boundaries beyond previous generations, the thermal challenges associated with power delivery become increasingly significant constraints on system performance and reliability.

The thermal characteristics of HBM4 PDN components directly impact inductance control strategies. Higher operating temperatures increase conductor resistance, which can degrade power integrity and signal quality. This temperature-dependent resistance variation must be accounted for when designing inductance control mechanisms, particularly in high-current paths where I²R losses are substantial.

Decoupling capacitor (decap) performance is notably affected by thermal conditions. Most ceramic capacitors exhibit significant capacitance degradation at elevated temperatures, potentially reducing their effectiveness in mitigating power supply noise. Strategic placement of decaps must therefore consider not only electrical parameters but also thermal gradients across the PDN structure.

Heat dissipation pathways require careful engineering in HBM4 implementations. The 3D stacked architecture creates thermal bottlenecks that can lead to hotspots, particularly at interposer connections where current density is highest. Advanced thermal interface materials (TIMs) with optimized thermal conductivity are essential between the HBM4 stack and heat spreading solutions.

Liquid cooling solutions are increasingly being considered for high-performance HBM4 applications. Direct liquid cooling of interposers can significantly reduce thermal resistance, allowing for more aggressive power delivery designs with lower inductance paths that would otherwise generate prohibitive heat levels under conventional cooling approaches.

Thermal-aware PDN simulation has become mandatory in the HBM4 design process. Coupled electro-thermal models must accurately predict temperature distributions resulting from various power delivery scenarios, enabling designers to identify potential reliability issues before physical implementation.

Temperature monitoring and dynamic thermal management systems represent another crucial consideration. Embedding temperature sensors within critical PDN components allows for real-time adjustment of memory operation parameters, potentially extending the operational envelope of HBM4 systems while maintaining reliability targets.

The interplay between thermal management and signal integrity presents unique challenges. Thermal expansion and contraction cycles can affect connection reliability at interposer interfaces, potentially increasing parasitic inductance over time. Materials with matched coefficients of thermal expansion must be selected to minimize these effects throughout the expected operational temperature range.

The thermal characteristics of HBM4 PDN components directly impact inductance control strategies. Higher operating temperatures increase conductor resistance, which can degrade power integrity and signal quality. This temperature-dependent resistance variation must be accounted for when designing inductance control mechanisms, particularly in high-current paths where I²R losses are substantial.

Decoupling capacitor (decap) performance is notably affected by thermal conditions. Most ceramic capacitors exhibit significant capacitance degradation at elevated temperatures, potentially reducing their effectiveness in mitigating power supply noise. Strategic placement of decaps must therefore consider not only electrical parameters but also thermal gradients across the PDN structure.

Heat dissipation pathways require careful engineering in HBM4 implementations. The 3D stacked architecture creates thermal bottlenecks that can lead to hotspots, particularly at interposer connections where current density is highest. Advanced thermal interface materials (TIMs) with optimized thermal conductivity are essential between the HBM4 stack and heat spreading solutions.

Liquid cooling solutions are increasingly being considered for high-performance HBM4 applications. Direct liquid cooling of interposers can significantly reduce thermal resistance, allowing for more aggressive power delivery designs with lower inductance paths that would otherwise generate prohibitive heat levels under conventional cooling approaches.

Thermal-aware PDN simulation has become mandatory in the HBM4 design process. Coupled electro-thermal models must accurately predict temperature distributions resulting from various power delivery scenarios, enabling designers to identify potential reliability issues before physical implementation.

Temperature monitoring and dynamic thermal management systems represent another crucial consideration. Embedding temperature sensors within critical PDN components allows for real-time adjustment of memory operation parameters, potentially extending the operational envelope of HBM4 systems while maintaining reliability targets.

The interplay between thermal management and signal integrity presents unique challenges. Thermal expansion and contraction cycles can affect connection reliability at interposer interfaces, potentially increasing parasitic inductance over time. Materials with matched coefficients of thermal expansion must be selected to minimize these effects throughout the expected operational temperature range.

Signal Integrity and EMI Mitigation Techniques

Signal integrity and electromagnetic interference (EMI) are critical concerns in HBM4 Power Delivery Networks (PDNs) due to the high-speed data transmission and dense integration. As frequencies increase in HBM4 systems, maintaining signal quality while minimizing interference becomes increasingly challenging.

The primary signal integrity challenges in HBM4 PDNs stem from impedance discontinuities, crosstalk between adjacent channels, and reflection issues. These problems are exacerbated by the reduced spacing between interconnects and the higher operating frequencies. Advanced simulation tools utilizing 3D electromagnetic field solvers have become essential for predicting and mitigating these issues during the design phase.

Differential signaling techniques have proven effective in improving signal integrity within HBM4 systems. By transmitting complementary signals through paired conductors, common-mode noise can be significantly reduced. This approach, combined with careful impedance matching and trace length equalization, helps maintain signal quality across the complex PDN structure.

For EMI mitigation, strategic shielding implementations have shown promising results. Embedded Faraday cages within the substrate layers can isolate sensitive components from electromagnetic radiation. Additionally, the placement of guard traces between high-speed signal paths helps minimize crosstalk and contains electromagnetic fields within designated areas.

Decoupling capacitor placement strategies play a dual role in both power integrity and EMI suppression. Beyond their primary function of stabilizing voltage levels, properly distributed decoupling capacitors create low-impedance paths for high-frequency noise, effectively reducing EMI radiation. Multi-layer ceramic capacitors (MLCCs) with low equivalent series inductance (ESL) have demonstrated superior performance in this application.

Advanced materials with enhanced electromagnetic properties are being explored to further improve signal integrity. Low-loss dielectrics and engineered substrates with controlled permittivity can significantly reduce signal degradation. Meanwhile, specialized via structures with optimized geometries help maintain signal integrity through layer transitions while minimizing unwanted radiation.

Time-domain reflectometry (TDR) and vector network analysis (VNA) techniques have become standard practices for validating signal integrity in HBM4 PDNs. These measurement methodologies enable precise characterization of impedance profiles and identification of potential signal integrity issues before final implementation.

The primary signal integrity challenges in HBM4 PDNs stem from impedance discontinuities, crosstalk between adjacent channels, and reflection issues. These problems are exacerbated by the reduced spacing between interconnects and the higher operating frequencies. Advanced simulation tools utilizing 3D electromagnetic field solvers have become essential for predicting and mitigating these issues during the design phase.

Differential signaling techniques have proven effective in improving signal integrity within HBM4 systems. By transmitting complementary signals through paired conductors, common-mode noise can be significantly reduced. This approach, combined with careful impedance matching and trace length equalization, helps maintain signal quality across the complex PDN structure.

For EMI mitigation, strategic shielding implementations have shown promising results. Embedded Faraday cages within the substrate layers can isolate sensitive components from electromagnetic radiation. Additionally, the placement of guard traces between high-speed signal paths helps minimize crosstalk and contains electromagnetic fields within designated areas.

Decoupling capacitor placement strategies play a dual role in both power integrity and EMI suppression. Beyond their primary function of stabilizing voltage levels, properly distributed decoupling capacitors create low-impedance paths for high-frequency noise, effectively reducing EMI radiation. Multi-layer ceramic capacitors (MLCCs) with low equivalent series inductance (ESL) have demonstrated superior performance in this application.

Advanced materials with enhanced electromagnetic properties are being explored to further improve signal integrity. Low-loss dielectrics and engineered substrates with controlled permittivity can significantly reduce signal degradation. Meanwhile, specialized via structures with optimized geometries help maintain signal integrity through layer transitions while minimizing unwanted radiation.

Time-domain reflectometry (TDR) and vector network analysis (VNA) techniques have become standard practices for validating signal integrity in HBM4 PDNs. These measurement methodologies enable precise characterization of impedance profiles and identification of potential signal integrity issues before final implementation.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!