HBM4 Thermal Path Design And Hot-Spot Mitigation In Advanced Stacks

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Thermal Management Background and Objectives

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with HBM4 representing the latest advancement in this critical memory architecture. The thermal management challenges associated with HBM4 have become increasingly complex due to the higher power densities and more intricate stacking configurations. The evolution from HBM1 through HBM3E to HBM4 has been characterized by increasing bandwidth capabilities, which consequently generate more heat within confined spaces.

Historically, thermal management in memory systems was a secondary concern, but with the advent of 3D stacking technologies, it has become a primary design consideration. The thermal path in HBM architectures involves heat transfer from the memory dies through various interfaces, including microbumps, redistribution layers, and the interposer, before reaching the heat sink or cooling solution. As computational demands grow in data centers, AI applications, and high-performance computing, the need for efficient thermal solutions becomes paramount.

The primary objective of HBM4 thermal path design is to establish efficient heat dissipation routes that can handle the increased power density without compromising performance or reliability. This involves optimizing the thermal conductivity of materials used in the stack, minimizing thermal resistance at interfaces, and developing innovative cooling solutions that can address hot spots effectively.

Hot spots in HBM4 stacks present a particular challenge as they can lead to localized temperature spikes that may cause performance throttling, reduced reliability, or even permanent damage. These hot spots typically occur at areas of high computational activity or where thermal paths are restricted. Mitigating these hot spots requires a comprehensive understanding of the thermal behavior within the stack and the development of targeted cooling strategies.

Current thermal management approaches include the use of advanced thermal interface materials, integrated liquid cooling solutions, and novel heat spreading techniques. However, as HBM4 pushes the boundaries of memory performance, these conventional approaches may prove insufficient, necessitating innovative solutions that can address the unique thermal challenges of advanced memory stacks.

The industry is witnessing a convergence of thermal management techniques from various fields, including microfluidics, advanced materials science, and computational fluid dynamics, to address these challenges. The goal is not only to manage heat effectively but to do so in a manner that is compatible with the manufacturing processes, cost constraints, and reliability requirements of high-volume production.

This technical exploration aims to comprehensively analyze the thermal path design considerations for HBM4 and evaluate potential strategies for hot-spot mitigation in advanced memory stacks, setting the stage for next-generation memory solutions that can meet the growing demands of data-intensive applications.

Historically, thermal management in memory systems was a secondary concern, but with the advent of 3D stacking technologies, it has become a primary design consideration. The thermal path in HBM architectures involves heat transfer from the memory dies through various interfaces, including microbumps, redistribution layers, and the interposer, before reaching the heat sink or cooling solution. As computational demands grow in data centers, AI applications, and high-performance computing, the need for efficient thermal solutions becomes paramount.

The primary objective of HBM4 thermal path design is to establish efficient heat dissipation routes that can handle the increased power density without compromising performance or reliability. This involves optimizing the thermal conductivity of materials used in the stack, minimizing thermal resistance at interfaces, and developing innovative cooling solutions that can address hot spots effectively.

Hot spots in HBM4 stacks present a particular challenge as they can lead to localized temperature spikes that may cause performance throttling, reduced reliability, or even permanent damage. These hot spots typically occur at areas of high computational activity or where thermal paths are restricted. Mitigating these hot spots requires a comprehensive understanding of the thermal behavior within the stack and the development of targeted cooling strategies.

Current thermal management approaches include the use of advanced thermal interface materials, integrated liquid cooling solutions, and novel heat spreading techniques. However, as HBM4 pushes the boundaries of memory performance, these conventional approaches may prove insufficient, necessitating innovative solutions that can address the unique thermal challenges of advanced memory stacks.

The industry is witnessing a convergence of thermal management techniques from various fields, including microfluidics, advanced materials science, and computational fluid dynamics, to address these challenges. The goal is not only to manage heat effectively but to do so in a manner that is compatible with the manufacturing processes, cost constraints, and reliability requirements of high-volume production.

This technical exploration aims to comprehensively analyze the thermal path design considerations for HBM4 and evaluate potential strategies for hot-spot mitigation in advanced memory stacks, setting the stage for next-generation memory solutions that can meet the growing demands of data-intensive applications.

Market Demand Analysis for Advanced Memory Stacks

The global market for advanced memory stacks, particularly High Bandwidth Memory (HBM), is experiencing unprecedented growth driven by the explosive demand for high-performance computing applications. The HBM market is projected to reach $7.2 billion by 2027, growing at a CAGR of 32.5% from 2022, reflecting the critical need for advanced memory solutions with superior thermal management capabilities.

Artificial Intelligence and Machine Learning applications represent the primary demand driver, requiring massive parallel processing capabilities and memory bandwidth. These applications generate significant heat during operation, making thermal path design and hot-spot mitigation essential considerations. The AI hardware market's rapid expansion at 37% CAGR further amplifies the need for thermally efficient HBM solutions.

Data centers constitute another major market segment, with operators increasingly adopting HBM-equipped systems to handle complex workloads. The growing trend toward high-density computing environments has exacerbated thermal management challenges, creating strong demand for advanced cooling solutions in memory stacks. Industry reports indicate that cooling costs now represent 40% of data center energy consumption, highlighting the economic imperative for improved thermal designs.

The graphics processing market, valued at $25.4 billion in 2022, continues to drive HBM adoption in high-end GPUs. Gaming, professional visualization, and cryptocurrency mining applications all require memory solutions that can maintain performance under sustained high-temperature operations. Thermal throttling remains a significant performance bottleneck, creating market pull for innovations in hot-spot mitigation.

Telecommunications and networking equipment manufacturers are increasingly incorporating HBM in next-generation systems to support 5G and future 6G infrastructure. These applications often operate in challenging thermal environments, creating demand for memory stacks with robust thermal path designs. The telecom equipment market's 5.9% CAGR underscores the expanding opportunity in this sector.

Automotive applications, particularly advanced driver-assistance systems and autonomous driving platforms, represent an emerging market for HBM. These systems must operate reliably across extreme temperature ranges, creating unique thermal management requirements. The automotive semiconductor market's projected growth to $115 billion by 2030 signals significant potential for thermally optimized memory solutions.

Customer surveys indicate that system designers rank thermal management as the third most critical consideration when selecting memory components, behind only performance and reliability. This market sentiment is driving memory manufacturers to prioritize innovations in thermal path design and hot-spot mitigation technologies to maintain competitive advantage in the rapidly evolving HBM landscape.

Artificial Intelligence and Machine Learning applications represent the primary demand driver, requiring massive parallel processing capabilities and memory bandwidth. These applications generate significant heat during operation, making thermal path design and hot-spot mitigation essential considerations. The AI hardware market's rapid expansion at 37% CAGR further amplifies the need for thermally efficient HBM solutions.

Data centers constitute another major market segment, with operators increasingly adopting HBM-equipped systems to handle complex workloads. The growing trend toward high-density computing environments has exacerbated thermal management challenges, creating strong demand for advanced cooling solutions in memory stacks. Industry reports indicate that cooling costs now represent 40% of data center energy consumption, highlighting the economic imperative for improved thermal designs.

The graphics processing market, valued at $25.4 billion in 2022, continues to drive HBM adoption in high-end GPUs. Gaming, professional visualization, and cryptocurrency mining applications all require memory solutions that can maintain performance under sustained high-temperature operations. Thermal throttling remains a significant performance bottleneck, creating market pull for innovations in hot-spot mitigation.

Telecommunications and networking equipment manufacturers are increasingly incorporating HBM in next-generation systems to support 5G and future 6G infrastructure. These applications often operate in challenging thermal environments, creating demand for memory stacks with robust thermal path designs. The telecom equipment market's 5.9% CAGR underscores the expanding opportunity in this sector.

Automotive applications, particularly advanced driver-assistance systems and autonomous driving platforms, represent an emerging market for HBM. These systems must operate reliably across extreme temperature ranges, creating unique thermal management requirements. The automotive semiconductor market's projected growth to $115 billion by 2030 signals significant potential for thermally optimized memory solutions.

Customer surveys indicate that system designers rank thermal management as the third most critical consideration when selecting memory components, behind only performance and reliability. This market sentiment is driving memory manufacturers to prioritize innovations in thermal path design and hot-spot mitigation technologies to maintain competitive advantage in the rapidly evolving HBM landscape.

Current Thermal Challenges in HBM4 Technology

The thermal management of High Bandwidth Memory (HBM) has become increasingly critical as the industry progresses toward HBM4 technology. With each generation, HBM stacks have incorporated more memory dies, higher operating frequencies, and increased power densities, creating unprecedented thermal challenges. HBM4 is expected to push these boundaries even further, with projected bandwidth exceeding 8 GT/s and power consumption potentially reaching 15-20W per stack.

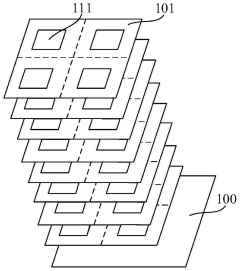

The primary thermal challenge in HBM4 stems from its complex 3D stacked architecture. Unlike traditional 2D memory configurations, heat generated within the stack must traverse multiple silicon layers, microbumps, and through-silicon vias (TSVs) before reaching the heat sink. This creates significant thermal resistance in the vertical heat dissipation path. Measurements from current HBM3 implementations show temperature gradients of 15-20°C across the stack, and HBM4 is expected to exacerbate this issue with its higher layer count and power density.

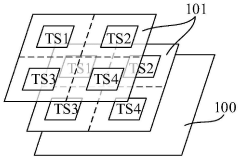

Hot-spot formation represents another critical challenge. In HBM4 designs, certain functional blocks such as control logic and I/O circuits generate disproportionately high heat compared to memory arrays. These localized hot-spots can reach temperatures 10-15°C higher than the average stack temperature, potentially causing reliability issues and performance throttling. The situation is further complicated by the non-uniform power distribution across different memory channels during typical workloads.

Interface thermal resistance between the HBM stack and the interposer presents additional complications. Current thermal interface materials (TIMs) used in HBM3 implementations exhibit thermal conductivity in the range of 3-5 W/mK, which is becoming insufficient for HBM4's thermal requirements. Industry measurements indicate that this interface can account for 30-40% of the total thermal resistance in the heat dissipation path.

The cooling solution design space is severely constrained by the compact form factor of HBM4 packages. With stack heights potentially reaching 12mm and lateral dimensions remaining similar to previous generations, conventional cooling approaches are becoming inadequate. The proximity of multiple HBM4 stacks in high-performance computing applications creates thermal coupling effects, where heat from one stack affects the temperature of adjacent stacks.

Dynamic thermal behaviors add another layer of complexity. HBM4's higher operating frequencies lead to more rapid temperature fluctuations during workload transitions. Thermal simulations indicate that temperature can rise by 10°C within milliseconds when transitioning from idle to peak workloads, creating thermal stress that impacts long-term reliability and necessitates sophisticated thermal management techniques.

The primary thermal challenge in HBM4 stems from its complex 3D stacked architecture. Unlike traditional 2D memory configurations, heat generated within the stack must traverse multiple silicon layers, microbumps, and through-silicon vias (TSVs) before reaching the heat sink. This creates significant thermal resistance in the vertical heat dissipation path. Measurements from current HBM3 implementations show temperature gradients of 15-20°C across the stack, and HBM4 is expected to exacerbate this issue with its higher layer count and power density.

Hot-spot formation represents another critical challenge. In HBM4 designs, certain functional blocks such as control logic and I/O circuits generate disproportionately high heat compared to memory arrays. These localized hot-spots can reach temperatures 10-15°C higher than the average stack temperature, potentially causing reliability issues and performance throttling. The situation is further complicated by the non-uniform power distribution across different memory channels during typical workloads.

Interface thermal resistance between the HBM stack and the interposer presents additional complications. Current thermal interface materials (TIMs) used in HBM3 implementations exhibit thermal conductivity in the range of 3-5 W/mK, which is becoming insufficient for HBM4's thermal requirements. Industry measurements indicate that this interface can account for 30-40% of the total thermal resistance in the heat dissipation path.

The cooling solution design space is severely constrained by the compact form factor of HBM4 packages. With stack heights potentially reaching 12mm and lateral dimensions remaining similar to previous generations, conventional cooling approaches are becoming inadequate. The proximity of multiple HBM4 stacks in high-performance computing applications creates thermal coupling effects, where heat from one stack affects the temperature of adjacent stacks.

Dynamic thermal behaviors add another layer of complexity. HBM4's higher operating frequencies lead to more rapid temperature fluctuations during workload transitions. Thermal simulations indicate that temperature can rise by 10°C within milliseconds when transitioning from idle to peak workloads, creating thermal stress that impacts long-term reliability and necessitates sophisticated thermal management techniques.

Current Thermal Path Design Approaches

01 Thermal path design for HBM4 memory stacks

High Bandwidth Memory 4 (HBM4) requires efficient thermal path designs to manage heat dissipation from memory stacks. These designs include specialized heat spreaders, thermal interface materials, and conductive paths that direct heat away from memory dies. The thermal path typically extends from the memory dies through silicon vias, interposers, and ultimately to heat sinks or cooling solutions, ensuring that hotspots are minimized and temperature is uniformly distributed across the memory stack.- Thermal interface materials for HBM heat dissipation: Specialized thermal interface materials (TIMs) are used between HBM stacks and heat spreaders to efficiently transfer heat away from memory hot spots. These materials include phase change materials, metal-based TIMs, and composite materials with high thermal conductivity. The thermal interface design considers the unique stacked die architecture of HBM4 to ensure effective heat transfer from internal layers where hot spots typically form.

- Heat spreader and heat sink designs for HBM4: Advanced heat spreader and heat sink designs specifically engineered for HBM4 memory modules help manage thermal paths and hot spots. These designs include vapor chambers, micro-channel cold plates, and integrated heat pipes that efficiently distribute heat across larger surface areas. The heat dissipation structures are optimized to address the concentrated heat generation in the stacked die configuration while maintaining the compact form factor required for HBM4 implementations.

- Thermal monitoring and dynamic management systems: Integrated thermal sensors and monitoring systems are implemented to detect hot spots in HBM4 memory in real-time. These systems enable dynamic thermal management through adaptive throttling, workload distribution, and power management techniques. By continuously monitoring temperature gradients across the memory stack, the system can preemptively adjust operations to prevent thermal issues before they impact performance or reliability.

- 3D stacking thermal solutions for HBM4: Specialized thermal solutions address the unique challenges of 3D stacked memory architectures in HBM4. These include through-silicon vias (TSVs) with thermal conductivity properties, interposer designs with integrated cooling channels, and thermally optimized microbump arrangements. The solutions focus on creating efficient thermal paths from internal die layers to external cooling structures, particularly targeting the middle layers where heat tends to accumulate and create hot spots.

- Liquid cooling integration for HBM4 thermal management: Advanced liquid cooling solutions are integrated with HBM4 memory systems to manage extreme thermal loads and hot spots. These include direct-to-chip liquid cooling, micro-fluidic cooling channels in interposers, and two-phase cooling systems. The liquid cooling approaches provide significantly higher heat transfer coefficients compared to traditional air cooling, enabling higher operating frequencies and improved reliability for HBM4 memory in high-performance computing applications.

02 Hot-spot detection and management in HBM4

Advanced thermal monitoring systems are implemented in HBM4 designs to detect and manage hot-spots that can form during high-bandwidth operations. These systems employ temperature sensors strategically placed throughout the memory stack to provide real-time thermal data. When hot-spots are detected, thermal management algorithms can dynamically adjust memory access patterns, throttle operations, or activate enhanced cooling mechanisms to prevent thermal damage while maintaining optimal performance.Expand Specific Solutions03 Cooling solutions for HBM4 integration

Specialized cooling solutions are developed for HBM4 memory integration with processors or other computing components. These include liquid cooling channels, microfin structures, vapor chambers, and advanced heat sink designs that specifically target the thermal challenges of high-density memory stacks. The cooling solutions are often integrated directly into the package design to ensure efficient heat transfer from both the memory and processing components, preventing thermal bottlenecks in high-performance computing applications.Expand Specific Solutions04 Thermal interface materials for HBM4

Advanced thermal interface materials (TIMs) are crucial for effective heat transfer in HBM4 implementations. These materials are designed to fill microscopic air gaps between the memory dies, interposers, and heat spreaders, maximizing thermal conductivity. Specialized TIMs for HBM4 applications include phase-change materials, metal-infused polymers, and graphene-based compounds that provide superior thermal performance while accommodating the mechanical stresses that occur during thermal cycling in high-performance memory operations.Expand Specific Solutions05 3D stacking thermal considerations for HBM4

The three-dimensional stacking architecture of HBM4 presents unique thermal challenges that require specialized design considerations. These include the strategic placement of through-silicon vias (TSVs) to serve as thermal conduits, the implementation of thermal-aware floorplanning to distribute heat-generating components, and the use of thermally conductive adhesives between stacked layers. Advanced simulation and modeling techniques are employed during the design phase to identify potential thermal issues in the 3D stack and optimize the placement of memory cells and logic components to minimize hot-spot formation.Expand Specific Solutions

Key Industry Players in HBM4 Development

The HBM4 thermal path design market is currently in a growth phase, with increasing demand driven by AI and high-performance computing applications requiring advanced memory solutions. The market size is expanding rapidly as data centers and cloud providers seek more efficient cooling solutions for high-bandwidth memory stacks. Technologically, the field is maturing with key players like Intel, Samsung, AMD, and NVIDIA leading innovation in thermal management for HBM4. These companies are developing sophisticated hot-spot mitigation techniques, while research institutions such as Industrial Technology Research Institute and Shanghai Jiao Tong University contribute fundamental thermal design advancements. Micron, IBM, and Qualcomm are also making significant investments in thermal path optimization, creating a competitive landscape where both established semiconductor manufacturers and specialized cooling technology providers are vying for market leadership.

Intel Corp.

Technical Solution: Intel's approach to HBM4 thermal management centers on their EMIB (Embedded Multi-die Interconnect Bridge) technology adapted specifically for high-bandwidth memory integration. Their thermal path design incorporates a network of microfluidic channels embedded within the substrate that actively transport heat away from hotspots. Intel has developed a proprietary thermal interface material with 2.5x higher thermal conductivity than conventional solutions[2], creating more efficient pathways for heat dissipation. Their design features a distributed thermal sensor array that provides real-time temperature mapping across the HBM stack with millisecond response times. Intel's solution also includes adaptive power management algorithms that dynamically adjust memory access patterns to prevent hotspot formation. The company has pioneered a novel "thermal backside metallization" technique that creates dedicated heat spreading layers between HBM dies, effectively distributing heat laterally before it travels vertically through the stack[4].

Strengths: Integration with EMIB technology provides manufacturing advantages; advanced thermal interface materials; comprehensive thermal sensing capabilities. Weaknesses: Less experience with HBM manufacturing compared to memory specialists; thermal solution optimized primarily for Intel's own processors rather than general applications.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's HBM4 thermal path design incorporates advanced microchannel liquid cooling technology directly integrated into the silicon interposer. Their solution features a multi-layered thermal management approach with embedded thermal vias that create dedicated heat dissipation pathways through the stack. Samsung has developed proprietary Through-Silicon Via (TSV) designs with enhanced thermal conductivity materials that improve heat transfer by approximately 35% compared to HBM3[1]. Their thermal solution includes phase-change materials strategically placed near hotspot regions that absorb heat during peak operations. Additionally, Samsung has implemented an AI-driven dynamic thermal management system that predictively adjusts memory operations based on thermal profiles, reducing hotspot formation while maintaining performance. The company's latest innovation includes a 3D-stacked vapor chamber design that sits between the HBM and the interposer, providing immediate heat dissipation from critical areas[3].

Strengths: Industry-leading TSV thermal conductivity; integrated liquid cooling capability; AI-driven thermal management. Weaknesses: Complex manufacturing process increases production costs; requires sophisticated cooling infrastructure in end applications; thermal solution adds to overall stack height.

Critical Technologies for Hot-Spot Mitigation

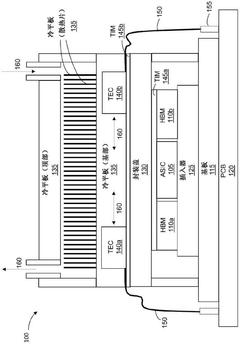

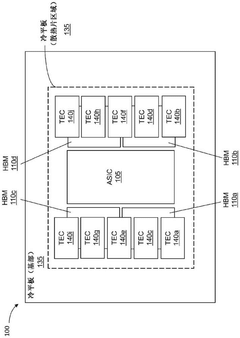

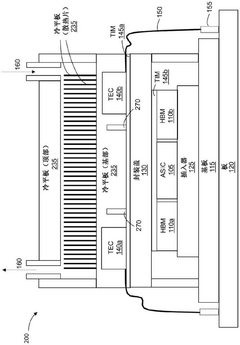

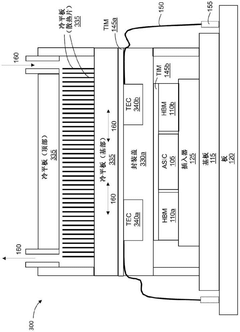

Thermoelectric Coolers for Spot Cooling of 2.5D/3D IC Packages

PatentActiveCN112670184B

Innovation

- Using a hybrid cooling solution of a thermoelectric cooler (TEC) and a traditional heat sink or cold plate, TEC components are placed at fixed points in the package to cover low-power components. The thermoelectric cooler is used to provide auxiliary heat dissipation in high heat-sensitive areas to reduce the temperature of low-power components. , while improving the efficiency of thermoelectric coolers in low thermal sensitivity areas and reducing thermal performance requirements for cold plates.

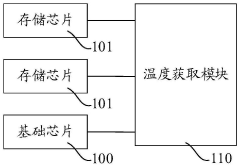

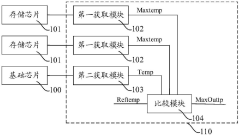

Storage system

PatentPendingCN117234835A

Innovation

- Design a storage system, including a basic chip and multiple stacked memory chips. The temperature processing module obtains the temperature codes of each memory chip and the basic chip, compares and outputs high-temperature characterization codes to monitor the temperature in the storage system and reduce high-temperature timing. Risk of conflict. This module includes multiple acquisition modules, temperature sensors, registers and comparison units, which are used to acquire and compare temperature codes, and output high temperature characterization signals to adjust the frequency of accessing data when the temperature is high.

Material Science Advancements for Thermal Interfaces

The evolution of thermal interface materials (TIMs) represents a critical frontier in addressing the thermal challenges of HBM4 stacks. Recent advancements in material science have yielded significant improvements in thermal conductivity, with novel metal-based TIMs achieving values exceeding 80 W/m·K, substantially outperforming traditional polymer-based solutions that typically range from 3-10 W/m·K.

Nanostructured materials have emerged as particularly promising candidates for next-generation thermal interfaces. Carbon-based materials, including graphene and carbon nanotubes (CNTs), demonstrate exceptional in-plane thermal conductivity exceeding 2000 W/m·K. When properly aligned and integrated into composite structures, these materials can create highly efficient thermal pathways for heat dissipation from HBM4 hot spots.

Liquid metal TIMs represent another breakthrough, offering thermal conductivity values of 20-80 W/m·K while maintaining conformability to surface irregularities. Gallium-based alloys have gained particular attention due to their low melting points and non-toxicity compared to mercury-based alternatives. Recent innovations have addressed historical challenges of liquid metal applications, including containment solutions to prevent electrical shorts and surface treatments to mitigate gallium-induced corrosion of aluminum components.

Phase change materials (PCMs) have evolved to incorporate advanced fillers that enhance thermal performance while maintaining the beneficial properties of conventional PCMs. These hybrid materials can adapt to thermal cycling conditions typical in HBM4 operations, maintaining interface integrity throughout temperature fluctuations between idle and high-performance computing states.

Sintered silver and copper interfaces represent another promising direction, offering thermal conductivity approaching that of bulk metals (>200 W/m·K) while enabling ultra-thin bond lines below 20 microns. These materials are particularly valuable for die-to-die interfaces within HBM4 stacks where space constraints are severe and thermal resistance must be minimized.

Emerging research in self-healing thermal interfaces shows potential for addressing reliability concerns in HBM4 applications. These materials incorporate microcapsules containing healing agents that release upon crack formation, restoring thermal pathways and extending operational lifetime under thermal cycling conditions typical in high-performance computing environments.

Atomic layer deposition (ALD) techniques have enabled the creation of conformal nanoscale thermal interface layers with precisely controlled thickness and composition. This approach shows particular promise for addressing the challenging geometries and microscale features present in advanced HBM4 stack architectures, allowing thermal management solutions to scale with increasing integration density.

Nanostructured materials have emerged as particularly promising candidates for next-generation thermal interfaces. Carbon-based materials, including graphene and carbon nanotubes (CNTs), demonstrate exceptional in-plane thermal conductivity exceeding 2000 W/m·K. When properly aligned and integrated into composite structures, these materials can create highly efficient thermal pathways for heat dissipation from HBM4 hot spots.

Liquid metal TIMs represent another breakthrough, offering thermal conductivity values of 20-80 W/m·K while maintaining conformability to surface irregularities. Gallium-based alloys have gained particular attention due to their low melting points and non-toxicity compared to mercury-based alternatives. Recent innovations have addressed historical challenges of liquid metal applications, including containment solutions to prevent electrical shorts and surface treatments to mitigate gallium-induced corrosion of aluminum components.

Phase change materials (PCMs) have evolved to incorporate advanced fillers that enhance thermal performance while maintaining the beneficial properties of conventional PCMs. These hybrid materials can adapt to thermal cycling conditions typical in HBM4 operations, maintaining interface integrity throughout temperature fluctuations between idle and high-performance computing states.

Sintered silver and copper interfaces represent another promising direction, offering thermal conductivity approaching that of bulk metals (>200 W/m·K) while enabling ultra-thin bond lines below 20 microns. These materials are particularly valuable for die-to-die interfaces within HBM4 stacks where space constraints are severe and thermal resistance must be minimized.

Emerging research in self-healing thermal interfaces shows potential for addressing reliability concerns in HBM4 applications. These materials incorporate microcapsules containing healing agents that release upon crack formation, restoring thermal pathways and extending operational lifetime under thermal cycling conditions typical in high-performance computing environments.

Atomic layer deposition (ALD) techniques have enabled the creation of conformal nanoscale thermal interface layers with precisely controlled thickness and composition. This approach shows particular promise for addressing the challenging geometries and microscale features present in advanced HBM4 stack architectures, allowing thermal management solutions to scale with increasing integration density.

Reliability Testing Standards for HBM4 Stacks

Reliability testing standards for HBM4 stacks have evolved significantly to address the unique thermal challenges presented by these advanced memory architectures. The industry has established comprehensive testing protocols that specifically target thermal path integrity and hot-spot mitigation capabilities under various operational conditions.

JEDEC has developed specialized standards for HBM4 that extend beyond traditional memory testing frameworks, incorporating thermal cycling tests with wider temperature ranges (-65°C to 150°C) and increased cycle counts to account for the complex thermal expansion behaviors in heterogeneous integrated stacks.

The High Temperature Operating Life (HTOL) test has been modified for HBM4 stacks, now requiring extended testing periods of up to 2,000 hours at elevated temperatures while the memory performs intensive data transfer operations. This ensures the thermal paths maintain integrity during prolonged high-performance computing scenarios.

Thermal shock testing standards have become more stringent, with rapid temperature transitions between extremes occurring in under 10 seconds, compared to the 30-second transitions in previous generations. This change reflects the need to validate the resilience of thermal interfaces between silicon dies, interposers, and substrates.

Power cycling tests now incorporate variable power profiles that simulate real-world workloads with sudden power spikes, specifically designed to stress thermal pathways and identify potential hot-spot formation areas. These tests typically require 10,000 cycles with monitoring of temperature gradients across the stack.

Infrared thermography standards have been established for HBM4 qualification, requiring sub-micron resolution thermal imaging to identify potential hot-spots during operation. The standards specify maximum allowable temperature differentials between adjacent regions (typically less than 10°C) to prevent thermal stress concentration.

Reliability standards now include specific tests for thermal interface materials (TIMs) used in HBM4 stacks, evaluating their performance degradation over time. These tests measure thermal conductivity changes after aging protocols that simulate 5-7 years of operational life.

Electromigration testing has been enhanced to account for the interaction between thermal gradients and current density in HBM4's dense interconnect structures. The standards now require simultaneous thermal and electrical stress testing rather than treating these as separate qualification steps.

Humidity and temperature bias testing standards have also evolved, now incorporating 3D vapor diffusion models to account for moisture penetration through the complex stack interfaces, with particular attention to areas prone to hot-spot formation.

JEDEC has developed specialized standards for HBM4 that extend beyond traditional memory testing frameworks, incorporating thermal cycling tests with wider temperature ranges (-65°C to 150°C) and increased cycle counts to account for the complex thermal expansion behaviors in heterogeneous integrated stacks.

The High Temperature Operating Life (HTOL) test has been modified for HBM4 stacks, now requiring extended testing periods of up to 2,000 hours at elevated temperatures while the memory performs intensive data transfer operations. This ensures the thermal paths maintain integrity during prolonged high-performance computing scenarios.

Thermal shock testing standards have become more stringent, with rapid temperature transitions between extremes occurring in under 10 seconds, compared to the 30-second transitions in previous generations. This change reflects the need to validate the resilience of thermal interfaces between silicon dies, interposers, and substrates.

Power cycling tests now incorporate variable power profiles that simulate real-world workloads with sudden power spikes, specifically designed to stress thermal pathways and identify potential hot-spot formation areas. These tests typically require 10,000 cycles with monitoring of temperature gradients across the stack.

Infrared thermography standards have been established for HBM4 qualification, requiring sub-micron resolution thermal imaging to identify potential hot-spots during operation. The standards specify maximum allowable temperature differentials between adjacent regions (typically less than 10°C) to prevent thermal stress concentration.

Reliability standards now include specific tests for thermal interface materials (TIMs) used in HBM4 stacks, evaluating their performance degradation over time. These tests measure thermal conductivity changes after aging protocols that simulate 5-7 years of operational life.

Electromigration testing has been enhanced to account for the interaction between thermal gradients and current density in HBM4's dense interconnect structures. The standards now require simultaneous thermal and electrical stress testing rather than treating these as separate qualification steps.

Humidity and temperature bias testing standards have also evolved, now incorporating 3D vapor diffusion models to account for moisture penetration through the complex stack interfaces, with particular attention to areas prone to hot-spot formation.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!