How HBM4 Enables Reliable Power Delivery In Multi-Stack Packages?

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Evolution and Power Delivery Objectives

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with each generation addressing the growing demands of high-performance computing applications. The journey from HBM1 to HBM4 represents a continuous pursuit of higher bandwidth, increased capacity, improved energy efficiency, and enhanced reliability. HBM4, the latest iteration in this evolutionary path, marks a substantial advancement in addressing the critical challenge of power delivery in multi-stack packages.

The evolution of HBM technology has been driven by the exponential growth in computational requirements across various domains, including artificial intelligence, machine learning, high-performance computing, and graphics processing. HBM1, introduced in 2013, offered a significant improvement over traditional DRAM technologies with its stacked die architecture and wide interface. HBM2, released in 2016, doubled the bandwidth while improving power efficiency. HBM2E, an enhancement to HBM2, further increased bandwidth and capacity to meet the demands of data-intensive applications.

HBM3, announced in 2021, represented a major leap forward with substantially higher bandwidth, increased capacity, and improved power efficiency. However, as the complexity and density of HBM stacks increased, power delivery emerged as a critical challenge, particularly in multi-stack configurations where thermal management and signal integrity become increasingly complex.

HBM4 aims to address these challenges with specific objectives focused on reliable power delivery in multi-stack packages. The primary goal is to optimize power distribution networks to ensure stable voltage delivery across all layers of the memory stack, even under peak load conditions. This involves innovative approaches to power plane design, decoupling capacitor placement, and through-silicon via (TSV) optimization to minimize voltage droop and power supply noise.

Another key objective is to enhance thermal management capabilities to prevent hotspots and ensure uniform temperature distribution across the memory stack. This is crucial for maintaining reliable operation and preventing performance degradation due to thermal throttling. HBM4 also aims to improve signal integrity in high-density interconnects, reducing crosstalk and electromagnetic interference that can compromise power delivery.

The technology trend indicates a move toward more sophisticated power management techniques, including dynamic voltage and frequency scaling at a finer granularity, adaptive power gating, and intelligent power distribution based on workload characteristics. These advancements are essential for supporting the increasing bandwidth and capacity requirements while maintaining or improving energy efficiency.

In summary, HBM4's evolution represents a focused effort to overcome the power delivery challenges in multi-stack packages, enabling the next generation of high-performance computing systems with unprecedented memory bandwidth and capacity while ensuring reliable operation under demanding workloads.

The evolution of HBM technology has been driven by the exponential growth in computational requirements across various domains, including artificial intelligence, machine learning, high-performance computing, and graphics processing. HBM1, introduced in 2013, offered a significant improvement over traditional DRAM technologies with its stacked die architecture and wide interface. HBM2, released in 2016, doubled the bandwidth while improving power efficiency. HBM2E, an enhancement to HBM2, further increased bandwidth and capacity to meet the demands of data-intensive applications.

HBM3, announced in 2021, represented a major leap forward with substantially higher bandwidth, increased capacity, and improved power efficiency. However, as the complexity and density of HBM stacks increased, power delivery emerged as a critical challenge, particularly in multi-stack configurations where thermal management and signal integrity become increasingly complex.

HBM4 aims to address these challenges with specific objectives focused on reliable power delivery in multi-stack packages. The primary goal is to optimize power distribution networks to ensure stable voltage delivery across all layers of the memory stack, even under peak load conditions. This involves innovative approaches to power plane design, decoupling capacitor placement, and through-silicon via (TSV) optimization to minimize voltage droop and power supply noise.

Another key objective is to enhance thermal management capabilities to prevent hotspots and ensure uniform temperature distribution across the memory stack. This is crucial for maintaining reliable operation and preventing performance degradation due to thermal throttling. HBM4 also aims to improve signal integrity in high-density interconnects, reducing crosstalk and electromagnetic interference that can compromise power delivery.

The technology trend indicates a move toward more sophisticated power management techniques, including dynamic voltage and frequency scaling at a finer granularity, adaptive power gating, and intelligent power distribution based on workload characteristics. These advancements are essential for supporting the increasing bandwidth and capacity requirements while maintaining or improving energy efficiency.

In summary, HBM4's evolution represents a focused effort to overcome the power delivery challenges in multi-stack packages, enabling the next generation of high-performance computing systems with unprecedented memory bandwidth and capacity while ensuring reliable operation under demanding workloads.

Market Demand for Advanced Memory Solutions

The demand for advanced memory solutions has surged dramatically in recent years, driven primarily by the exponential growth in data-intensive applications. High-performance computing (HPC), artificial intelligence (AI), machine learning (ML), and large language models (LLMs) have created unprecedented requirements for memory bandwidth, capacity, and power efficiency. The global market for high-bandwidth memory is projected to grow at a compound annual growth rate of 24% through 2028, reflecting the critical need for next-generation memory technologies like HBM4.

Data centers and cloud service providers represent the largest market segment demanding advanced memory solutions, as they struggle to manage the computational requirements of increasingly complex AI training workloads. These workloads have grown from requiring gigabytes to terabytes of high-speed memory, creating significant challenges for existing memory architectures. The memory wall—the growing disparity between processor and memory performance—has become a critical bottleneck in system performance.

Enterprise customers are increasingly prioritizing memory solutions that can deliver not only higher bandwidth but also improved power efficiency. With data centers already consuming approximately 1-2% of global electricity, the energy consumption of memory subsystems has become a significant concern. Market research indicates that customers are willing to pay premium prices for memory technologies that can demonstrate substantial improvements in performance-per-watt metrics.

The automotive and edge computing sectors represent emerging markets for advanced memory solutions. As autonomous driving technologies mature, the computational requirements for in-vehicle systems continue to escalate, creating demand for high-performance, reliable memory solutions that can operate in challenging environmental conditions. Similarly, edge computing applications require memory architectures that can deliver high bandwidth while operating within strict power constraints.

Reliability has emerged as a critical market requirement, particularly for multi-stack memory packages. System integrators report that memory-related failures account for a significant percentage of system downtime in high-performance computing environments. The financial impact of these failures, especially in mission-critical applications, has heightened market sensitivity to reliability concerns in advanced memory solutions.

The geographical distribution of demand shows particular strength in regions with concentrated AI and HPC development activities. North America leads in demand, followed by East Asia, particularly South Korea, Taiwan, and Japan, where much of the memory manufacturing infrastructure is located. Europe shows growing demand, driven by investments in scientific computing and automotive applications.

Data centers and cloud service providers represent the largest market segment demanding advanced memory solutions, as they struggle to manage the computational requirements of increasingly complex AI training workloads. These workloads have grown from requiring gigabytes to terabytes of high-speed memory, creating significant challenges for existing memory architectures. The memory wall—the growing disparity between processor and memory performance—has become a critical bottleneck in system performance.

Enterprise customers are increasingly prioritizing memory solutions that can deliver not only higher bandwidth but also improved power efficiency. With data centers already consuming approximately 1-2% of global electricity, the energy consumption of memory subsystems has become a significant concern. Market research indicates that customers are willing to pay premium prices for memory technologies that can demonstrate substantial improvements in performance-per-watt metrics.

The automotive and edge computing sectors represent emerging markets for advanced memory solutions. As autonomous driving technologies mature, the computational requirements for in-vehicle systems continue to escalate, creating demand for high-performance, reliable memory solutions that can operate in challenging environmental conditions. Similarly, edge computing applications require memory architectures that can deliver high bandwidth while operating within strict power constraints.

Reliability has emerged as a critical market requirement, particularly for multi-stack memory packages. System integrators report that memory-related failures account for a significant percentage of system downtime in high-performance computing environments. The financial impact of these failures, especially in mission-critical applications, has heightened market sensitivity to reliability concerns in advanced memory solutions.

The geographical distribution of demand shows particular strength in regions with concentrated AI and HPC development activities. North America leads in demand, followed by East Asia, particularly South Korea, Taiwan, and Japan, where much of the memory manufacturing infrastructure is located. Europe shows growing demand, driven by investments in scientific computing and automotive applications.

Current Challenges in Multi-Stack Package Power Delivery

Multi-stack package designs incorporating High Bandwidth Memory (HBM) face significant power delivery challenges that impact system reliability and performance. As HBM technology advances toward HBM4, these challenges become increasingly complex due to higher bandwidth requirements, increased power consumption, and more intricate integration schemes. Current power delivery networks (PDNs) in multi-stack packages struggle with several critical limitations that must be addressed for successful HBM4 implementation.

Voltage droop and IR drop issues represent primary concerns in existing designs. As signals traverse through the interposer and microbumps connecting HBM stacks to the base die, significant voltage drops occur, particularly during high-speed data transfer operations. These voltage fluctuations can lead to timing violations, data corruption, and in severe cases, system failures. Current HBM3 implementations already operate at reduced margins, and HBM4's higher performance targets will further exacerbate these challenges.

Thermal management presents another substantial hurdle. Power density in multi-stack packages has reached unprecedented levels, with hotspots forming at critical interconnect points. These thermal issues directly impact power delivery reliability as resistance increases with temperature, creating a negative feedback loop that further degrades power integrity. Existing cooling solutions struggle to efficiently dissipate heat from the internal layers of HBM stacks, particularly in configurations with four or more memory stacks.

Signal integrity degradation occurs as power and ground planes experience noise coupling and impedance mismatches. The proximity of high-speed data paths to power delivery networks in tightly packed multi-stack designs creates electromagnetic interference that compromises both signal quality and power stability. Current isolation techniques prove increasingly inadequate as data rates climb toward HBM4 specifications.

Manufacturing variability compounds these challenges, as process variations in through-silicon vias (TSVs), microbumps, and redistribution layers create inconsistent electrical characteristics across the power delivery network. These variations lead to unpredictable performance and reliability issues that are difficult to model accurately during the design phase. The industry currently lacks standardized methodologies for characterizing and compensating for these manufacturing variations in multi-stack power delivery systems.

Power management algorithms and dynamic voltage scaling techniques used in current designs exhibit insufficient response times for HBM4's performance requirements. The latency between sensing power demands and adjusting voltage levels creates windows of vulnerability where memory operations may fail due to transient power conditions. More sophisticated, predictive power management approaches are needed but remain underdeveloped in current implementations.

Voltage droop and IR drop issues represent primary concerns in existing designs. As signals traverse through the interposer and microbumps connecting HBM stacks to the base die, significant voltage drops occur, particularly during high-speed data transfer operations. These voltage fluctuations can lead to timing violations, data corruption, and in severe cases, system failures. Current HBM3 implementations already operate at reduced margins, and HBM4's higher performance targets will further exacerbate these challenges.

Thermal management presents another substantial hurdle. Power density in multi-stack packages has reached unprecedented levels, with hotspots forming at critical interconnect points. These thermal issues directly impact power delivery reliability as resistance increases with temperature, creating a negative feedback loop that further degrades power integrity. Existing cooling solutions struggle to efficiently dissipate heat from the internal layers of HBM stacks, particularly in configurations with four or more memory stacks.

Signal integrity degradation occurs as power and ground planes experience noise coupling and impedance mismatches. The proximity of high-speed data paths to power delivery networks in tightly packed multi-stack designs creates electromagnetic interference that compromises both signal quality and power stability. Current isolation techniques prove increasingly inadequate as data rates climb toward HBM4 specifications.

Manufacturing variability compounds these challenges, as process variations in through-silicon vias (TSVs), microbumps, and redistribution layers create inconsistent electrical characteristics across the power delivery network. These variations lead to unpredictable performance and reliability issues that are difficult to model accurately during the design phase. The industry currently lacks standardized methodologies for characterizing and compensating for these manufacturing variations in multi-stack power delivery systems.

Power management algorithms and dynamic voltage scaling techniques used in current designs exhibit insufficient response times for HBM4's performance requirements. The latency between sensing power demands and adjusting voltage levels creates windows of vulnerability where memory operations may fail due to transient power conditions. More sophisticated, predictive power management approaches are needed but remain underdeveloped in current implementations.

Current Power Delivery Network Solutions for HBM4

01 Power delivery network design for HBM4

Specialized power delivery network (PDN) designs for High Bandwidth Memory 4 (HBM4) focus on maintaining stable voltage levels and minimizing power fluctuations. These designs incorporate advanced power distribution architectures that reduce impedance and voltage drops across the memory stack. By optimizing the power delivery path from voltage regulators to memory dies, these solutions ensure reliable operation at high data transfer rates while managing the increased power demands of HBM4 technology.- Power distribution architecture for HBM4: Advanced power distribution architectures specifically designed for HBM4 memory systems that ensure stable voltage delivery across high-speed memory stacks. These architectures incorporate specialized power planes, optimized power routing, and dedicated power management circuitry to maintain reliable operation under high bandwidth conditions. The designs address the increased power requirements of HBM4 while minimizing voltage droop and power delivery network impedance.

- Thermal management solutions for power delivery: Thermal management techniques integrated with power delivery systems to ensure reliable operation of HBM4 memory. These solutions include advanced heat dissipation structures, thermal interface materials, and cooling mechanisms that work in conjunction with power delivery networks. By effectively managing heat generated during high-bandwidth operations, these systems prevent thermal-related power instabilities and extend the operational reliability of HBM4 memory stacks.

- Power management integrated circuits for HBM4: Specialized power management integrated circuits (PMICs) designed specifically for HBM4 applications that provide precise voltage regulation, current monitoring, and power sequencing. These PMICs incorporate advanced features such as dynamic voltage scaling, adaptive power management, and fast transient response to accommodate the high-speed, high-bandwidth requirements of HBM4 memory while maintaining power efficiency and reliability under varying load conditions.

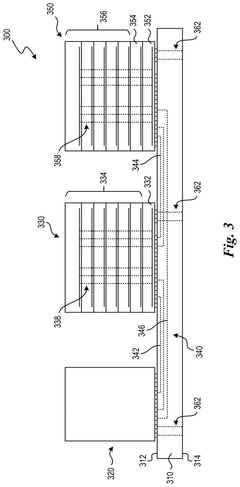

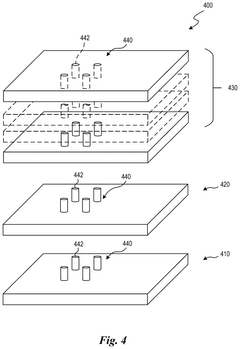

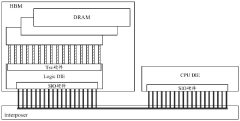

- 3D stacking power delivery optimization: Innovative power delivery solutions specifically designed for 3D stacked HBM4 architectures. These approaches optimize through-silicon via (TSV) placement, power plane design, and interposer power distribution to minimize power delivery impedance in vertically stacked memory configurations. The techniques address the unique challenges of delivering stable power through multiple silicon layers while maintaining signal integrity in high-bandwidth memory systems.

- Dynamic power management protocols: Advanced protocols and algorithms for dynamic power management in HBM4 systems that adaptively adjust power delivery based on workload requirements. These solutions include intelligent power state transitions, workload-aware voltage regulation, and predictive power management techniques that optimize energy efficiency while ensuring reliable operation. The protocols enable fine-grained control over power consumption during different memory access patterns and bandwidth demands.

02 Thermal management solutions for power stability

Thermal management techniques are crucial for maintaining reliable power delivery in HBM4 implementations. These solutions include advanced heat dissipation structures, thermal interface materials, and active cooling systems that prevent thermal throttling and ensure consistent power delivery. By effectively managing heat generated during high-bandwidth operations, these approaches maintain optimal operating temperatures, prevent power fluctuations, and extend the operational lifespan of HBM4 memory systems.Expand Specific Solutions03 Power-aware memory controllers and interfaces

Specialized memory controllers and interfaces designed for HBM4 implement power-aware protocols that optimize power consumption while maintaining performance. These controllers dynamically adjust voltage levels, clock frequencies, and refresh rates based on workload demands. By incorporating advanced power state management and intelligent scheduling algorithms, these systems ensure reliable power delivery to HBM4 memory stacks while minimizing unnecessary power consumption during periods of lower activity.Expand Specific Solutions04 3D integration and TSV power distribution

Advanced 3D integration techniques and Through-Silicon Via (TSV) power distribution methods are essential for reliable HBM4 power delivery. These approaches optimize the placement and design of power TSVs to minimize resistance and inductance in the power delivery path. By strategically distributing power across multiple layers of the memory stack and implementing redundant power paths, these solutions enhance power integrity and ensure stable voltage levels throughout the HBM4 memory structure.Expand Specific Solutions05 Voltage regulation and power management circuitry

Specialized voltage regulation and power management circuitry for HBM4 implementations focus on maintaining stable supply voltages despite varying load conditions. These circuits incorporate advanced feedback mechanisms, fast-response regulators, and adaptive power management techniques to compensate for transient voltage fluctuations. By integrating sophisticated power monitoring and control systems close to the memory dies, these solutions ensure reliable power delivery to HBM4 memory while optimizing energy efficiency during different operational modes.Expand Specific Solutions

Key Players in HBM4 Development Ecosystem

The HBM4 power delivery market is in a growth phase, with increasing demand driven by AI and high-performance computing applications. The market is expected to expand significantly as multi-stack packages become essential for data centers and advanced computing systems. Technologically, the field is rapidly maturing with key players like Samsung Electronics, SK hynix, and Micron Technology leading innovation in HBM4 power delivery solutions. These companies have developed advanced technologies to address thermal challenges and signal integrity in high-density memory stacks. Other significant contributors include TSMC and Intel, who are integrating HBM4 into their semiconductor manufacturing processes. Chinese companies such as ChangXin Memory and JCET Group are also emerging as important players, investing heavily to close the technological gap with established market leaders.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered HBM4 power delivery solutions through their innovative "Through-Silicon Via (TSV) Redundancy" architecture. This approach incorporates multiple parallel power delivery TSVs within each stack to create redundant power pathways, significantly enhancing reliability in multi-stack packages. Their design implements a sophisticated power distribution network (PDN) that optimizes current density across the stacks while minimizing IR drop. Samsung's HBM4 technology features an advanced voltage regulation module (VRM) positioned closer to the memory dies, reducing transmission distance and associated power losses. The company has also developed proprietary decoupling capacitor arrangements strategically placed throughout the stack to mitigate power supply noise and transient voltage fluctuations. Samsung's implementation achieves up to 1.2TB/s bandwidth while maintaining power integrity across 12-high HBM stacks.

Strengths: Industry-leading TSV redundancy architecture provides exceptional reliability; advanced on-die power management reduces overall system power requirements. Weaknesses: Higher manufacturing costs due to complex TSV implementation; requires sophisticated thermal management solutions to address increased power density in multi-stack configurations.

SK hynix, Inc.

Technical Solution: SK hynix has developed a comprehensive HBM4 power delivery solution centered around their "Distributed Power Architecture" (DPA). This innovative approach divides the HBM4 stack into multiple power domains with independent voltage regulation, allowing for optimized power delivery to different functional blocks. Their technology incorporates advanced micro-bumps with reduced resistance and inductance characteristics, minimizing power loss during transmission between layers. SK hynix's HBM4 implementation features an intelligent power management system that dynamically adjusts voltage levels based on workload demands, significantly improving energy efficiency during varied operational states. The company has also pioneered a novel interposer design with embedded passive components that serve as localized power reservoirs, stabilizing voltage delivery during high-current transients. Their solution achieves reliable power delivery while supporting bandwidth exceeding 1TB/s across multi-stack configurations.

Strengths: Distributed power architecture provides excellent voltage stability across different functional blocks; dynamic voltage scaling significantly improves energy efficiency. Weaknesses: Complex power domain management increases controller complexity; requires sophisticated interposer technology that may impact manufacturing yields.

Core Innovations in HBM4 Power Architecture

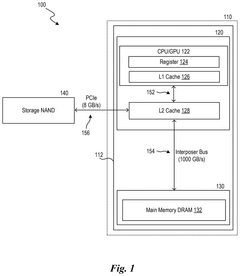

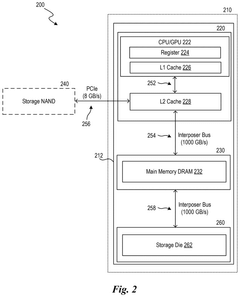

Vertically stacked high bandwidth storage devices and associated systems and methods

PatentPendingUS20250231895A1

Innovation

- Integration of high bandwidth storage (HBS) devices within the semiconductor package, which include non-volatile memory dies and high bandwidth communication paths, allowing for expanded storage capacity and efficient data transfer within the package.

Power-on and power-off method and device of chip

PatentPendingCN117806441A

Innovation

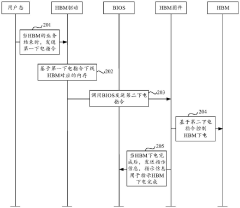

- By completely shutting down the HBM when it is not in use, and only supplying power when needed, using a combination of software and hardware, the HBM firmware controls the HBM's power-on and power-off process based on power-on or power-off instructions, reducing hardware overhead and costs.

Thermal Management Strategies in HBM4 Implementations

Thermal management represents a critical challenge in HBM4 implementation, particularly as power density increases with higher bandwidth and more complex multi-stack configurations. The thermal design power (TDP) of HBM4 stacks significantly exceeds previous generations, necessitating innovative cooling strategies to maintain operational reliability and performance.

Active cooling solutions have emerged as essential components for HBM4 implementations. These include advanced liquid cooling systems that directly target the memory stacks, providing more efficient heat dissipation compared to traditional air cooling methods. Integrated microchannel cooling, where coolant flows through channels etched directly into the silicon interposer or package substrate, offers promising thermal management capabilities for high-performance computing applications utilizing HBM4.

Thermal interface materials (TIMs) play a crucial role in HBM4 thermal management. Next-generation TIMs with enhanced thermal conductivity properties are being developed specifically for HBM4 applications, including metal-based TIMs and phase-change materials that optimize heat transfer between the memory dies and heat dissipation components. These materials help minimize thermal resistance across the package assembly.

Advanced package-level thermal solutions incorporate heat spreaders and vapor chambers designed specifically for the unique geometry of HBM4 stacks. These components distribute heat more evenly across the package, preventing hotspots that could compromise reliability. Some implementations feature integrated heat pipes that efficiently transport thermal energy away from critical components to external dissipation structures.

Thermal-aware floor planning has become essential in HBM4 system design. Strategic placement of HBM4 stacks relative to processing units and other heat-generating components helps optimize overall thermal profiles. This approach includes creating thermal isolation zones and implementing thermal-aware routing of high-power interconnects to minimize heat concentration.

Dynamic thermal management techniques are increasingly important for HBM4 implementations. These include adaptive power management algorithms that monitor temperature across the memory subsystem and adjust operational parameters accordingly. Memory controllers can implement thermal throttling mechanisms that temporarily reduce bandwidth or adjust refresh rates to prevent thermal runaway conditions during peak workloads.

Computational fluid dynamics (CFD) modeling has become an indispensable tool for HBM4 thermal management. Advanced simulation techniques allow engineers to predict thermal behavior under various operational conditions, enabling optimization of cooling solutions before physical prototyping. These models account for the complex three-dimensional heat flow patterns unique to multi-stack HBM4 configurations.

Active cooling solutions have emerged as essential components for HBM4 implementations. These include advanced liquid cooling systems that directly target the memory stacks, providing more efficient heat dissipation compared to traditional air cooling methods. Integrated microchannel cooling, where coolant flows through channels etched directly into the silicon interposer or package substrate, offers promising thermal management capabilities for high-performance computing applications utilizing HBM4.

Thermal interface materials (TIMs) play a crucial role in HBM4 thermal management. Next-generation TIMs with enhanced thermal conductivity properties are being developed specifically for HBM4 applications, including metal-based TIMs and phase-change materials that optimize heat transfer between the memory dies and heat dissipation components. These materials help minimize thermal resistance across the package assembly.

Advanced package-level thermal solutions incorporate heat spreaders and vapor chambers designed specifically for the unique geometry of HBM4 stacks. These components distribute heat more evenly across the package, preventing hotspots that could compromise reliability. Some implementations feature integrated heat pipes that efficiently transport thermal energy away from critical components to external dissipation structures.

Thermal-aware floor planning has become essential in HBM4 system design. Strategic placement of HBM4 stacks relative to processing units and other heat-generating components helps optimize overall thermal profiles. This approach includes creating thermal isolation zones and implementing thermal-aware routing of high-power interconnects to minimize heat concentration.

Dynamic thermal management techniques are increasingly important for HBM4 implementations. These include adaptive power management algorithms that monitor temperature across the memory subsystem and adjust operational parameters accordingly. Memory controllers can implement thermal throttling mechanisms that temporarily reduce bandwidth or adjust refresh rates to prevent thermal runaway conditions during peak workloads.

Computational fluid dynamics (CFD) modeling has become an indispensable tool for HBM4 thermal management. Advanced simulation techniques allow engineers to predict thermal behavior under various operational conditions, enabling optimization of cooling solutions before physical prototyping. These models account for the complex three-dimensional heat flow patterns unique to multi-stack HBM4 configurations.

Supply Chain Considerations for HBM4 Adoption

The adoption of HBM4 technology presents significant supply chain considerations that organizations must carefully evaluate before implementation. The global semiconductor supply chain for high-bandwidth memory remains complex, with limited suppliers capable of manufacturing these advanced components. Currently, only a handful of manufacturers—primarily Samsung, SK Hynix, and Micron—possess the technical capabilities to produce HBM4 at scale, creating potential bottlenecks in availability.

Procurement strategies for HBM4 require long-term planning due to extended lead times, which typically range from 16 to 24 weeks under normal market conditions but can extend significantly during supply constraints. Organizations implementing HBM4 solutions should establish strategic partnerships with key suppliers to secure allocation priorities and potentially negotiate favorable pricing structures through volume commitments.

The manufacturing complexity of HBM4 introduces additional supply chain vulnerabilities. The production process involves advanced silicon interposers, through-silicon vias (TSVs), and micro-bump technologies that require specialized equipment and expertise. These manufacturing complexities contribute to higher costs and potential yield issues, particularly during early production phases, which may impact availability and pricing stability.

Geographic concentration of HBM manufacturing presents another critical consideration. With production facilities primarily located in East Asia, geopolitical tensions or regional disruptions could significantly impact global supply. Forward-thinking organizations are increasingly exploring supply chain diversification strategies, including supporting initiatives to develop manufacturing capabilities in alternative regions such as North America and Europe.

Quality assurance represents a crucial element in the HBM4 supply chain. The reliability requirements for power delivery in multi-stack packages necessitate rigorous testing protocols throughout the supply chain. Organizations must implement comprehensive supplier qualification processes and ongoing quality monitoring to ensure components meet the exacting specifications required for reliable power delivery in HBM4 implementations.

Cost management strategies must account for the premium pricing of HBM4 technology. Initial adoption will likely command significant price premiums compared to previous generations, with gradual cost reductions as manufacturing processes mature and yields improve. Organizations should develop total cost of ownership models that factor in not only component costs but also integration expenses, cooling requirements, and potential performance benefits that may offset higher acquisition costs.

Procurement strategies for HBM4 require long-term planning due to extended lead times, which typically range from 16 to 24 weeks under normal market conditions but can extend significantly during supply constraints. Organizations implementing HBM4 solutions should establish strategic partnerships with key suppliers to secure allocation priorities and potentially negotiate favorable pricing structures through volume commitments.

The manufacturing complexity of HBM4 introduces additional supply chain vulnerabilities. The production process involves advanced silicon interposers, through-silicon vias (TSVs), and micro-bump technologies that require specialized equipment and expertise. These manufacturing complexities contribute to higher costs and potential yield issues, particularly during early production phases, which may impact availability and pricing stability.

Geographic concentration of HBM manufacturing presents another critical consideration. With production facilities primarily located in East Asia, geopolitical tensions or regional disruptions could significantly impact global supply. Forward-thinking organizations are increasingly exploring supply chain diversification strategies, including supporting initiatives to develop manufacturing capabilities in alternative regions such as North America and Europe.

Quality assurance represents a crucial element in the HBM4 supply chain. The reliability requirements for power delivery in multi-stack packages necessitate rigorous testing protocols throughout the supply chain. Organizations must implement comprehensive supplier qualification processes and ongoing quality monitoring to ensure components meet the exacting specifications required for reliable power delivery in HBM4 implementations.

Cost management strategies must account for the premium pricing of HBM4 technology. Initial adoption will likely command significant price premiums compared to previous generations, with gradual cost reductions as manufacturing processes mature and yields improve. Organizations should develop total cost of ownership models that factor in not only component costs but also integration expenses, cooling requirements, and potential performance benefits that may offset higher acquisition costs.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!