How To Establish FinFET Device Uniformity In Large Scale Production

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Technology Background and Objectives

FinFET technology emerged in the early 2000s as a revolutionary advancement in semiconductor manufacturing, addressing the limitations of traditional planar transistors. As device dimensions continued to shrink below 22nm, conventional transistor architectures faced severe short-channel effects, increased leakage currents, and diminished performance gains. The three-dimensional fin structure of FinFETs provided superior electrostatic control of the channel, enabling continued scaling while maintaining performance improvements and power efficiency.

The evolution of FinFET technology has progressed through several generations, from initial 22nm implementations to current advanced nodes at 5nm and below. Each generation has brought refinements in fin geometry, gate stack materials, and manufacturing processes. This progression has been driven by the semiconductor industry's relentless pursuit of Moore's Law, despite increasing technical challenges and economic constraints.

A critical aspect of FinFET development has been the transition from research prototypes to high-volume manufacturing. This transition necessitated significant innovations in process control, metrology, and yield management. The three-dimensional nature of FinFETs introduced new complexities in fabrication, requiring precise control of fin height, width, and profile across entire wafers.

The primary technical objective in FinFET manufacturing is achieving device uniformity at scale. Variations in critical dimensions such as fin width, height, and gate length directly impact transistor performance parameters including threshold voltage, drive current, and leakage. These variations can lead to inconsistent circuit behavior, reduced yields, and reliability concerns. As chip designs incorporate billions of transistors, even small variations can significantly impact overall performance and power consumption.

Current industry goals focus on establishing robust manufacturing processes that can deliver consistent FinFET device characteristics across wafers, lots, and fabrication facilities. This requires advanced process control systems, in-line metrology capabilities, and sophisticated statistical methods to identify and mitigate sources of variation. Additionally, there is growing emphasis on developing predictive models that can anticipate process drift and enable proactive adjustments.

Looking forward, the industry aims to extend FinFET technology to even smaller nodes while maintaining acceptable levels of device uniformity. This will require innovations in lithography, etching, deposition, and metrology techniques. Simultaneously, research continues on potential successor technologies such as Gate-All-Around (GAA) FETs and Nanosheet transistors, which may eventually replace FinFETs while building upon the manufacturing knowledge gained from large-scale FinFET production.

The evolution of FinFET technology has progressed through several generations, from initial 22nm implementations to current advanced nodes at 5nm and below. Each generation has brought refinements in fin geometry, gate stack materials, and manufacturing processes. This progression has been driven by the semiconductor industry's relentless pursuit of Moore's Law, despite increasing technical challenges and economic constraints.

A critical aspect of FinFET development has been the transition from research prototypes to high-volume manufacturing. This transition necessitated significant innovations in process control, metrology, and yield management. The three-dimensional nature of FinFETs introduced new complexities in fabrication, requiring precise control of fin height, width, and profile across entire wafers.

The primary technical objective in FinFET manufacturing is achieving device uniformity at scale. Variations in critical dimensions such as fin width, height, and gate length directly impact transistor performance parameters including threshold voltage, drive current, and leakage. These variations can lead to inconsistent circuit behavior, reduced yields, and reliability concerns. As chip designs incorporate billions of transistors, even small variations can significantly impact overall performance and power consumption.

Current industry goals focus on establishing robust manufacturing processes that can deliver consistent FinFET device characteristics across wafers, lots, and fabrication facilities. This requires advanced process control systems, in-line metrology capabilities, and sophisticated statistical methods to identify and mitigate sources of variation. Additionally, there is growing emphasis on developing predictive models that can anticipate process drift and enable proactive adjustments.

Looking forward, the industry aims to extend FinFET technology to even smaller nodes while maintaining acceptable levels of device uniformity. This will require innovations in lithography, etching, deposition, and metrology techniques. Simultaneously, research continues on potential successor technologies such as Gate-All-Around (GAA) FETs and Nanosheet transistors, which may eventually replace FinFETs while building upon the manufacturing knowledge gained from large-scale FinFET production.

Market Demand Analysis for Uniform FinFET Devices

The semiconductor industry's demand for uniform FinFET devices has been growing exponentially as advanced computing applications proliferate across multiple sectors. Market research indicates that the global FinFET technology market is projected to reach $35 billion by 2025, with a compound annual growth rate of approximately 22% from 2020. This substantial growth is primarily driven by the increasing adoption of FinFET technology in high-performance computing, artificial intelligence, and mobile applications.

Device uniformity has emerged as a critical market requirement as chip manufacturers push toward smaller process nodes. According to industry surveys, over 80% of semiconductor fabrication facilities cite device uniformity as one of their top three challenges in scaling production. This concern is particularly pronounced in the 7nm node and below, where even minor variations can significantly impact yield rates and device performance.

The automotive and industrial IoT sectors represent rapidly expanding markets for uniform FinFET devices. With autonomous driving technologies requiring unprecedented levels of computational reliability, automotive semiconductor demand is expected to grow at 13.4% annually through 2026. These applications demand not just high performance but exceptional consistency across billions of transistors.

Mobile device manufacturers constitute another significant market segment demanding uniform FinFET production. As smartphones and tablets continue to incorporate more advanced features while maintaining or reducing power consumption, the uniformity of transistor performance becomes increasingly critical. Market analysis shows that mobile processor manufacturers are willing to pay premium prices for chips with demonstrated uniformity metrics that exceed industry standards.

Data center operators represent perhaps the most demanding customer segment. With server farms operating thousands of processors simultaneously, performance variability translates directly to efficiency losses. Market research indicates that data center operators could realize energy savings of approximately $1.2 billion annually through improved transistor uniformity, creating strong economic incentives for adoption.

The geographical distribution of market demand shows concentration in East Asia (particularly Taiwan, South Korea, and Japan), North America, and Western Europe. However, emerging markets in China and India are showing accelerated growth rates as domestic semiconductor industries develop. Chinese investment in semiconductor manufacturing is expected to exceed $150 billion over the next decade, with significant portions allocated to advanced node development including FinFET uniformity solutions.

Device uniformity has emerged as a critical market requirement as chip manufacturers push toward smaller process nodes. According to industry surveys, over 80% of semiconductor fabrication facilities cite device uniformity as one of their top three challenges in scaling production. This concern is particularly pronounced in the 7nm node and below, where even minor variations can significantly impact yield rates and device performance.

The automotive and industrial IoT sectors represent rapidly expanding markets for uniform FinFET devices. With autonomous driving technologies requiring unprecedented levels of computational reliability, automotive semiconductor demand is expected to grow at 13.4% annually through 2026. These applications demand not just high performance but exceptional consistency across billions of transistors.

Mobile device manufacturers constitute another significant market segment demanding uniform FinFET production. As smartphones and tablets continue to incorporate more advanced features while maintaining or reducing power consumption, the uniformity of transistor performance becomes increasingly critical. Market analysis shows that mobile processor manufacturers are willing to pay premium prices for chips with demonstrated uniformity metrics that exceed industry standards.

Data center operators represent perhaps the most demanding customer segment. With server farms operating thousands of processors simultaneously, performance variability translates directly to efficiency losses. Market research indicates that data center operators could realize energy savings of approximately $1.2 billion annually through improved transistor uniformity, creating strong economic incentives for adoption.

The geographical distribution of market demand shows concentration in East Asia (particularly Taiwan, South Korea, and Japan), North America, and Western Europe. However, emerging markets in China and India are showing accelerated growth rates as domestic semiconductor industries develop. Chinese investment in semiconductor manufacturing is expected to exceed $150 billion over the next decade, with significant portions allocated to advanced node development including FinFET uniformity solutions.

Current Challenges in FinFET Manufacturing Uniformity

Despite significant advancements in FinFET technology, achieving uniform device characteristics across large-scale production remains one of the most formidable challenges in semiconductor manufacturing. The three-dimensional nature of FinFET structures introduces complexity that far exceeds traditional planar transistors, creating multifaceted uniformity issues that impact yield and performance.

Fin geometry variations represent a primary concern, where even nanometer-scale deviations in fin width, height, or pitch can dramatically alter threshold voltage and drive current characteristics. These variations stem from limitations in lithography precision, etching process control, and pattern transfer fidelity, particularly as dimensions approach sub-7nm nodes.

Gate stack uniformity presents another critical challenge. The conformal deposition of high-k dielectric materials and metal gates around the three-dimensional fin structures requires exceptional process control. Variations in gate oxide thickness or metal gate work function across a wafer can lead to significant device-to-device performance disparities, affecting circuit timing and power consumption.

Channel doping uniformity becomes increasingly difficult to maintain in FinFET structures due to the complex three-dimensional dopant diffusion pathways. Achieving consistent dopant profiles throughout the fin height and across multiple fins demands sophisticated implantation techniques and thermal budget management that push the boundaries of current manufacturing capabilities.

Strain engineering, while beneficial for carrier mobility enhancement, introduces additional uniformity challenges. Ensuring consistent strain profiles across millions of devices requires precise control of epitaxial growth processes and stress liner deposition, with variations potentially causing significant mobility fluctuations between devices.

Contact resistance variability has emerged as a dominant factor affecting FinFET performance uniformity. As device dimensions shrink, the relative impact of contact resistance increases, making variations in silicide formation or metal-semiconductor interfaces increasingly problematic for overall device consistency.

Wafer-level process variations compound these challenges, with edge effects, temperature gradients during thermal processes, and plasma non-uniformities during etching or deposition creating systematic variations across wafers. These effects become more pronounced with increasing wafer sizes and higher device densities.

The economic implications of these uniformity challenges are substantial, with reduced yields directly impacting production costs. Furthermore, the increasing complexity of process control systems and metrology tools required to monitor and maintain uniformity adds significant capital expenditure to manufacturing operations.

Fin geometry variations represent a primary concern, where even nanometer-scale deviations in fin width, height, or pitch can dramatically alter threshold voltage and drive current characteristics. These variations stem from limitations in lithography precision, etching process control, and pattern transfer fidelity, particularly as dimensions approach sub-7nm nodes.

Gate stack uniformity presents another critical challenge. The conformal deposition of high-k dielectric materials and metal gates around the three-dimensional fin structures requires exceptional process control. Variations in gate oxide thickness or metal gate work function across a wafer can lead to significant device-to-device performance disparities, affecting circuit timing and power consumption.

Channel doping uniformity becomes increasingly difficult to maintain in FinFET structures due to the complex three-dimensional dopant diffusion pathways. Achieving consistent dopant profiles throughout the fin height and across multiple fins demands sophisticated implantation techniques and thermal budget management that push the boundaries of current manufacturing capabilities.

Strain engineering, while beneficial for carrier mobility enhancement, introduces additional uniformity challenges. Ensuring consistent strain profiles across millions of devices requires precise control of epitaxial growth processes and stress liner deposition, with variations potentially causing significant mobility fluctuations between devices.

Contact resistance variability has emerged as a dominant factor affecting FinFET performance uniformity. As device dimensions shrink, the relative impact of contact resistance increases, making variations in silicide formation or metal-semiconductor interfaces increasingly problematic for overall device consistency.

Wafer-level process variations compound these challenges, with edge effects, temperature gradients during thermal processes, and plasma non-uniformities during etching or deposition creating systematic variations across wafers. These effects become more pronounced with increasing wafer sizes and higher device densities.

The economic implications of these uniformity challenges are substantial, with reduced yields directly impacting production costs. Furthermore, the increasing complexity of process control systems and metrology tools required to monitor and maintain uniformity adds significant capital expenditure to manufacturing operations.

Current Solutions for FinFET Uniformity Control

01 Fin structure optimization for uniformity

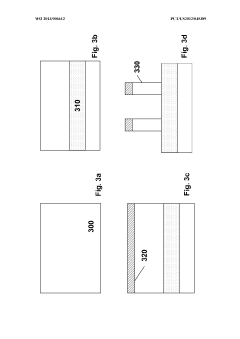

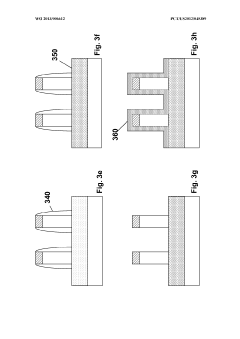

Various techniques for optimizing fin structures to improve device uniformity in FinFET devices. These include controlling fin height, width, and pitch to ensure consistent electrical characteristics across the device. Specific approaches involve precise etching processes, fin shape engineering, and dimensional control methods that minimize variations in threshold voltage and current flow across multiple fins.- Fin structure optimization for uniformity: Optimizing the structure of fins in FinFET devices is crucial for achieving uniformity. This includes controlling fin height, width, and pitch to ensure consistent electrical characteristics across the device. Various techniques such as precise etching processes and advanced lithography methods are employed to create uniform fin structures. These optimizations help minimize variations in threshold voltage and current flow, leading to better overall device performance and reliability.

- Gate engineering techniques for FinFET uniformity: Gate engineering plays a significant role in improving FinFET device uniformity. This involves optimizing gate materials, gate length control, and gate stack composition. Advanced techniques such as work function metal engineering and high-k dielectric integration help achieve uniform threshold voltages across multiple fins. Proper gate formation processes minimize variations in electrical characteristics, resulting in consistent performance across the entire chip area.

- Channel doping and strain engineering: Controlling channel doping profiles and implementing strain engineering techniques are effective methods for enhancing FinFET uniformity. Precise dopant placement and concentration management help achieve consistent threshold voltages. Strain engineering, through materials like silicon-germanium, creates uniform mechanical stress in the channel region, improving carrier mobility consistently across all transistors. These techniques work together to reduce device-to-device variations and improve overall manufacturing yield.

- Advanced process control and monitoring: Implementing sophisticated process control and monitoring systems is essential for maintaining FinFET device uniformity. This includes in-line metrology, statistical process control, and feedback loops that allow for real-time adjustments during manufacturing. Advanced inspection techniques help identify variations early in the fabrication process, enabling corrective actions before completion. These control systems ensure consistent device parameters across wafers and between different production batches.

- Multi-fin design and layout optimization: Optimizing the design and layout of multi-fin structures significantly improves overall FinFET uniformity. This includes careful consideration of fin spacing, orientation, and density to minimize proximity effects and ensure consistent electrical behavior. Advanced layout techniques account for stress effects between adjacent structures and optimize current distribution across multiple fins. These design strategies help achieve uniform performance characteristics across different transistor configurations within complex integrated circuits.

02 Gate stack engineering for uniform performance

Methods for improving gate stack uniformity in FinFET devices to enhance overall device performance. This includes techniques for consistent gate dielectric formation, metal gate deposition processes, and work function material selection. Advanced approaches focus on minimizing gate length variations, controlling gate profile, and ensuring uniform gate-to-fin coverage to reduce threshold voltage variations across the device.Expand Specific Solutions03 Doping and strain engineering techniques

Specialized doping methodologies and strain engineering techniques to improve FinFET uniformity. These include controlled dopant implantation processes, uniform dopant activation methods, and strain introduction techniques that enhance carrier mobility consistently across all fins. Advanced approaches involve selective epitaxial growth processes and stress memorization techniques to maintain uniform electrical characteristics.Expand Specific Solutions04 Process control and manufacturing optimization

Manufacturing process control methods specifically designed to enhance FinFET uniformity during fabrication. These include advanced lithography techniques, precise etch control processes, and specialized cleaning methods that minimize process variations. Statistical process control approaches and in-line monitoring techniques are employed to identify and correct uniformity issues during device fabrication.Expand Specific Solutions05 Multi-fin design and layout optimization

Design and layout strategies for multi-fin FinFET structures to improve device uniformity. These include optimized fin spacing, orientation considerations, and layout-dependent effect mitigation techniques. Advanced approaches involve dummy fin insertion, fin depopulation in critical areas, and layout-aware design rules that account for process variations to ensure consistent electrical performance across the entire chip.Expand Specific Solutions

Key Players in FinFET Semiconductor Industry

The FinFET device uniformity landscape is currently in a mature growth phase, with the global market expected to reach $70 billion by 2026. Leading players like Taiwan Semiconductor Manufacturing Co. (TSMC) and Samsung have achieved high technical maturity in mass production, while GLOBALFOUNDRIES, Intel, and United Microelectronics Corp. (UMC) maintain strong competitive positions. Chinese manufacturers including SMIC and Shanghai Huali are rapidly advancing their capabilities but face technical gaps. Applied Materials and IBM provide critical equipment and research support. The competitive dynamics are intensifying as companies like AMD and Texas Instruments drive demand for increasingly uniform and reliable FinFET devices, with research institutions like the Institute of Microelectronics of Chinese Academy of Sciences contributing to technological advancement.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered advanced FinFET manufacturing techniques focusing on process uniformity through their Statistical Process Control (SPC) system that monitors over 18,000 parameters in real-time across production lines. Their approach combines multi-patterning lithography with self-aligned double/quadruple patterning (SADP/SAQP) to achieve fin uniformity with variations below 1nm. TSMC implements a comprehensive metrology system with inline optical and electron-beam inspection at critical process steps, allowing for immediate detection and correction of process deviations. Their unique feed-forward control system adjusts subsequent process steps based on measurements from previous steps, compensating for minor variations. Additionally, TSMC employs machine learning algorithms to analyze historical process data and predict potential uniformity issues before they occur, reducing defect density to below 0.1 defects/cm² in their advanced FinFET nodes. Their N5 and N3 processes incorporate EUV lithography to further enhance uniformity by reducing multi-patterning complexity.

Strengths: Industry-leading metrology capabilities with sub-nanometer measurement precision; integrated AI-based predictive maintenance systems; extensive experience scaling FinFET to high volume manufacturing. Weaknesses: Higher production costs compared to planar technologies; requires significant capital investment in advanced equipment; complex process integration challenges when transitioning to new nodes.

International Business Machines Corp.

Technical Solution: IBM has pioneered a multi-faceted approach to FinFET uniformity focusing on their "Computational Scaling" methodology. This combines advanced lithography techniques with computational design and process modeling to achieve consistent device characteristics. IBM's approach includes their patented "Sidewall Image Transfer" technique that creates highly uniform fin structures with pitch multiplication, reducing variability in fin width to less than 1nm (3σ). Their process incorporates a unique hydrogen annealing step post-fin formation that smooths fin sidewalls and reduces line edge roughness by approximately 40%, significantly improving carrier mobility consistency. For large-scale production, IBM implements a comprehensive virtual metrology system that uses physics-based models combined with machine learning to predict critical dimensions at points where direct measurement is impractical. Their "Design-Technology Co-Optimization" framework integrates design rules with manufacturing constraints, creating layout patterns specifically optimized for process uniformity. Additionally, IBM's "Variation-Aware Design" methodology accounts for expected process variations during the design phase, ensuring circuits function correctly despite minor manufacturing inconsistencies.

Strengths: Industry-leading research capabilities with extensive experience in advanced materials and processes; strong integration between design and manufacturing; sophisticated computational modeling capabilities for process optimization. Weaknesses: Limited commercial-scale manufacturing capacity compared to dedicated foundries; higher production costs; greater focus on performance over cost optimization.

Critical Patents in FinFET Manufacturing Processes

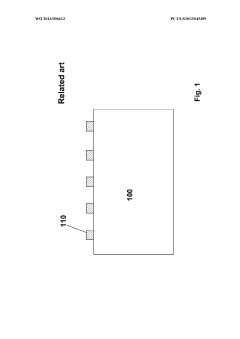

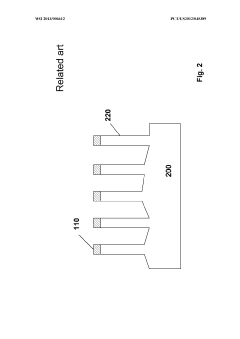

Bulk finfet with uniform height and bottom isolation

PatentWO2013006612A1

Innovation

- The formation of finFETs with uniform height and bottom isolation is achieved by using an insulating region comprising specific dopants like aluminum, arsenic, boron, gallium, indium, phosphorous, antimony, sulfur, selenium, germanium, carbon, argon, xenon, or fluorine, and converting an etch stop layer into an insulating layer to electrically isolate the fin from the substrate.

Fin FET devices from bulk semiconductor and method for forming

PatentInactiveEP1532659A2

Innovation

- A method that forms finFETs from bulk semiconductor wafers by selectively damaging the substrate to control fin height and width, using heavy ion implantation or marker layers for precise etching, and oxidizing the damaged areas to create isolation between fins and source/drain regions, allowing for optimized fin dimensions and reduced variability.

Yield Management Strategies for FinFET Production

Yield management in FinFET production represents a critical component for semiconductor manufacturers seeking to establish device uniformity at scale. Effective yield strategies must address the inherent complexities of three-dimensional transistor architectures while maintaining economic viability in high-volume manufacturing environments.

Statistical Process Control (SPC) forms the foundation of modern yield management approaches, with specialized adaptations for FinFET-specific parameters. Leading fabs implement advanced SPC systems that monitor critical dimensions including fin width, height, and pitch with nanometer-level precision. These systems typically incorporate real-time feedback loops that can detect deviations across wafer lots and trigger immediate process adjustments.

Defect density reduction strategies have evolved significantly for FinFET production, focusing on particulate control in key process steps such as fin formation and gate patterning. Advanced filtration systems operating at sub-10nm levels have demonstrated up to 40% reduction in critical defects compared to planar technology manufacturing environments. Complementary techniques such as advanced cleaning protocols specifically designed for high-aspect-ratio structures have become standard in leading foundries.

In-line metrology has undergone substantial enhancement to address FinFET uniformity challenges. Non-destructive measurement techniques including scatterometry and advanced optical critical dimension (OCD) systems enable comprehensive monitoring without sacrificing production wafers. The integration of machine learning algorithms with these metrology systems has improved detection sensitivity by approximately 30% for subtle variations that impact device performance.

Process window optimization represents another crucial yield management approach. Unlike planar technologies, FinFET processes require significantly tighter control of multiple interdependent parameters. Leading manufacturers employ Design of Experiments (DoE) methodologies combined with computational modeling to identify optimal process windows that maximize uniformity while maintaining throughput requirements.

Binning and sorting strategies have also evolved to accommodate FinFET-specific performance variations. Advanced electrical test methodologies can now identify subtle variations in threshold voltage and leakage current that correlate with specific process deviations. This enables manufacturers to implement targeted process improvements while maintaining commercially viable yields through appropriate product binning.

Equipment matching and calibration protocols have become increasingly sophisticated, with leading fabs implementing chamber-to-chamber matching requirements at tolerances below 2% for critical process steps. These stringent requirements ensure that devices produced on different tools within the same facility maintain consistent performance characteristics, a fundamental requirement for large-scale production.

Statistical Process Control (SPC) forms the foundation of modern yield management approaches, with specialized adaptations for FinFET-specific parameters. Leading fabs implement advanced SPC systems that monitor critical dimensions including fin width, height, and pitch with nanometer-level precision. These systems typically incorporate real-time feedback loops that can detect deviations across wafer lots and trigger immediate process adjustments.

Defect density reduction strategies have evolved significantly for FinFET production, focusing on particulate control in key process steps such as fin formation and gate patterning. Advanced filtration systems operating at sub-10nm levels have demonstrated up to 40% reduction in critical defects compared to planar technology manufacturing environments. Complementary techniques such as advanced cleaning protocols specifically designed for high-aspect-ratio structures have become standard in leading foundries.

In-line metrology has undergone substantial enhancement to address FinFET uniformity challenges. Non-destructive measurement techniques including scatterometry and advanced optical critical dimension (OCD) systems enable comprehensive monitoring without sacrificing production wafers. The integration of machine learning algorithms with these metrology systems has improved detection sensitivity by approximately 30% for subtle variations that impact device performance.

Process window optimization represents another crucial yield management approach. Unlike planar technologies, FinFET processes require significantly tighter control of multiple interdependent parameters. Leading manufacturers employ Design of Experiments (DoE) methodologies combined with computational modeling to identify optimal process windows that maximize uniformity while maintaining throughput requirements.

Binning and sorting strategies have also evolved to accommodate FinFET-specific performance variations. Advanced electrical test methodologies can now identify subtle variations in threshold voltage and leakage current that correlate with specific process deviations. This enables manufacturers to implement targeted process improvements while maintaining commercially viable yields through appropriate product binning.

Equipment matching and calibration protocols have become increasingly sophisticated, with leading fabs implementing chamber-to-chamber matching requirements at tolerances below 2% for critical process steps. These stringent requirements ensure that devices produced on different tools within the same facility maintain consistent performance characteristics, a fundamental requirement for large-scale production.

Environmental Impact of FinFET Manufacturing Processes

The manufacturing processes of FinFET devices involve numerous chemical and physical operations that generate significant environmental impacts. The production of these advanced transistors requires extensive use of rare earth elements, heavy metals, and toxic chemicals including arsenic, phosphorus, and various acid compounds. These materials pose substantial environmental risks if not properly managed throughout the manufacturing lifecycle.

Water consumption represents one of the most critical environmental concerns in FinFET production. A single semiconductor fabrication facility can consume between 2-4 million gallons of ultra-pure water daily, with FinFET processes requiring even more intensive purification steps than traditional planar transistors. The wastewater generated contains various contaminants including heavy metals, organic solvents, and acidic compounds that require sophisticated treatment systems.

Energy usage in FinFET manufacturing is exceptionally high, primarily due to the precise temperature control requirements and clean room operations. The extreme ultraviolet (EUV) lithography systems used in advanced FinFET nodes consume substantial electricity, with a single tool requiring up to 1 MW of power during operation. This energy intensity translates to a significant carbon footprint, particularly in regions where electricity generation relies heavily on fossil fuels.

Chemical waste management presents another substantial challenge. The etching and cleaning processes in FinFET fabrication generate perfluorocompounds (PFCs) and other greenhouse gases with global warming potentials thousands of times greater than CO2. Industry data suggests that semiconductor manufacturing contributes approximately 0.2% of global greenhouse gas emissions, with advanced node processes like FinFET production representing an increasing proportion of this impact.

Air quality impacts extend beyond greenhouse gases to include volatile organic compounds (VOCs), acid gases, and particulate matter. These emissions require sophisticated abatement systems to prevent local air quality degradation. The high-precision requirements for FinFET uniformity often necessitate more intensive chemical processes, potentially increasing these emissions compared to older semiconductor technologies.

Recent industry initiatives have focused on developing more sustainable manufacturing approaches. These include closed-loop water recycling systems that can reduce freshwater consumption by up to 50%, energy efficiency improvements through heat recovery and equipment optimization, and alternative chemistry approaches that replace the most environmentally problematic compounds with greener alternatives. However, the inherent complexity of FinFET structures often limits the implementation of these sustainability measures without compromising device uniformity.

Water consumption represents one of the most critical environmental concerns in FinFET production. A single semiconductor fabrication facility can consume between 2-4 million gallons of ultra-pure water daily, with FinFET processes requiring even more intensive purification steps than traditional planar transistors. The wastewater generated contains various contaminants including heavy metals, organic solvents, and acidic compounds that require sophisticated treatment systems.

Energy usage in FinFET manufacturing is exceptionally high, primarily due to the precise temperature control requirements and clean room operations. The extreme ultraviolet (EUV) lithography systems used in advanced FinFET nodes consume substantial electricity, with a single tool requiring up to 1 MW of power during operation. This energy intensity translates to a significant carbon footprint, particularly in regions where electricity generation relies heavily on fossil fuels.

Chemical waste management presents another substantial challenge. The etching and cleaning processes in FinFET fabrication generate perfluorocompounds (PFCs) and other greenhouse gases with global warming potentials thousands of times greater than CO2. Industry data suggests that semiconductor manufacturing contributes approximately 0.2% of global greenhouse gas emissions, with advanced node processes like FinFET production representing an increasing proportion of this impact.

Air quality impacts extend beyond greenhouse gases to include volatile organic compounds (VOCs), acid gases, and particulate matter. These emissions require sophisticated abatement systems to prevent local air quality degradation. The high-precision requirements for FinFET uniformity often necessitate more intensive chemical processes, potentially increasing these emissions compared to older semiconductor technologies.

Recent industry initiatives have focused on developing more sustainable manufacturing approaches. These include closed-loop water recycling systems that can reduce freshwater consumption by up to 50%, energy efficiency improvements through heat recovery and equipment optimization, and alternative chemistry approaches that replace the most environmentally problematic compounds with greener alternatives. However, the inherent complexity of FinFET structures often limits the implementation of these sustainability measures without compromising device uniformity.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!