Divider and realization method thereof

A technology of a divider and an adder, applied in the field of digital signal processing circuits, can solve the problems of large hardware resource occupation, difficult porting of dividers, long operation time, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

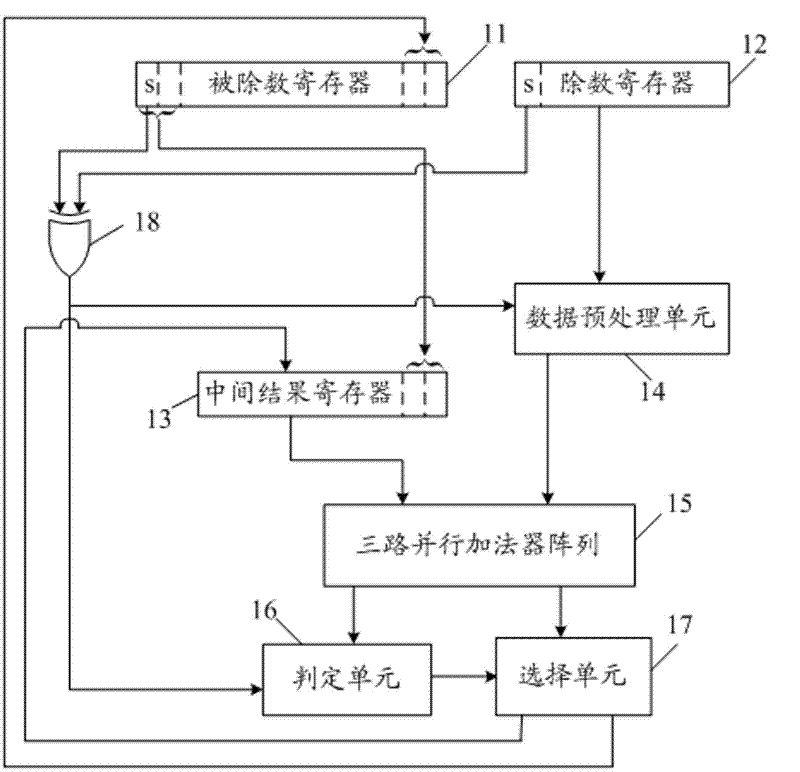

[0049] like figure 1 As shown, the fast 32-bit integer divider proposed by the present invention includes: the dividend register 11 for storing the dividend A; the divisor register 12 for storing the divisor B; the intermediate result register 13 for storing the intermediate result P; Processing unit 14; Three-way parallel adder array 15; Judgment unit 16 for sign processing / quotient judgment / partial remainder judgment; Selection unit 17 for quotient selection / partial remainder selection; Comparator 18, by dividing the dividend Compare with the sign of the divisor to determine whether the comparison operation of the next iterative quotient process is addition or subtraction. If the two signs are the same, the subtraction operation will be performed. If the two signs are different, the addition operation will be performed.

[0050] Wherein, after the division operation ends, the obtained quotient will be stored in the dividend register 11 .

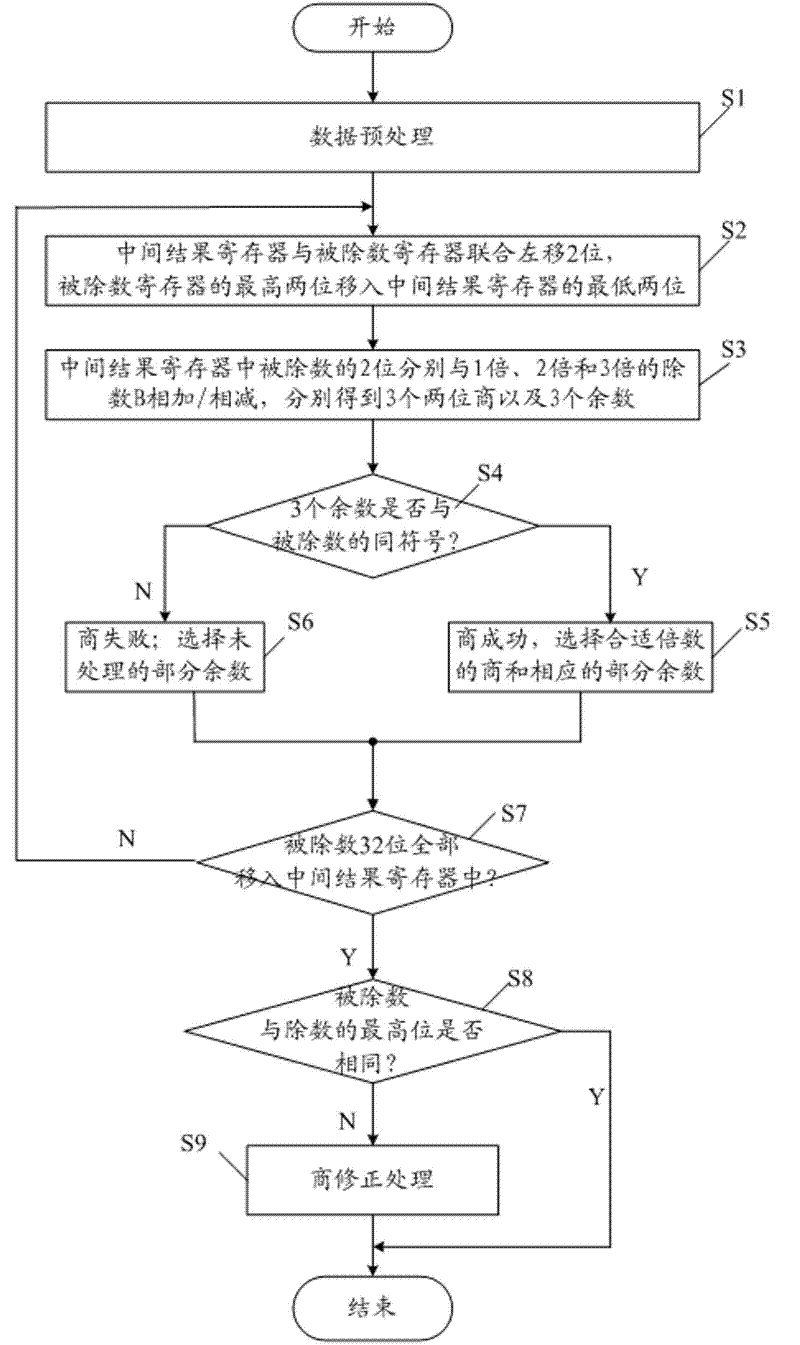

[0051] combine figure 2 Shown, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More