Sigma-Delta modulation circuit and method as well as corresponding phase-locked loop

A modulation circuit and phase-locked loop technology, applied in the direction of electrical components, automatic power control, etc., can solve the problem of lack of flexibility in output results, and achieve the effect of excellent stability and short locking time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In order to make the technical features of the present invention more comprehensible, the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

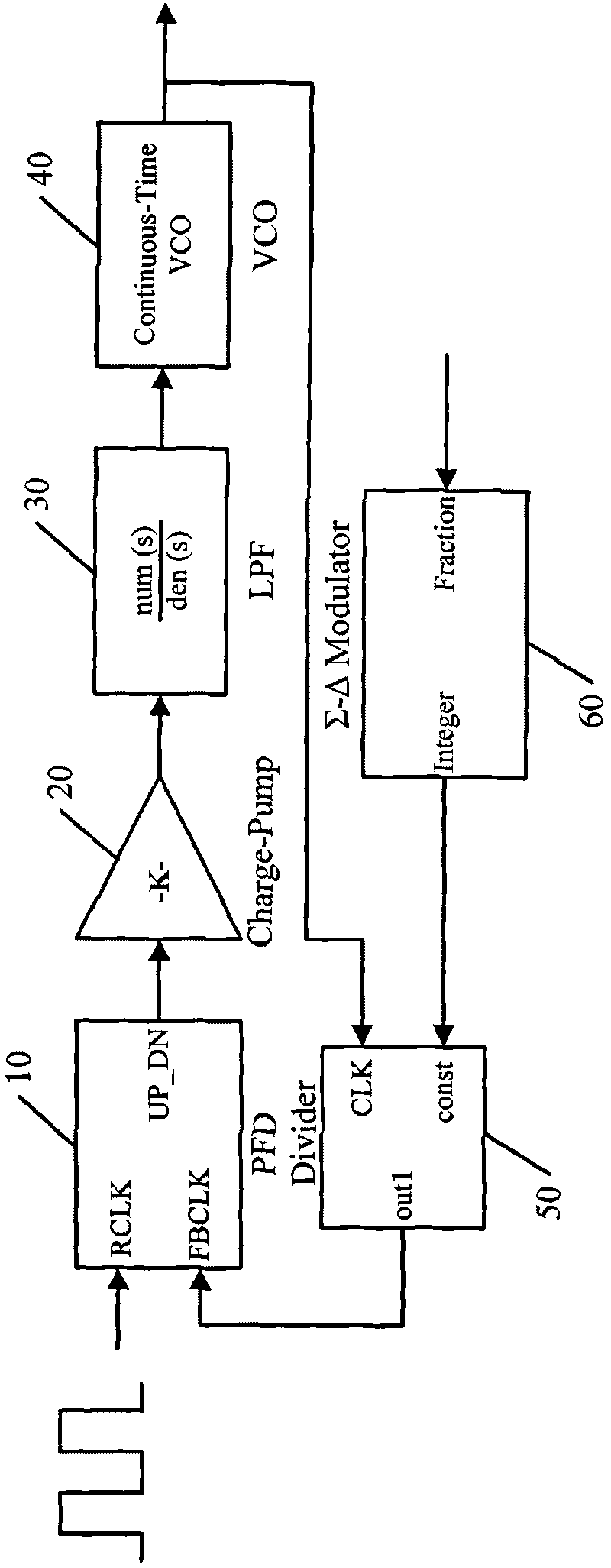

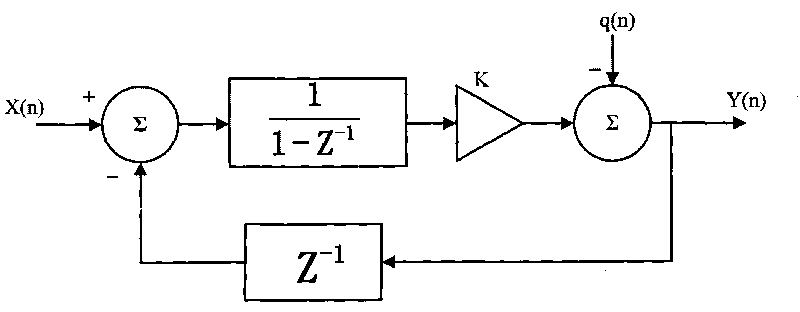

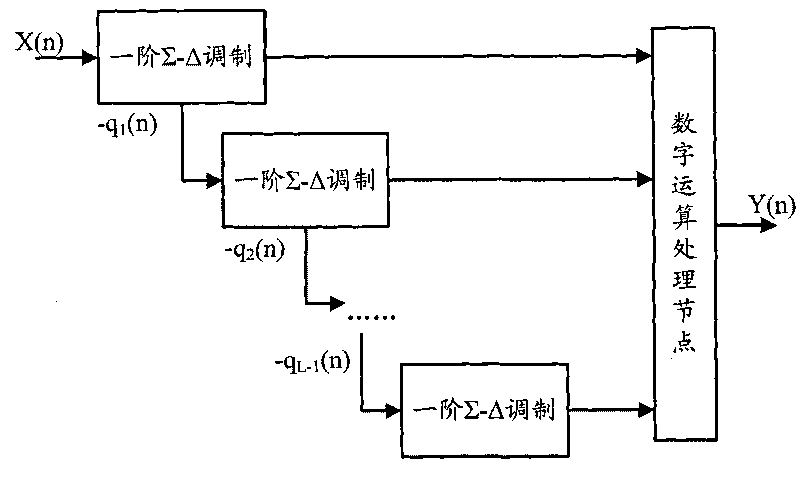

[0051] The processing method of the Σ-Δ modulator with a multi-stage noise shaping (MASH) structure in the prior art is performed bit by bit, and the quantization noise is quantized step by step, and then processed by the operation processing node to offset the noise of each level. quantization noise. In the following embodiments, the quantization noise feedback is used to realize the modulation. For details, please refer to Figure 4 , which is a structural block diagram of a sigma-delta modulation circuit provided by an embodiment of the present invention.

[0052] As shown in the figure, the Σ-Δ modulation circuit uses a fractional input signal (Fraction) F and a noise feedback signal (Error-Feedback) E to generate an integer output signal (Integer) I. The modulat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More