Monolithic FPGA (field programmable gate array) based Chirp Scaling imaging method

An imaging method and single-chip technology, applied in the field of signal processing, can solve the problems of slow DSP running speed, board error code, affecting the real-time performance and stability of imaging, and achieve the goal of ensuring accuracy, improving accuracy, and improving imaging real-time performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

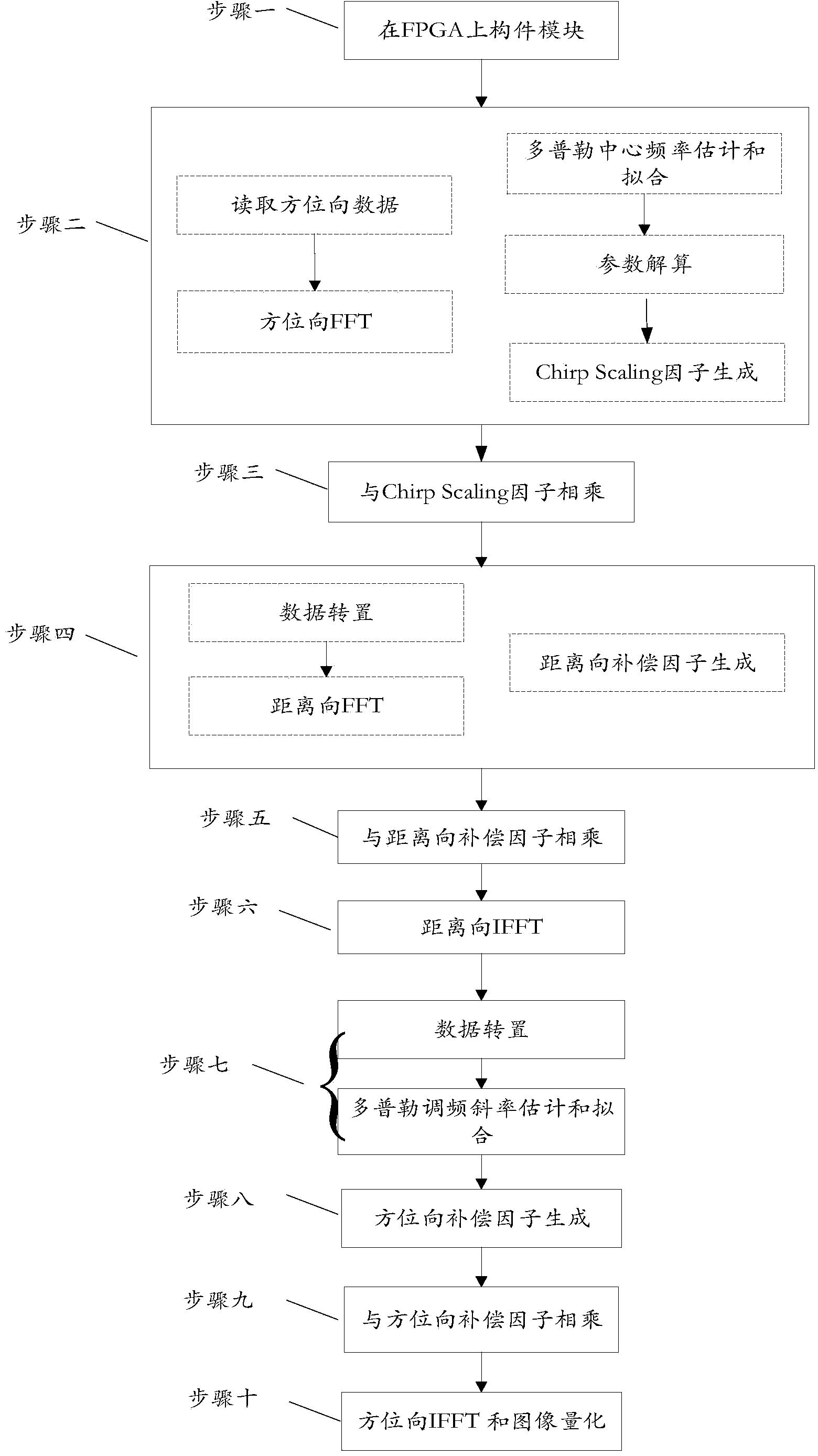

[0042] A kind of Chirp Scaling imaging method based on single-chip FPGA of the present invention, as figure 1 As shown, the specific steps are:

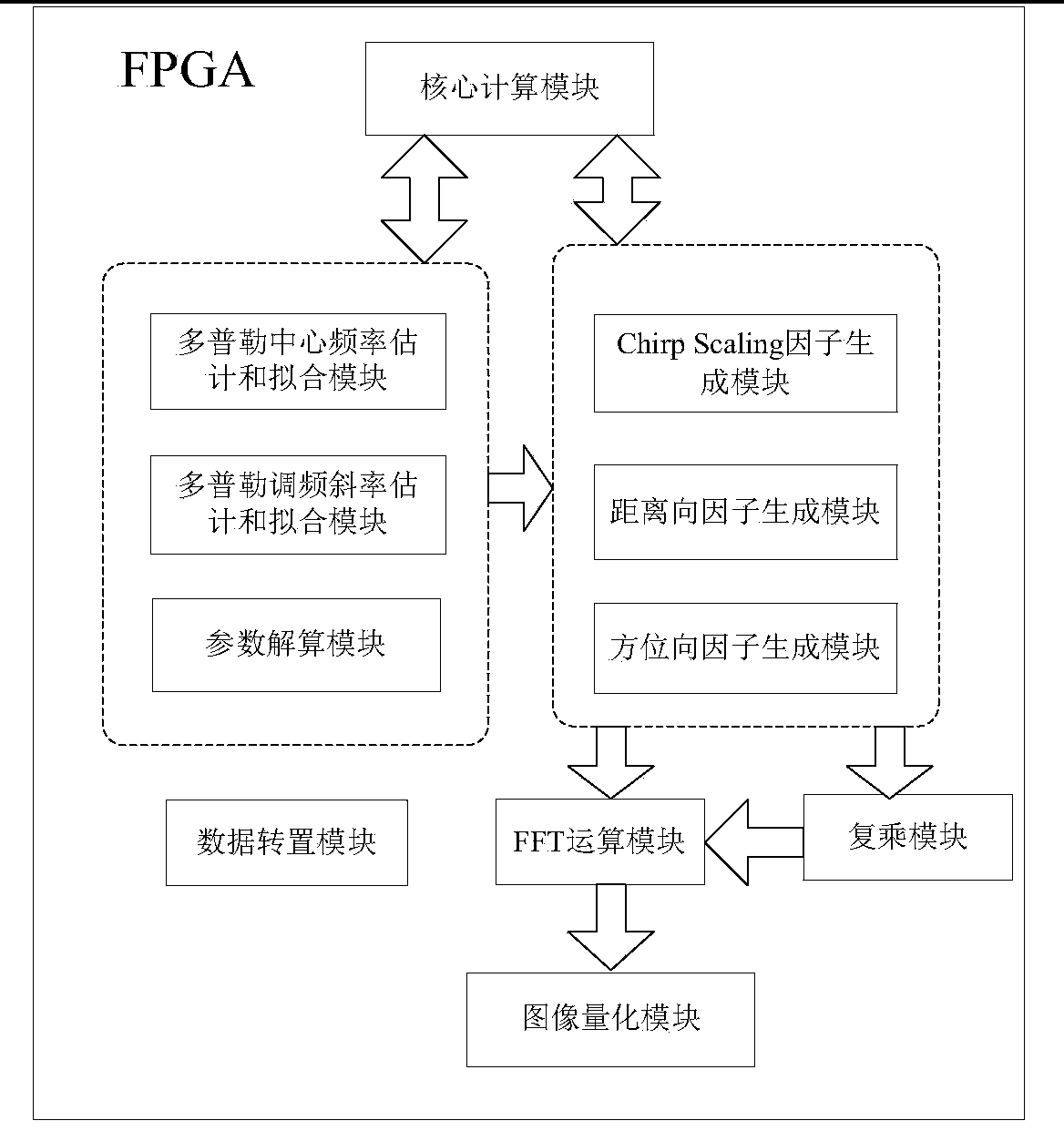

[0043] Step 1: Construct the FFT calculation module, Doppler center frequency estimation and fitting module, Doppler FM slope estimation and fitting module, parameter calculation module, Chirp Scaling factor generation module, and range compensation factor generation on a FPGA module, azimuth compensation factor generation module, multiplication module, data transposition module, core calculation module and image quantization module, such as figure 2 shown.

[0044] Step 2: Perform data processing and Chirp Scaling factor generation in parallel:

[0045] The data processing is as follows: the FFT operation module reads the azimuth echo data from the echo data, and then performs the azimuth fixed-po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More