Device and method for carrying out complex multiplication and butterfly calculation by virtue of floating point unit of processor

A floating-point multiplication and floating-point unit technology, which is applied in complex mathematical operations, machine execution devices, and concurrent instruction execution, can solve problems such as inability to meet real-time requirements, low utilization of hardware resources, large volume and power consumption, etc. Achieve good real-time performance and resource utilization, realize parallel and pipeline computing, and save hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further described below in conjunction with the accompanying drawings and embodiments, and the present invention includes but not limited to the following embodiments.

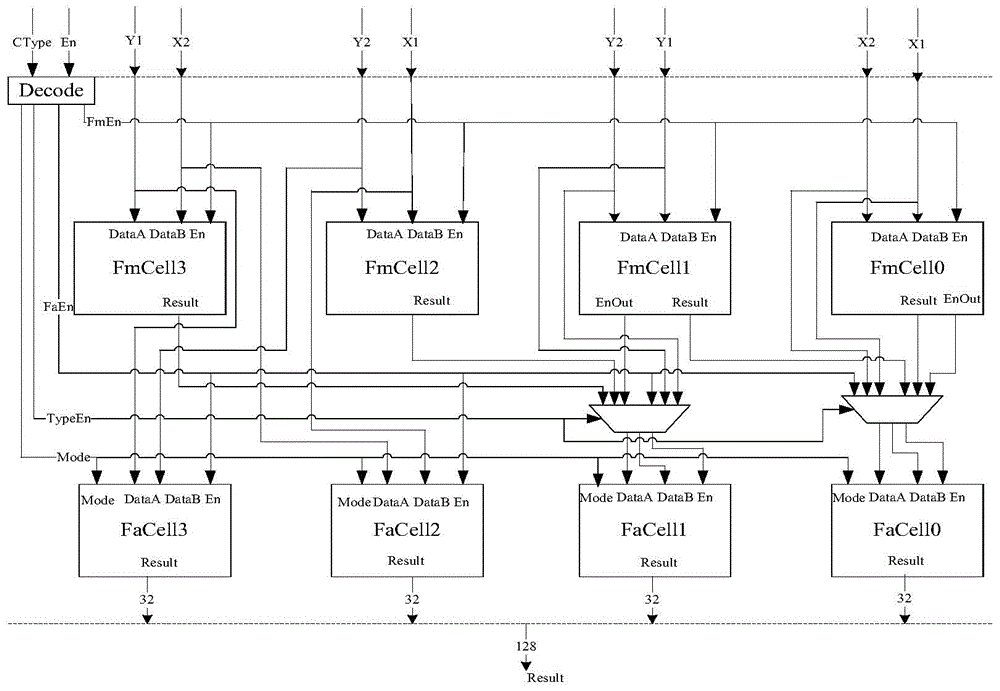

[0023] Adopted following circuit design scheme among the present invention:

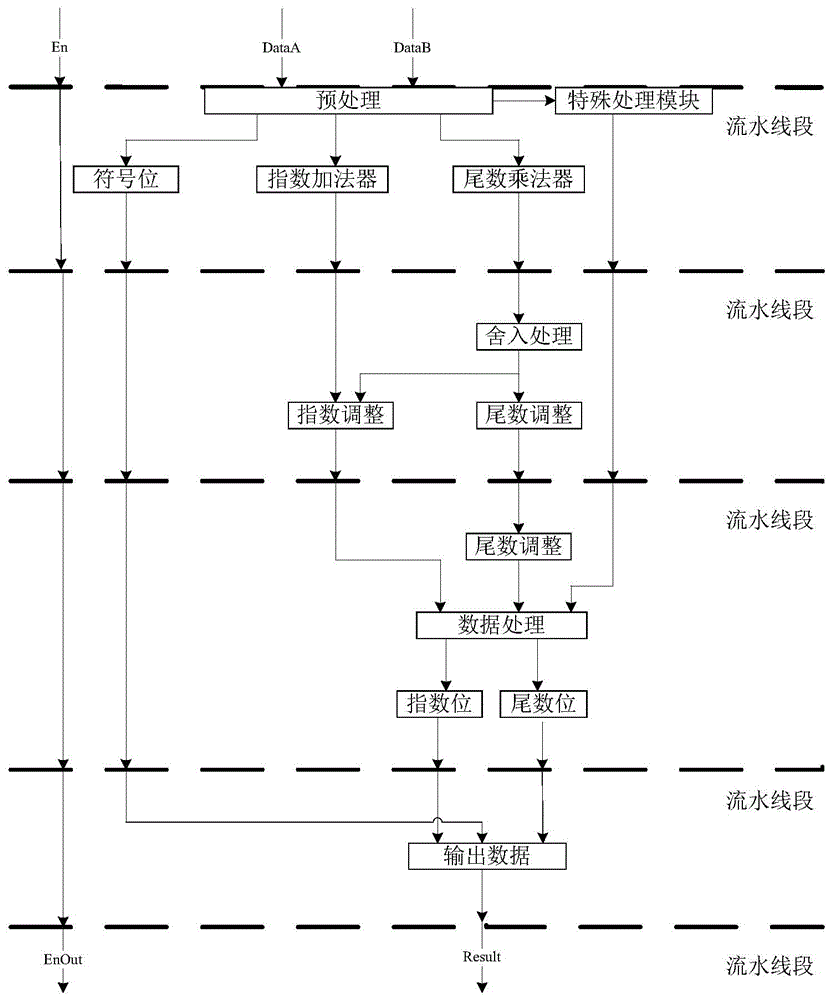

[0024] Firstly, in the present invention, the floating point unit is designed as a floating point addition unit FaCell and a floating point multiplication unit FmCell.

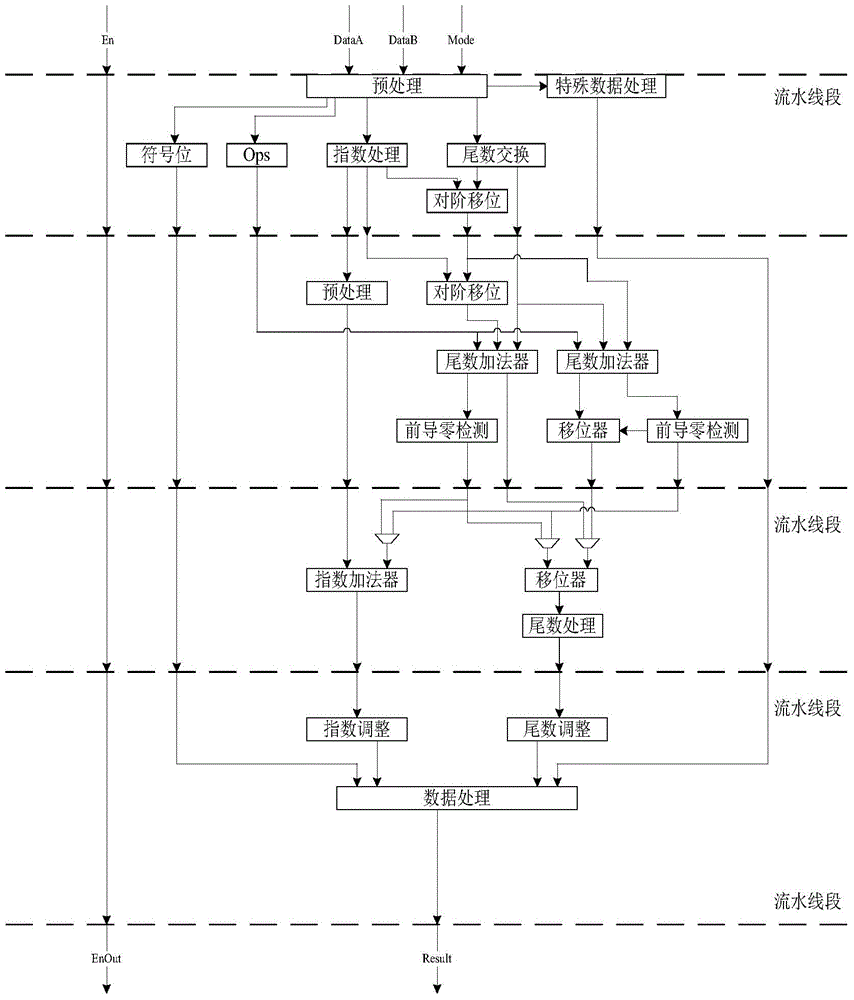

[0025] The input signal of the floating-point addition unit FaCell includes an enable signal FaEn, an operation mode Mode, a data input DataA, and a data input DataB. When the enable signal FaEn is effective, the floating-point addition unit performs a floating-point addition and subtraction operation, otherwise Do not perform any operation, and the operation mode Mode selects floating-point addition and floating-point subtraction operations. The output signal of the floating-point addition unit FaCell includes an enable signal o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More