Split-phase clock tdc based on iserdes series chain and its measurement method

A phase separation and clock technology, applied in the field of time measurement, can solve the problems of measurement accuracy limitation, only to the order of hundreds of picoseconds, and different delay values of delay units, so as to achieve the effect of improving the accuracy of time measurement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Below in conjunction with embodiment the present invention is described in further detail.

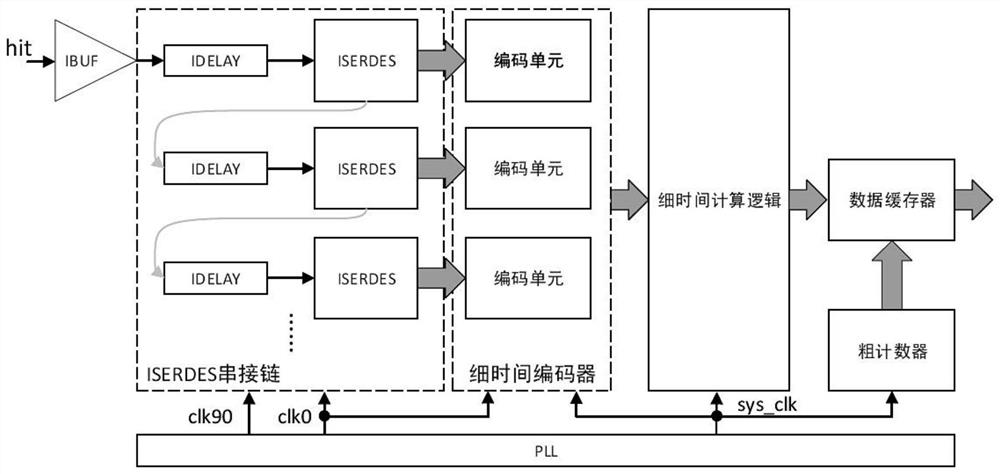

[0038] This embodiment proposes a phase-splitting clock TDC device based on the ISERDES serial chain, such as figure 1 As shown, it includes PLL, ISERDES serial chain, fine time encoder, fine time calculation logic, coarse time counter and data buffer.

[0039] The PLL is used to provide the phase split clock to the ISERDES serial chain and the fine time encoder, while providing the system clock to the fine time encoder, fine time calculation logic, and coarse time counter.

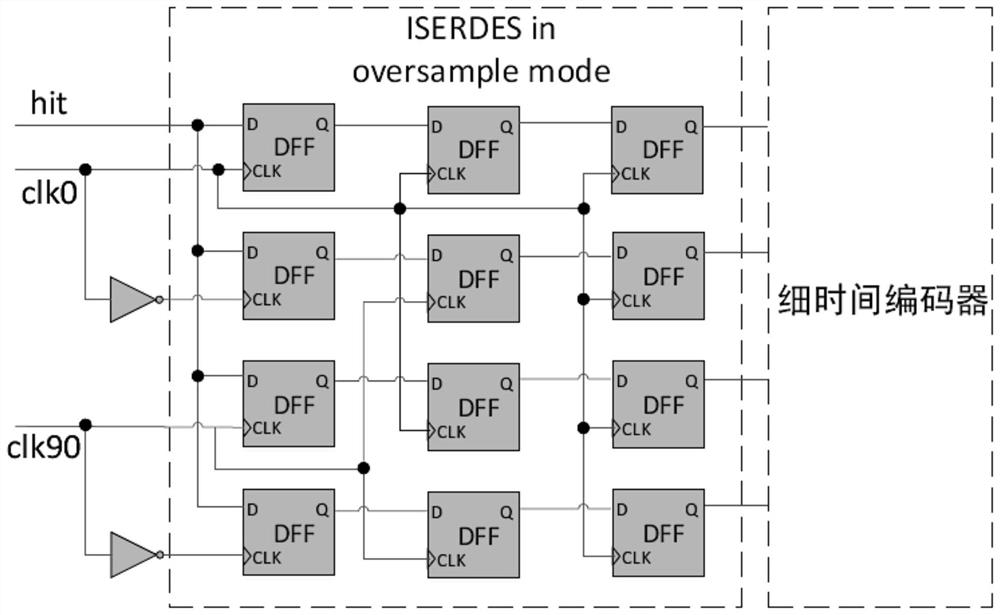

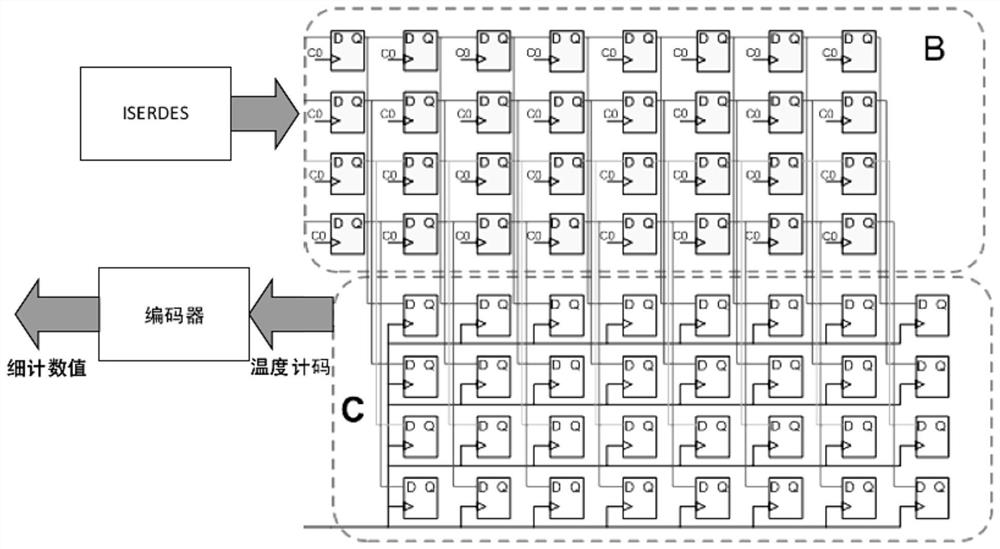

[0040] The ISERDES serial chain includes a multi-level IDELAY core and a multi-level ISERDES fine time sampling unit. The output end of the same level IDELAY core is connected to the input end of the ISERDES fine time sampling unit, and the output end of the upper-level ISERDES fine time sampling unit is connected to the ISERDES fine time sampling unit. The input end of the next-level IDELAY core is connec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More