Digital background cancellation of digital to analog converter mismatch noise in analog to digital converters

a digital to analog converter and background noise technology, applied in the field of noise, can solve the problems of mismatches giving rise to errors, dac noise, and the digital complexity of dnc processing well within practical limits, and achieve the effect of moderated digital hardware complexity and improved overall adc accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045]The following description is of the best mode presently contemplated for the carrying out of the invention. This description is made for the purpose of illustrating the general principles of the invention, and is not to be taken in a limiting sense. The scope of the invention is best determined by reference to the appended claims.

[0046]Although specific embodiments of the invention will now be described with reference to the drawings, it should be understood that such embodiments are by way of example only and are merely illustrative of but a small number of the many possible specific embodiments to which the principles of the invention may be applied. Various changes and modifications obvious to one skilled in the art to which the invention pertains are deemed to be within the spirit, scope and contemplation of the invention as further defined in the appended claims.

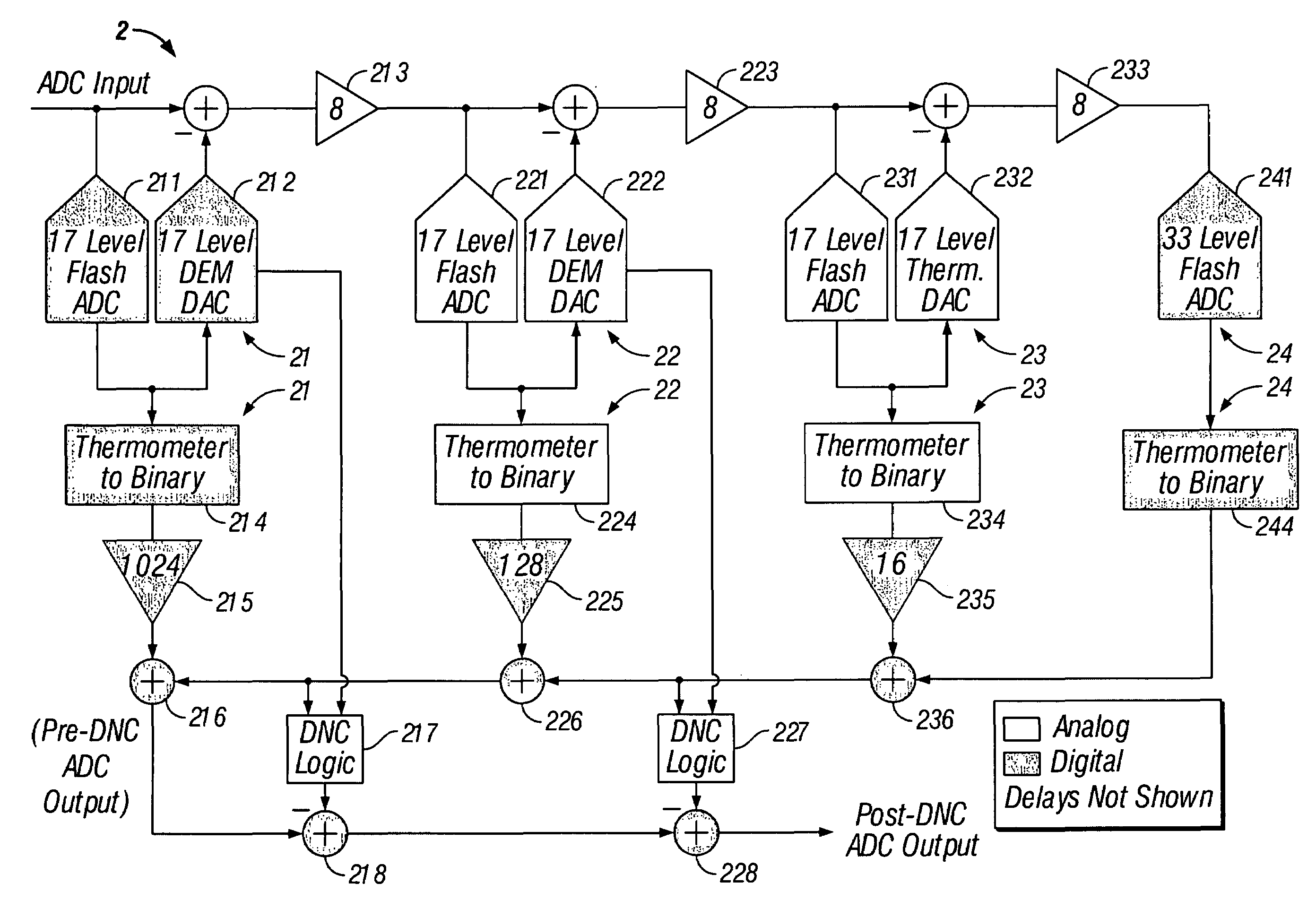

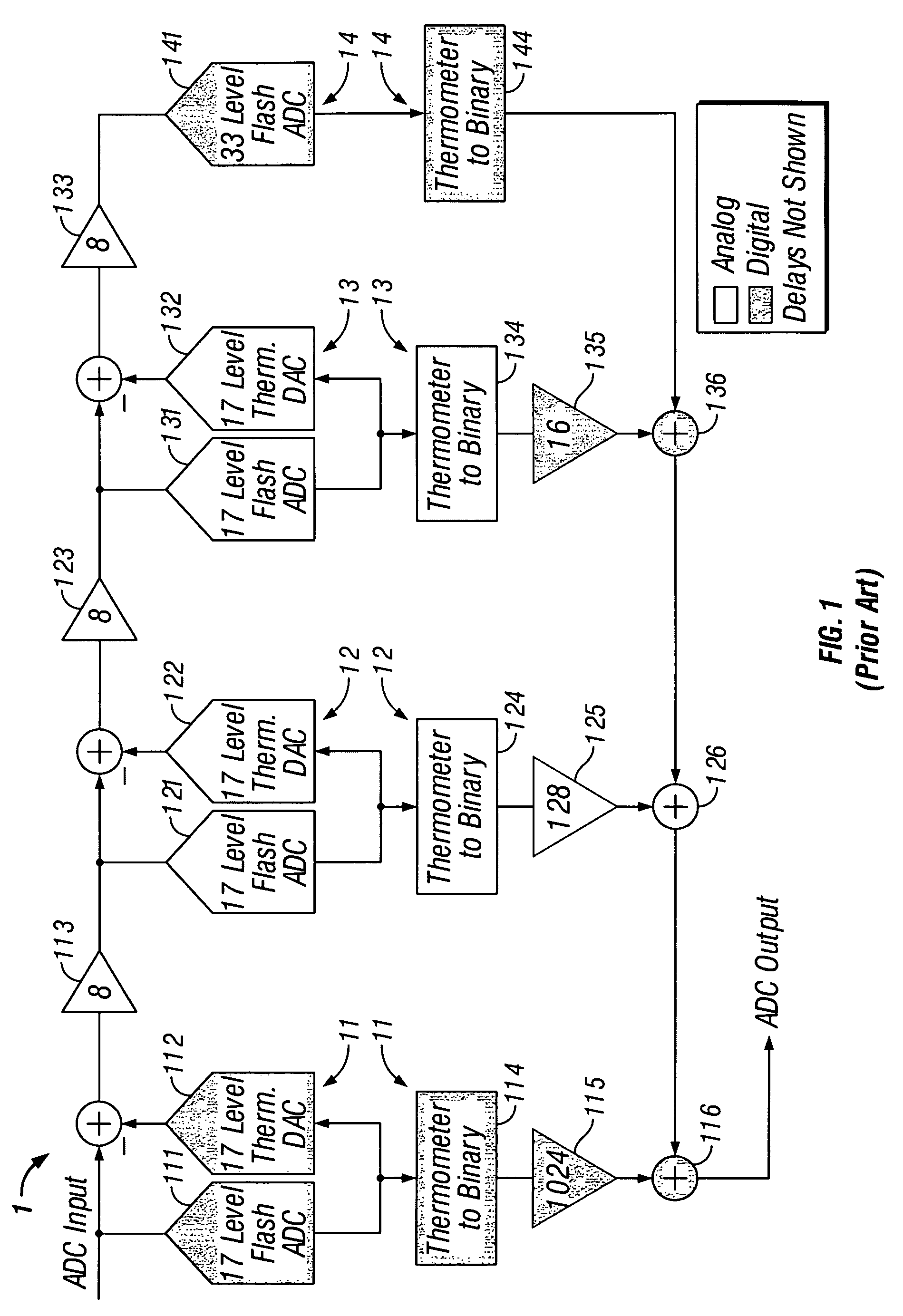

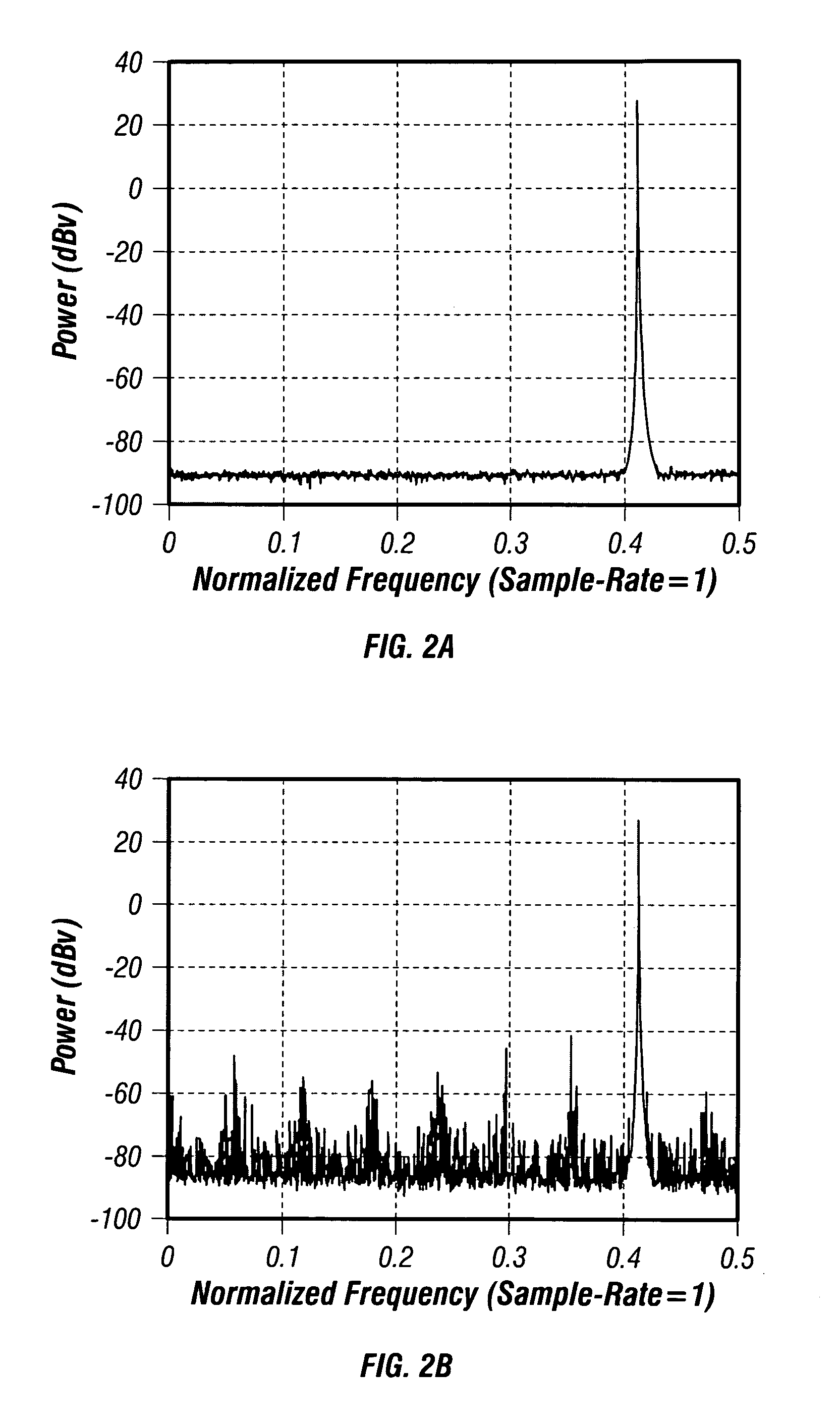

1. Digital Noise Cancellation (DNC)

[0047]In this specification each of the (i) DNC architecture, (ii) operation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More