Patents

Literature

55results about How to "Moderate complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

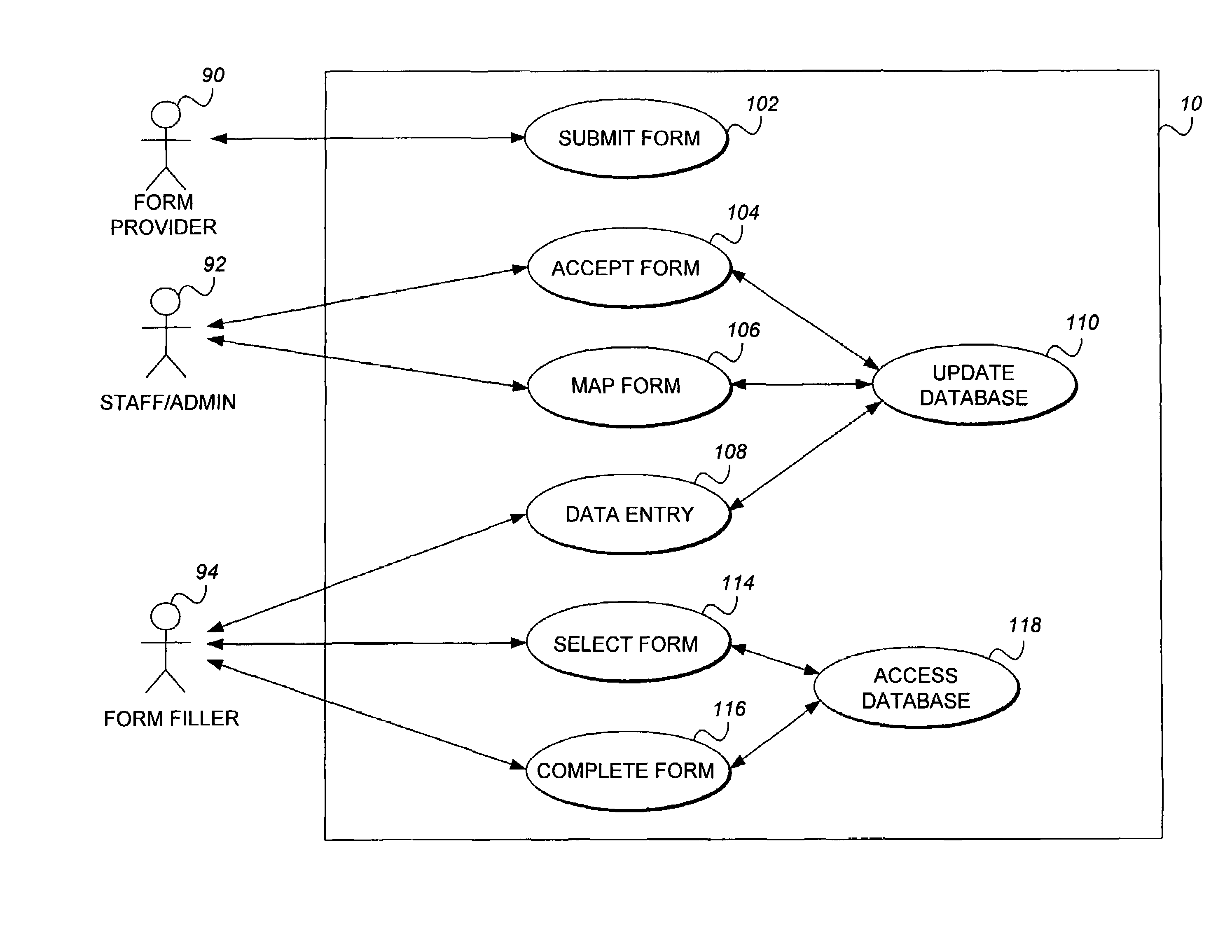

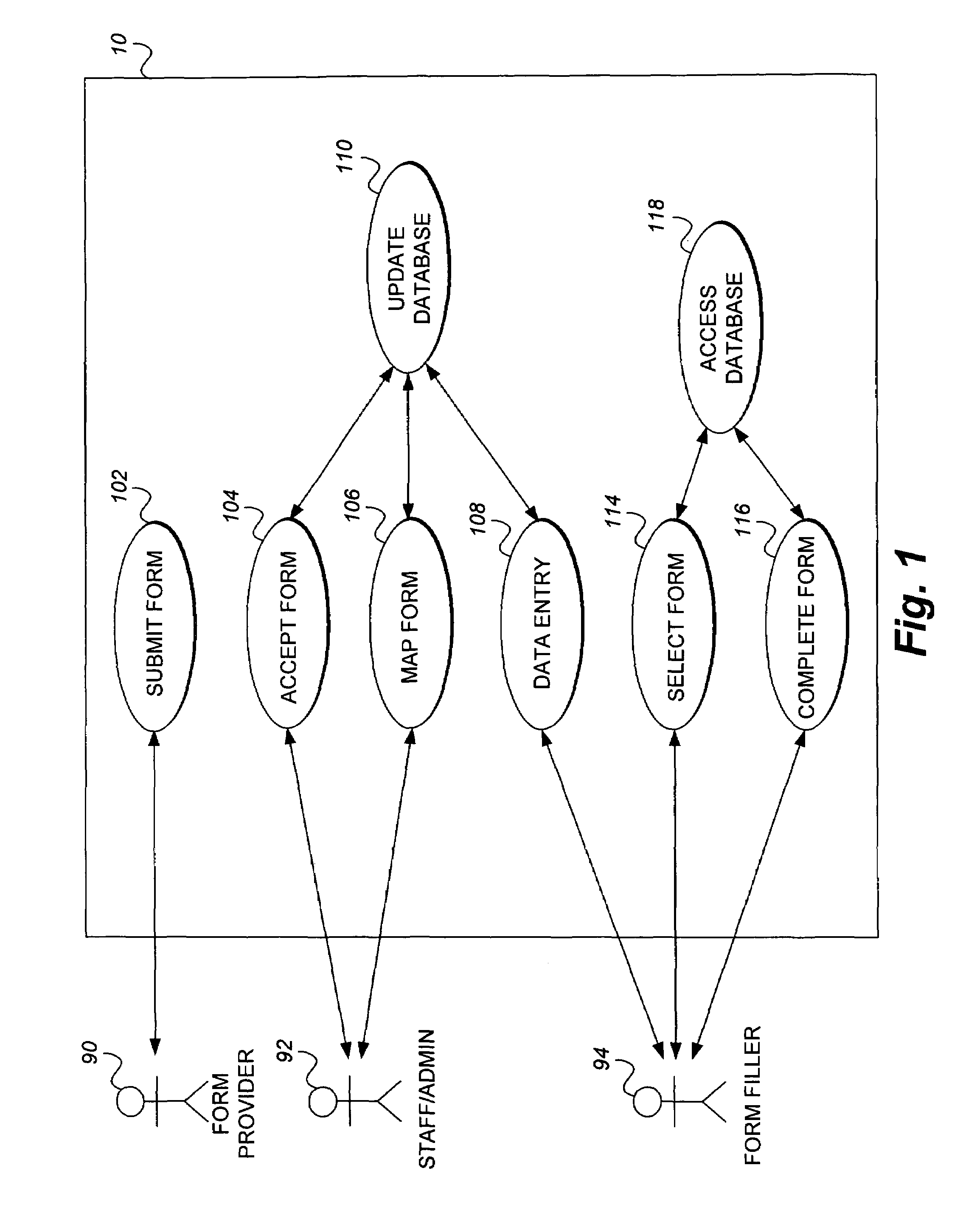

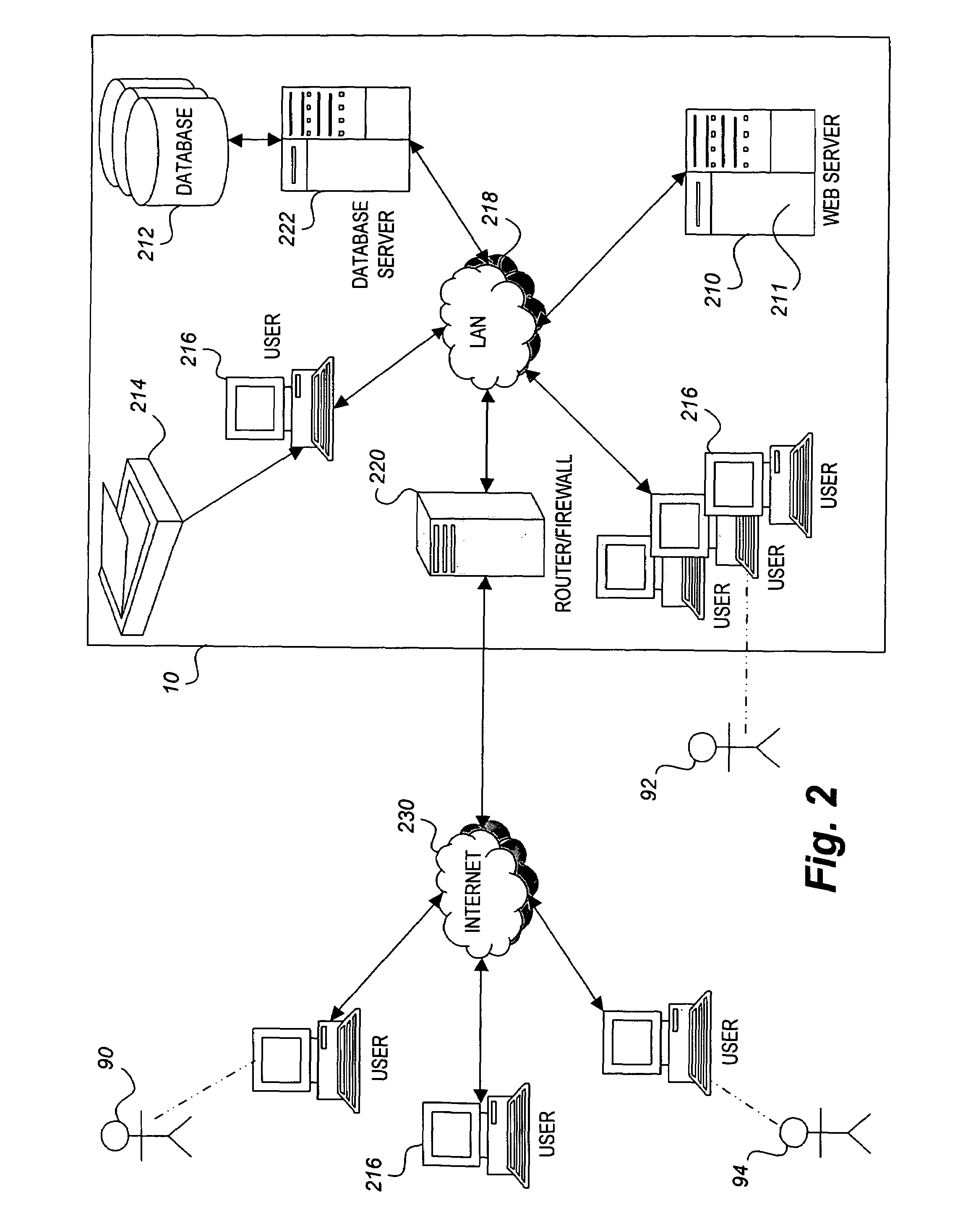

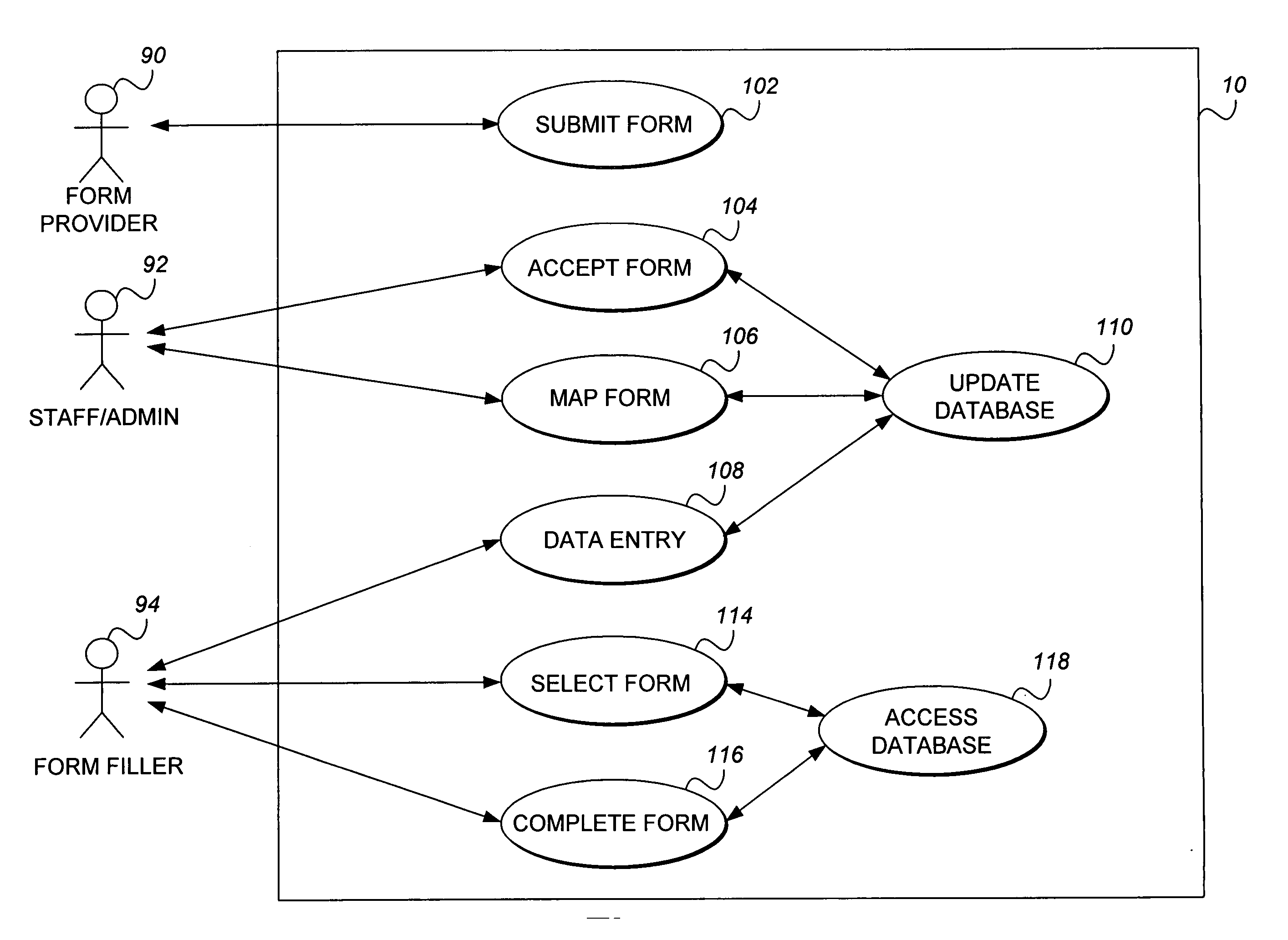

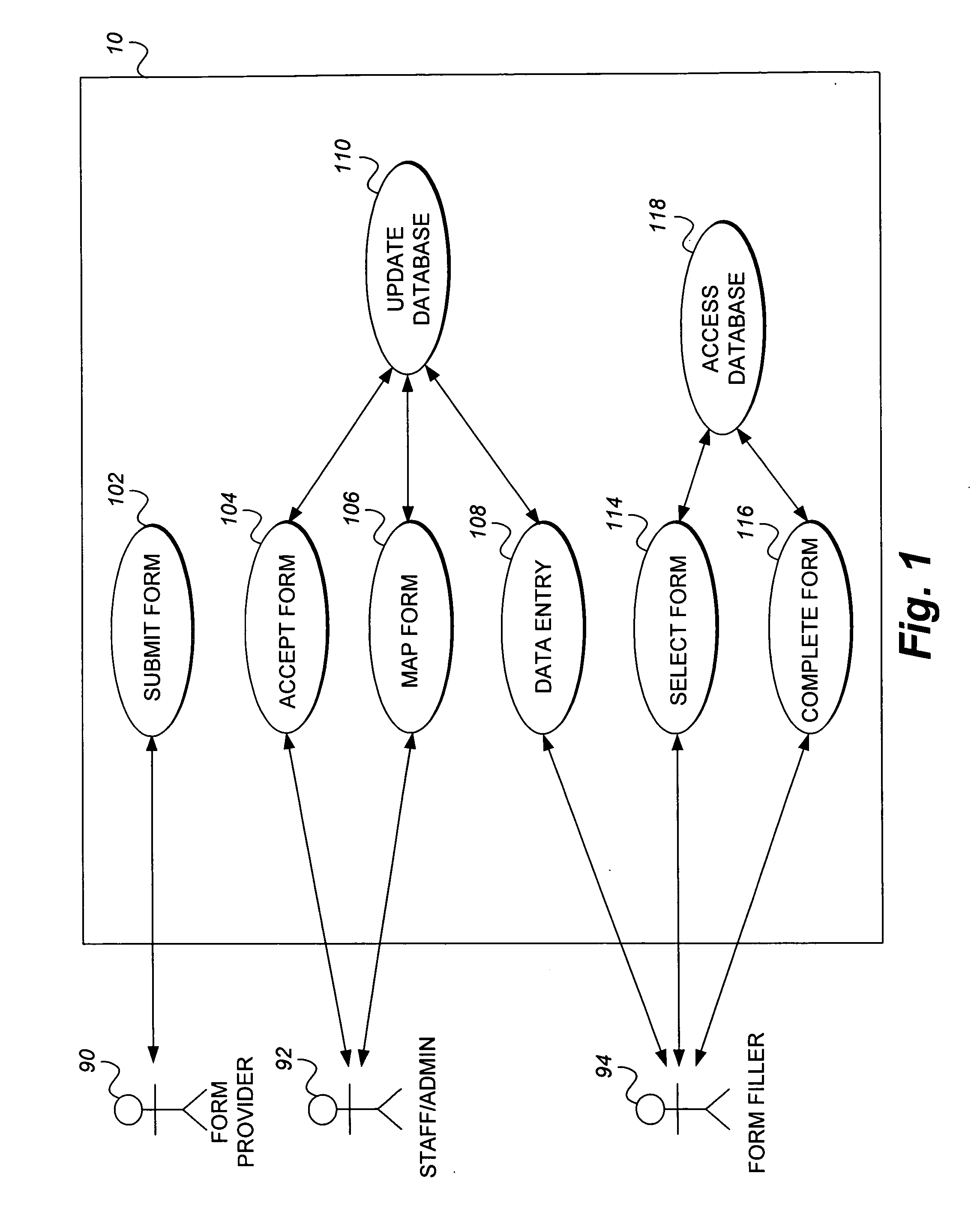

Computerized system for automated completion of forms

InactiveUS7203699B2Increase flexibilityModerate complexityData processing applicationsRelational databasesElectronic formThe Internet

Owner:BELLAMY ROBERT E

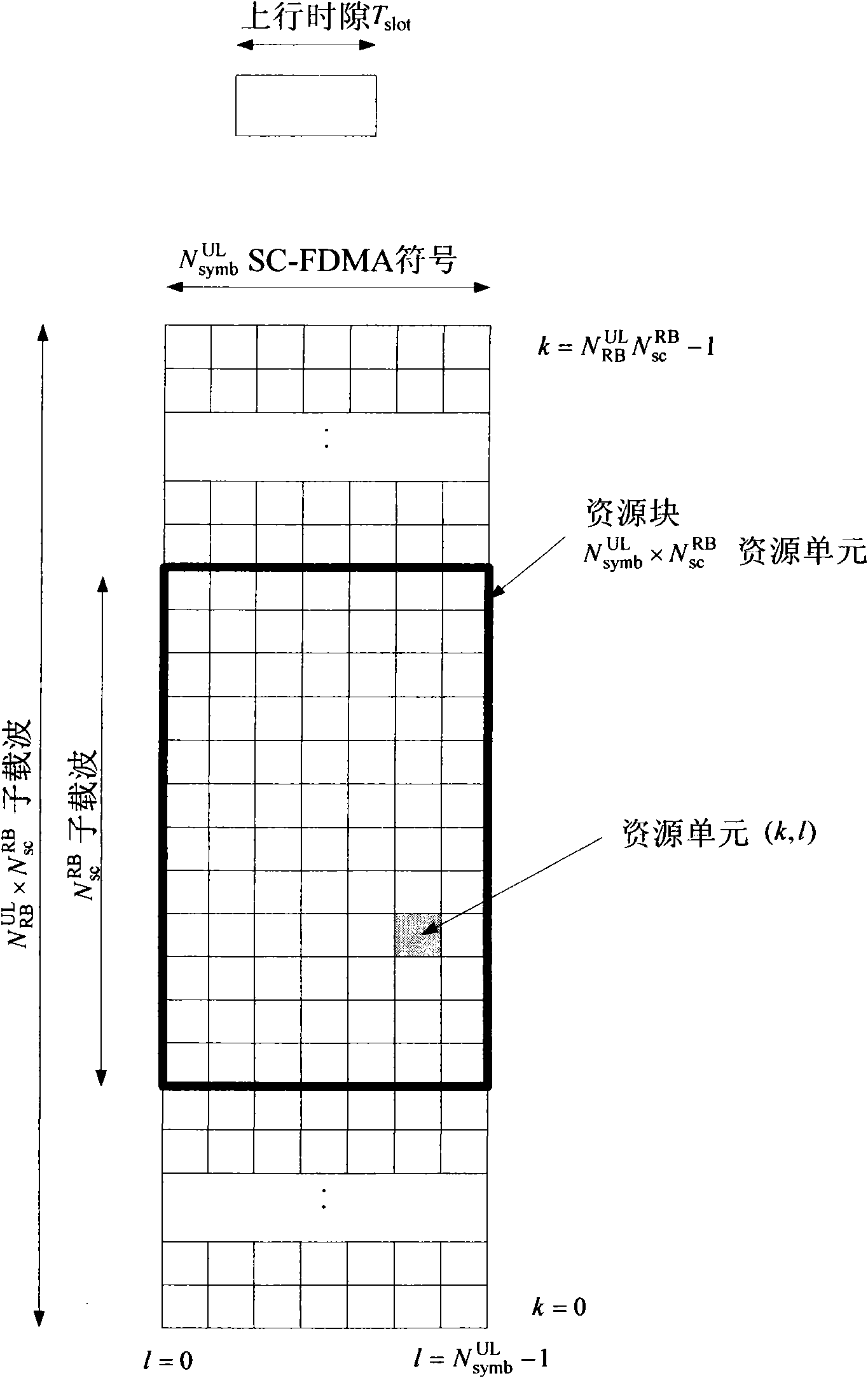

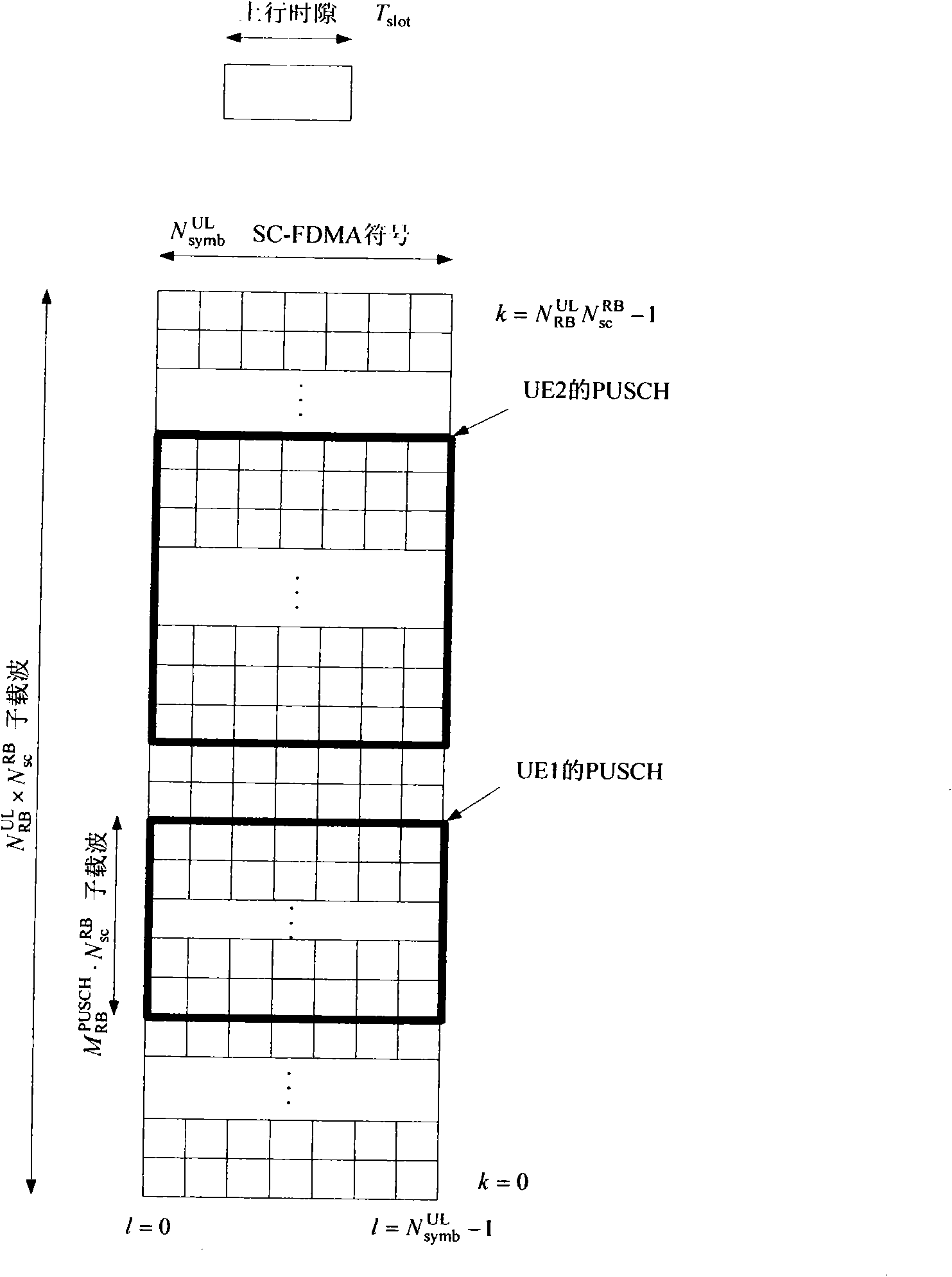

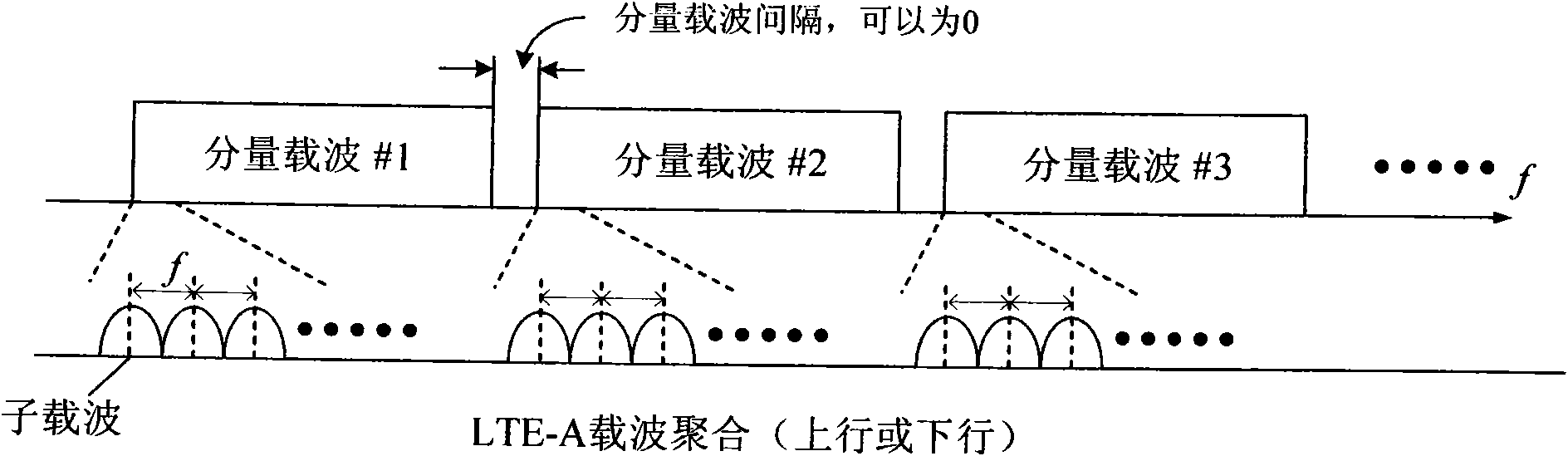

Indicating method and base station, decoding method and terminal for wireless channel resource allocation

ActiveCN101657018AReduce overheadModerate complexityTransmission path divisionWireless communicationBase stationChannel resource allocation

The present invention provides a method for indicating wireless channel resource allocation, indicating a starting position and an ending position of m group(s) distributed to a terminal, and indicating a first RBG and a last RBG for a group containing at least two RBGs; when the group contains one RBG and is not the last one, indicating the RBG contained by the group and a previous RBG of a firstRBG contained by a next group; when the group only contain one RBG and is the last one, indicating the RBG and a virtual RBG; or when the group only contain one RBG and is not the first one, indicating a following RBG of the last RBG contained by a previous group, and the RBG contained by the group; when the group only contain one RBG and is the first one, indicating a virtual RBG and the RBG contained by the group. The invention also provides a corresponding decoding method, a base station and a terminal for the wireless channel resource allocation. According to the invention, no matter whatis a number m of the groups, it is nothing remains but to add one virtual RBG only, such that signalling spending is minimum.

Owner:ZTE CORP

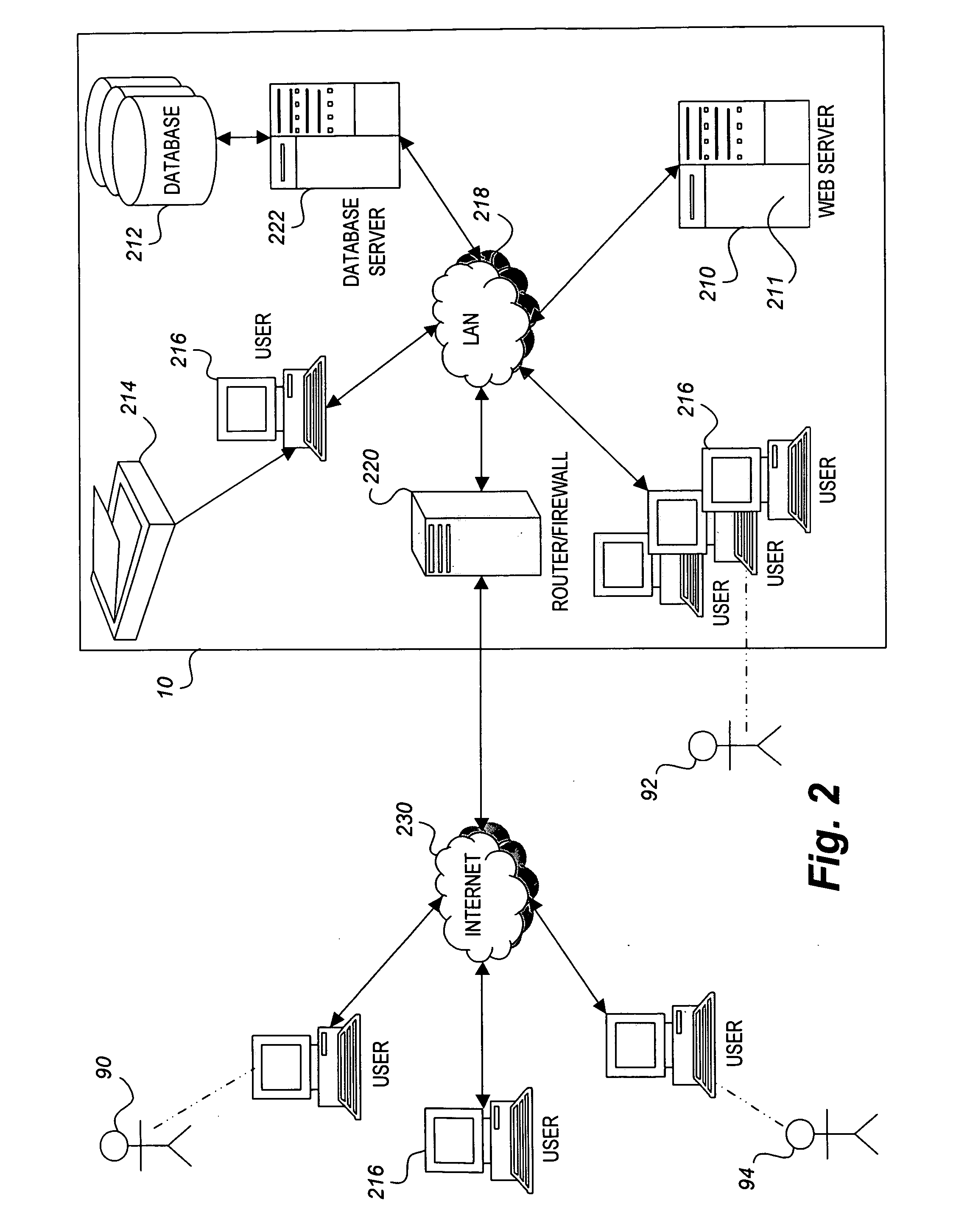

Computerized system for automated completion of forms

InactiveUS20050289114A1Increase flexibilityModerate complexityData processing applicationsRelational databasesElectronic formThe Internet

The computerized system for automated completion of forms is an Internet accessible system for automatically completing forms such as employment or other applications from individual user data retained in a database. The computerized system for automated completion of forms provides for conversion of a paper application form into an electronic form image that is then mapped to identify entry fields, define electronic entry fields associated with the entry fields on the paper form, and associate the electronic entry fields with data item definitions in the database for automatic filling of the form fields form data stored in the database. Users may enter their personal data into the database for subsequent filling of forms either through a default data entry process, or by filling out a first form.

Owner:BELLAMY ROBERT E

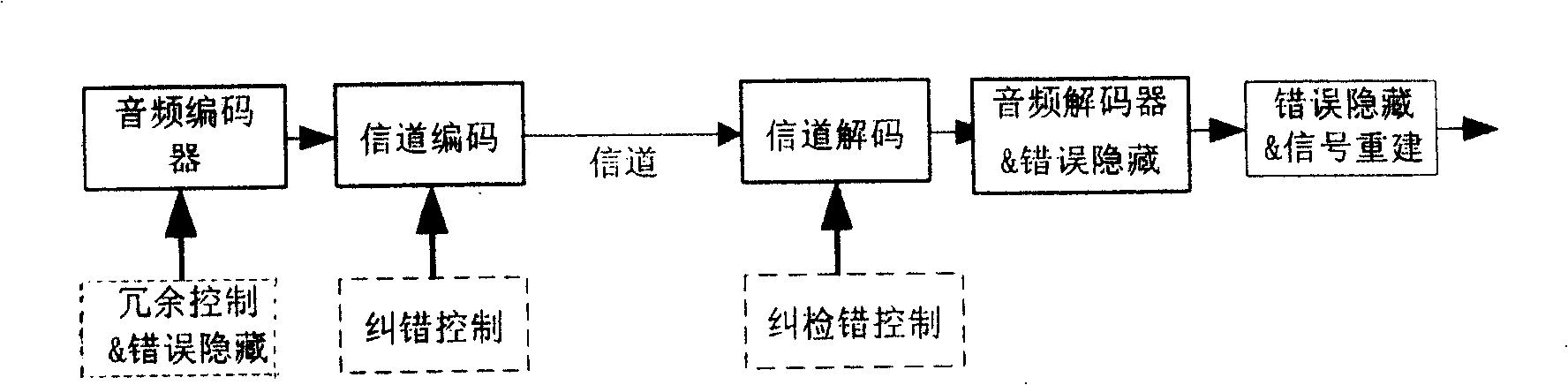

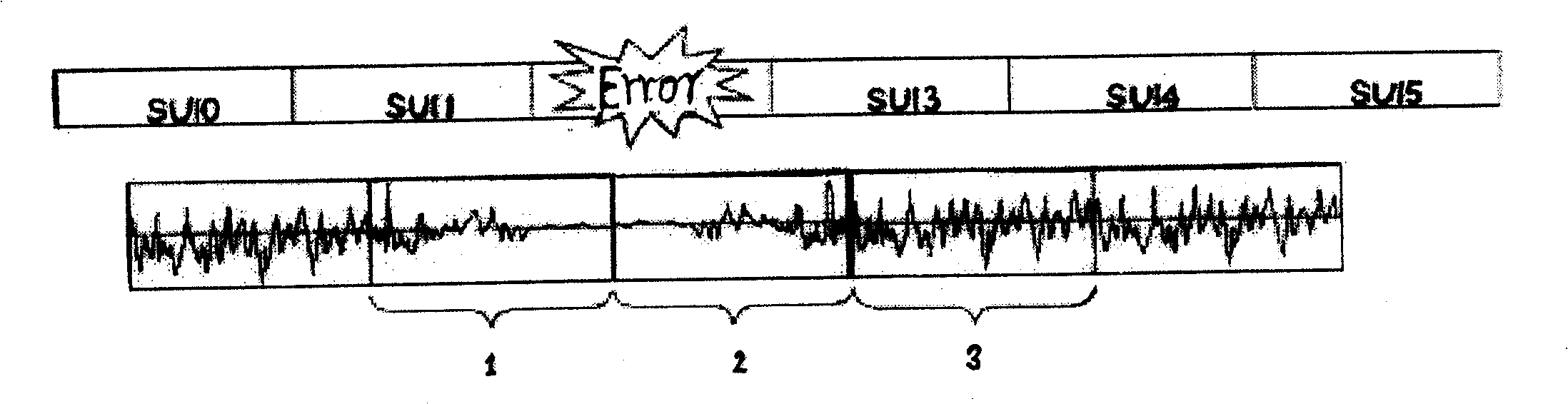

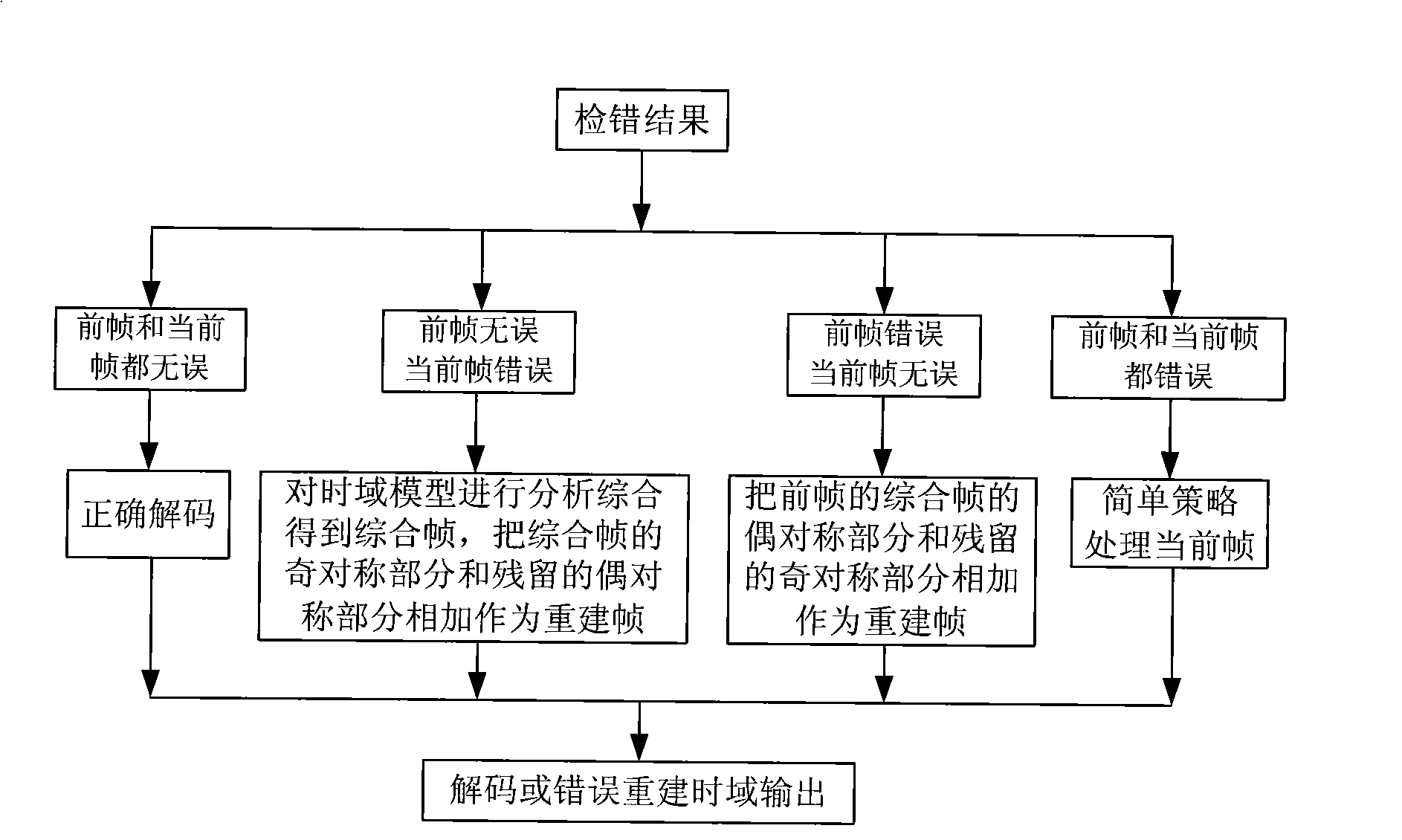

A method for hiding audio error based on sine model

InactiveCN101261833ALower latencyQuality improvementSpeech analysisCode conversionLoss rateError concealment

The invention provides a method for using a sine model to conceal an audio mistake, which belongs to the network and communication field. The operation procedures include: 1. the rebuilding of the whole system is classified into four parallel instances according to the mistakes of a previous frame and a current frame: A. the previous frame and the current frame are both correct and return after being correctly decoded; B. the previous frame is correct and the current frame is wrong, then a time domain model is analyzed and synthesized, and a rebuilding frame is made by overlapping the odd symmetrical section of a synthesized frame and the residual even symmetrical section; C. the previous frame is wrong and the current frame is correct, then a rebuilding frame is made by overlapping the even symmetrical section of the synthesized frame obtained from the model analysis and the residual odd symmetrical section; D. both the previous frame and the current frame are wrong, then the current frame is treated in a simple way; 2. output the obtained decoding result or the wrongly concealed time domain rebuilding. The method is suitable for treatment under various frame loss rates, and the continuous frame loss probability is relatively small for the medium or low frame loss rates, while the medium or high frame loss rates are treated by using a simple frame loss strategy, which can not cause greater audio distortion.

Owner:TSINGHUA UNIV

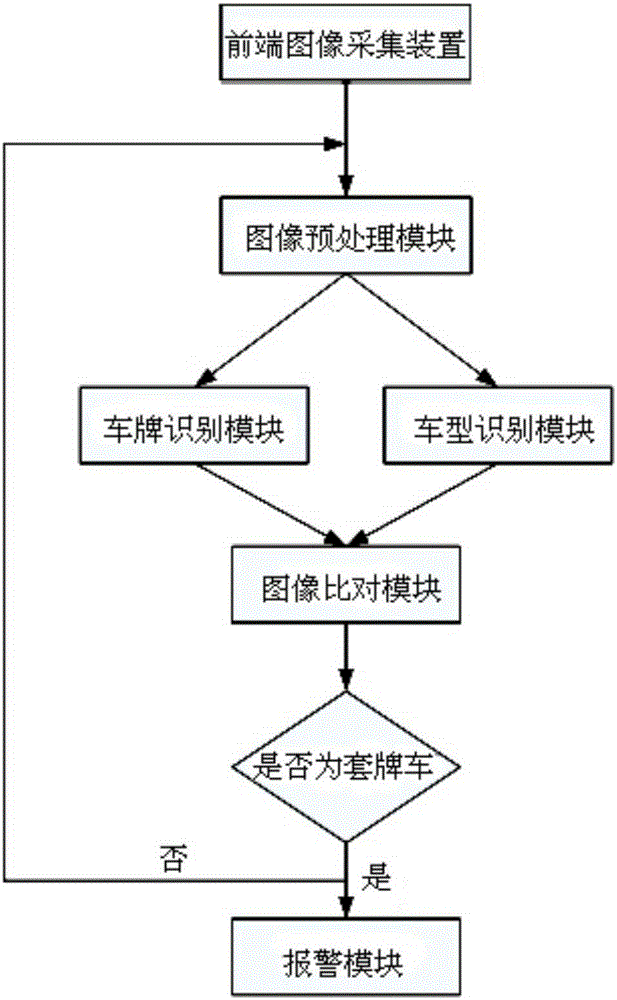

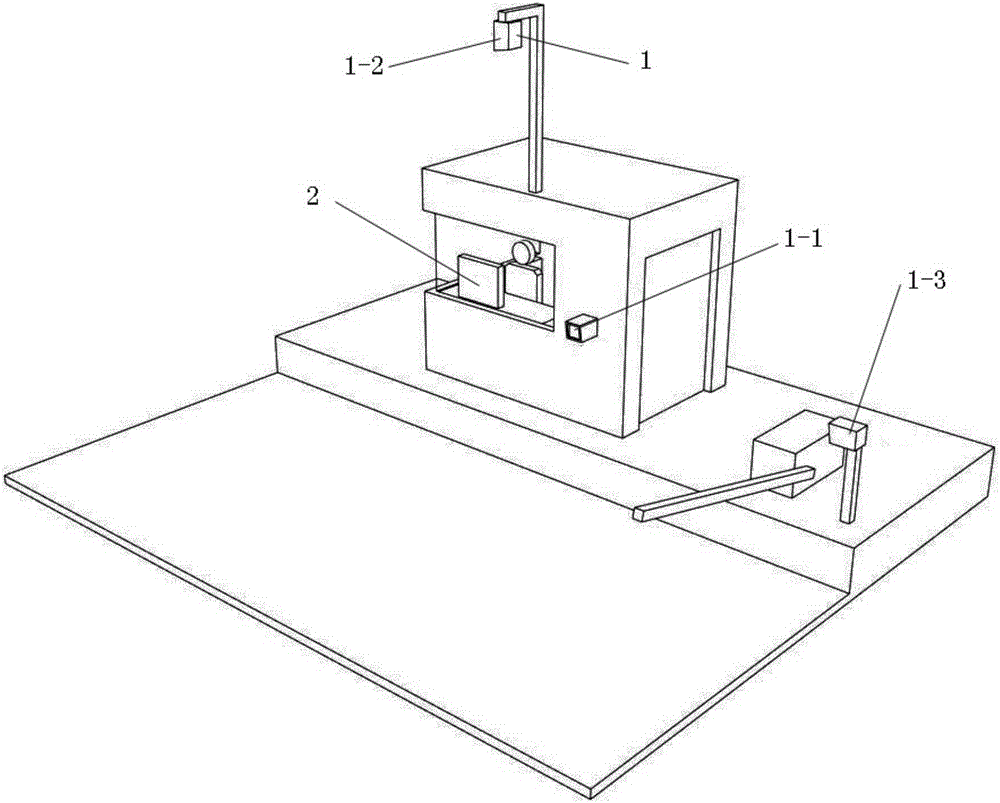

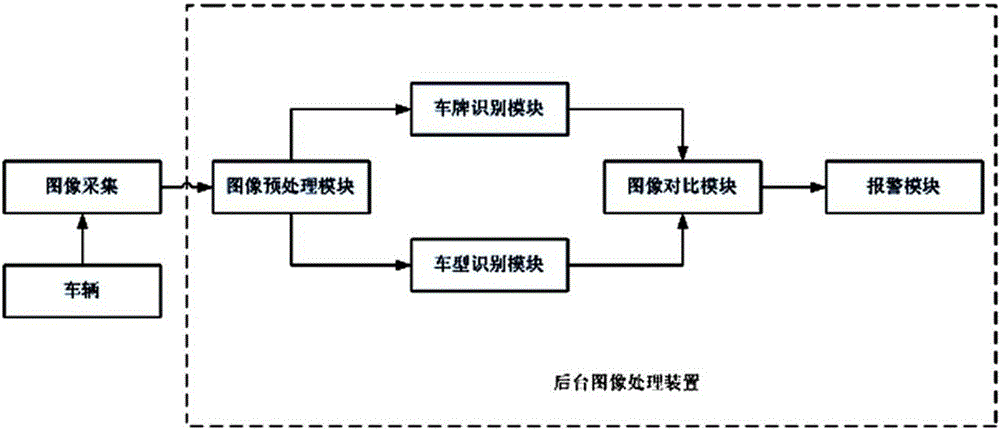

Fake plate vehicle recognition system and method

InactiveCN105185123AImprove timelinessHigh precisionRoad vehicles traffic controlAlgorithm complexityHardware structure

The invention discloses a fake plate vehicle recognition system and method. The system comprises a front end image acquisition device and a background image processing device which are in connection through a data line; the front end image acquisition device is installed at a road toll station entrance or a parking lot entrance, and comprises a side camera, a top camera and a front camera. The fake plate vehicle recognition system is an automatic intelligent query system, and can query actively; once finding a mode fake plate vehicle, the fake plate vehicle recognition system can inform traffic management departments at the first time, thereby improving the timeliness of investigating and penalizing fake plate vehicles of associated departments. The system can compare information including vehicle logos, license plates, vehicle colors, etc., and as detailed as vehicle models and configuration, thereby improving the accuracy of investigating and penalizing fake plate vehicles; a constructed nerve network has a reasonable structure, algorithm complexity is moderate, and operation is fast; the system has a simple hardware structure, and is easy to realize.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

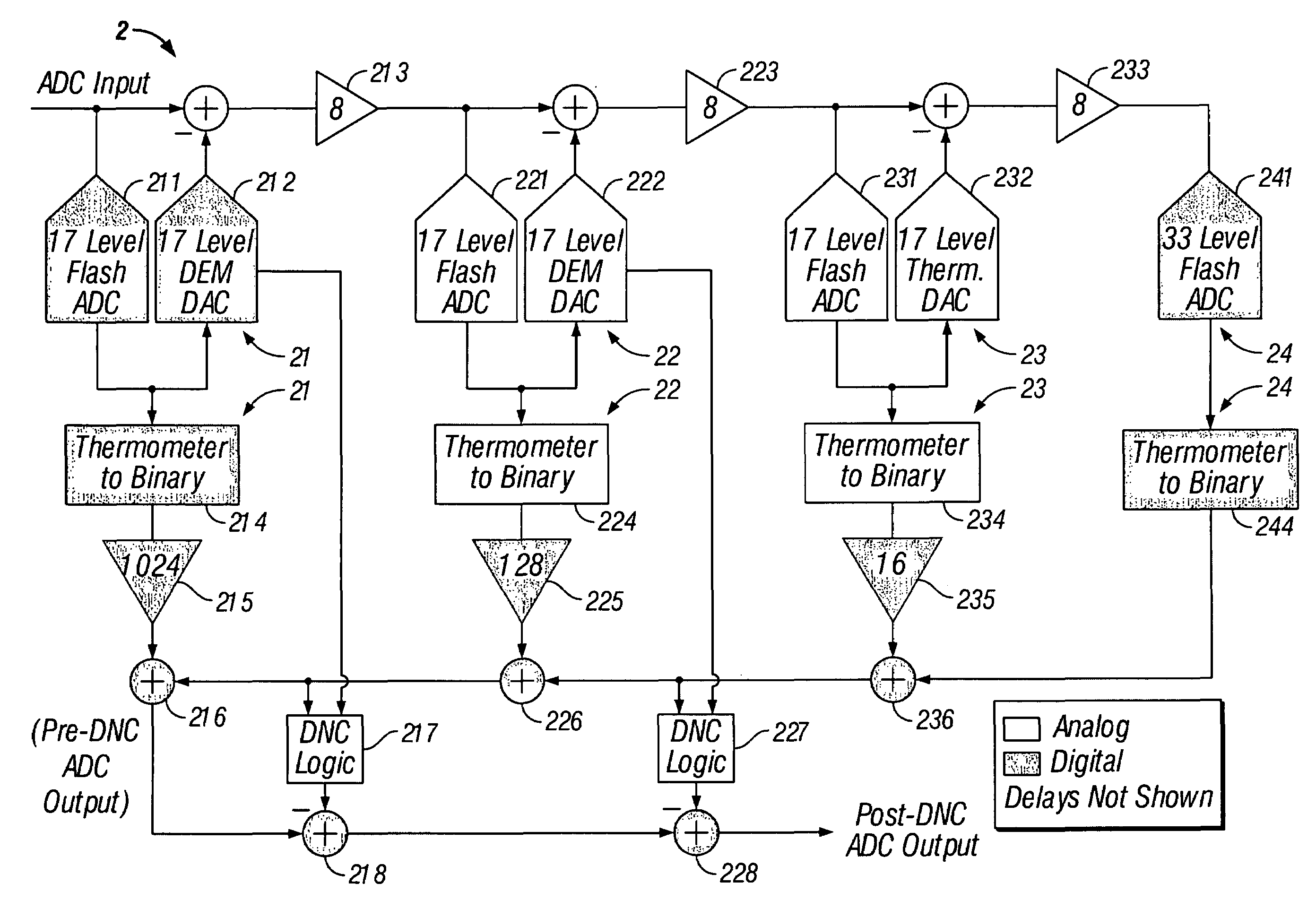

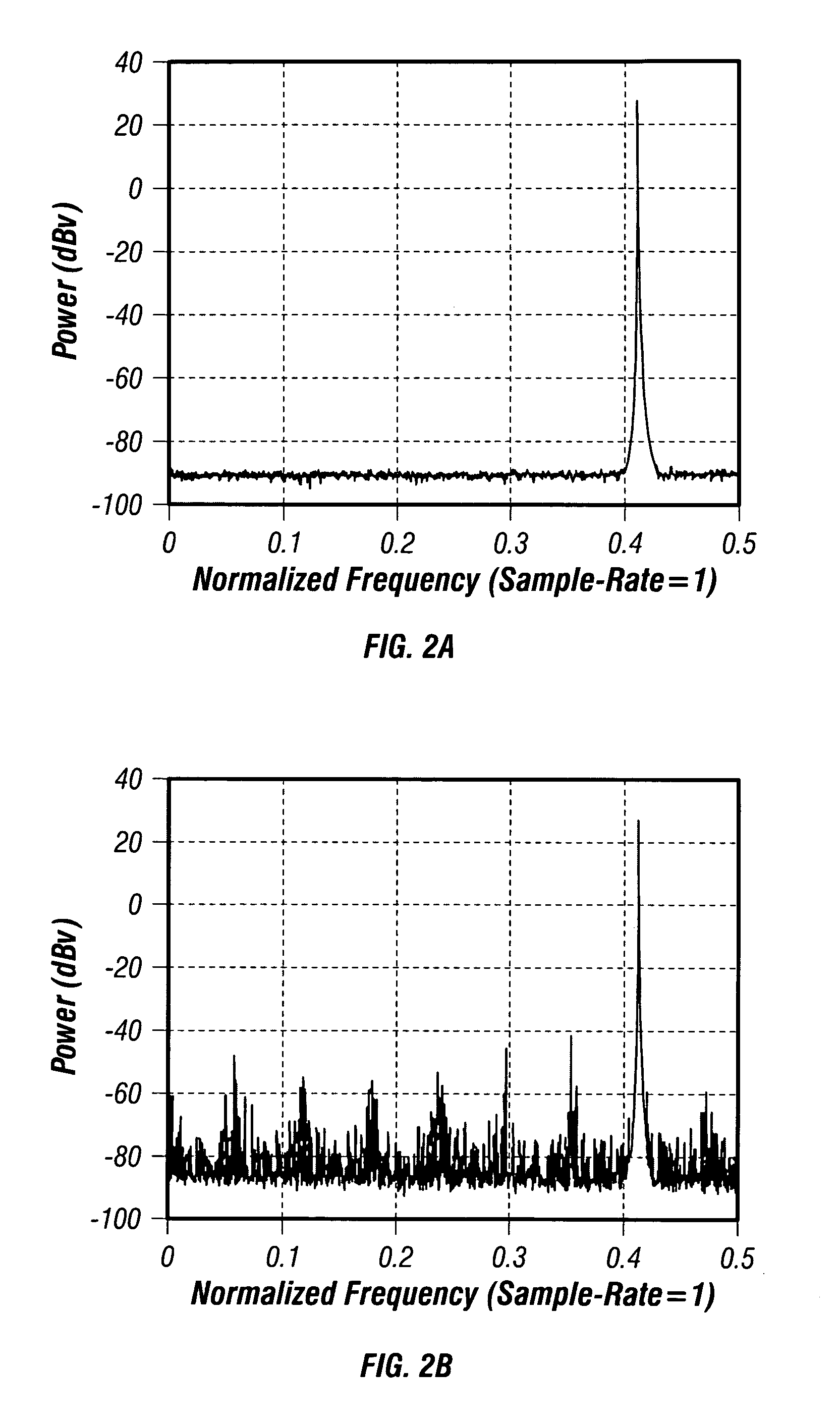

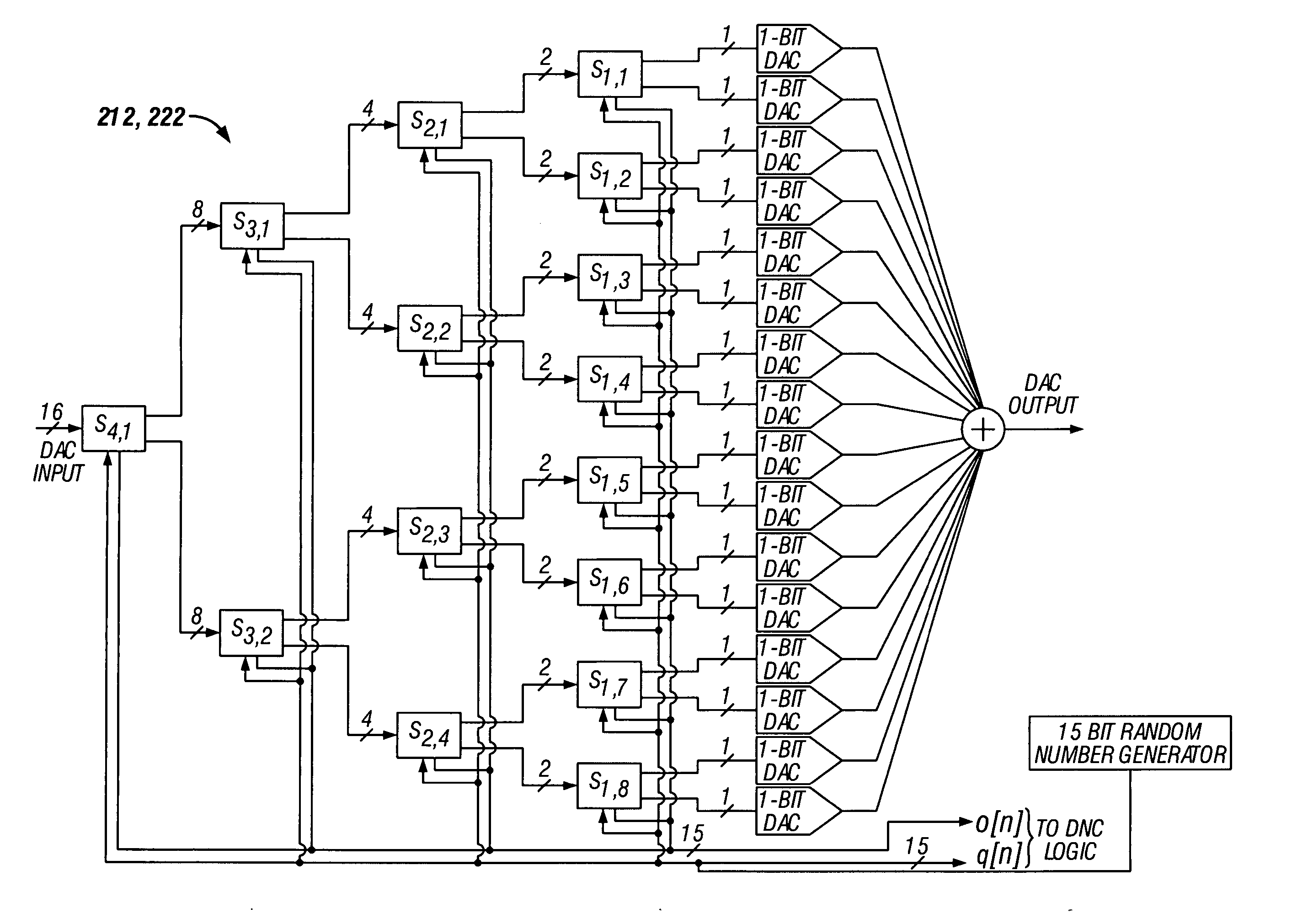

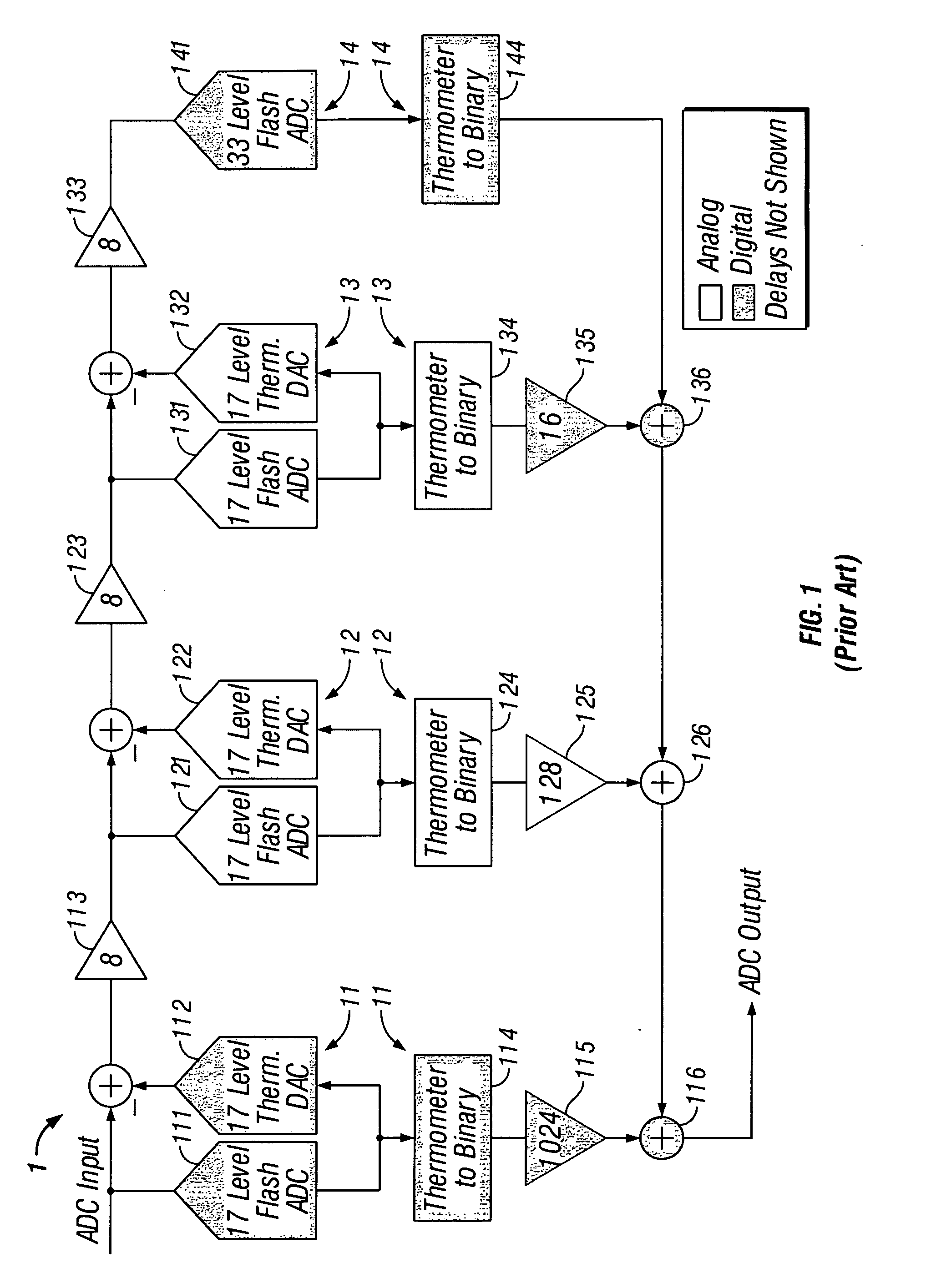

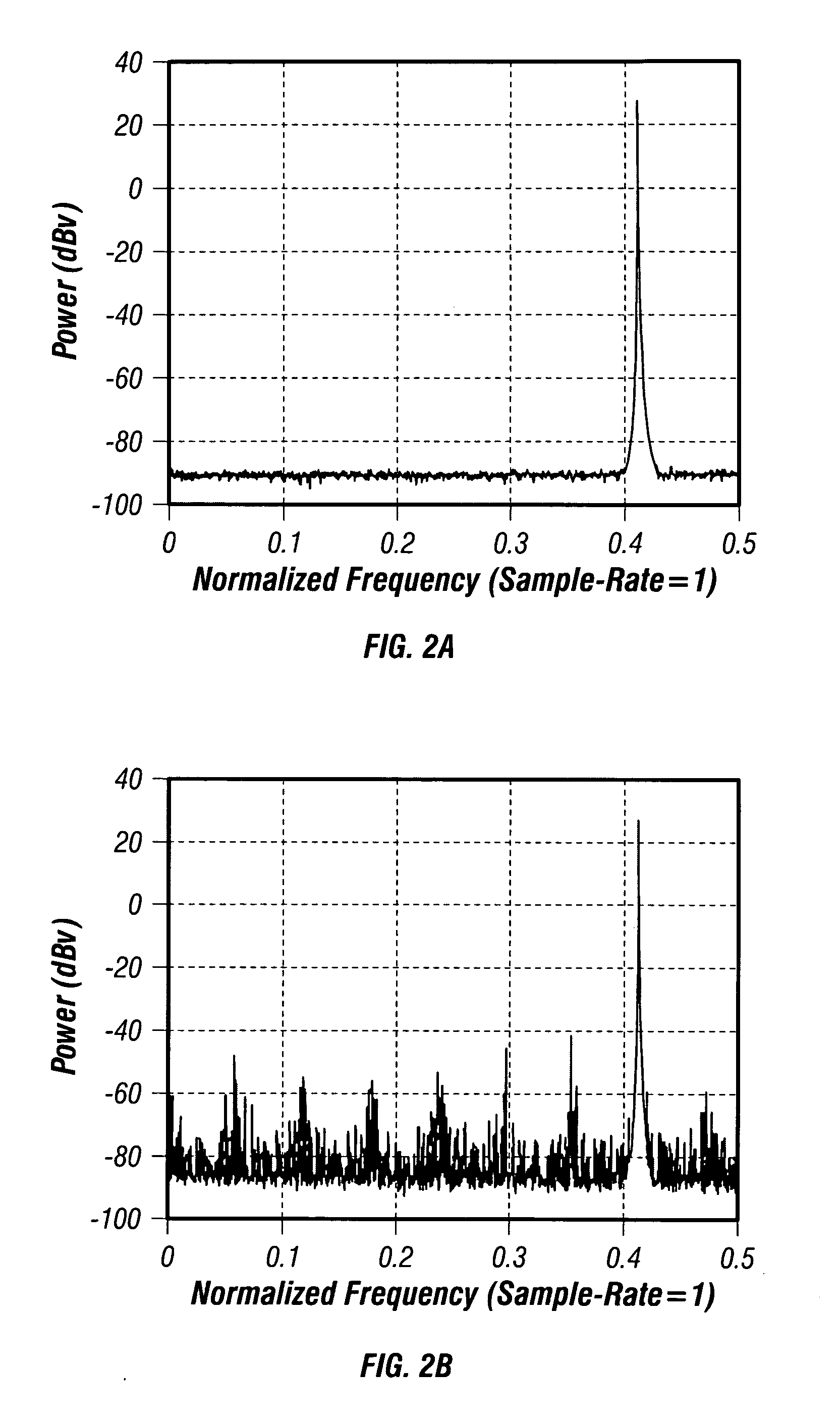

Digital background cancellation of digital to analog converter mismatch noise in analog to digital converters

InactiveUS7006028B2Reduce decreaseImprove accuracyElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

Devices for performing analog-to-digital conversion with reduced noise. In one implementation, an analog-to-digital converter includes at least one internal digital-to-analog converter (DAC) that comprises a plurality of analog components and converts an intermediate digital signal into an associated intermediate analog signal, a dynamic element matching (DEM) circuit coupled to the DAC to permute configurations of the analog components within the DAC, a noise cancellation circuit and a digital subtractor block. The noise cancellation circuit is coupled to receive a first digital sequence comprising a component of a digitized representation of an analog output of the DAC, and a second digital sequence representing a state of the DEM circuitry. The noise cancellation circuit is operable to combine the first and the second digital sequences so as to estimate a digital representation of a DAC noise caused by error sequence introduced mismatches among the analog components within the DAC. The digital subtractor block is coupled to the noise cancellation circuit and operable to use the estimated digital representation of the DAC noise to reduce the DAC noise.

Owner:RGT UNIV OF CALIFORNIA

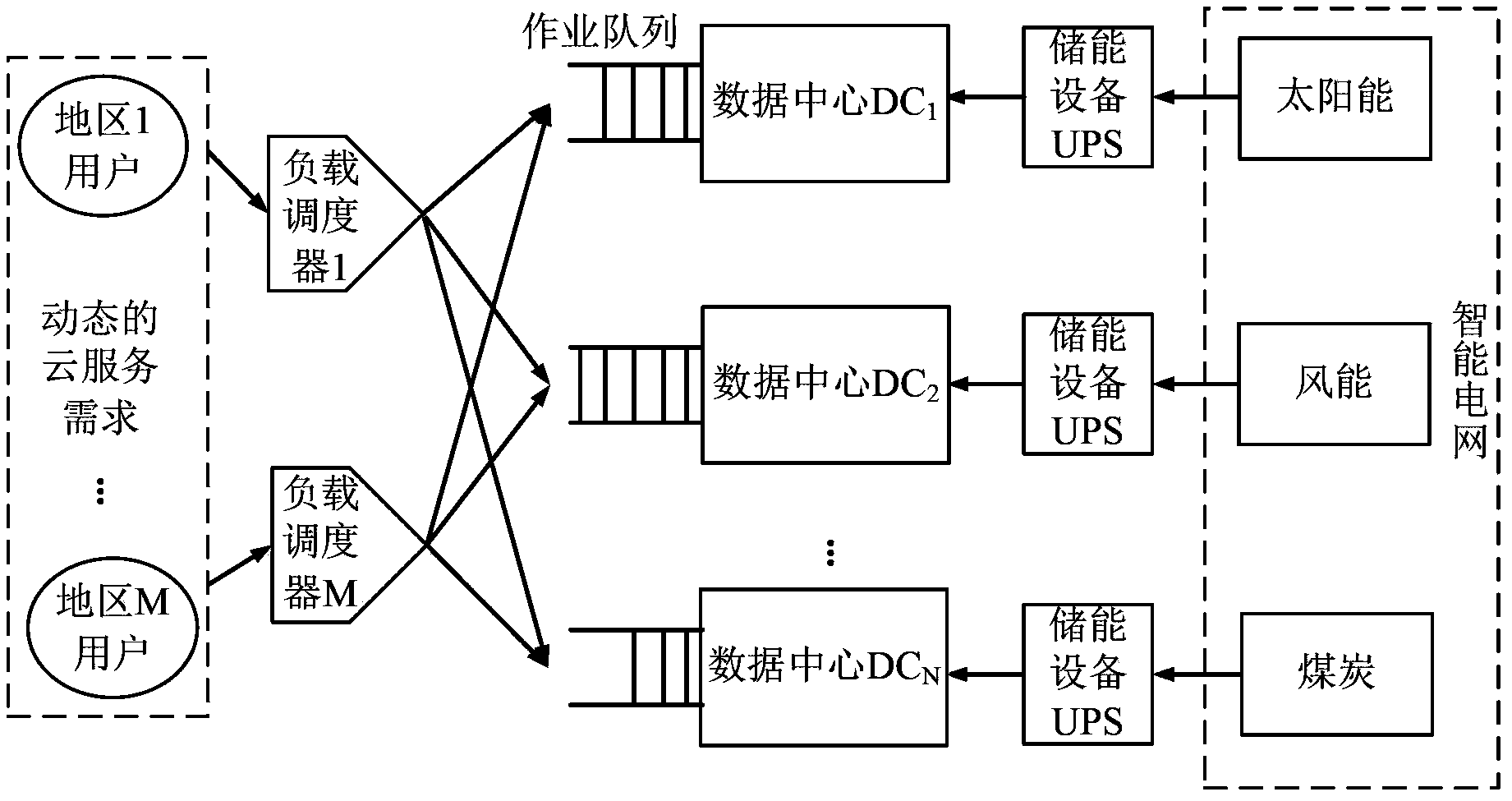

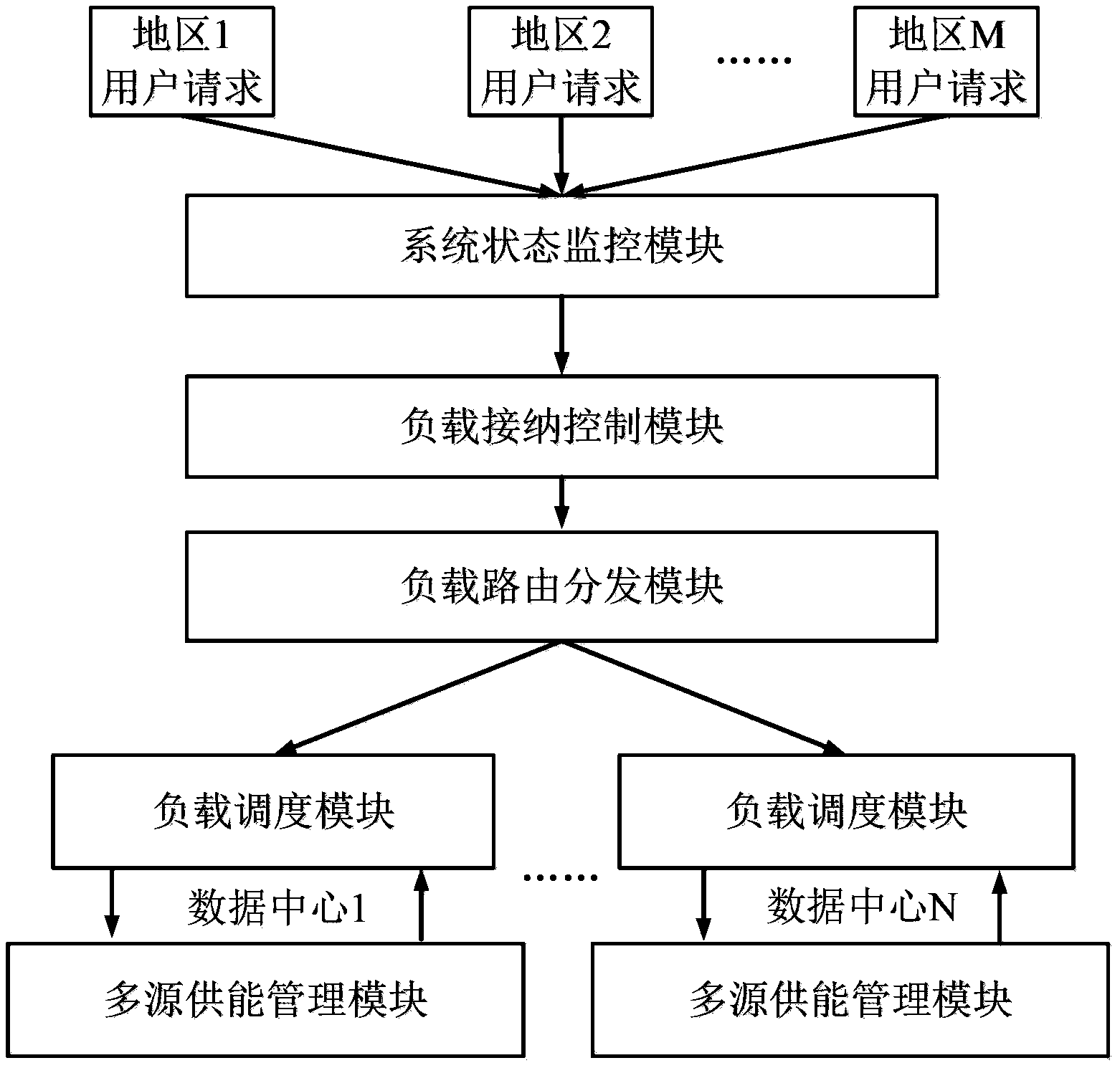

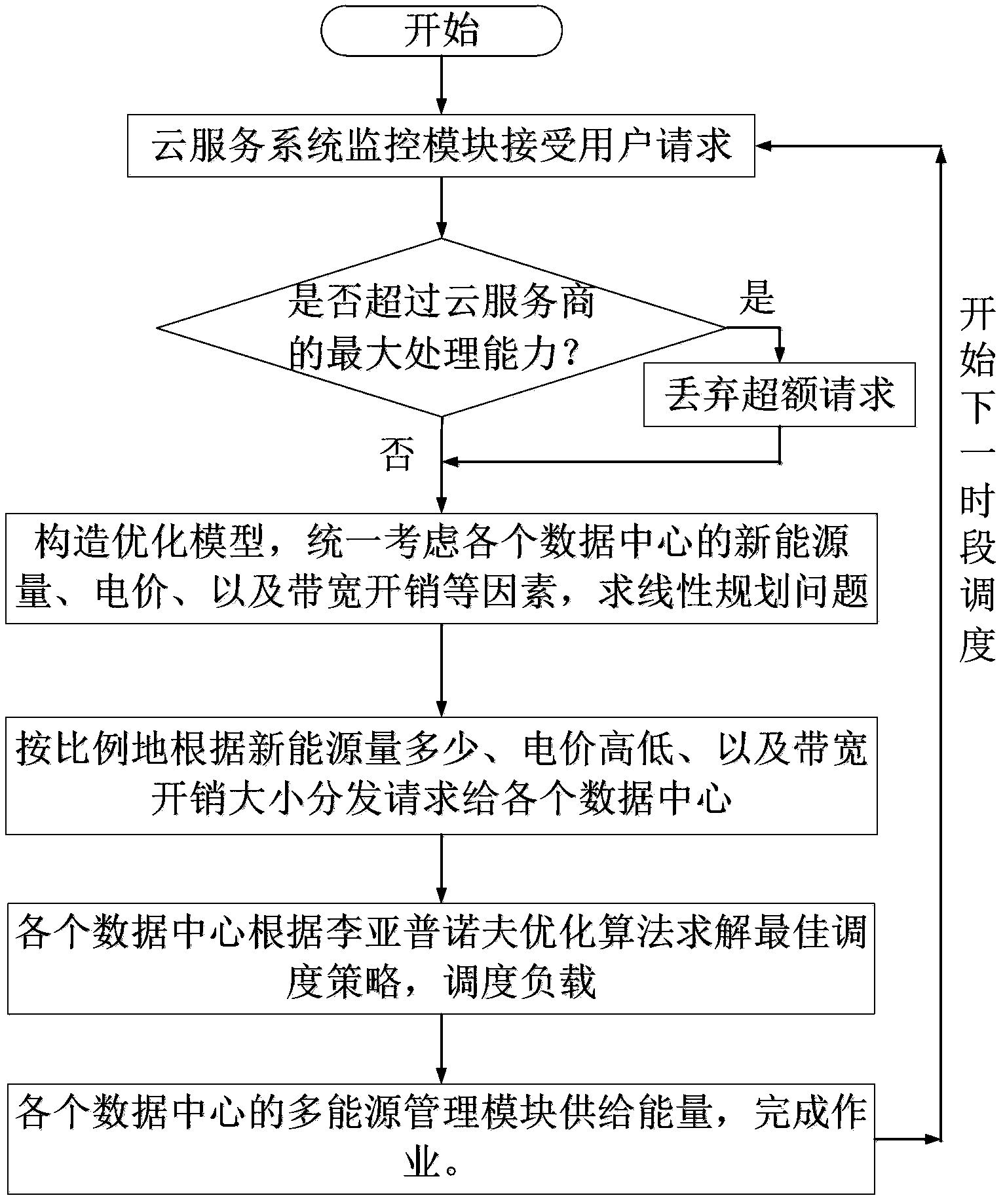

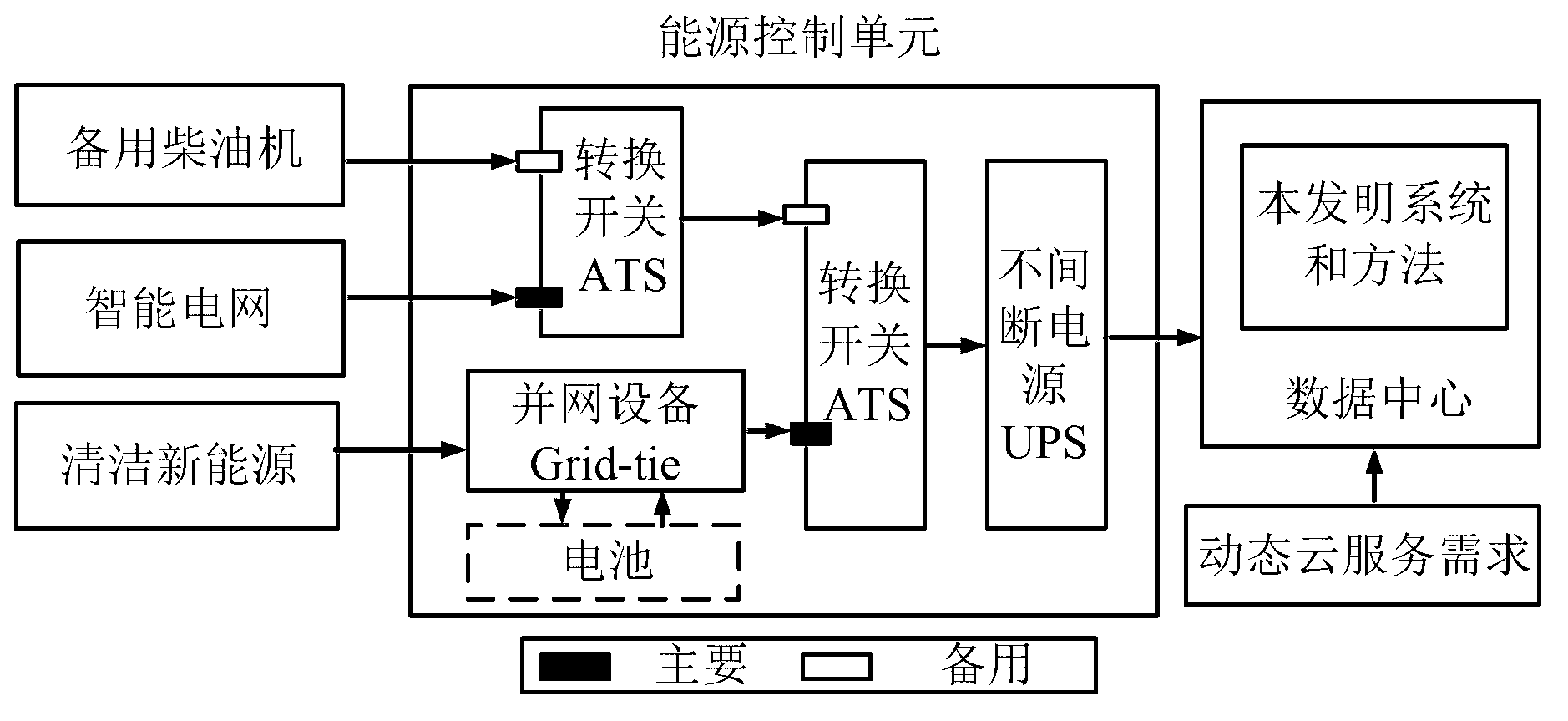

Cloud service distributed data center system and load dispatching method thereof

ActiveCN103384272AMinimize operational overheadLow electricity priceTransmissionElectricity priceNew energy

The invention discloses a cloud service distributed data center system which comprises a system state monitoring module, a load admission control module, a load routing distribution module, a load dispatching module and a multi-source energy supply management module. The system state monitoring module is used for acquiring cloud service requests from different users, recording the cloud service requests and information related to the cloud service requests and transmitting the cloud service requests to the load admission control module, the load admission control module is used for selecting parts of the cloud service requests according to the number of the received cloud service requests and transmitting the cloud service requests to the load routing distribution module, and the load routing distribution module is used for distributing the received cloud service requests to corresponding data centers for processing. The cloud service distributed data center system can solve the problems that a data center energy supply system in an existing system is high in long-term operating expenditure and unstable in new energy supply, electricity price fluctuates, and system data or stable distribution needs to be acquired in advance.

Owner:HUAZHONG UNIV OF SCI & TECH

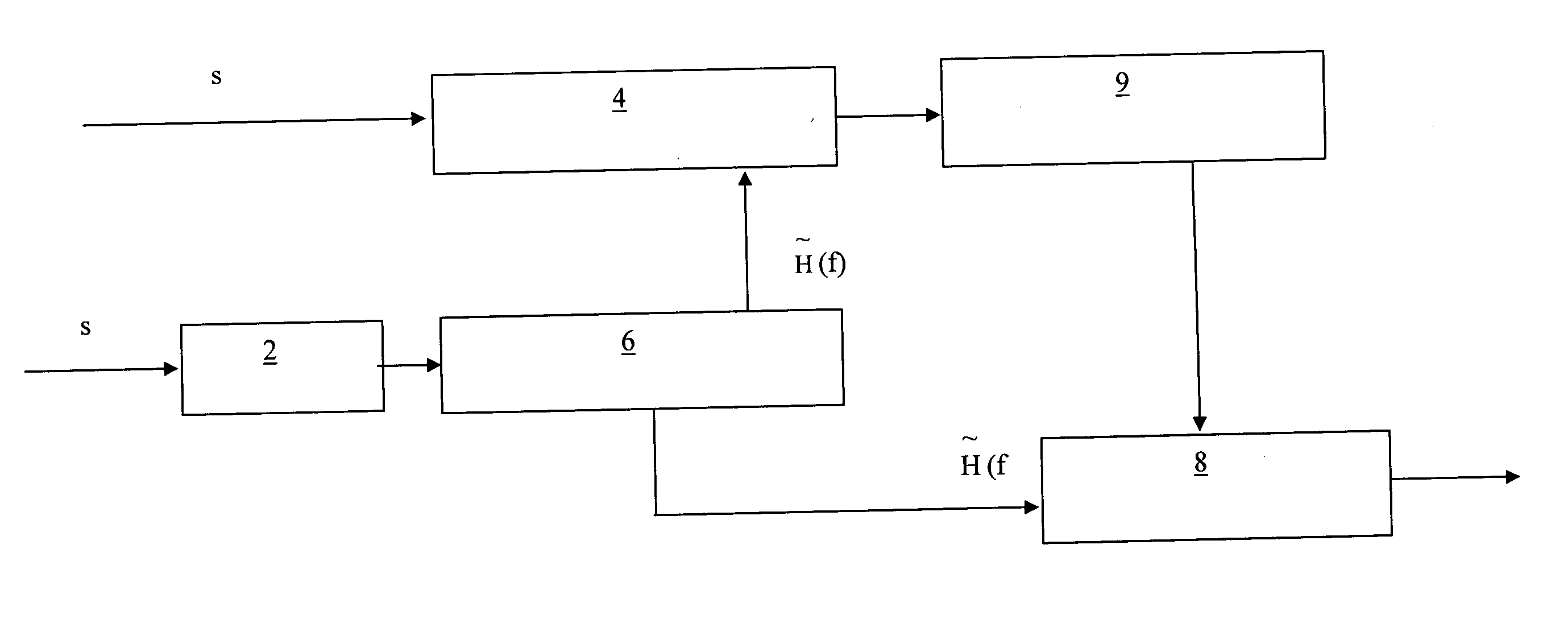

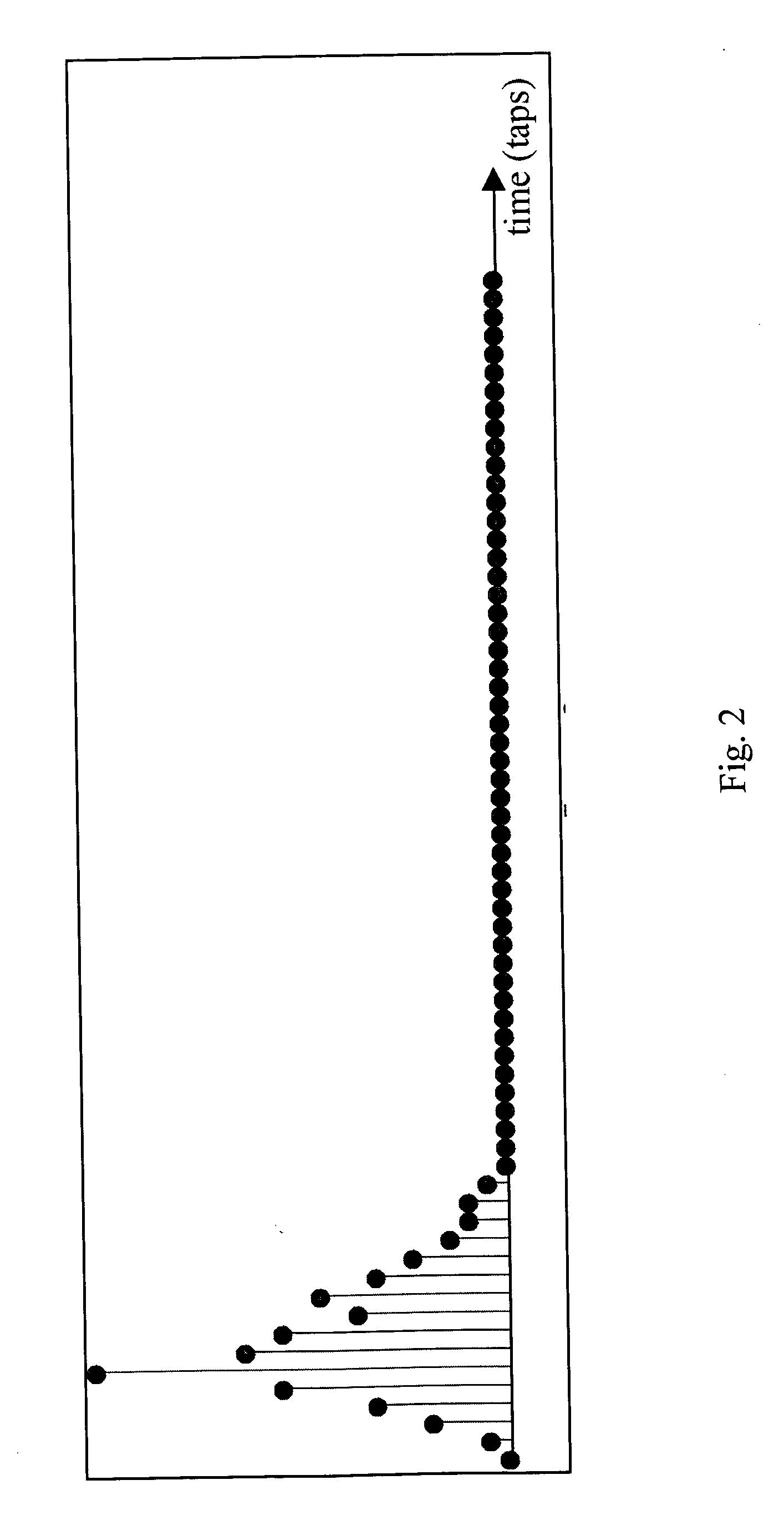

Method and apparatus for improving the quality of channel estimation algorithms using training sequences

InactiveUS20050111538A1Robust againstSignal to noise ratioMultiple-port networksDelay line applicationsSignal-to-noise ratio (imaging)Engineering

An aspect of the present invention is the use of two criteria in channel estimation, e.g. a value related to the length of an estimated Channel Impulse Response (CIR) and a value related to a noise content of the received signal, e.g. a Signal-to-Noise Ratio (SNR). These parameters can be used for the post-processing algorithm. An advantage of the present invention is that it is much more robust against long channels and / or high noise contents in received signals. Additionally it has moderate implementation complexity.

Owner:STMICROELECTRONICS BELGIUM

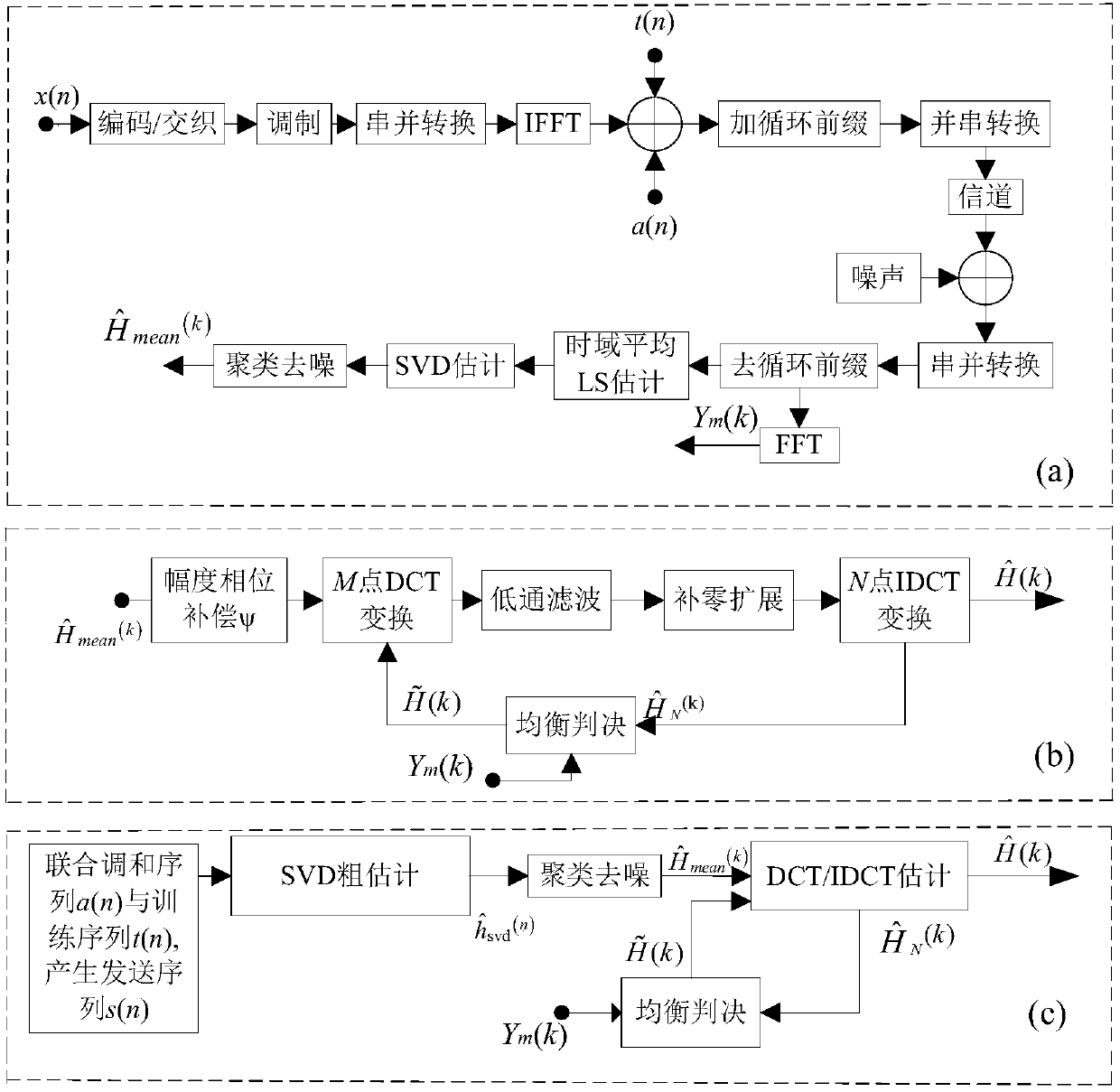

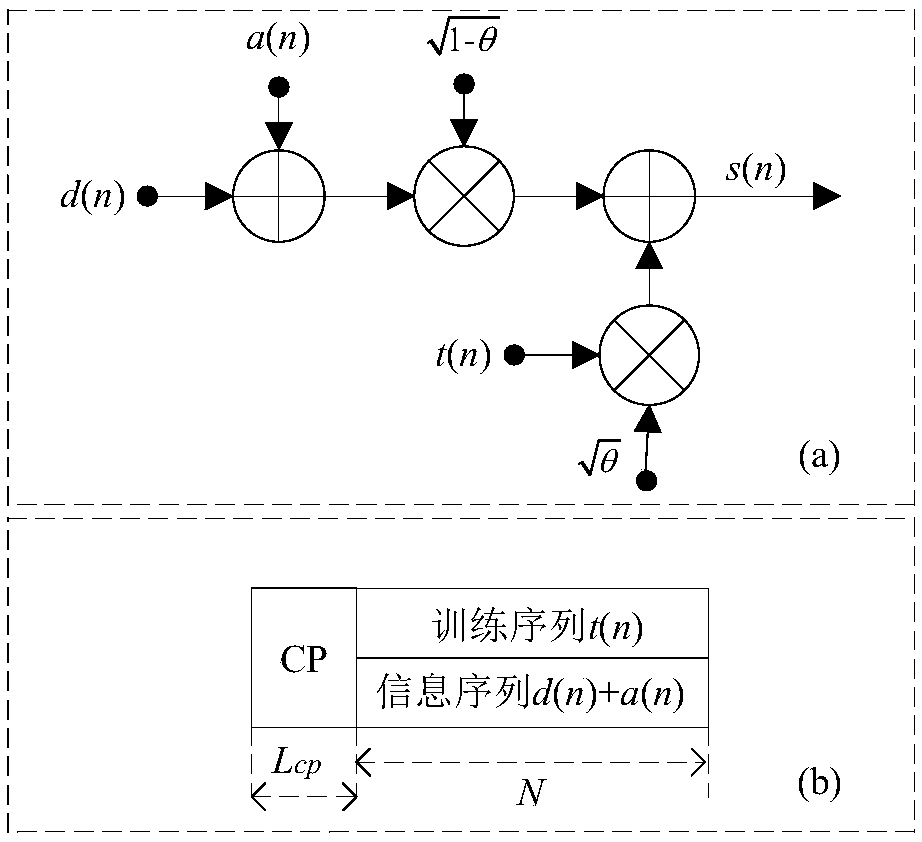

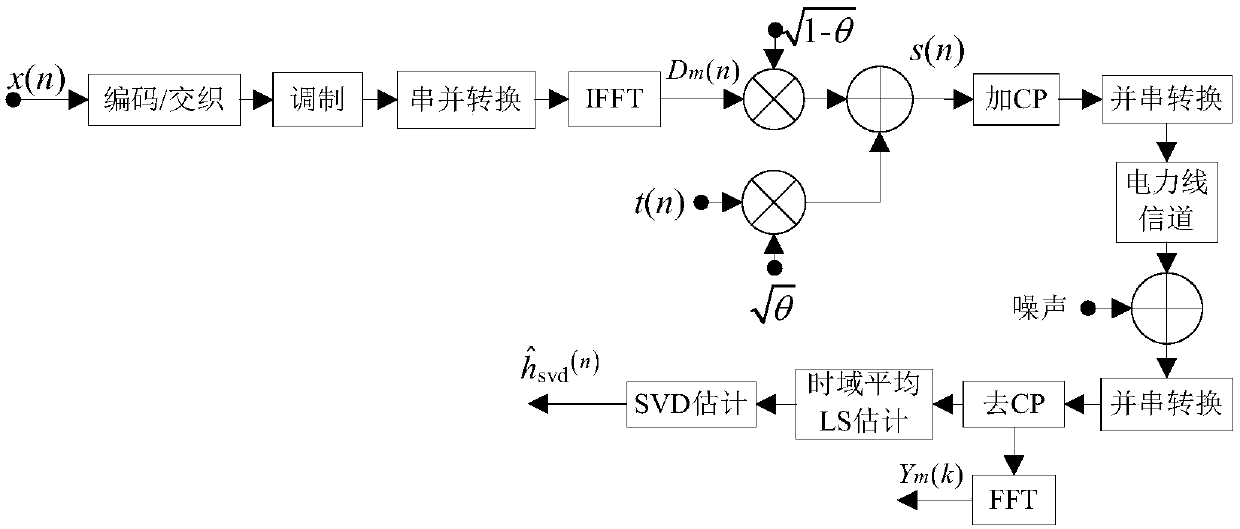

Transform domain quadratic estimation method based on combination of time domain clustering denoising with equalization decision making

ActiveCN108833311AEliminate noise interferenceModerate complexityChannel estimationTransmitter/receiver shaping networksTime domainChannel impulse response

The invention discloses a transform domain quadratic estimation method based on combination of time domain clustering denoising with equalization decision making. A harmonic sequence is designed at atransmitting terminal and weighted overlapping is carried out on the designed sequence and a training sequence to generate a transmitting sequence; with an SVD channel estimation method of the existing overlapped training sequence, rough estimation of a channel frequency domain response is obtained; a threshold is set and channel impulse responses are classified into an initial signal class training sample and a noise class training sample, and time domain clustering denoising processing is completed; and transform domain quadratic estimation is carried out on the denoised frequency domain response by using windowed DCT / IDCT interpolation, wherein an equalization decision making method is introduced into the quadratic estimation process. According to the transform domain quadratic estimation method disclosed by the invention, the influences on channel estimation performance by a data sequence and a training sequence are eliminated and the existing SVD channel estimation performance isimproved; noises can be eliminated effectively; and implementation complexity is low. The transform domain quadratic estimation method can be applied in multi-carrier communication well.

Owner:HANGZHOU DIANZI UNIV

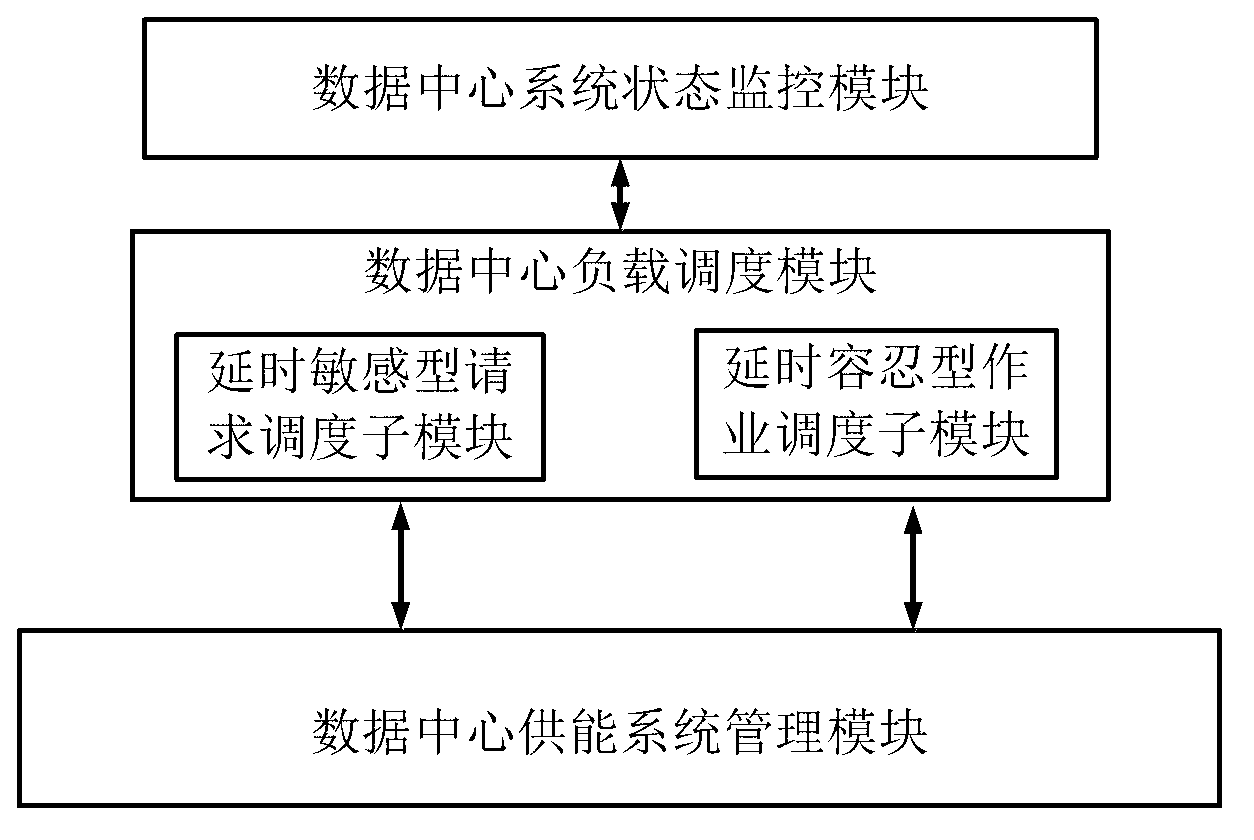

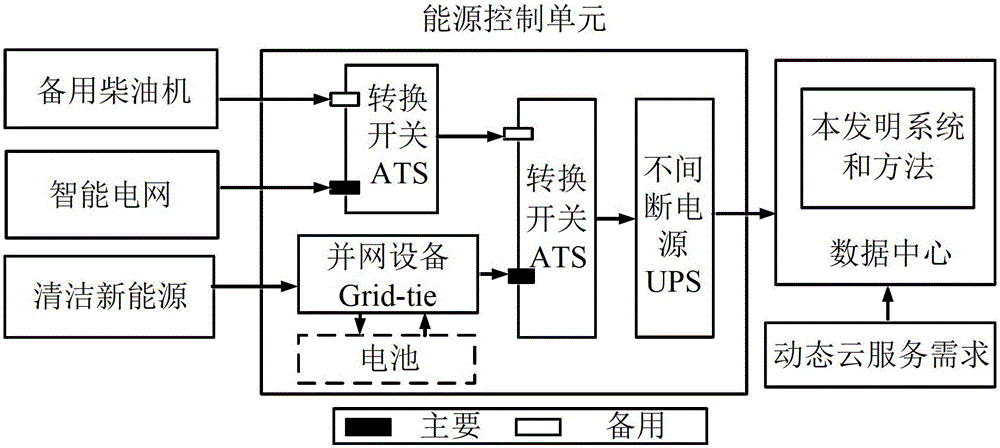

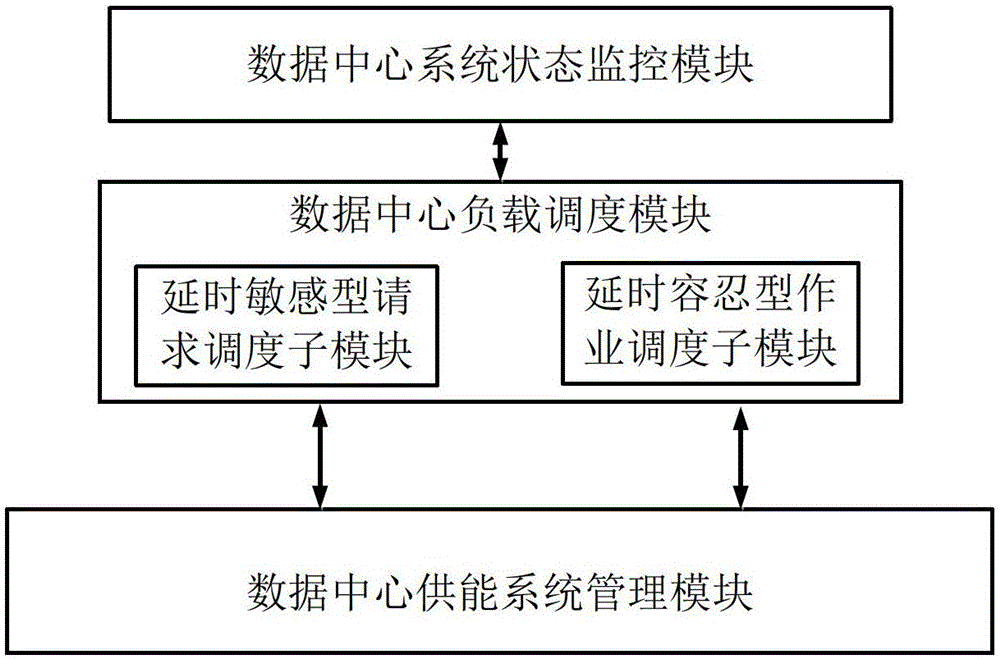

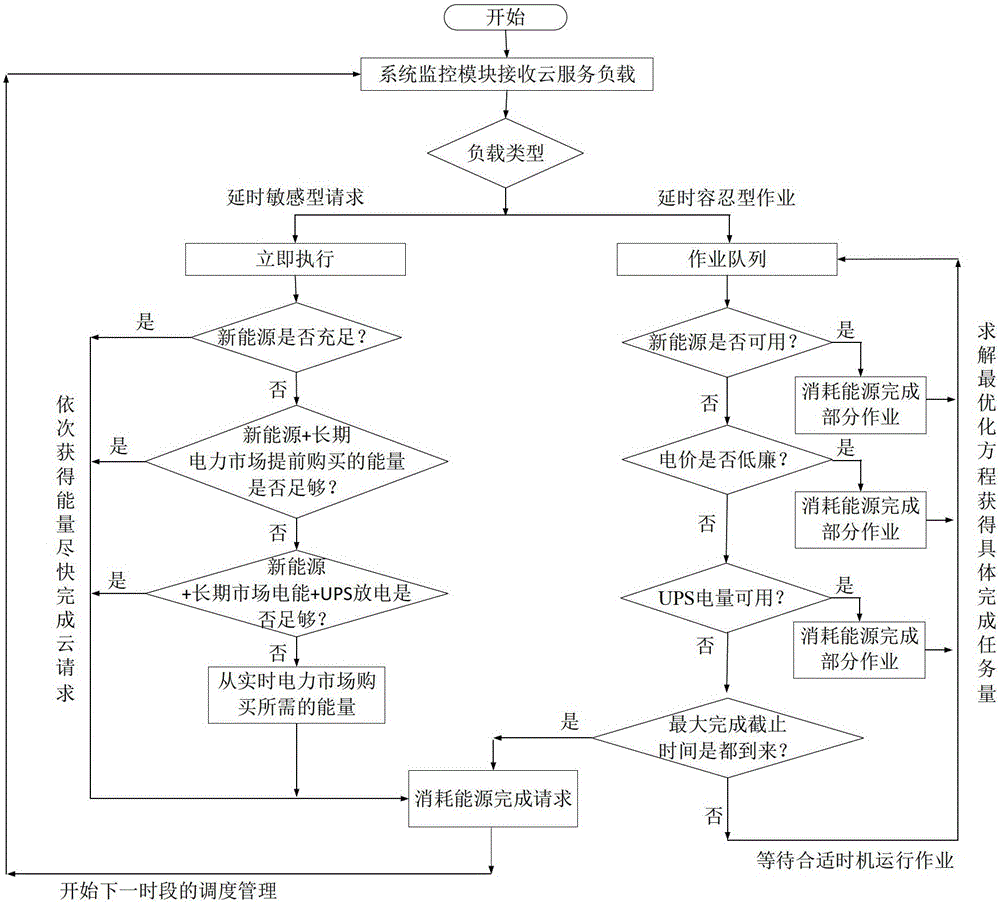

Multi-energy online control method and system for data center under dynamic cloud service request

ActiveCN103297505AMinimize operational overheadLow electricity priceTransmissionControl systemSystems management

The invention discloses a multi-energy online control system for data centers under dynamic cloud service requests. The multi-energy online control system for data centers under dynamic cloud service requests comprises a system status monitoring module, a load scheduling module and a multi-source energy supply system management module, wherein the load scheduling module comprises a delay-sensitive request scheduling sub-module and a delay tolerant job scheduling sub-module. The system status monitoring module is used for receiving service requests from a user's cloud service every once in a while, determining whether the cloud service request is a delay-sensitive request or a delay tolerant job, and sending the cloud service request belonging to the delay-sensitive request to the delay-sensitive request scheduling sub-module of the load scheduling module while sending the cloud service request belonging to the delay tolerant job to the delay tolerant job scheduling sub-module of the load scheduling module. The multi-energy online control system for data centers under dynamic cloud service requests has the advantages that long-term operating cost of data center energy supply system can be optimized, no system data is needed to be obtained in advance, and no steady state distribution is needed to be assumed.

Owner:HUAZHONG UNIV OF SCI & TECH

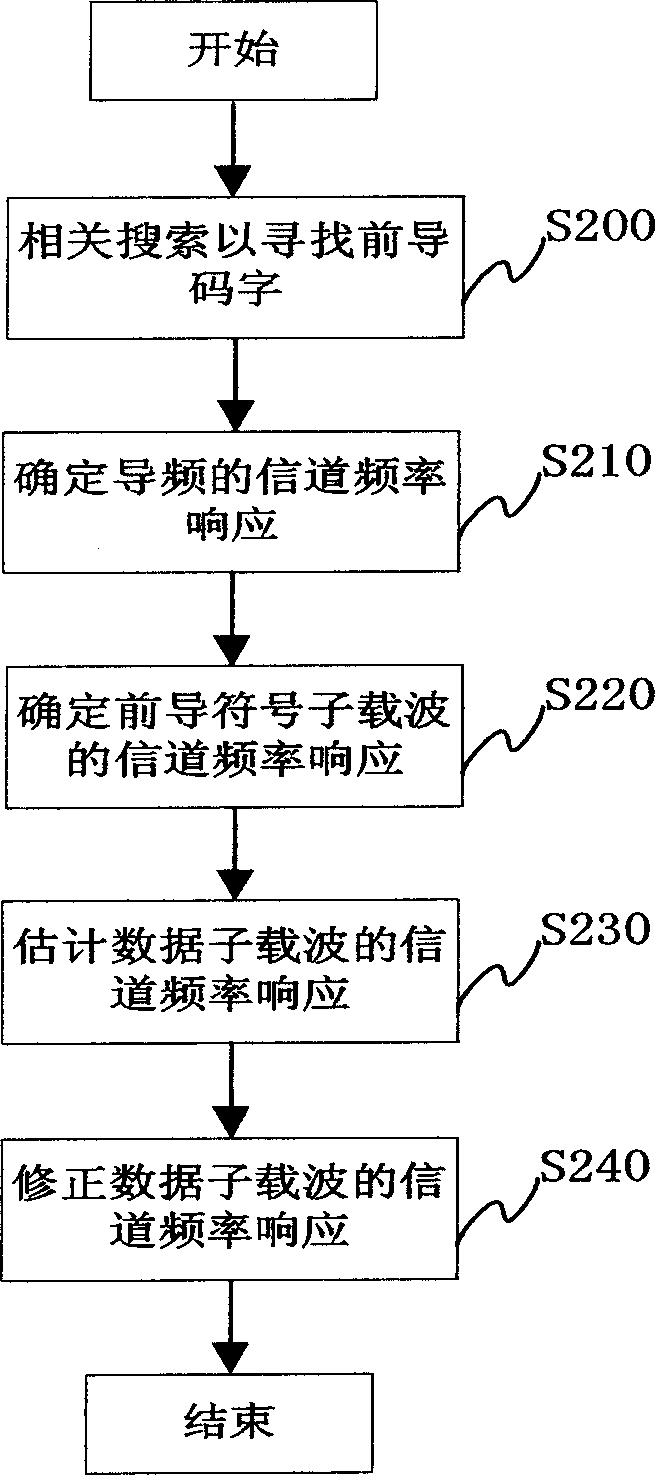

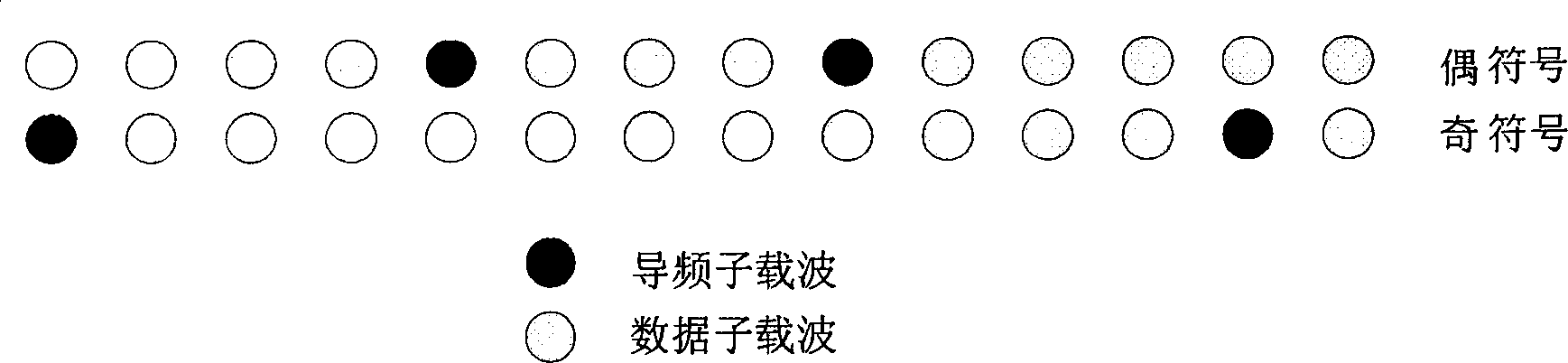

Channel estimation method and device for crossing frequency division multiplexing system

InactiveCN1909528AImprove accuracyOvercome the disadvantage of large interpolation errorBaseband system detailsMulti-frequency code systemsCarrier signalEngineering

The invention relates to a signal channel estimate method used in orthogonal frequency division multiplexing system, a relative device, and an orthogonal frequency division multiplexing system using said device, wherein said signal channel estimate method comprises: fixing the signal channel frequency response of sub carrier wave of at least one forward mark and the signal channel frequency response of several pilots of one data mark in one orthogonal frequency division multiplexing frame; based on said the nearby pilot of data mark, estimating the signal channel frequency response of data sub carrier wave; using said signal frequency response to correct the signal channel frequency response of said data sub carrier wave; compared with present technique, the invention can avoid noise effect and high interpolation error, to improve the system property, with low complexity.

Owner:UTSTARCOM TELECOM CO LTD

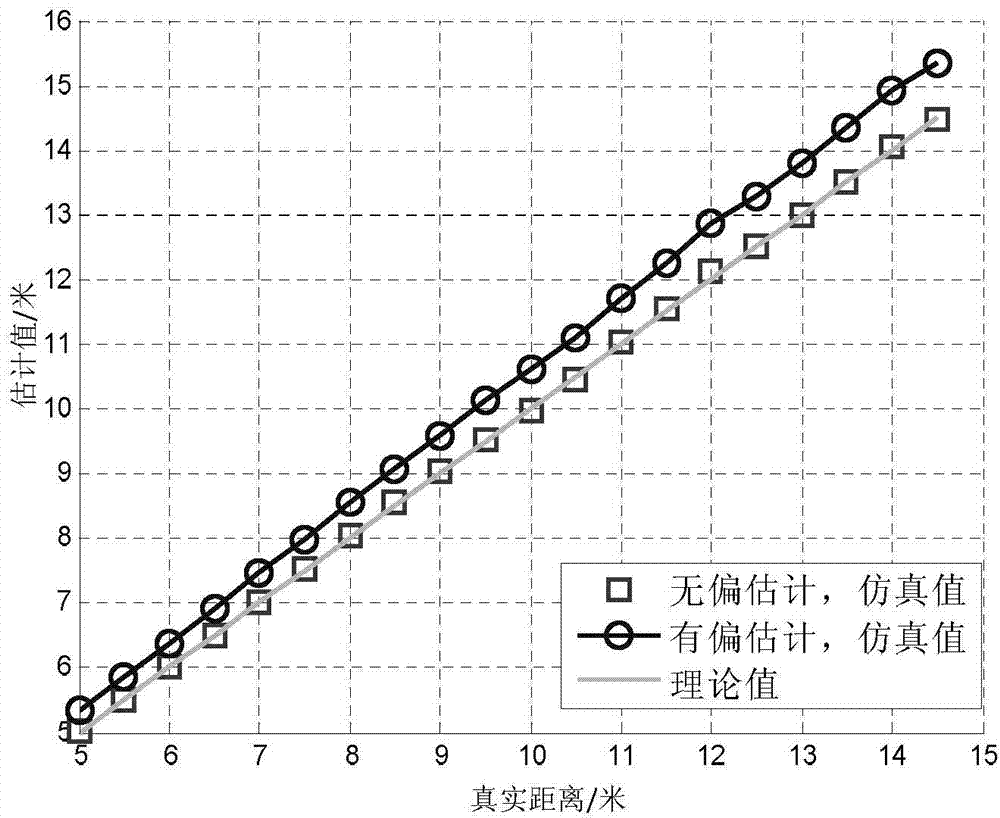

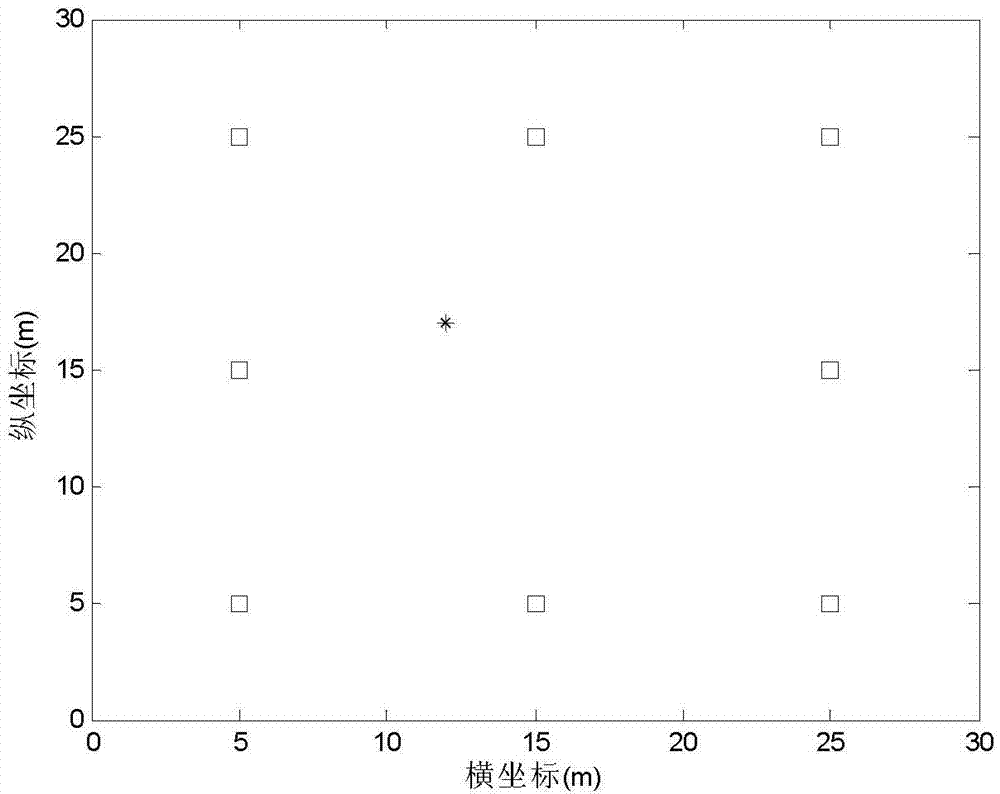

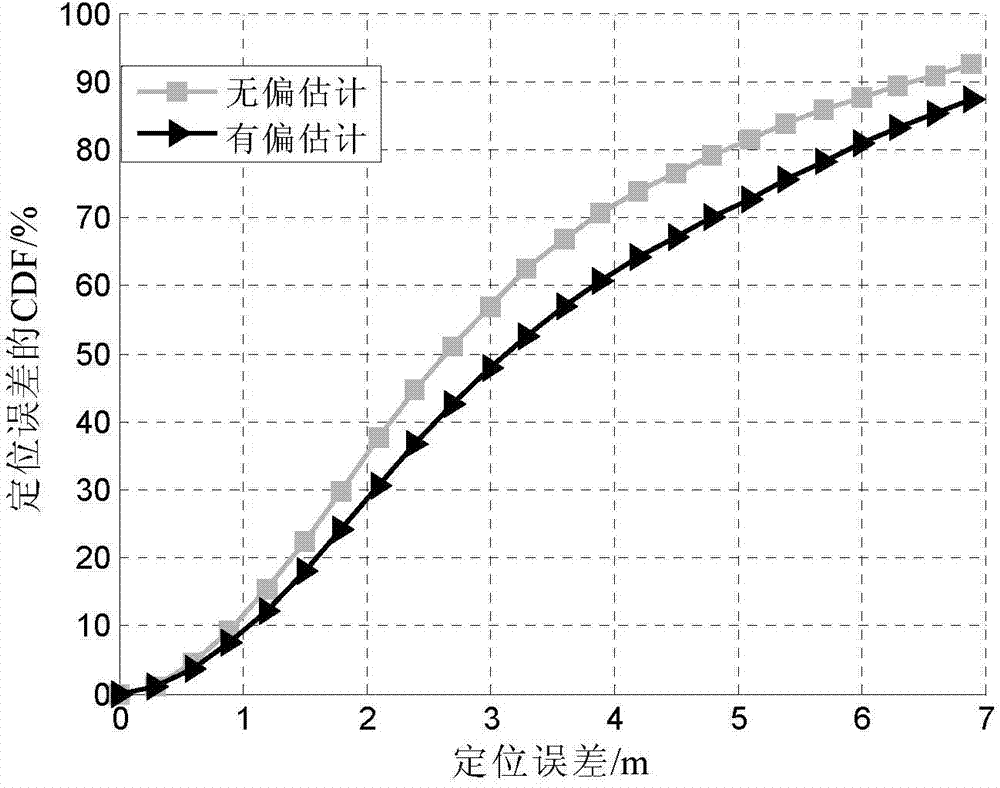

WSN (wireless sensor network) node positioning method based on RSS (Received Signal Strength) and distance measurement unbiased estimation

InactiveCN104507164AHigh precisionModerate complexityWireless communicationWireless mesh networkComputer science

The invention relates to a node positioning method, in particular to a WSN (wireless sensor network) node positioning method based on RSS (Received Signal Strength) and distance measurement unbiased estimation. The WSN node positioning method based on the RSS and the distance measurement unbiased estimation solves the problems that a WSN node positioning algorithm based on RSS distance measurement is influenced by noise, and thereby can not fully analyze distance measurement error, and furthermore can not essentially eliminate distance measurement deviation caused by the noise. The WSN node positioning method based on the RSS and the distance measurement unbiased estimation includes steps: 1, setting an unknown node U=(x, y), and setting a coordinate of a signal from a beacon node Bi as (xi, yi); 2, calculating the distance vi between the unknown node and the beacon node Bi; 3, obtaining unbiased estimator; 4, calculating the distance between the unknown node U and the beacon node Bi; 5, using a Newton iteration method to solve the position (x, y) of the unknown node U; 6, obtaining delta X7, and obtaining positioned positions xk and yk of the unknown node and the like. The WSN node positioning method based on the RSS and the distance measurement unbiased estimation is used in the node positioning field.

Owner:HARBIN INST OF TECH

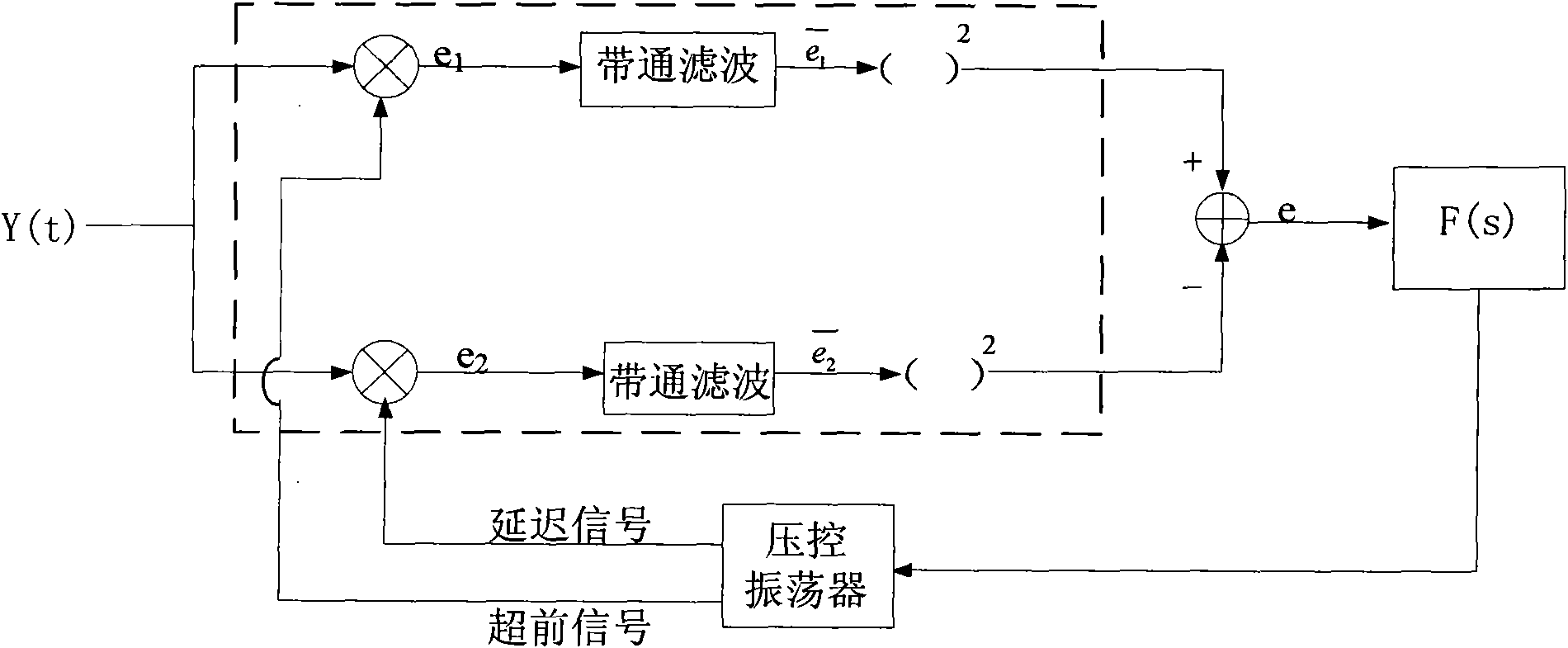

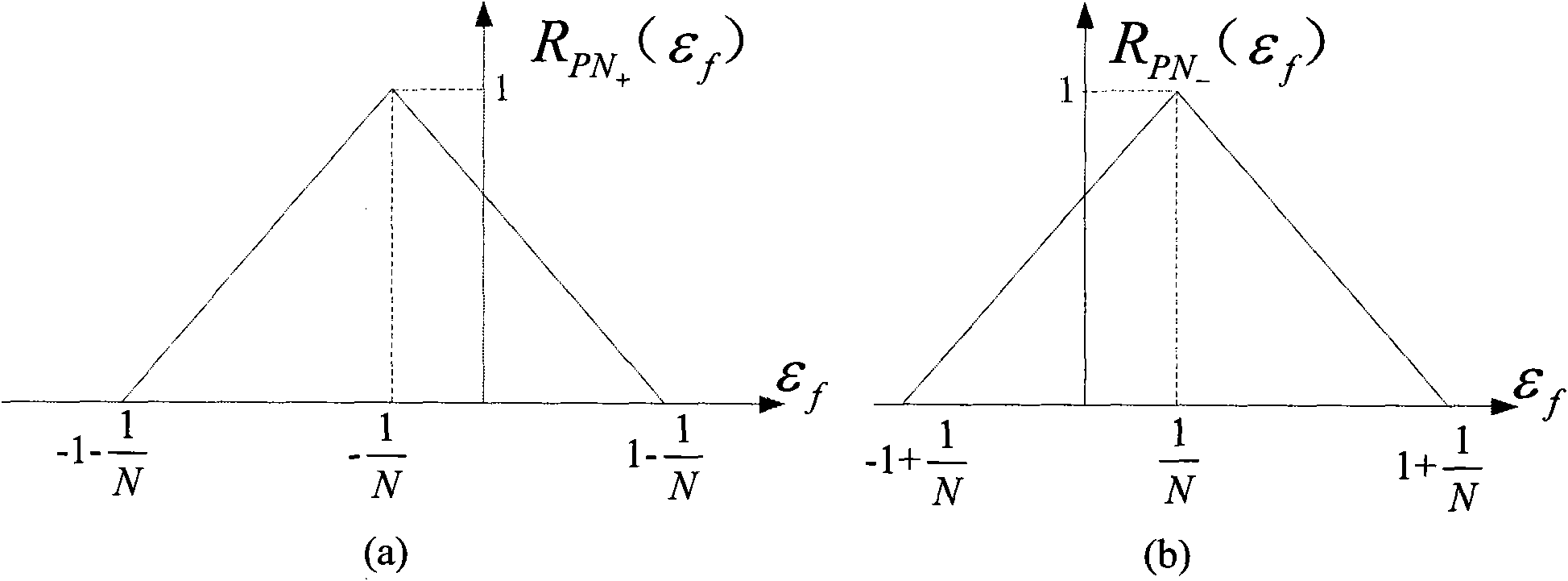

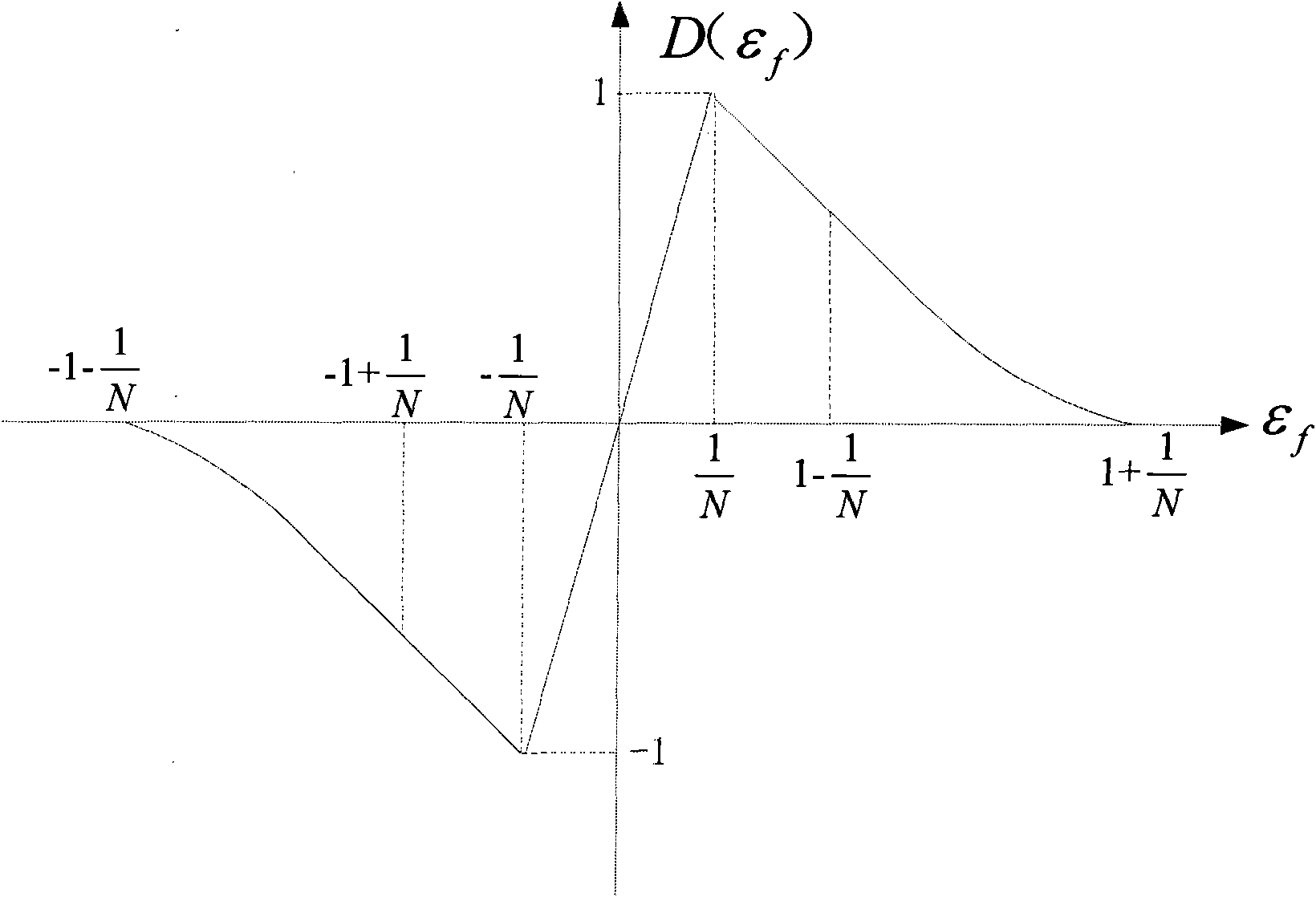

Method for detecting frequency errors of sampling clock, device and system thereof

InactiveCN101686477AModerate complexityTransmission monitoringWireless communicationDiscriminatorChannel impulse response

The embodiment of the invention discloses a method for detecting frequency errors of a sampling clock, a frequency discriminator thereof. The method comprises the following steps: respectively calculating and obtaining partial channel impulse responses on pseudo random sequences of two periods according to the received pseudo random sequences; correlating the two partial channel impulse responsesto acquire related waveforms; and performing lead-lag sampling time estimation on the related waveforms, and detecting errors of frequency of the sampling clock according to output results of the sampling time estimation. The frequency discriminator comprises a calculation module, a relation module and a detection module. Correspondingly, the embodiment of the invention also discloses a method anda system for synchronizing the sampling time; and impacts of small delay multipath can be mutually counteracted by constructing the channel impulse responses symmetric about a main path on the periphery of the main path so as to obtain the sampling clock without frequency errors, and achieve synchronization of the sampling time. The method has moderate complexity.

Owner:HUAWEI TECH CO LTD

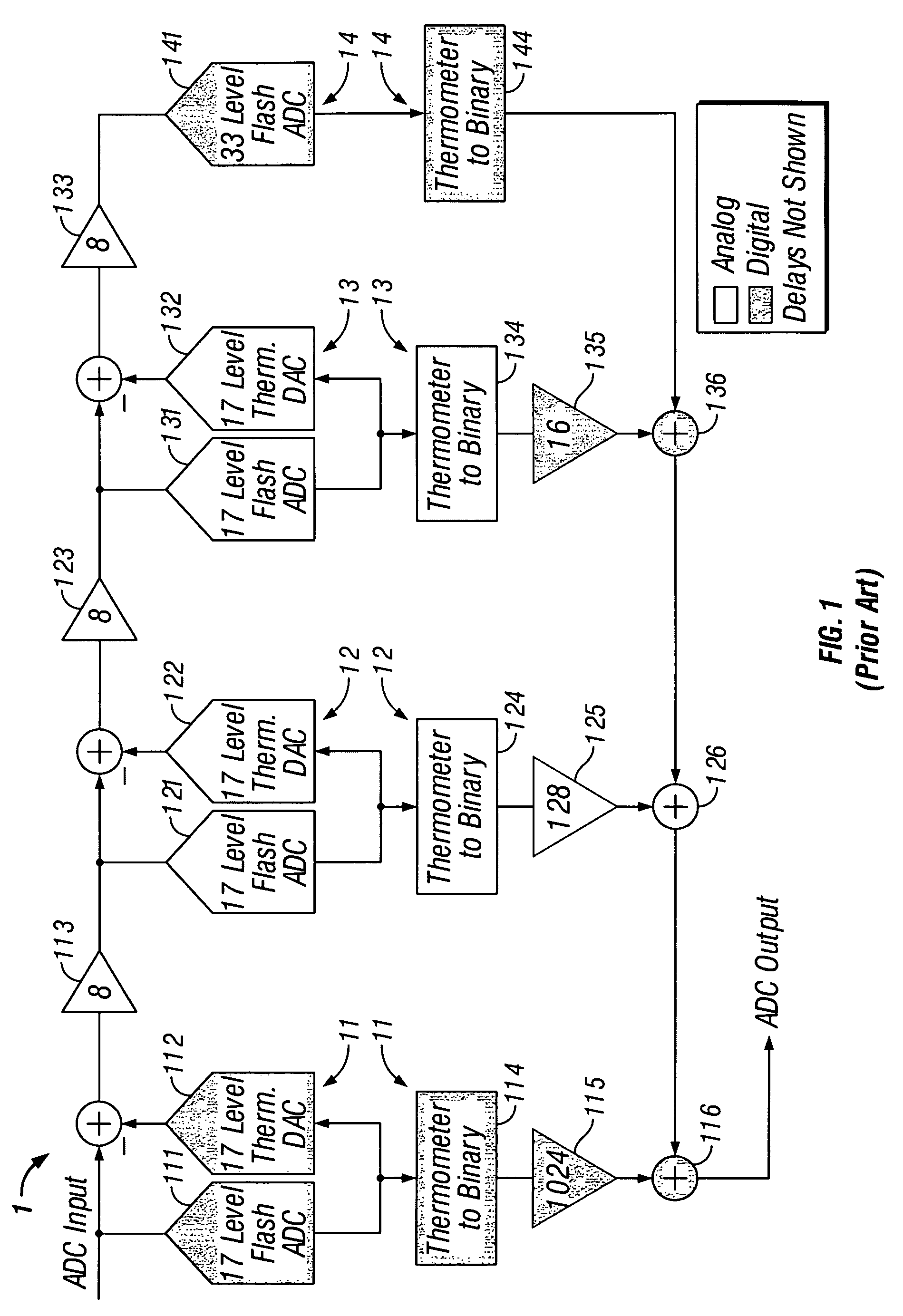

Digital background cancellation of digital to analog converter mismatch noise in analog to digital converters

InactiveUS20050156773A1Mitigate problemReduce decreaseElectric signal transmission systemsAnalogue-digital convertersFlash memoryA d converter

An improvement to a conventional multistage pipelined Analog-to-Digital Converter (ADC) 1 having multiple stages 11-14, connected one to the next by an interstage amplifier 113, 123, 133, each stage with a flash digital-to-analog converter (DAC) 111, 121, 131, a digital-to-analog converter (DAC) 112, 122, 132 producing an associated intermediate analog signal, a subtractor 113, 123, 133 of intermediate analog signals to produce an analog difference signal fed to the interstage amplifier of a next following stage, and a thermometer encoder 114, 124, 134 producing an associated digital output signal; the improvement directed to canceling noise resultant from component mismatch, particularly mismatched capacitors paired with a first-stage DAC 212 of the ADC 1. The improved ADC 2 uses in at least a first, and preferably two, stages 21, 22: (i) a flash DAC 212, 222 of a dynamic element matching (DEM) type producing, as well as an associated intermediate analog signal, random bits and parity bits; (ii) a Digital Noise Cancellation (DNC) logic circuit 217, 227, receiving the random bits and the parity bits and a digitized residue sum of the digital output signal's arising from all stages beyond a stage of which the DNC logic circuit 217, 227 is a part, so as to produce an error estimate for the stage; and (iii) a subtractor 218, 228 subtracting the error estimates of the DNC logic circuits 217, 227 from the combined digital output signal of all higher stages 22-24 in order to produce a corrected ADC digital output signal. A 14-bit 4-stage pipelined ADC 2 having, by way of example, a theoretical optimum conversion precision of 14.1 bits and a realistic conversion precision of 10.4 bits, is enhanced by modestly-sized and continuously-automatically-operative DNC to realize 13.3 bits conversion precision.

Owner:RGT UNIV OF CALIFORNIA

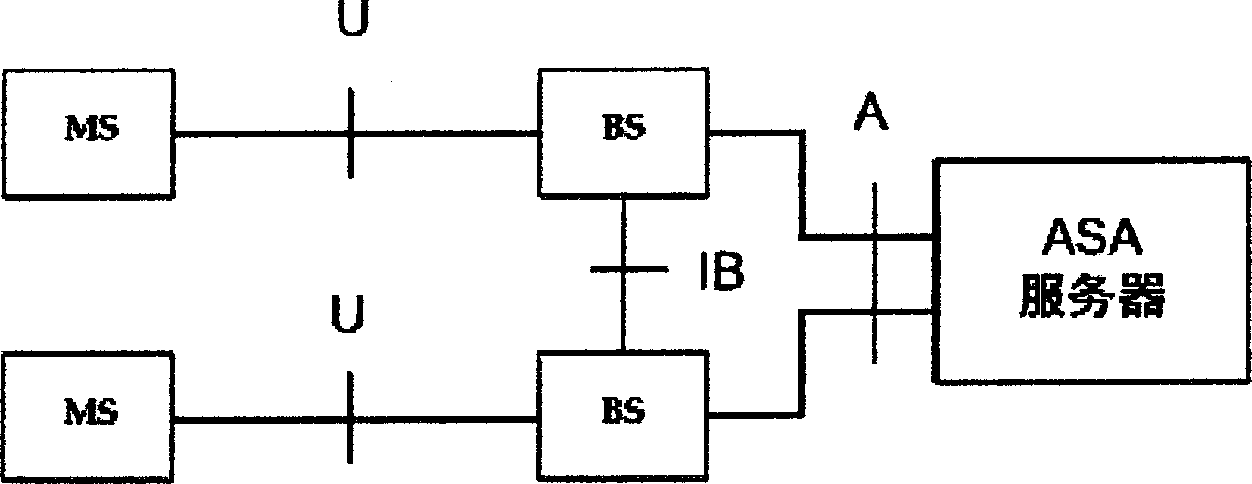

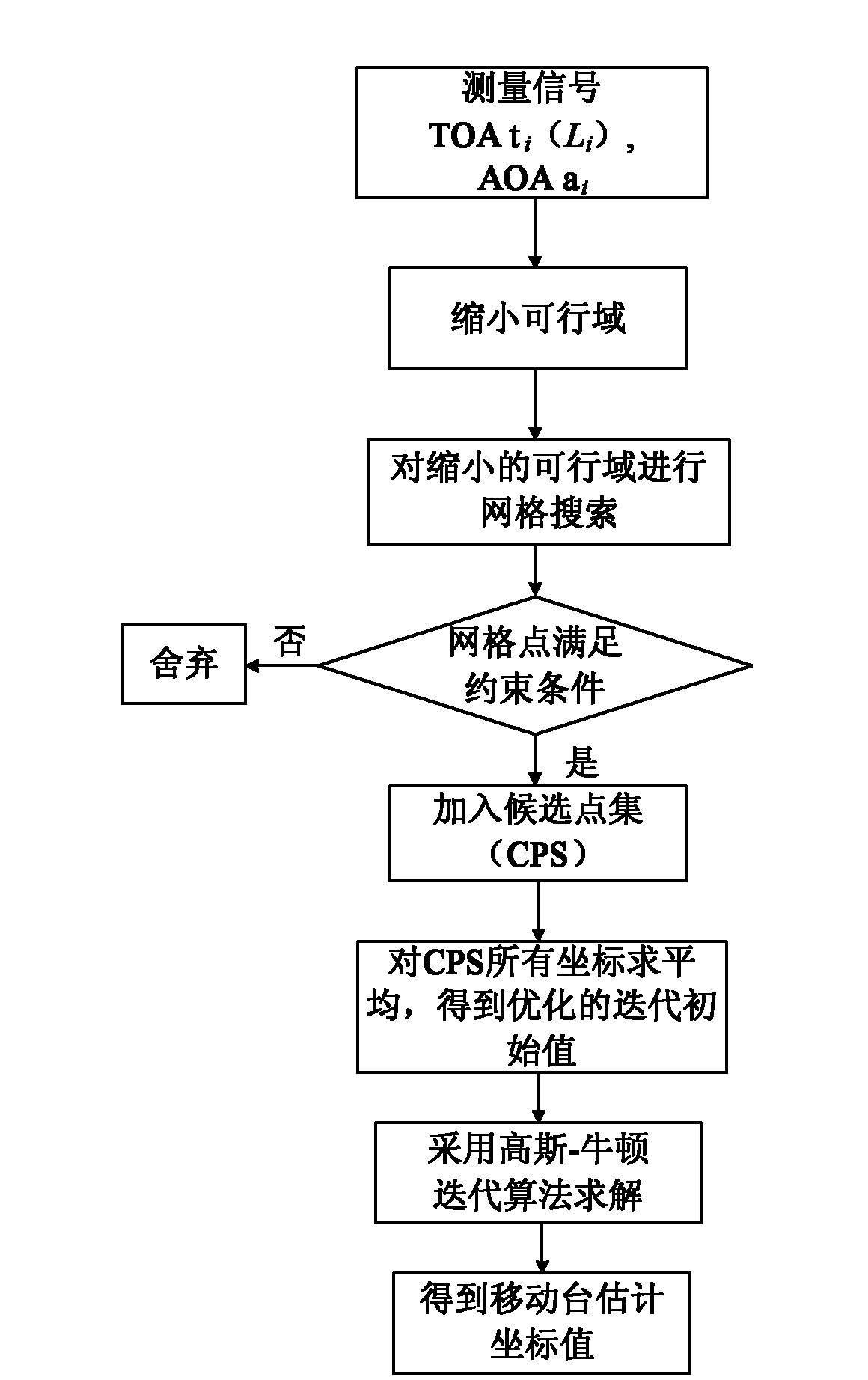

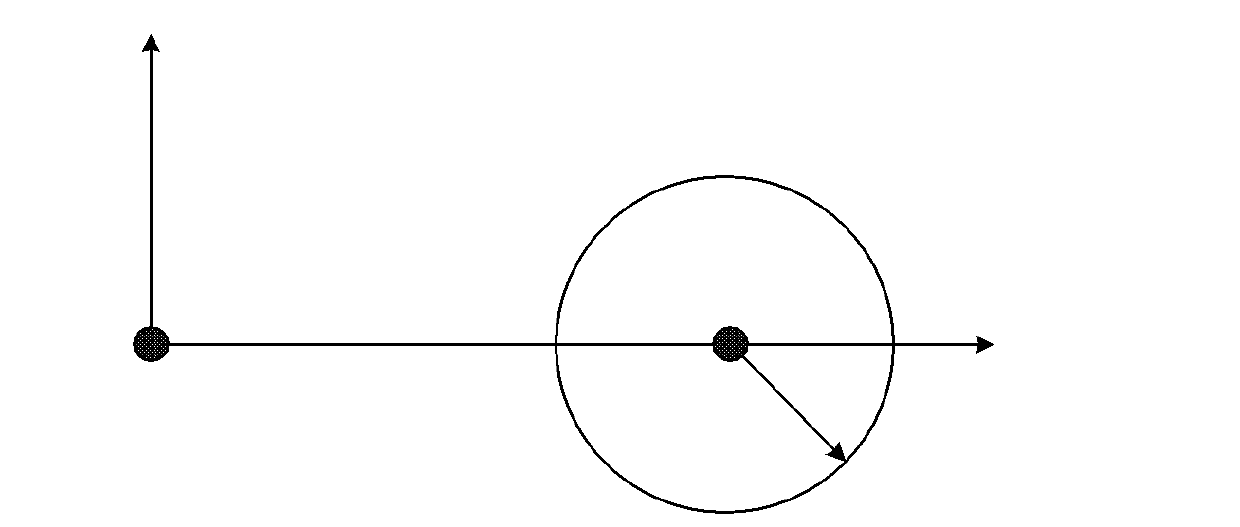

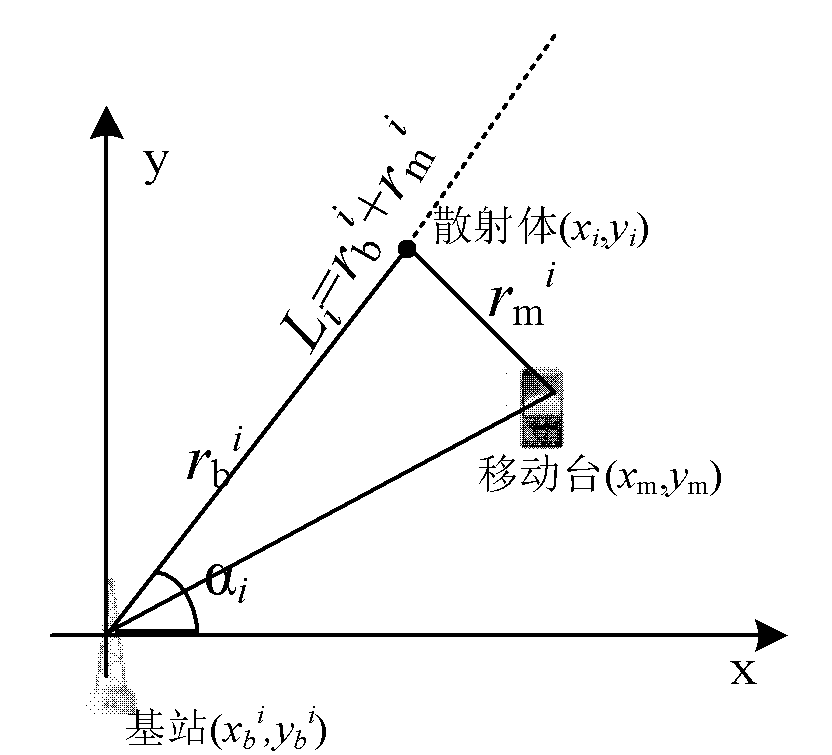

Geometric positioning improvement method under NLOS (non-line-of-sight) environment

ActiveCN102170658AOptimize initial iteration coordinate valuesHigh positioning accuracyWireless communicationAlgorithmMobile station

The invention relates to a geometric positioning improvement method under an NLOS (non-line-of-sight) environment, which adopts the Gauss-Newton iteration method with fast convergence, and combines with a grid searching method to optimize the iteration initial coordinate value. Compared with the existing geometric positioning method, the geometric positioning improvement method has the advantages that the complexity is moderated, the fast and stable convergence is provided, and the higher mobile station positioning accuracy can be obtained.

Owner:BEIJING JIAOTONG UNIV

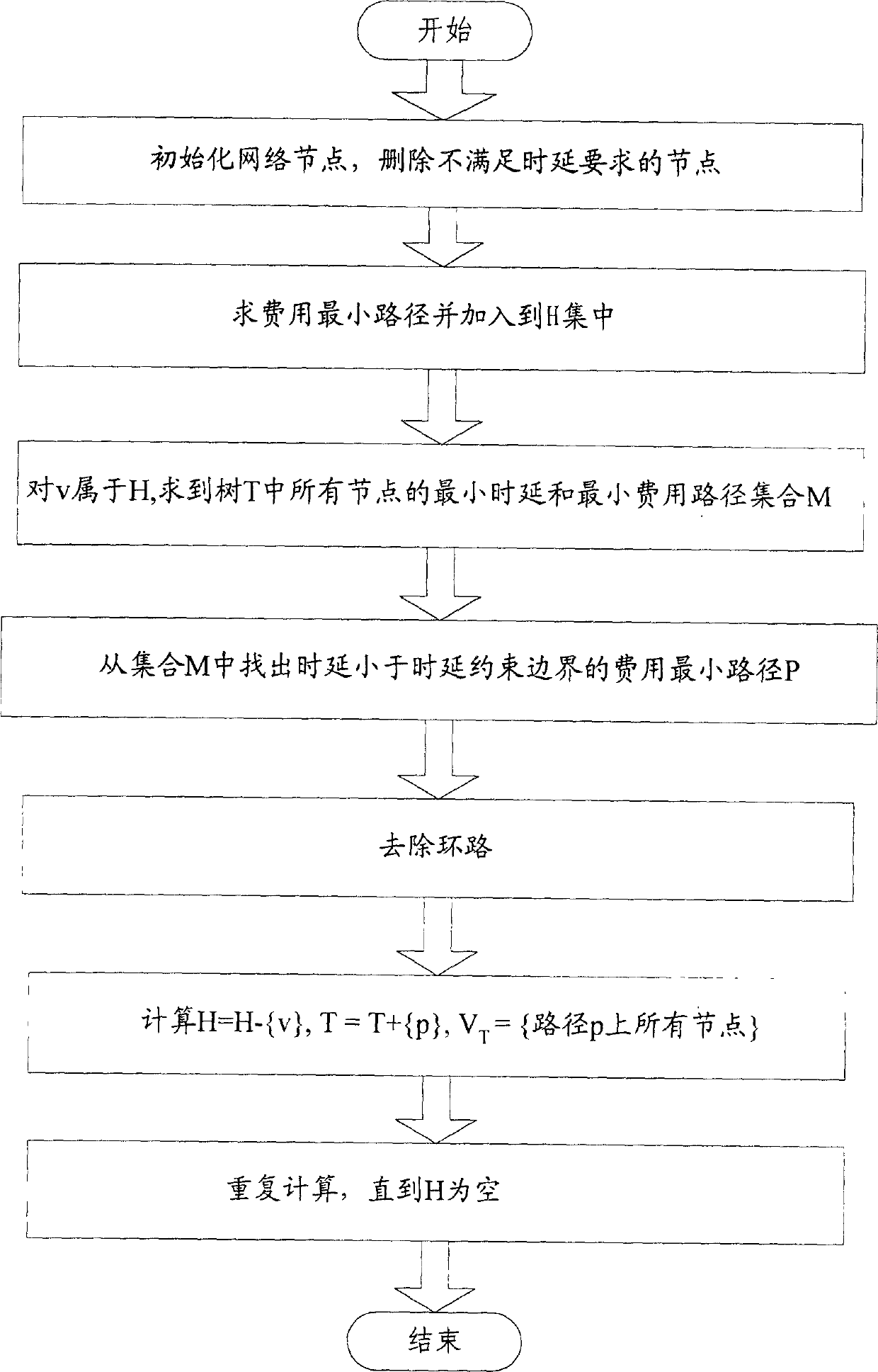

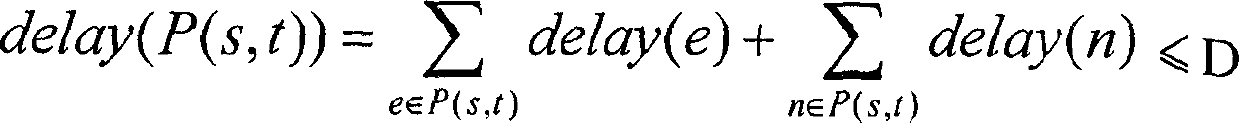

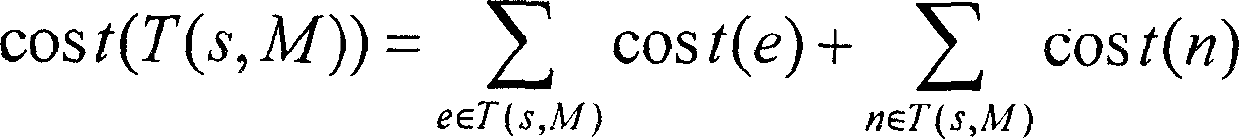

QoS restricting multicast routing method based on Steiner

This invention provides a multi-case route method based on Steiner Qos confine, actualized on NS2 flat, including 1 Single case and multi-case routes, adopting time lag restraining method to construct sharing multi-case tree, details shows as followings: a, basing on delay(P(s,t))ú¢Sigmadelay(e)ú½Sigmadelay(n) <=D to attain the least time delay route tree, if the delay agrees with constraint condition, Negotiating constraint boundary with aim node; b, basing on cost(T(sM))ú¢Sigmacost(e)ú½Sigmacost(n) to attain expense least route free, deleting the nodes disagreeing with request, adding the agreeing one into set H; c, figuring out the set M of least delay route and least expense route in tree T; d, finding out least expense route P with its delay less than constraint boundary; e, deleting wrong route; f, calculating H=H-{v}ú¼Tú¢T+{p}ú¼VTú¢{all nodes in route P}; g, repeating step c, till H=Phi, Phi being vacuous.

Owner:WUHAN UNIV OF TECH

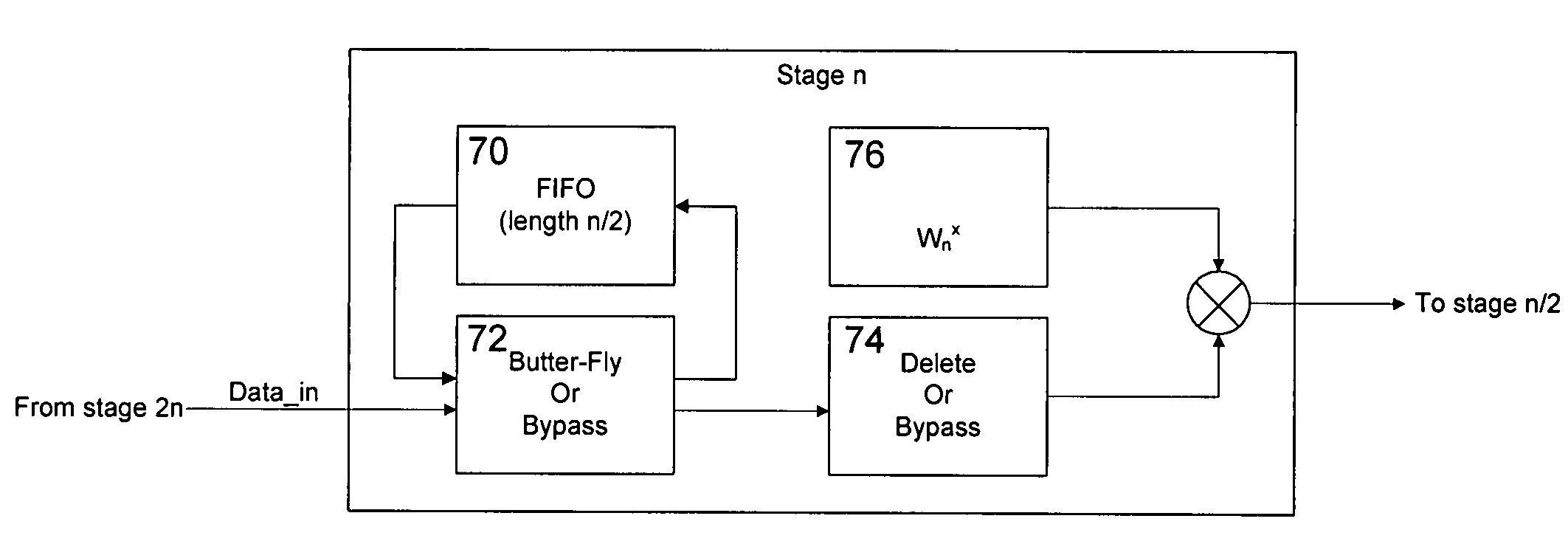

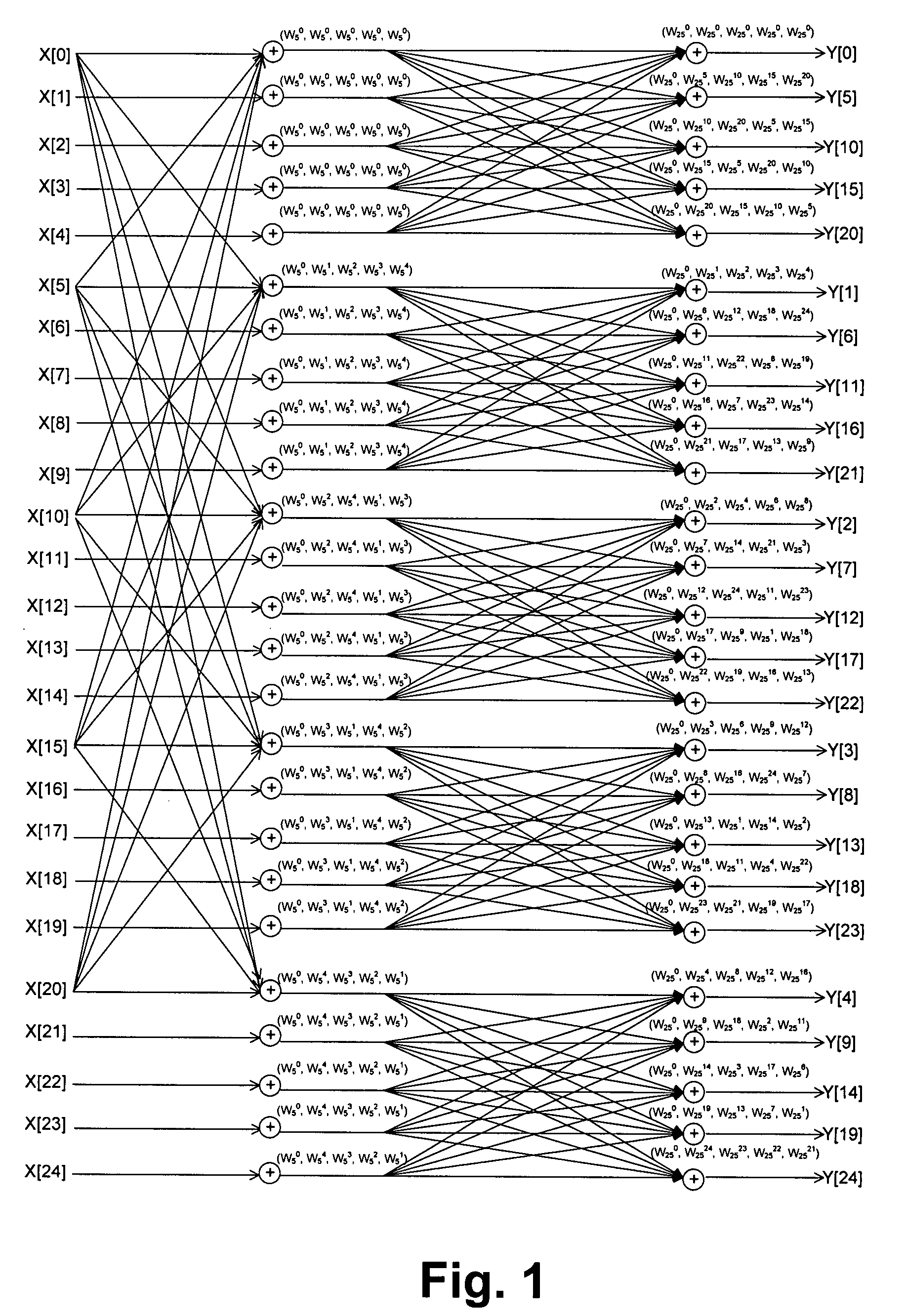

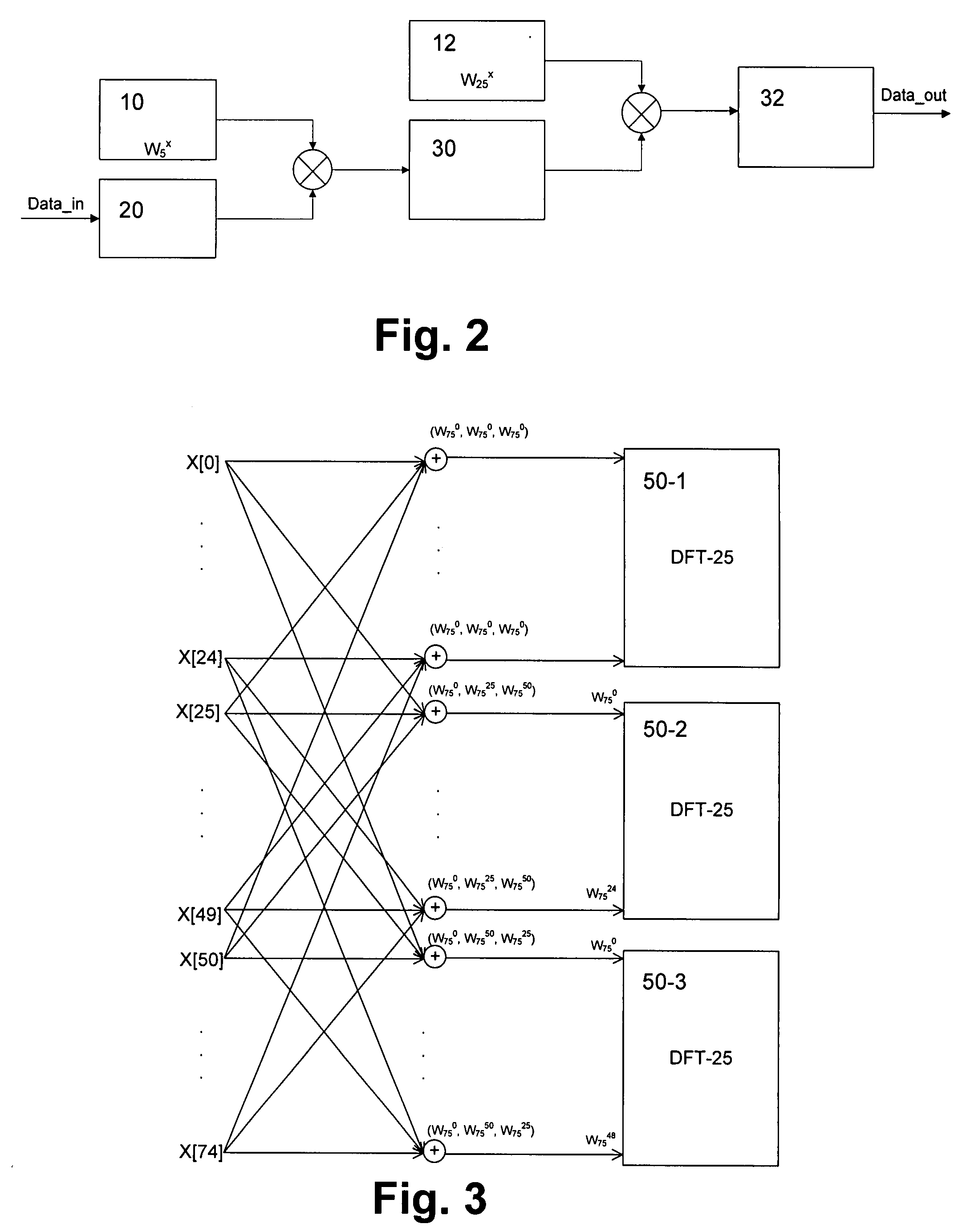

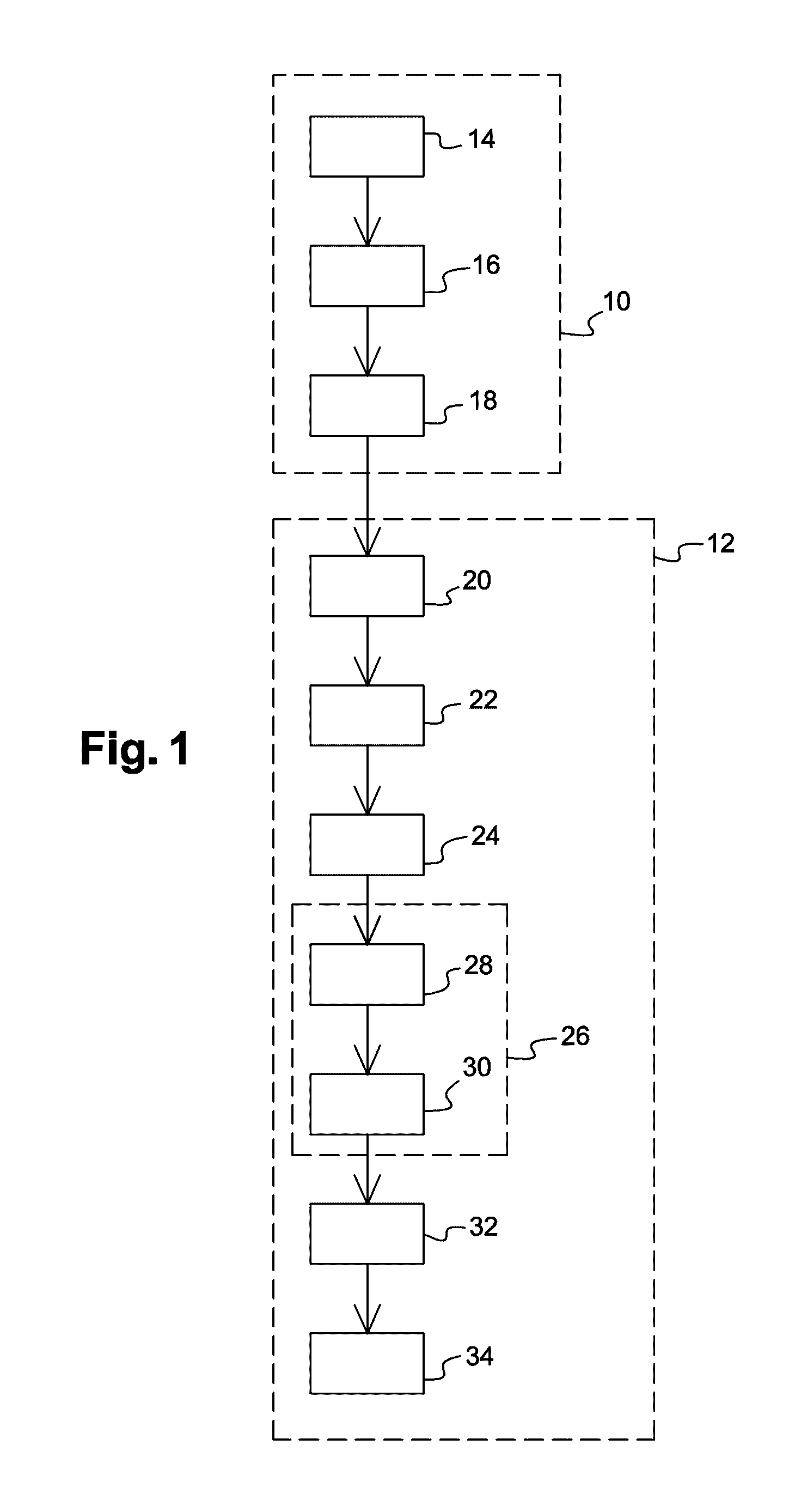

Optimized multi-mode DFT implementation

InactiveUS20080126462A1Moderate complexityReduce processing timeModulated-carrier systemsDigital computer detailsProgramming languageFourier transform on finite groups

The present invention relates to a method and apparatus for implementing a discrete Fourier transformation (DFT) of a predetermined vector size, wherein at least one enhanced DFT module is provided by using at least one type of DFT module including multiplication by first and second types of twiddle factors in respective different multiplication stages separated by an intermediate integration stage, and generating the enhanced DFT module by combining the at least one type of DFT module with a recursive stage configured to multiply by a third type of twiddle factor and to selectively switch between a bypass function and a butterfly function in said recursive stage. Thereby, an implementation of non 2x-radix Fourier transformation can be achieved with moderate hardware complexity.

Owner:NOKIA CORP

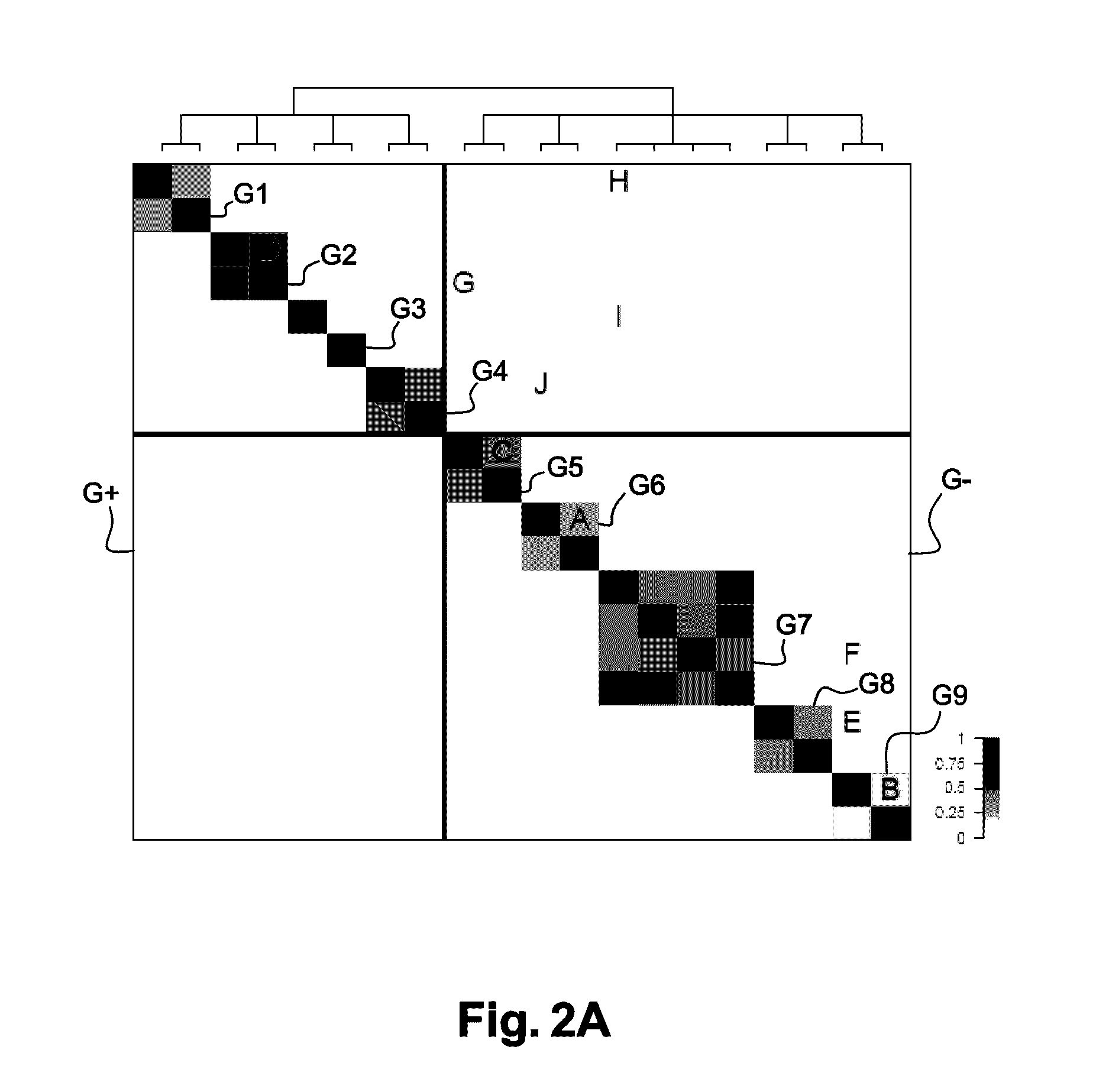

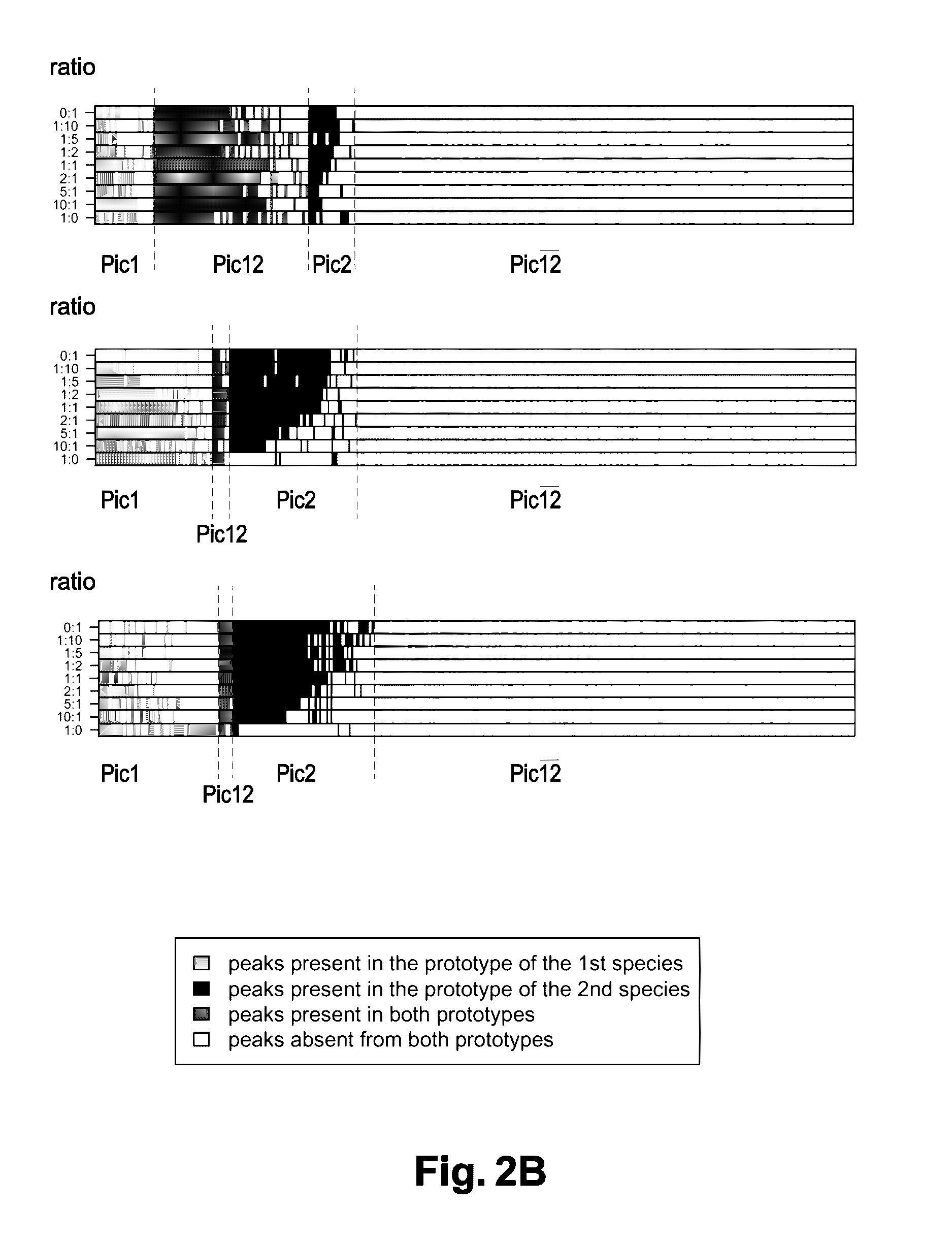

Method and device for analysing a biological sample

PendingUS20160371430A1Moderate complexityHigh success rateBiostatisticsComplex mathematical operationsCircumflexReconstruction error

A method of detecting in a biological sample at least two microorganisms belonging to two different taxa, represented by intensity vectors Pj obtained by multidimensional measurement technique,including (i) acquiring a digital signal of the biological sample with the measurementtechnology, (ii) determining an intensity vector x according to the acquired digitalsignal, (iii) constructing a set {ŷl} of candidate models ŷl=(ŷj,ŷ0)l modeling intensity vector x according tox^l=∑j=1Kγ^jPj(a)+γ^0Iprelationx^l=∑j=1Kγ^jPj(a)+γ^0Ipin which ∀jε[[1,K]], Pj(a)=Σi=1KaijPi; and ∀(i,j)ε[[1,K]]2, aij is a predeterminedcoefficient, (iv) selecting a candidate model {circumflex over (γ)}sel from set {{circumflex over (γ)}l} according toγ^sel=argminγ^l∈{γ^l}(Cv(γ^l)+Cc(γ^l))relationγ^sel=argminγ^l∈{γ^l}(Cv(γ^l)+Cc(γ^l))in which Cv({circumflex over (γ)}l) is a criterion quantifying a reconstruction error between the intensity vector of biological sample x and reconstruction {circumflex over (x)}l of intensity vector x by a candidate model {circumflex over (γ)}l; and Cc({circumflex over (γ)}l) is a criterion quantifying the complexity of a candidatemodel {circumflex over (γ)}l, and (v) determining the presence in the biological sample of at least two taxa when at least two components of vector {circumflex over (γ)}j of {circumflex over (γ)}sel are greater than a positive threshold.

Owner:BIOMERIEUX SA

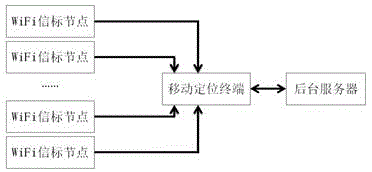

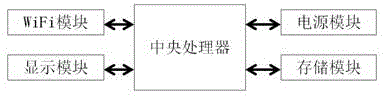

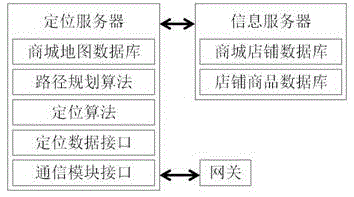

Shopping mall guide and fire-fighting assist system based on optimized indoor location algorithm

InactiveCN105486303AModerate complexityComplexity PreciseNavigation instrumentsComputer terminalDependability

The invention provides a shopping mall guide and fire-fighting assist system based on an optimized indoor location algorithm. The system has good stability, safety, reliability, high positioning accuracy, low hardware cost and moderate complexity of the algorithm, and is applied to the mall environment. The system can conduct bidirectional communication via WiFi beacon nodes; and location information emitted by a mobile location terminal is combined with the optimized location algorithm of a location server for computing, so as to output accurate and precise location results. Based on precise location technology combined with the push of the information server, the system provides the users with accurate indoor location information, store product information, secure path planning and other services, and greatly enhances the user experience and the safety factor in shopping mall.

Owner:SYSU CMU SHUNDE INT JOINT RES INST +1

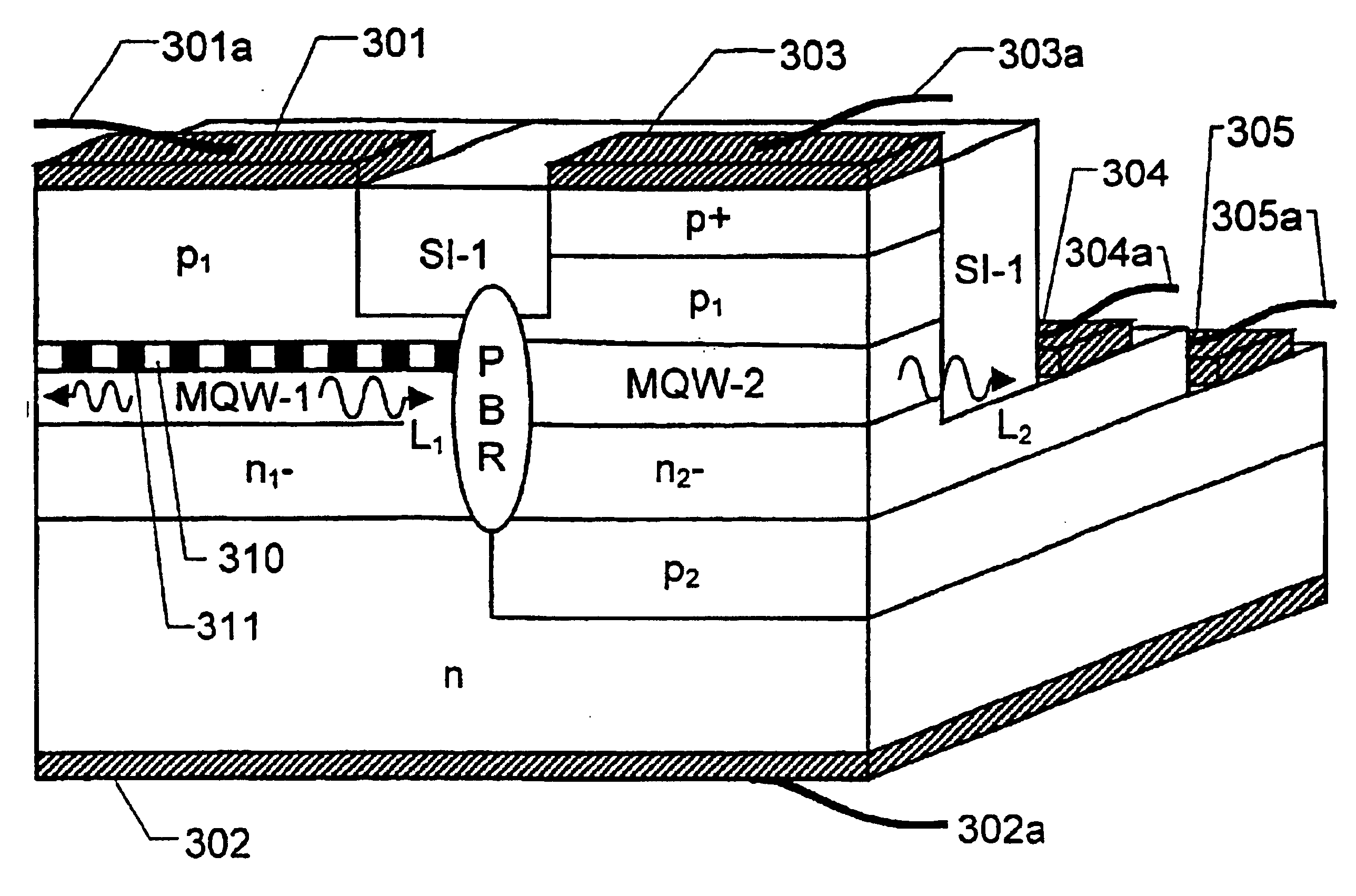

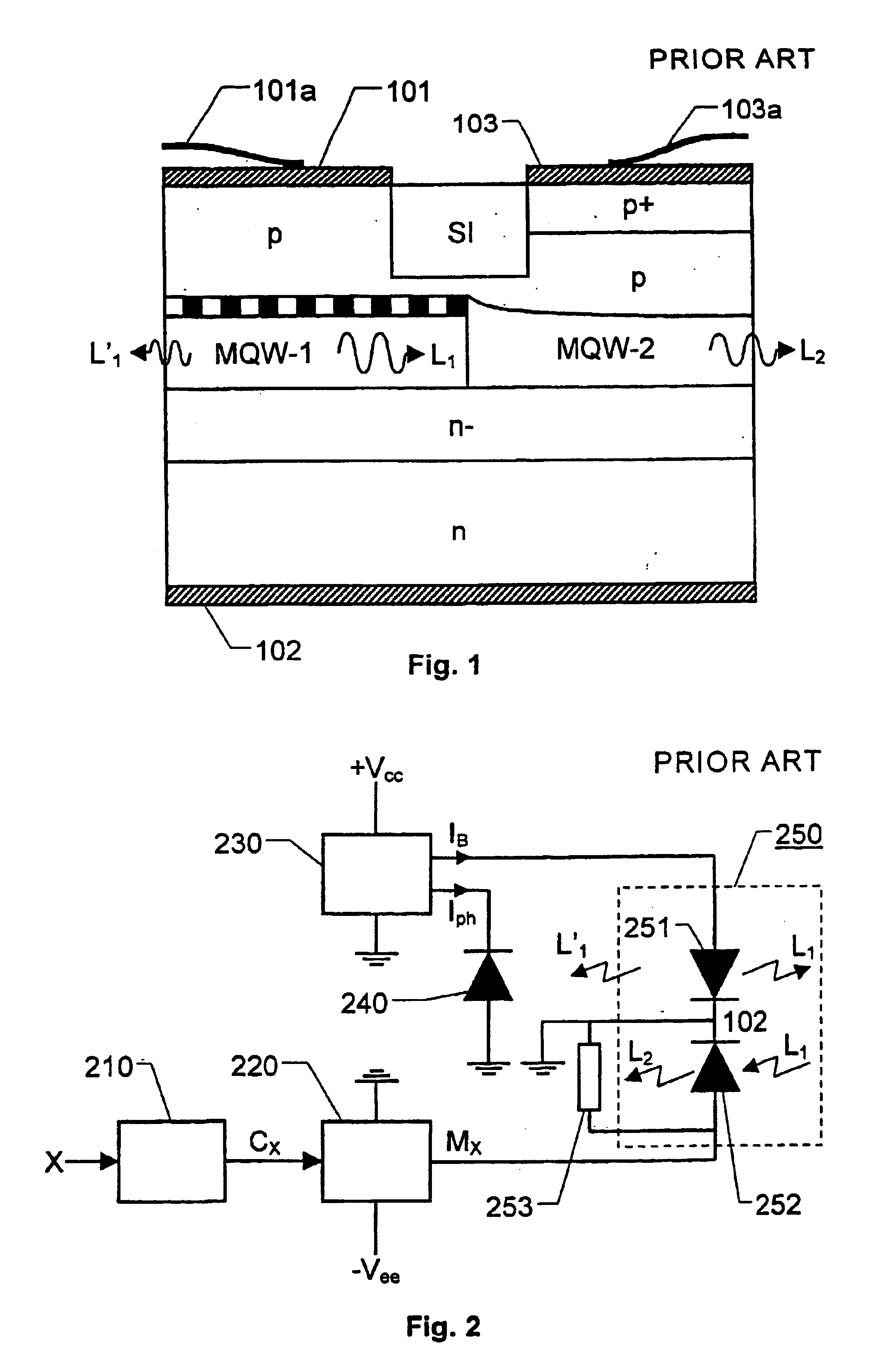

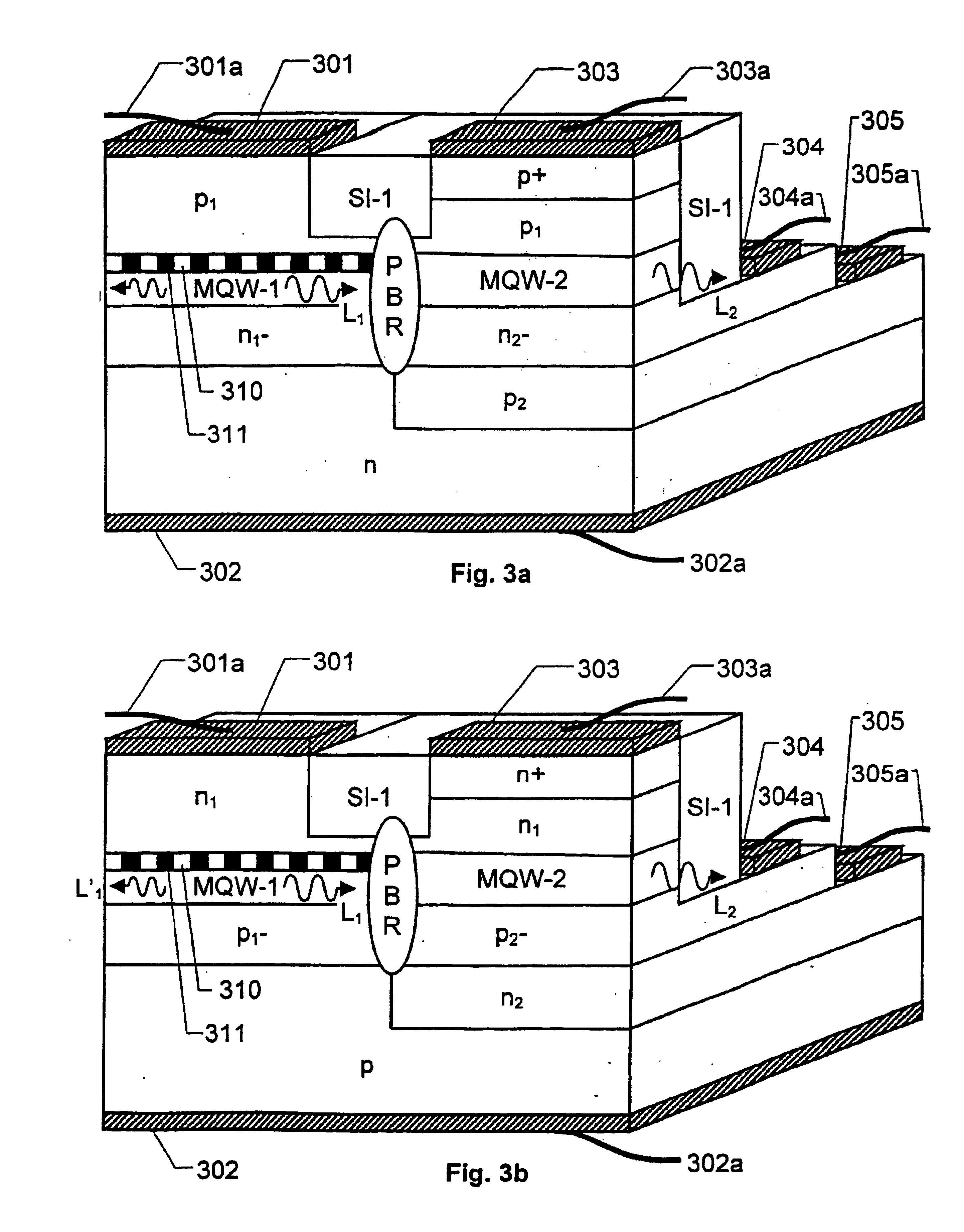

Laser modulator

InactiveUS6859479B2Moderate complexityImprove efficiencyLaser detailsSemiconductor lasersElectricityControl signal

An integrated device is provided having both laser and modulator sections. The laser section generates a primary light signal using a distributed feedback process. The modulator section influences the primary light signal by means of an electroabsorption process. The laser and modulator sections are electrically separated from each other with respect to anode and cathode areas. As a result, a single supply voltage can be used to operate the device. An optical transmitter contains, in addition to the integrated device, a protocol converter which receives an information signal to be transmitted and generates a control signal which is received by a modulator driver. Based thereon, the modulator driver produces a modulating signal, which causes a modulated light signal representing the information signal to be output. A laser bias control unit controls the output power level of the primary light signal based on a leak signal from the laser section.

Owner:II VI DELAWARE INC

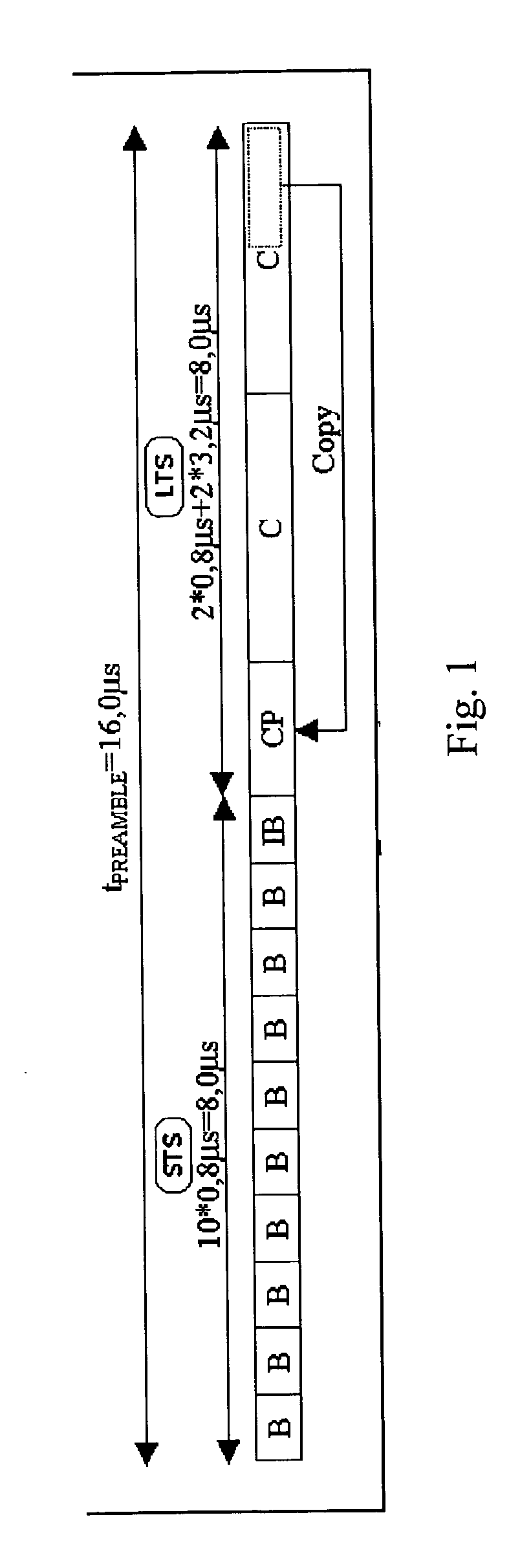

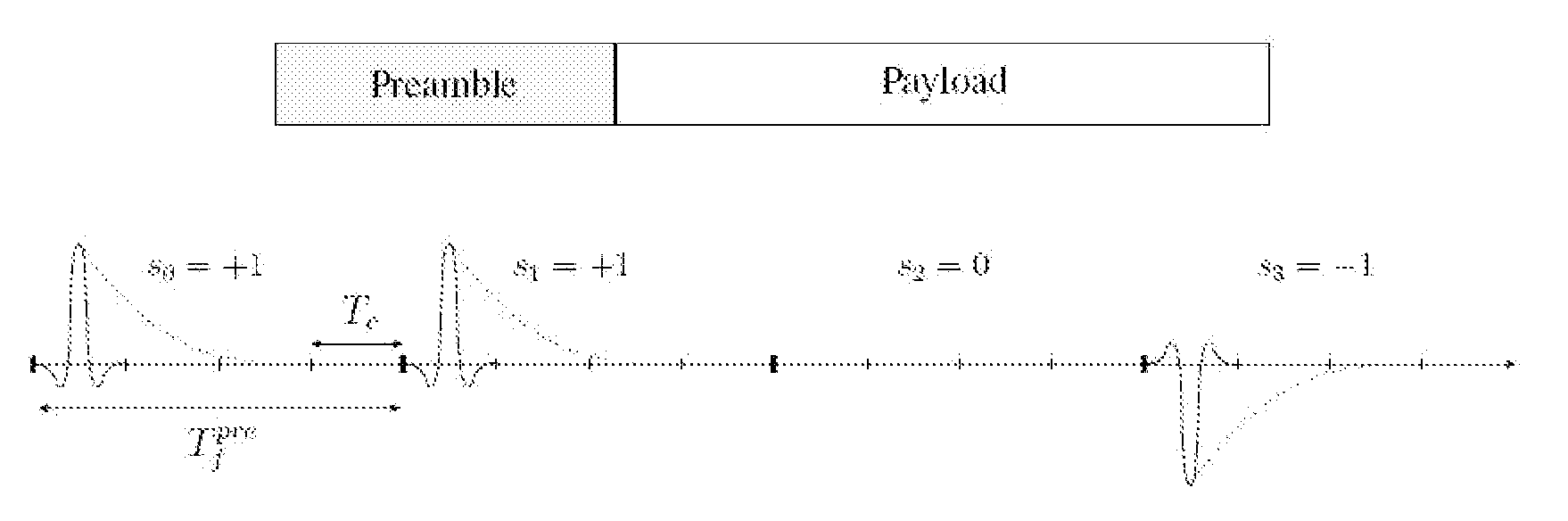

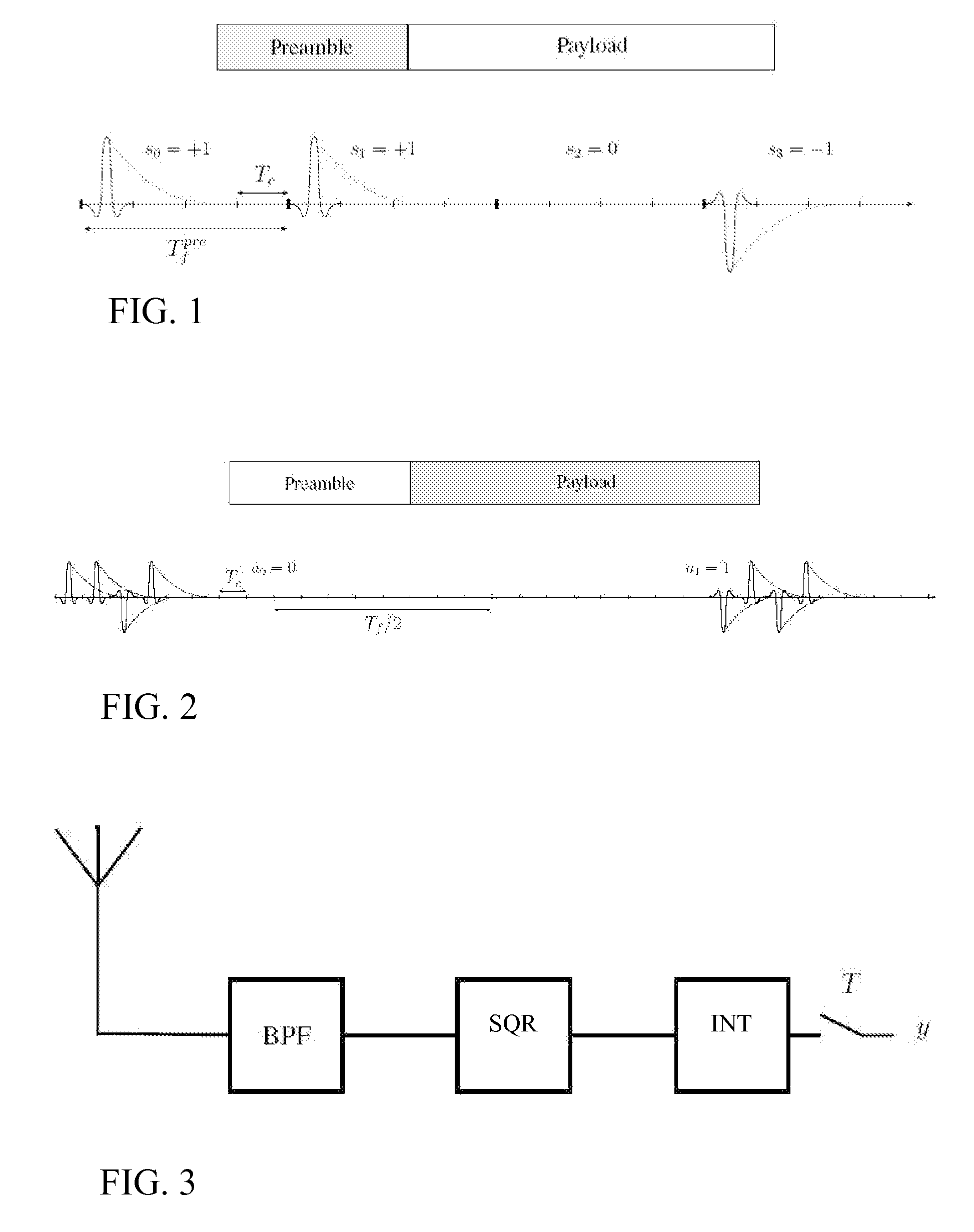

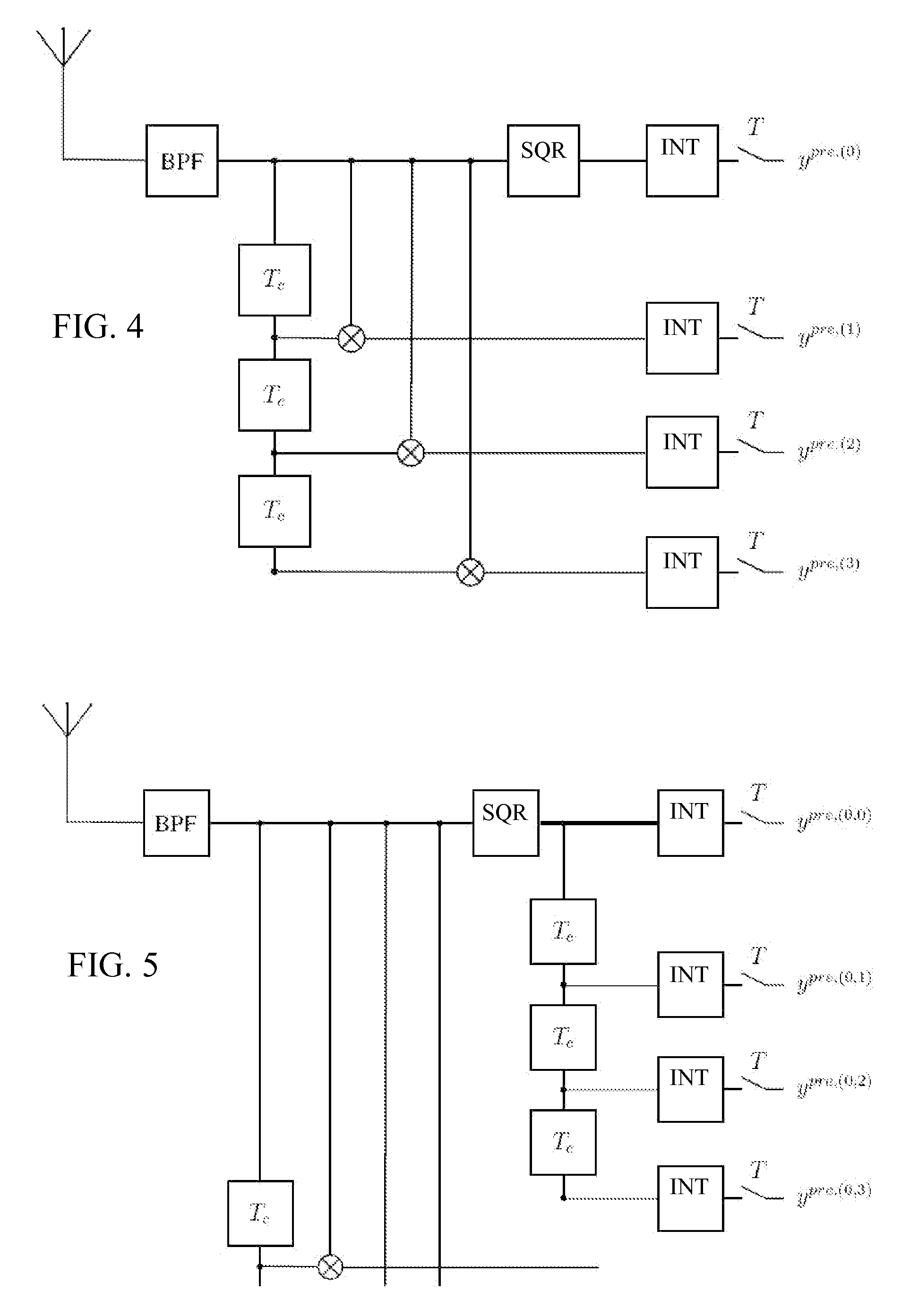

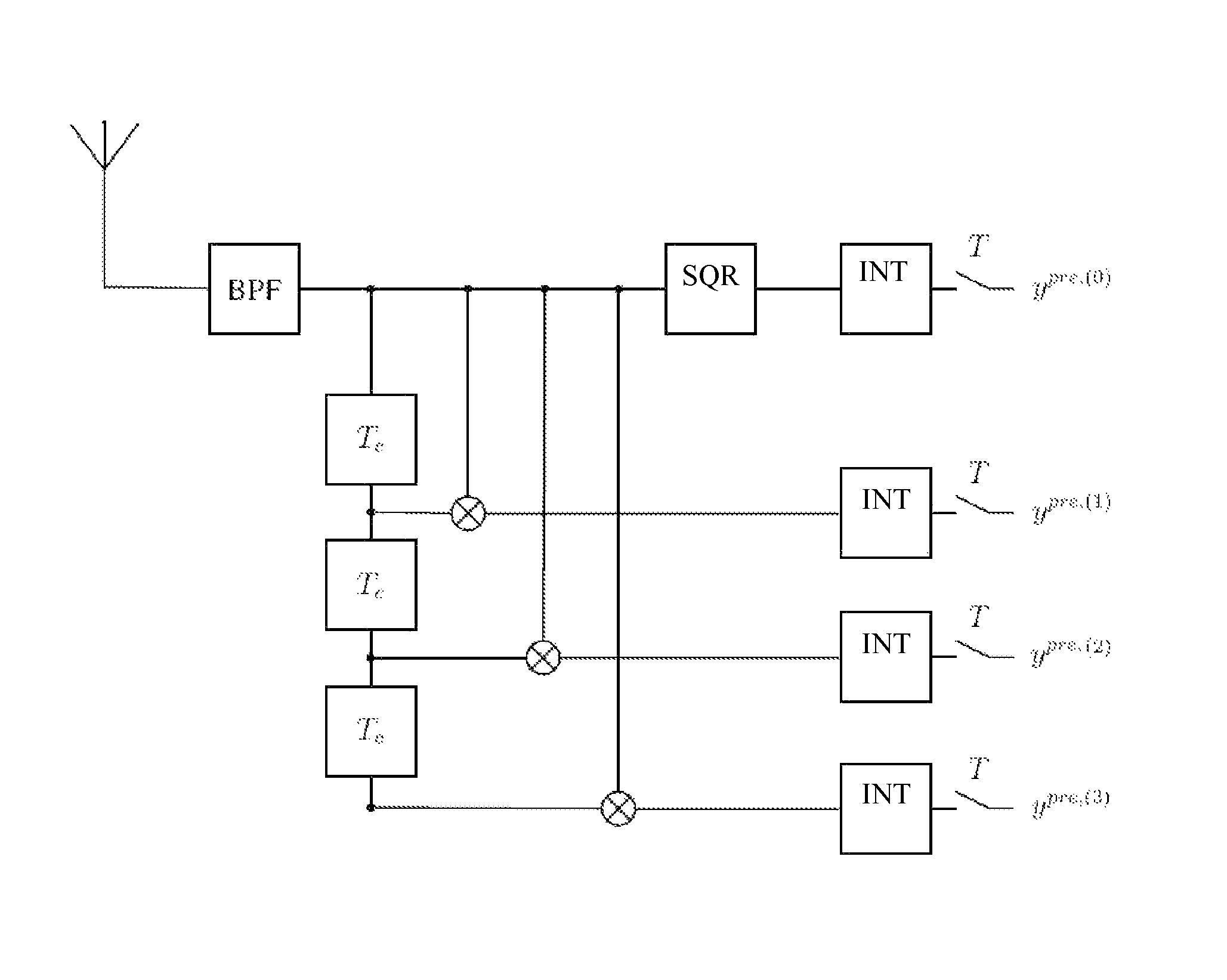

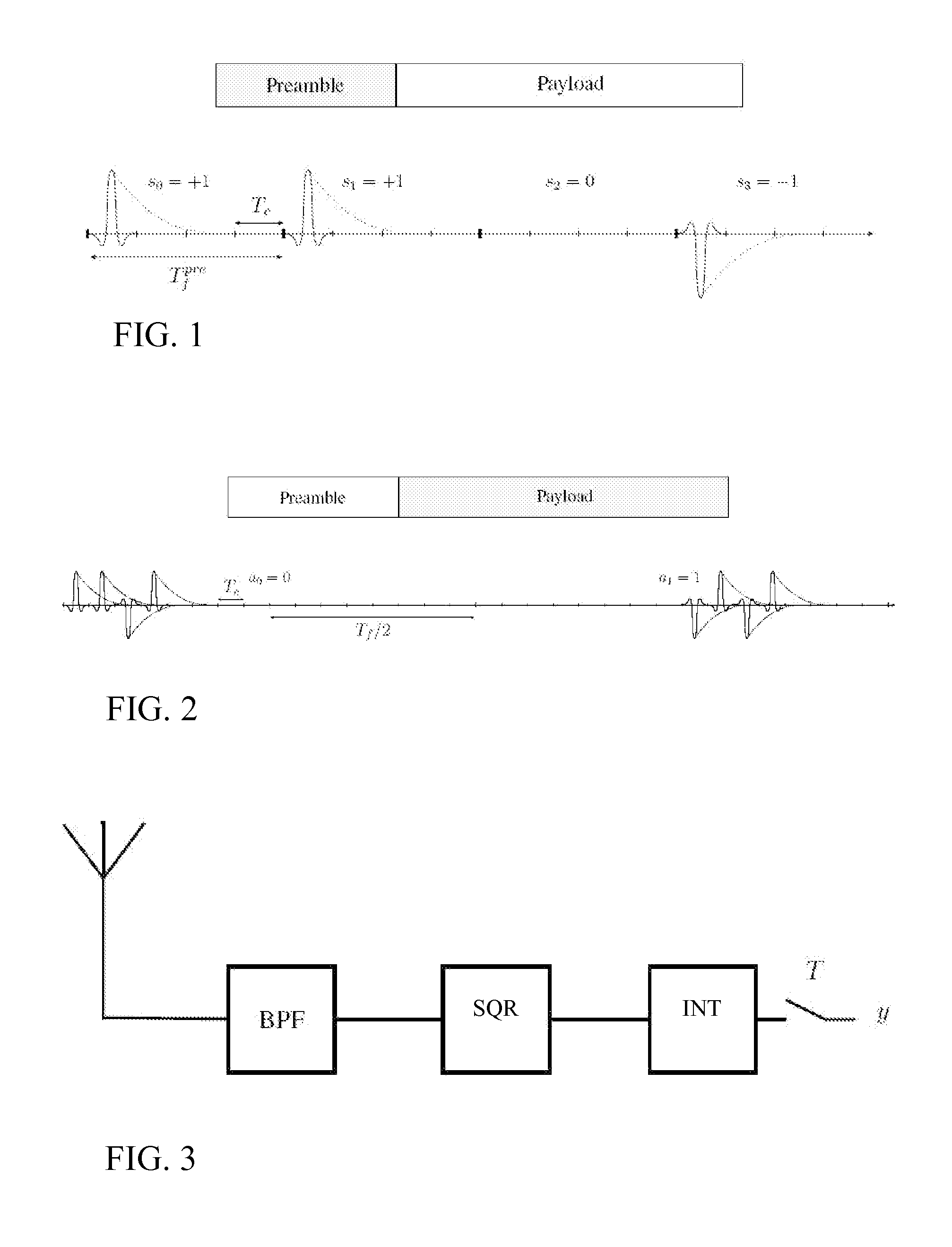

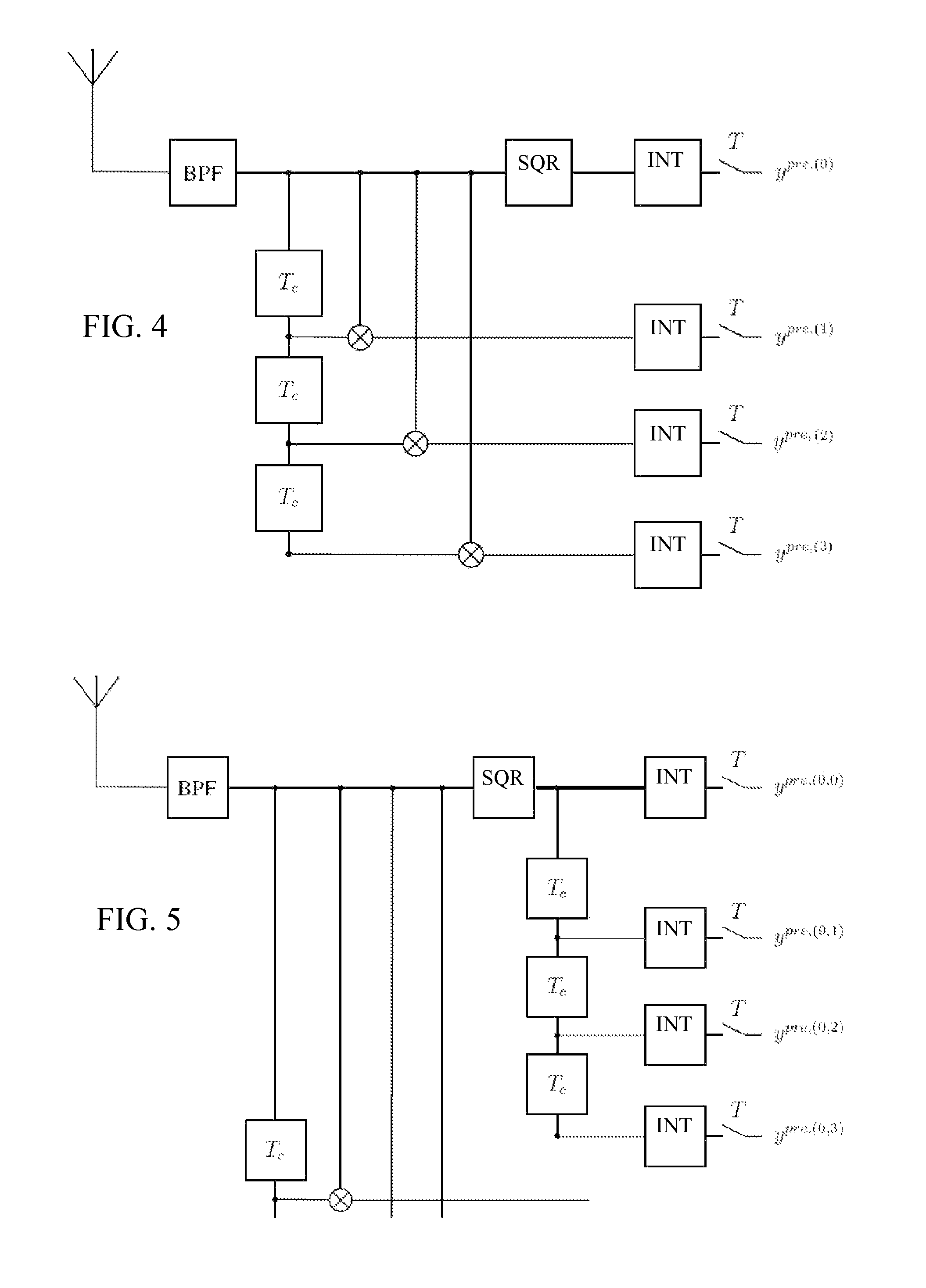

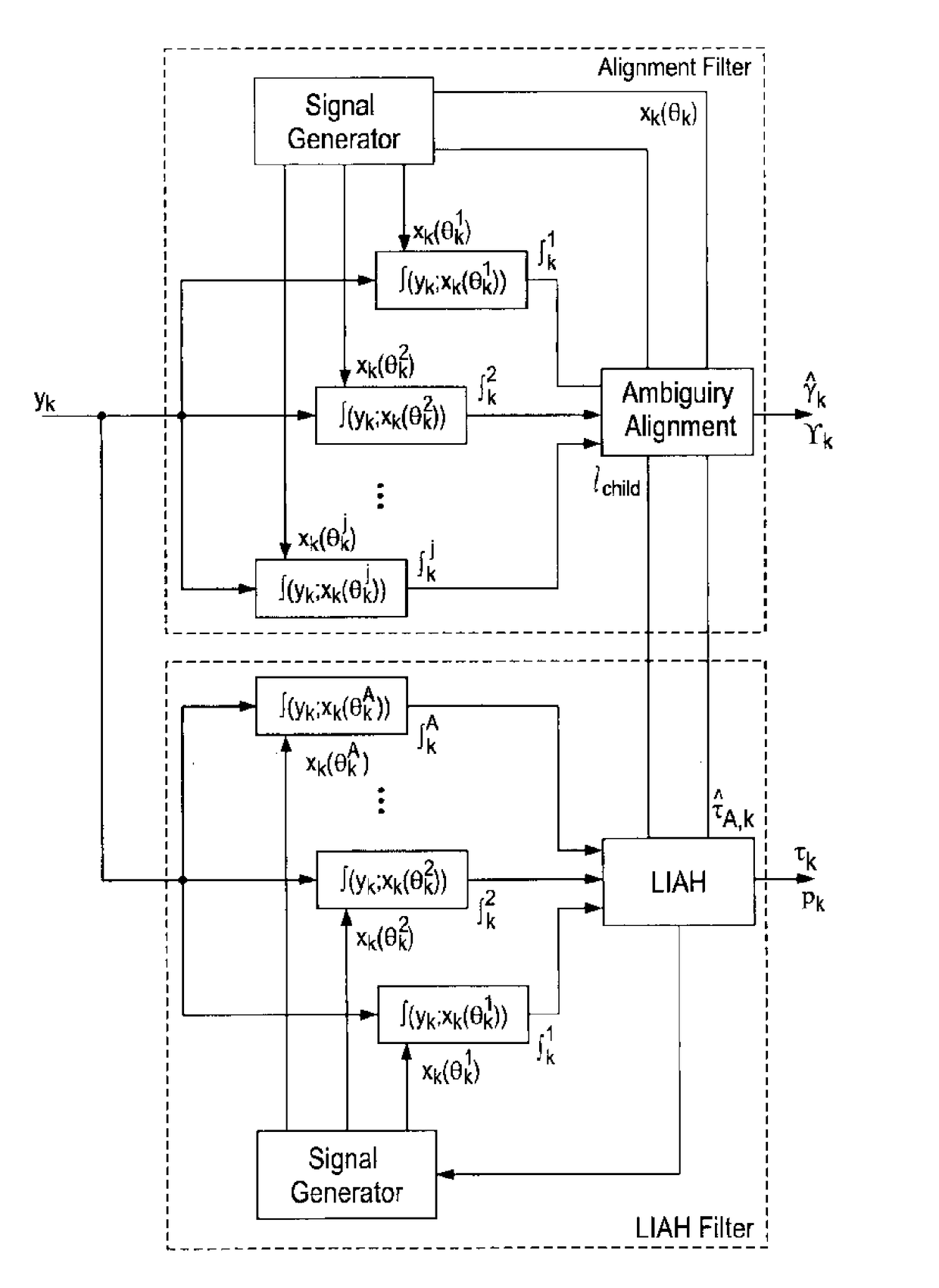

Method for retrieving data from ultra wideband radio transmission signals and receiver implementing said method

InactiveUS20100309875A1Improve robustnessIncreased complexityError preventionTime-division multiplexUltra-widebandWeight coefficient

The present invention concerns a receiver and a method for retrieving data from Ultra wideband radio transmission signals received by a receiver and transmitted in packets containing at least a preamble known to the receiver and a payload containing data unknown to the receiver. The payload data is formed of at least one burst containing at least one pulse. The method comprises the steps of receiving a signal corresponding to the preamble of a packet by a receiver; determining the energy of the received signal; determining weighting coefficients from the energy of the received signal; receiving a signal corresponding to the payload of a packet by a receiver; determining the energy of the received signal; calculating a threshold depending on the weighting coefficients; and applying a decision rule based on the sampled energy, weighted by said weighting coefficients and depending on said calculated threshold.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

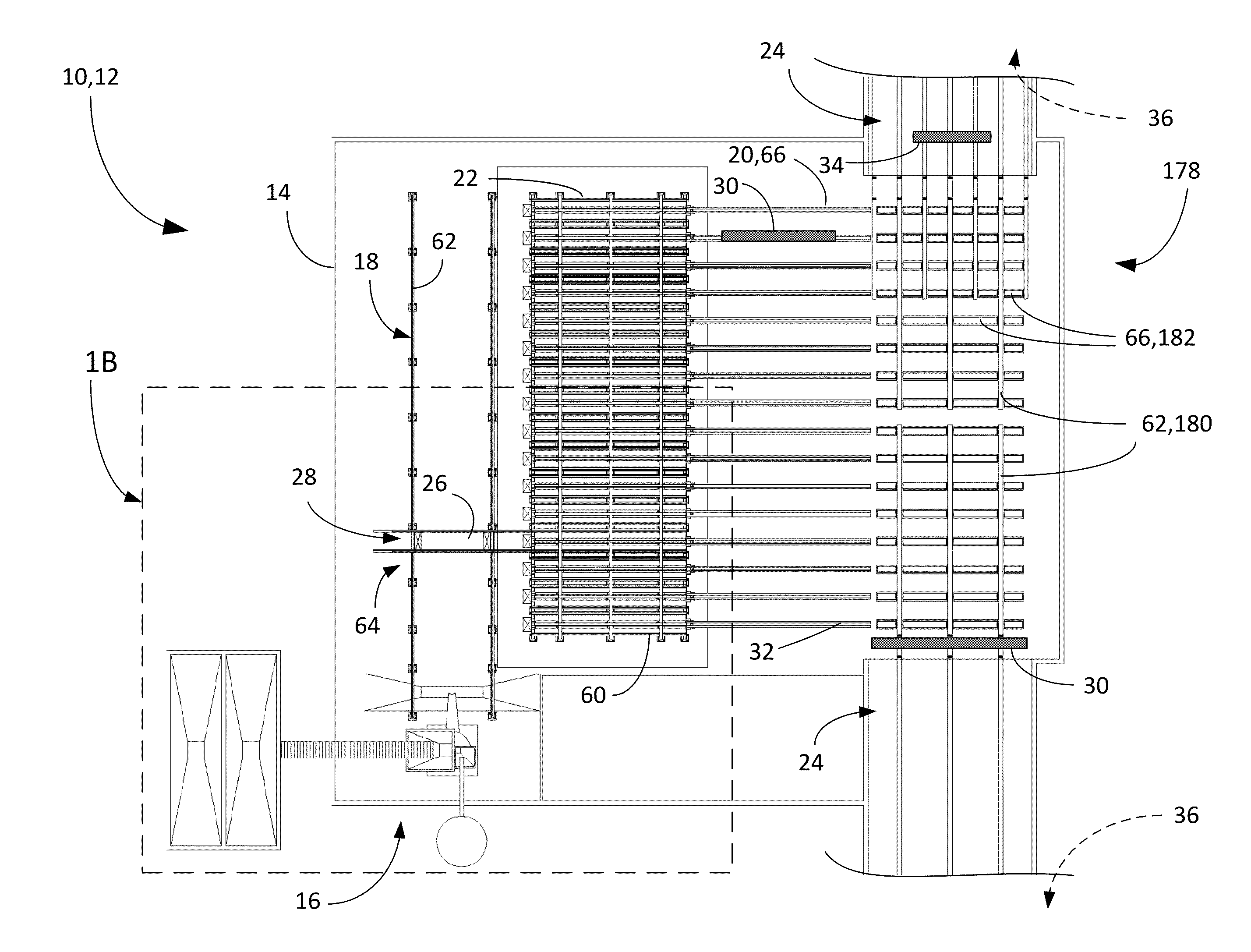

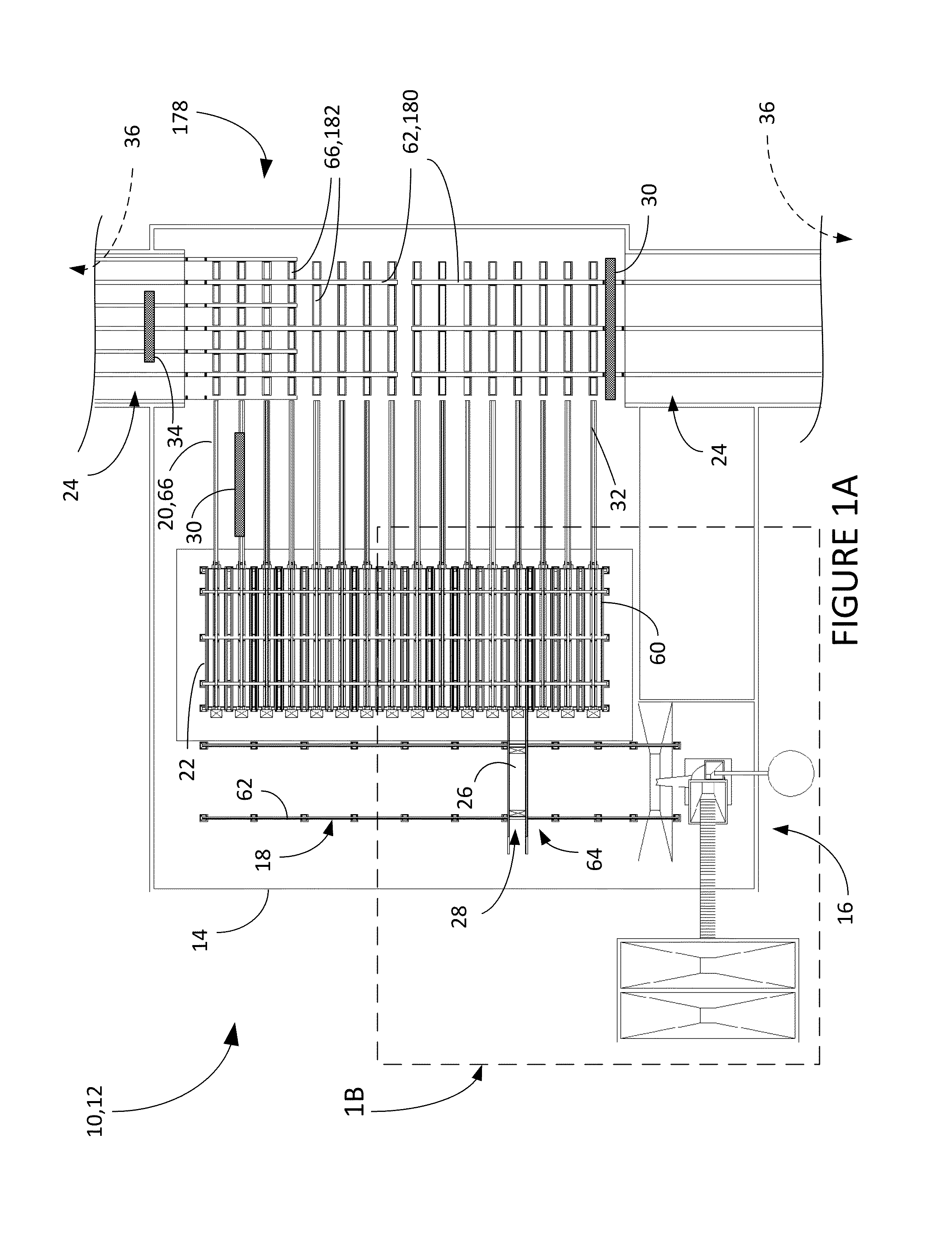

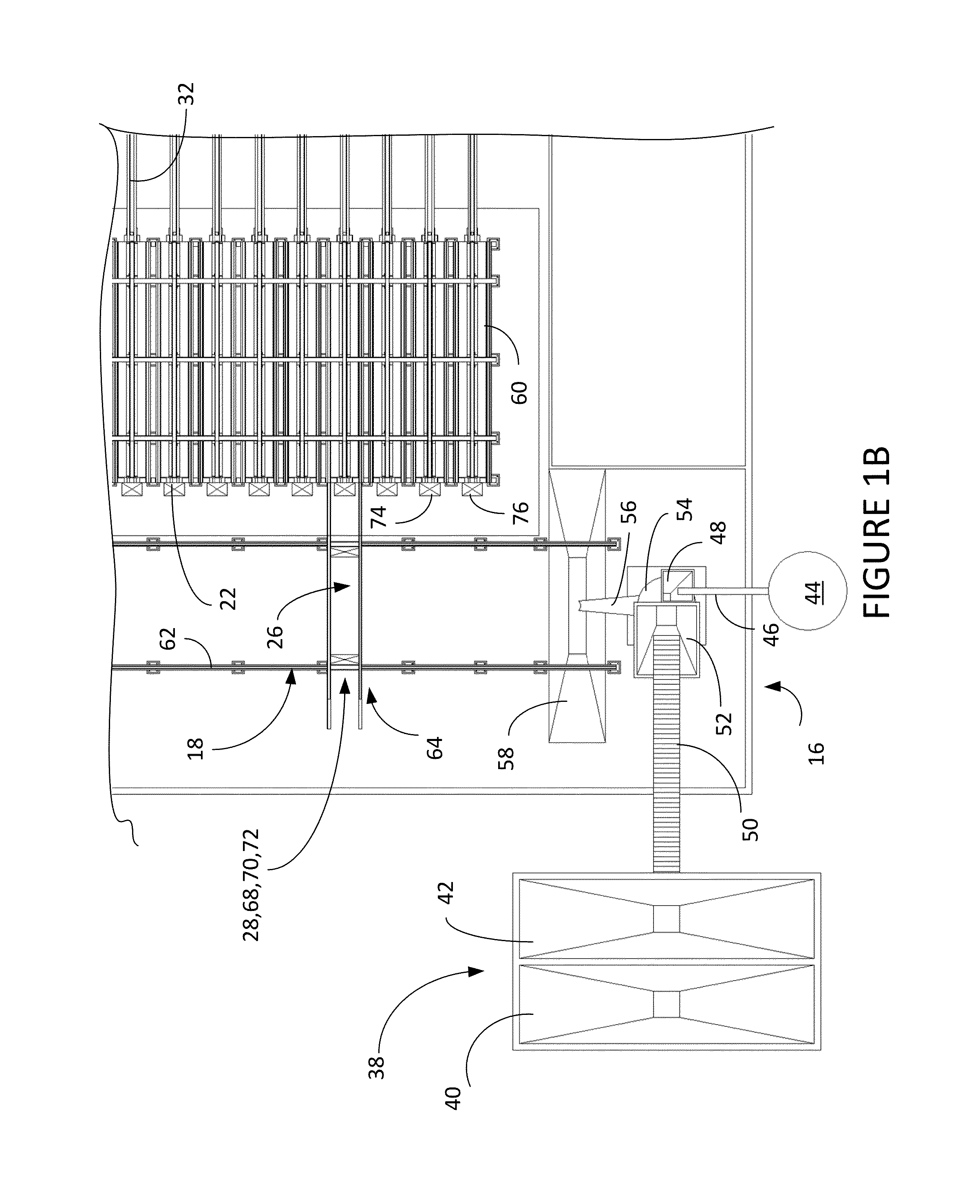

Concrete delivery subsystem for automated concrete fabrication system

ActiveUS9415528B1Efficient and streamlinedReduce sizeConstruction materialMouldsTransfer systemConcrete pump

A concrete delivery subsystem for delivering concrete to a plurality of casting machines having a concrete mixing source, a concrete pump; and a concrete transfer system, which includes a concrete placement boom a concrete delivery hose, and a concrete manifold having a splitting edge having a fillet radius within the range of 0.005 inch. to 0.01 inch. Also a concrete manifold having a splitting edge having a fillet radius within the range of 0.005 inch. to 0.01 inch.

Owner:SPEEDBLOCK INC

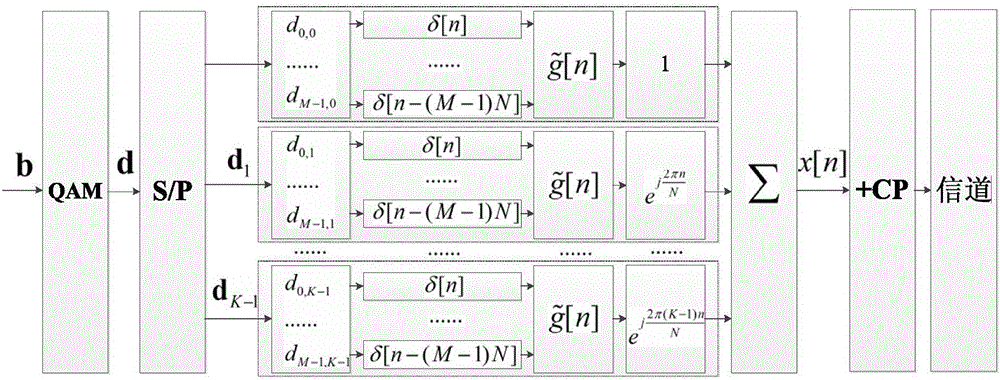

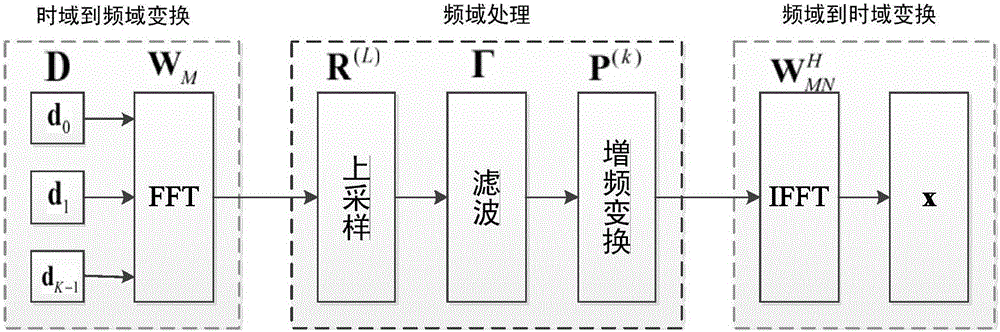

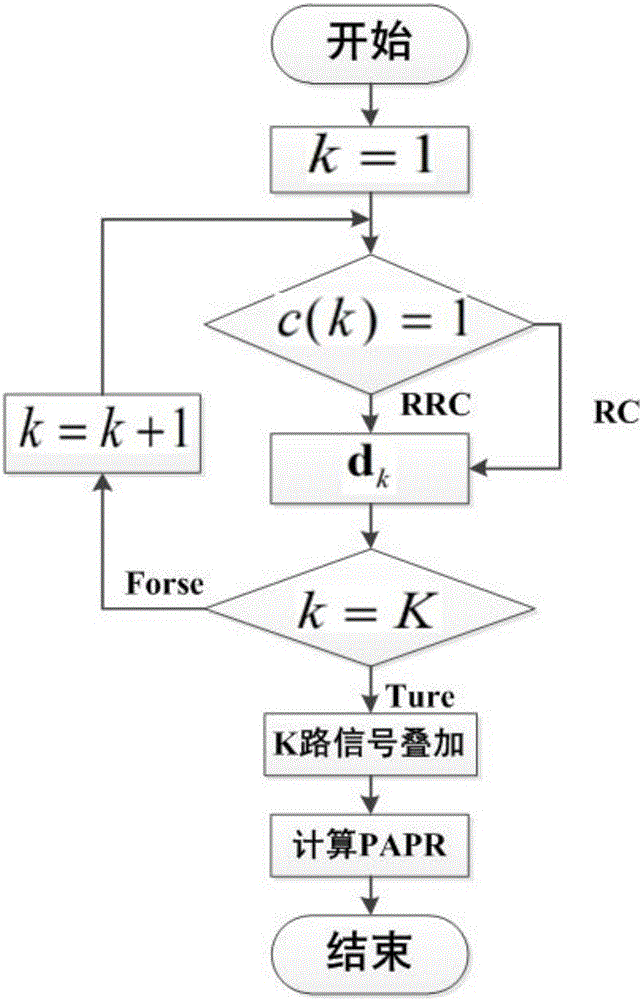

Algorithm for reducing PAPR (Peak to Average Power Ratio) in GFDM system on basis of random filter allocation

ActiveCN106254292AGood effectHigh computational complexityMulti-frequency code systemsCommunications systemCarrier signal

The invention requests to protect an algorithm for reducing a PAPR (Peak to Average Power Ratio) in GFDM system on basis of random filter allocation, and relates to a wireless communication system. Just like all multi-carrier systems, due to superposition of output signals, the GFDM system still has a high PAPR. Multiple methods for reducing a PAPR in an OFDM system exist, but due to the characteristics of the GFDM system, an effect obtained by directly adopting the method for reducing the PAPR in the OFDM system is not ideal. Aiming at the problems of the current research, according to the structural characteristic that the GFDM system can flexibly select a filter, a novel method for reducing the PAPR in the system is disclosed. By randomly allocating different filters to each path of subcarrier, the novel method aims to destroy phase consistency in the signal superposition process so as to effectively inhibit the PAPR, and cannot cause distortion of the signals. Theoretical analysis and a simulation result prove superiority of the algorithm.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Method for retrieving data from ultra wideband radio transmission signals and receiver implementing said method

InactiveUS8385187B2Moderate complexityReasonable complexityError preventionTime-division multiplexUltra-widebandWeight coefficient

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

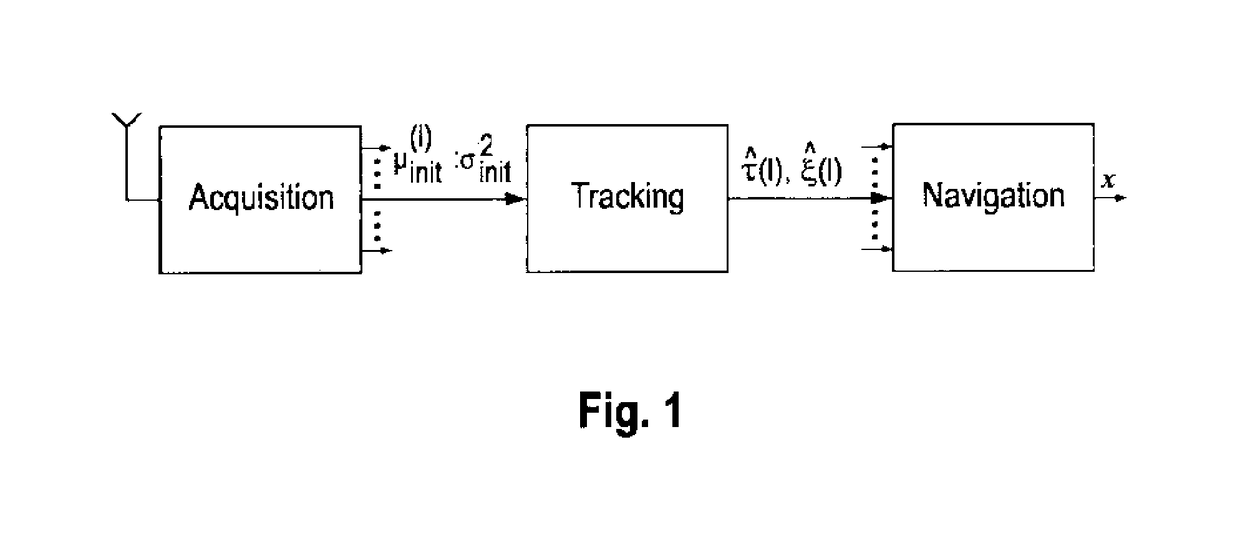

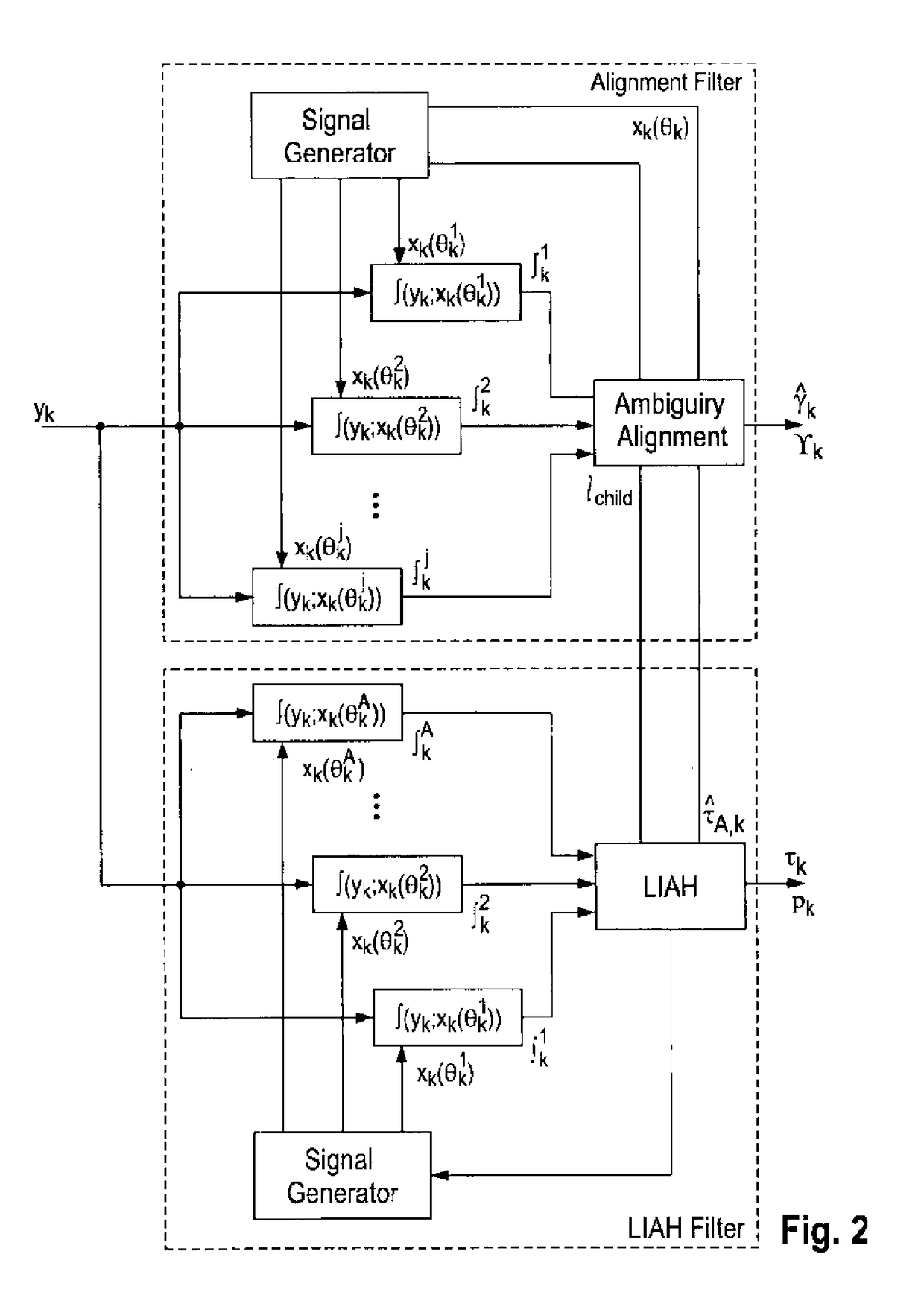

Ranging method and apparatus

ActiveUS20180246195A1Increase rangeHigh synchronization accuracyPosition fixationSatellite radio beaconingPropagation delaySignal correlation

The present invention relates to a method of determining a distance or location of a remote device or reflector, the method comprising: receiving a signal from a remote signal transmitter associated with or contained in or attached to the remote device; estimating a first propagation delay associated with the received signal, wherein the first propagation delay represents a first candidate for a correct propagation delay; deriving a relationship between the first candidate and one or more other candidates for a correct propagation delay from the received signal; determining a plurality of other candidates for a correct propagation delay based on said relationship; generating a likelihood histogram based on said candidates for a correct propagation delay; selecting a propagation delay from said candidates based on the likelihood histogram; and determining a distance or location of the remote device or reflector using the selected propagation delay.

Owner:TECH UNIV MUNCHEN

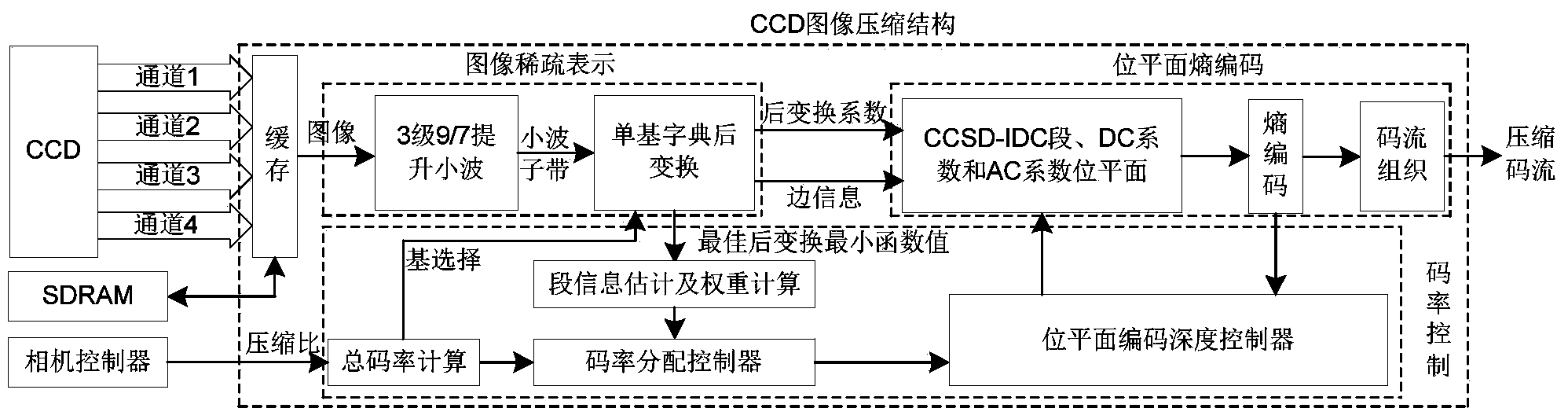

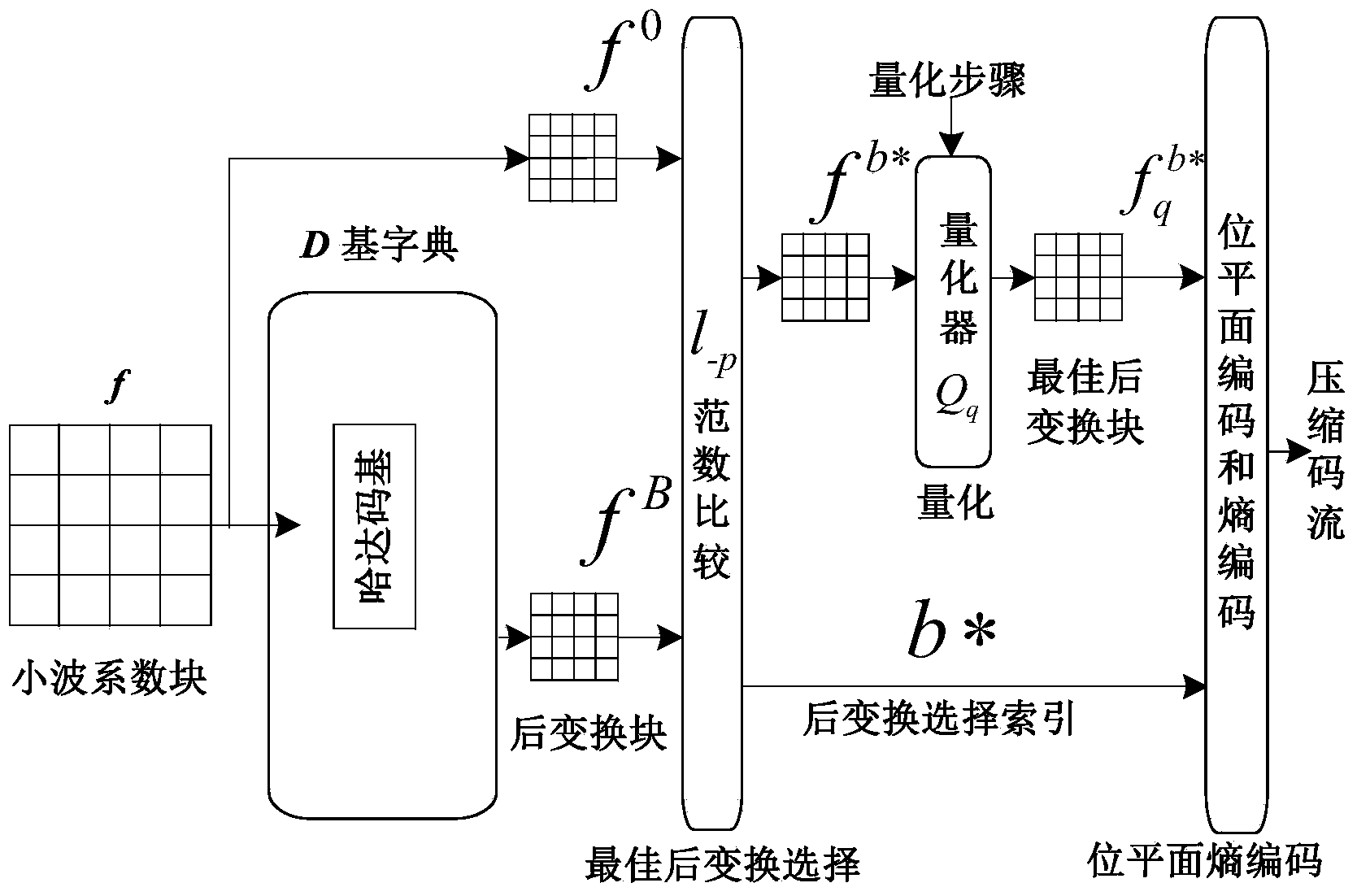

Image compression unit for large visual field TDICCD camera

InactiveCN103402043AEasy to keepPreserve texture informationTelevision system detailsColor television detailsVisual field lossImage compression

The invention discloses an image compression unit for a large visual field TDICCD camera, which includes an image sparse representation part, a bit plane entropy coding part and a rate control part, wherein the image sparse representation part includes the steps of firstly performing 3-level 9 / 7 wavelet transformation to the image, generating 1 low-frequency subband and 9 high-frequency subbands, and performing the post transformation to the 9 high-frequency subbands; the bit plane entropy coding part includes the steps of performing BPE coding to post transformation factors, and performing entropy coding to the coding result, coding a wavelet low-frequency subband through prediction, and performing entropy coding to a predicated residual error. According to the invention, the Hadamard single-machine dictionary post transformation strategy in the wavelet domain can be adopted to remove dependency among wavelet factors in the wavelet subband, the defect that the wavelet transformation is poor in sparse representation capability of remote sensing images with texture complex degree can be made up, rich information of the space CCD image borders and textures can be well protected; the image compression unit has the characteristics of excellent compression performance, moderate complex rate and high reliability, and is suitable for being used on satellites.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

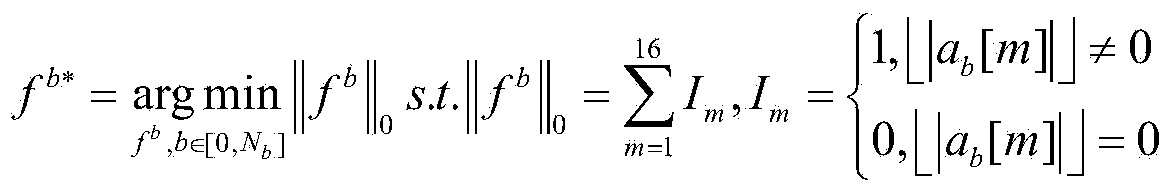

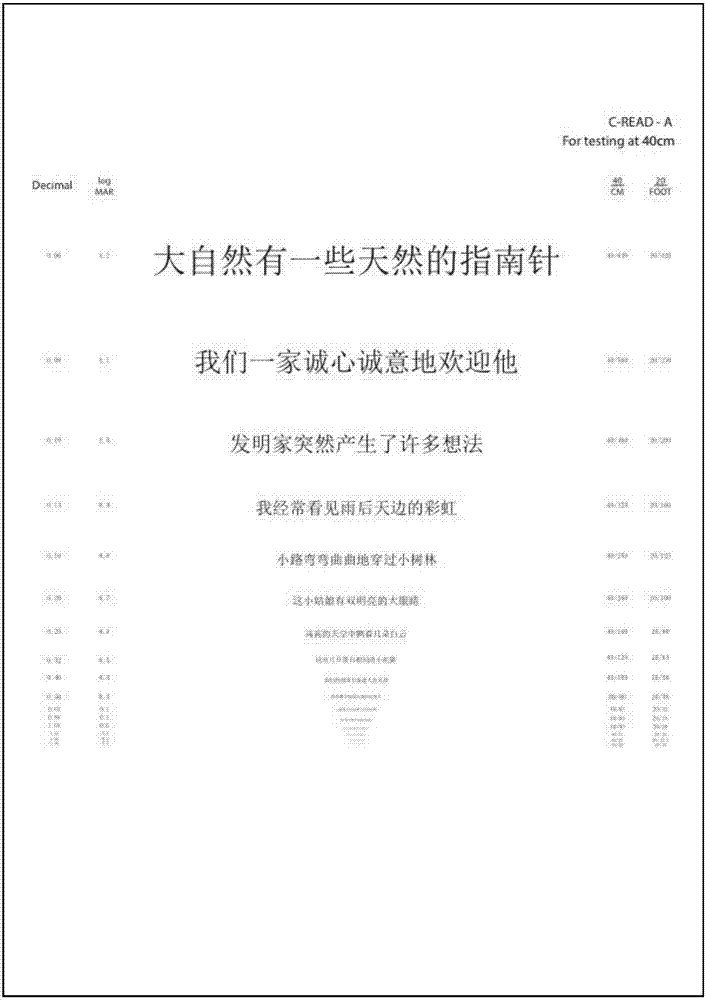

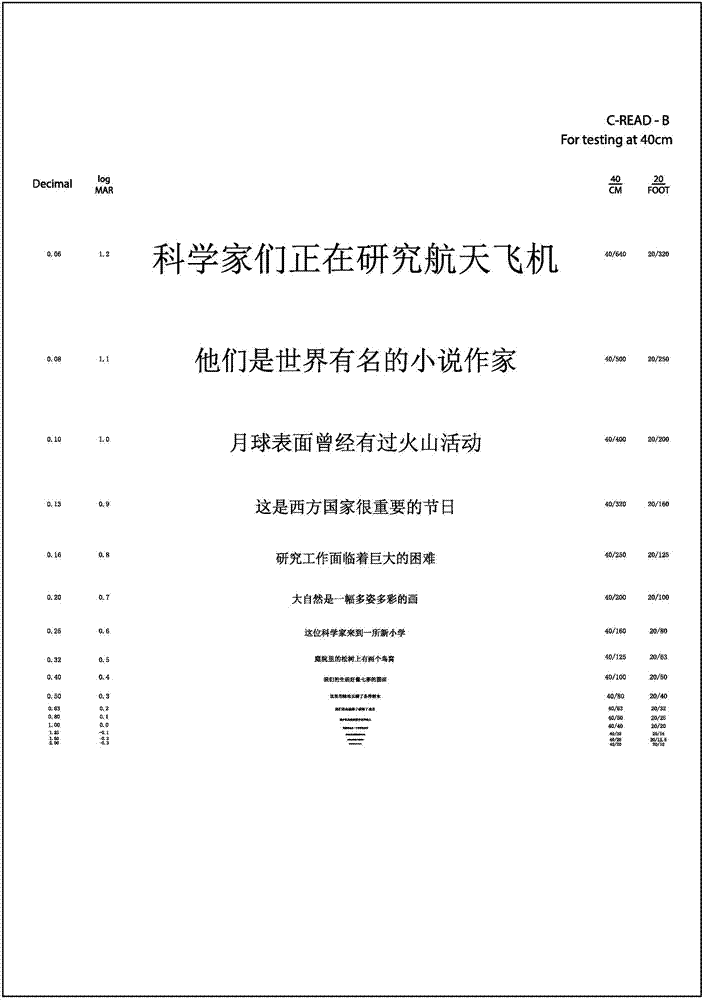

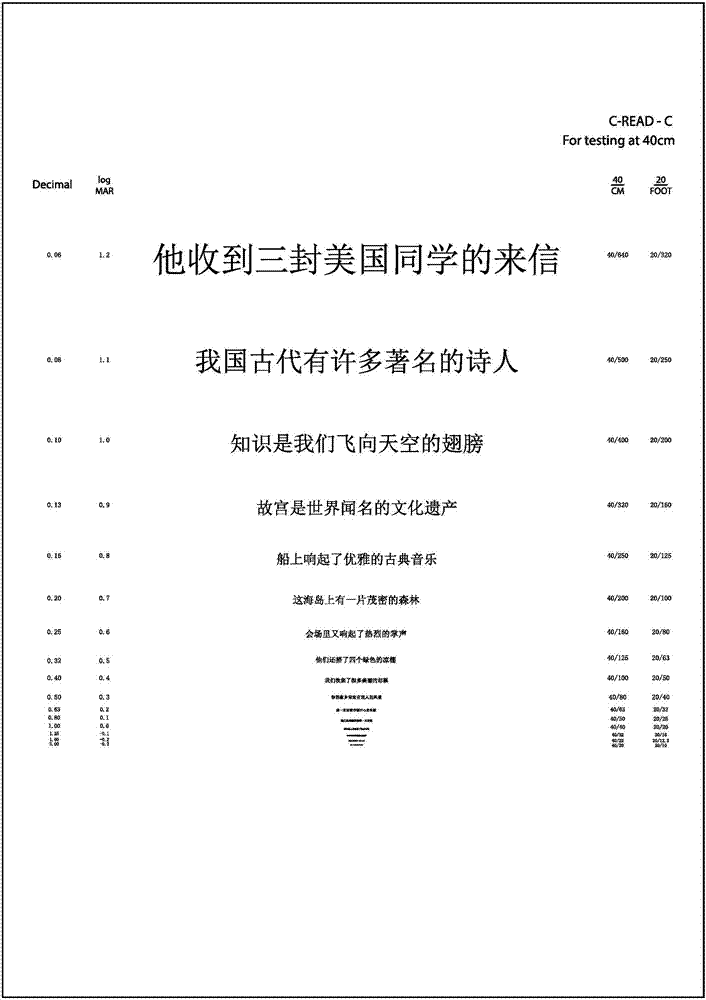

Chinese read logarithm vision testing chart and Chinese read ability testing method

The invention discloses a Chinese read logarithm vision testing chart and a Chinese read ability testing method. The Chinese read logarithm vision testing chart includes a plurality of lines of optotypes which are centralized and arranged along a longitudinal axis; the optotypes are sentences which are showed in each line; each sentence includes Chinese characters having the same printing size; the number of the optotypes in each line is identical; contents of the sentences of the optotypes in all the lines are different from each other; the size of the optotypes is represented by the height of the Chinese characters in the sentences of the optotypes, and is gradually decreasing from top to bottom; and the optotype size is a logarithm mark. In test, the Chinese read logarithm vision testing chart is drawn, the optotypes are visible for a subject line by line, the reading time and the number of error characters are recorded till the number of recognizable Chinese characters for the subject is equal to 0, and the Chinese character recognition ability of the subject and the reading speed of the subject can be calculated. The Chinese read logarithm vision testing chart and the Chineseread ability testing method can quickly and accurately acquire the Chinese character recognition ability and the reading speed of the subject, and can be applied to research or clinics.

Owner:PEKING UNIV

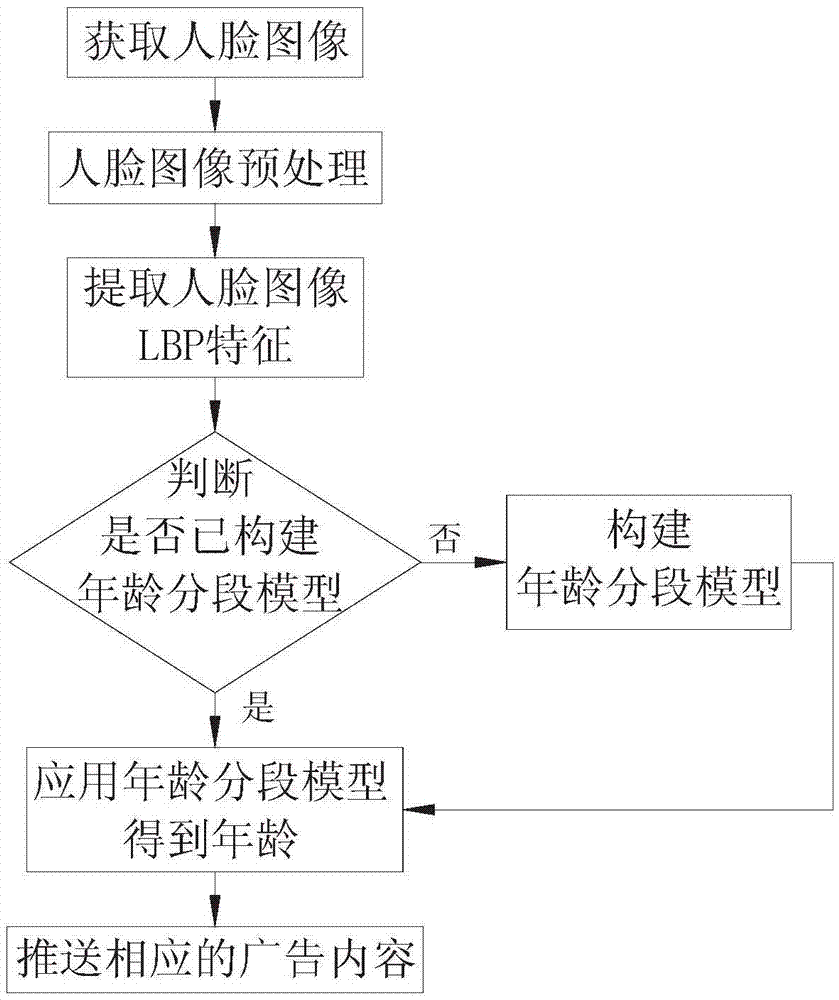

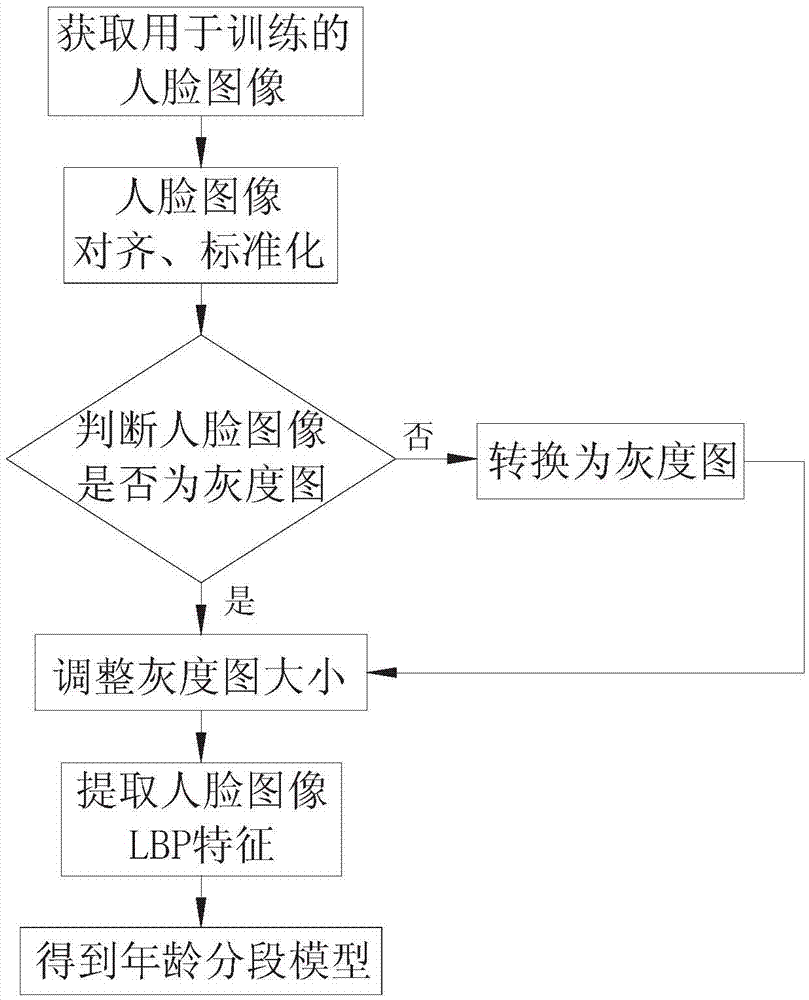

Advertisement pushing method based on age group

InactiveCN106921893AModerate sizeModerate complexityCharacter and pattern recognitionSelective content distributionAge groupsImage pre processing

Owner:苏州工业园区洛加大先进技术研究院

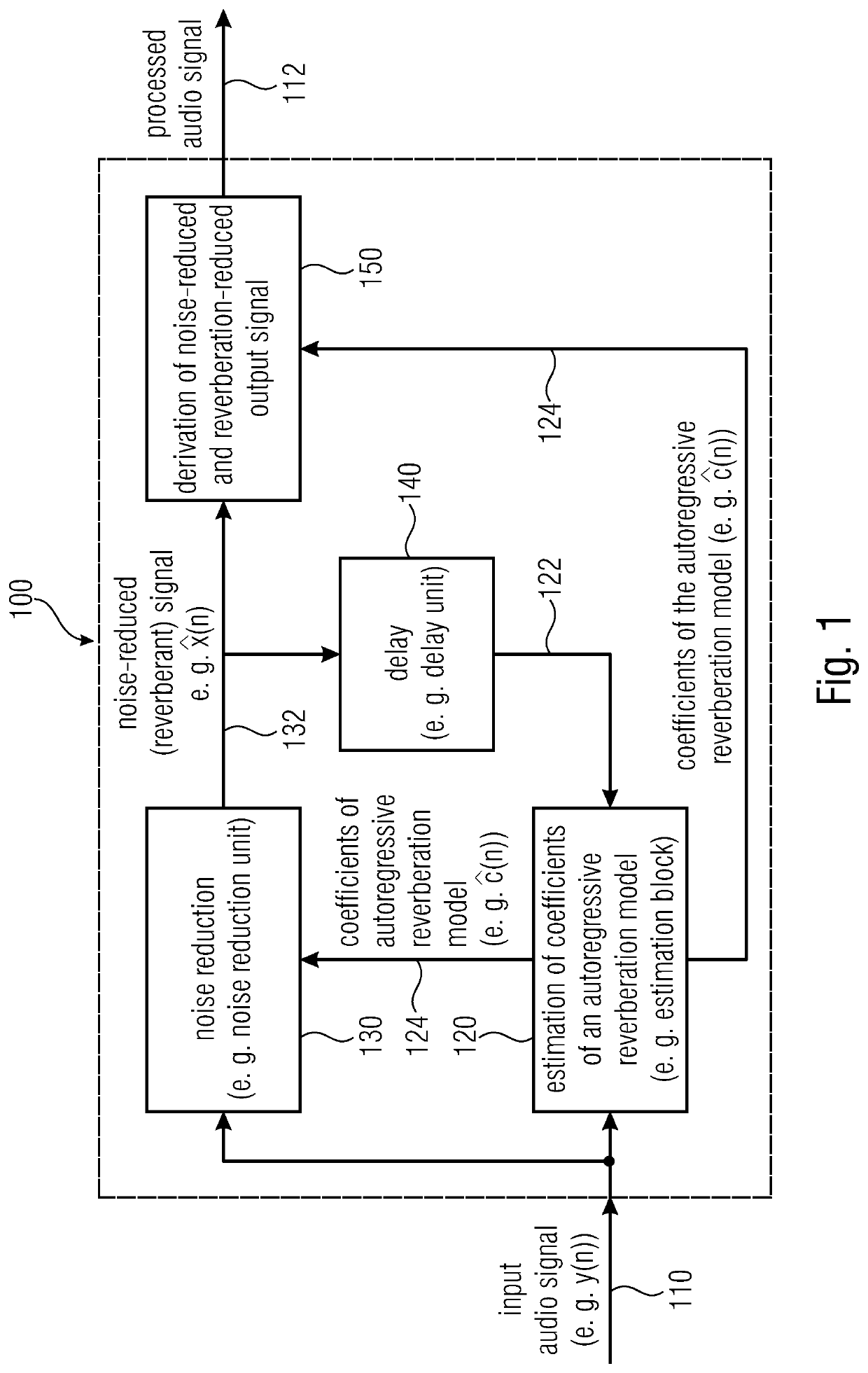

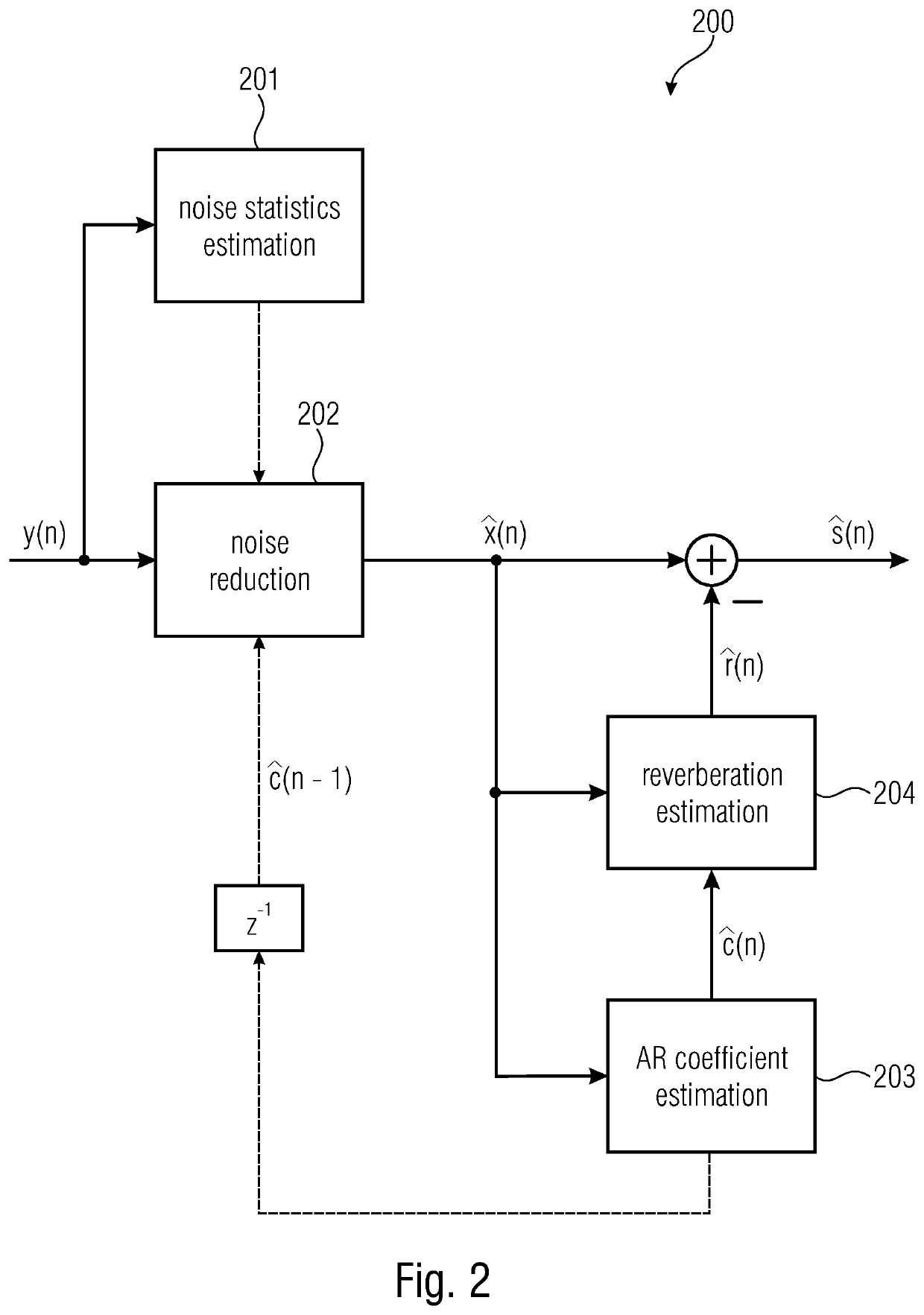

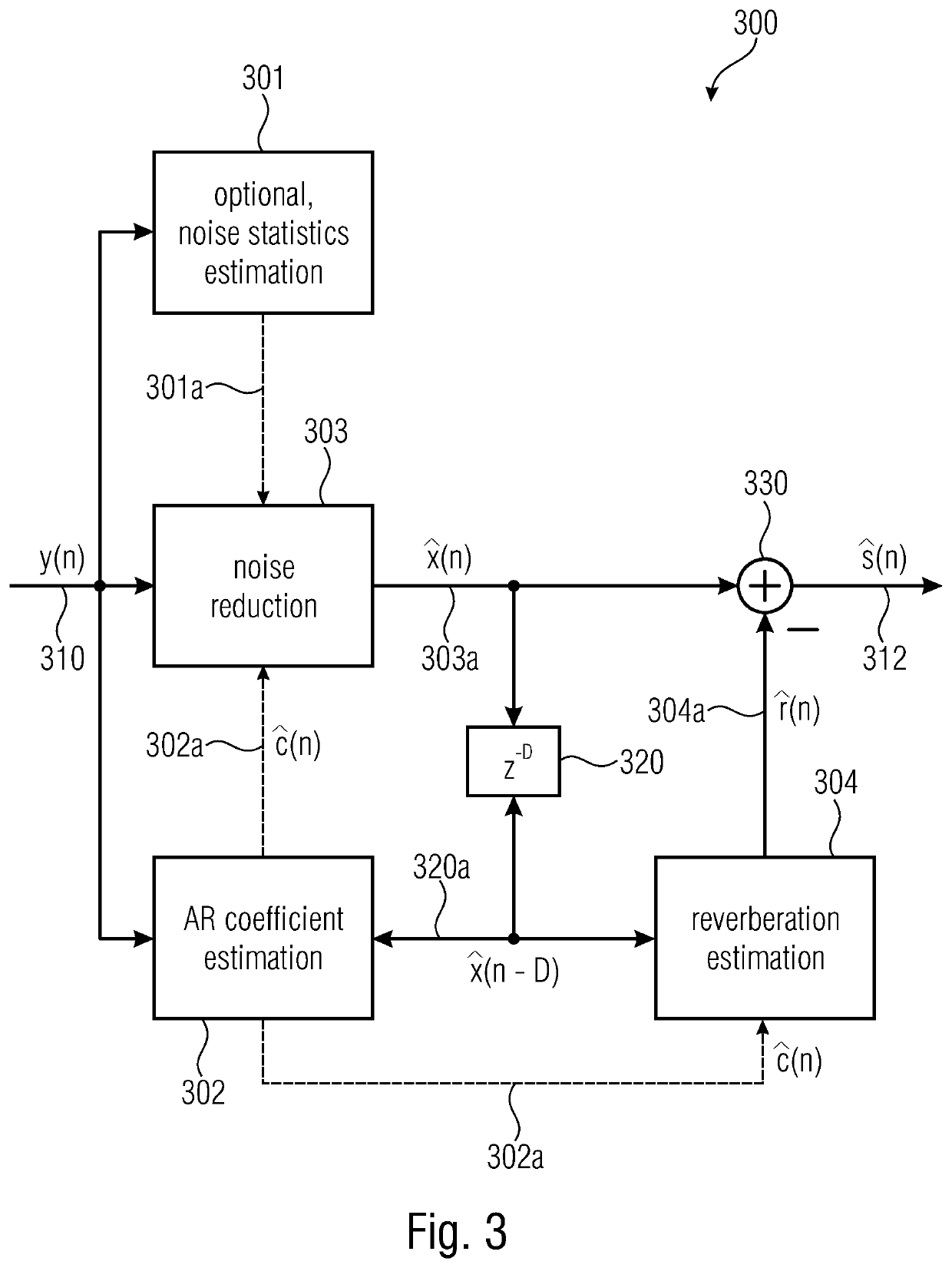

Signal processor and method for providing a processed audio signal reducing noise and reverberation

A signal processor for providing one or more processed audio signals on the basis of one or more input audio signals is configured to estimate coefficients of an autoregressive reverberation model using the input audio signals and the delayed noise-reduced reverberant signals obtained using a noise reduction. The signal processor is configured to provide noise-reduced reverberant signals using the input audio signals and the estimated coefficients of the autoregressive reverberation model. The signal processor is configured to derive noise-reduced and reverberation-reduced output signals using the noise-reduced reverberant signals and the estimated coefficients of the autoregressive reverberation model. A method and a computer program include a similar functionality.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Online control method and system for data center multi-energy under dynamic cloud service request

ActiveCN103297505BMinimize operational overheadLow electricity priceTransmissionData centerSystems management

The invention discloses a multi-energy online control system for data centers under dynamic cloud service requests. The multi-energy online control system for data centers under dynamic cloud service requests comprises a system status monitoring module, a load scheduling module and a multi-source energy supply system management module, wherein the load scheduling module comprises a delay-sensitive request scheduling sub-module and a delay tolerant job scheduling sub-module. The system status monitoring module is used for receiving service requests from a user's cloud service every once in a while, determining whether the cloud service request is a delay-sensitive request or a delay tolerant job, and sending the cloud service request belonging to the delay-sensitive request to the delay-sensitive request scheduling sub-module of the load scheduling module while sending the cloud service request belonging to the delay tolerant job to the delay tolerant job scheduling sub-module of the load scheduling module. The multi-energy online control system for data centers under dynamic cloud service requests has the advantages that long-term operating cost of data center energy supply system can be optimized, no system data is needed to be obtained in advance, and no steady state distribution is needed to be assumed.

Owner:HUAZHONG UNIV OF SCI & TECH