Digital satellite interface bias verification system

A technology of digital interface and verification system, which is applied in the field of verification of the input and output characteristics of satellite digital interfaces, can solve problems such as inability to adjust, cannot set multiple digital signal delay relationships, and cannot grasp the interface tolerance characteristics, etc., to achieve real-time effect of change

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Specific embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

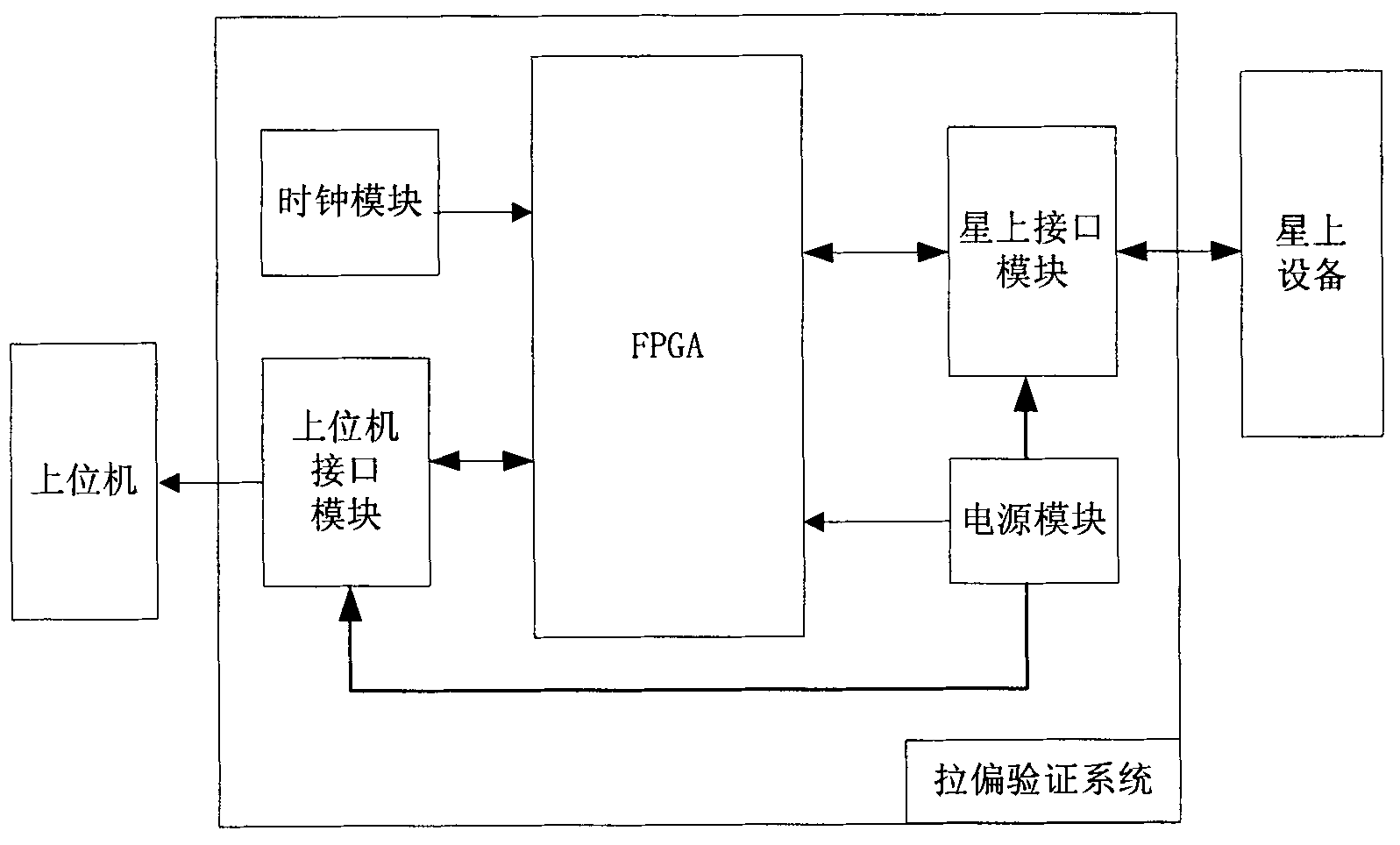

[0030] The invention provides a satellite digital interface deflection verification system, which is used for artificially deflecting signals input to satellite equipment during ground testing, so that the tolerance characteristics of the satellite interface can be tested on the ground. Such as figure 1 Shown is the composition of the system of the present invention, which mainly consists of the following modules: clock module, host computer interface module, FPGA, on-star interface module and power supply module;

[0031] In the present invention, FPGA uses 3.5 million gate chips VERTEX4 of XILINX company TM XC4VSX35, the corresponding configuration FLASH is XCF32PVO48C, the capacity is 32Mbit, and the package is VO48. The configuration mode of FPGA and Flash is the most basic main serial configuration mode, and the clock of FPGA is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More