Counter control type delay-locked loop circuit with mistaken locking correction mechanism

A technology of delay phase-locked loop and counter, applied in automatic control of power, electrical components, etc., can solve problems such as wrong locking, narrow frequency range, indeterminability, etc., achieve multi-phase output, wide frequency range, and solve errors lock effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

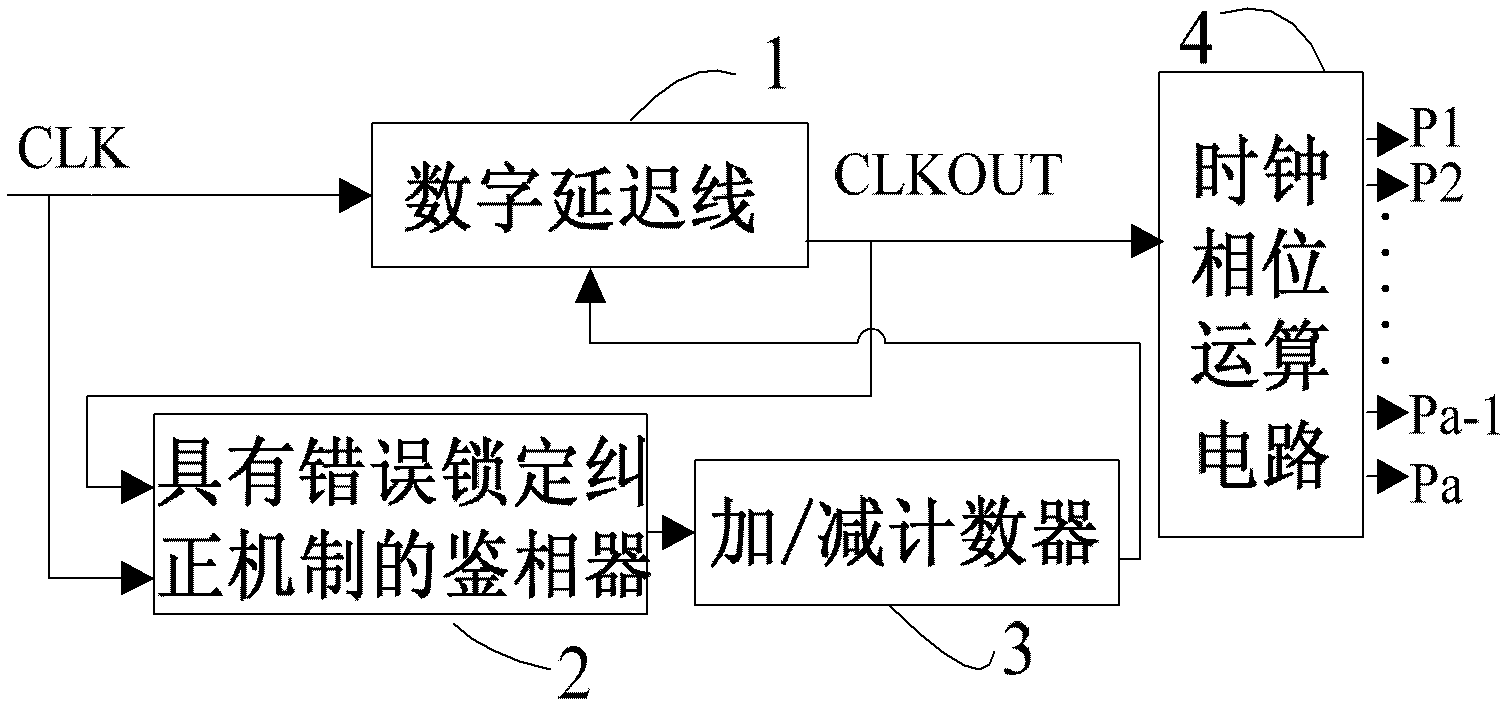

[0027] In order to make the technical features of the present invention more obvious and easy to understand, the present invention will be further described below with reference to the accompanying drawings and embodiments.

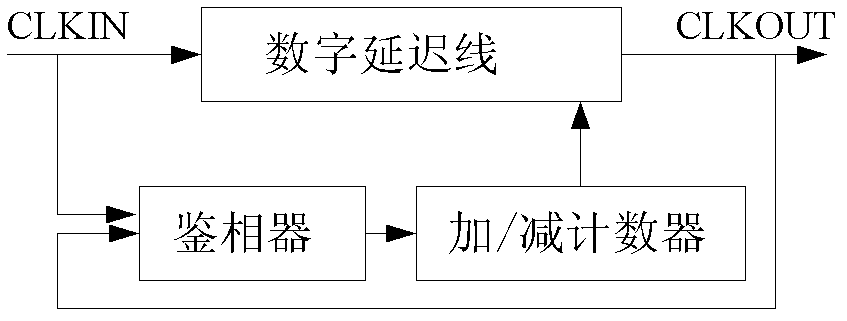

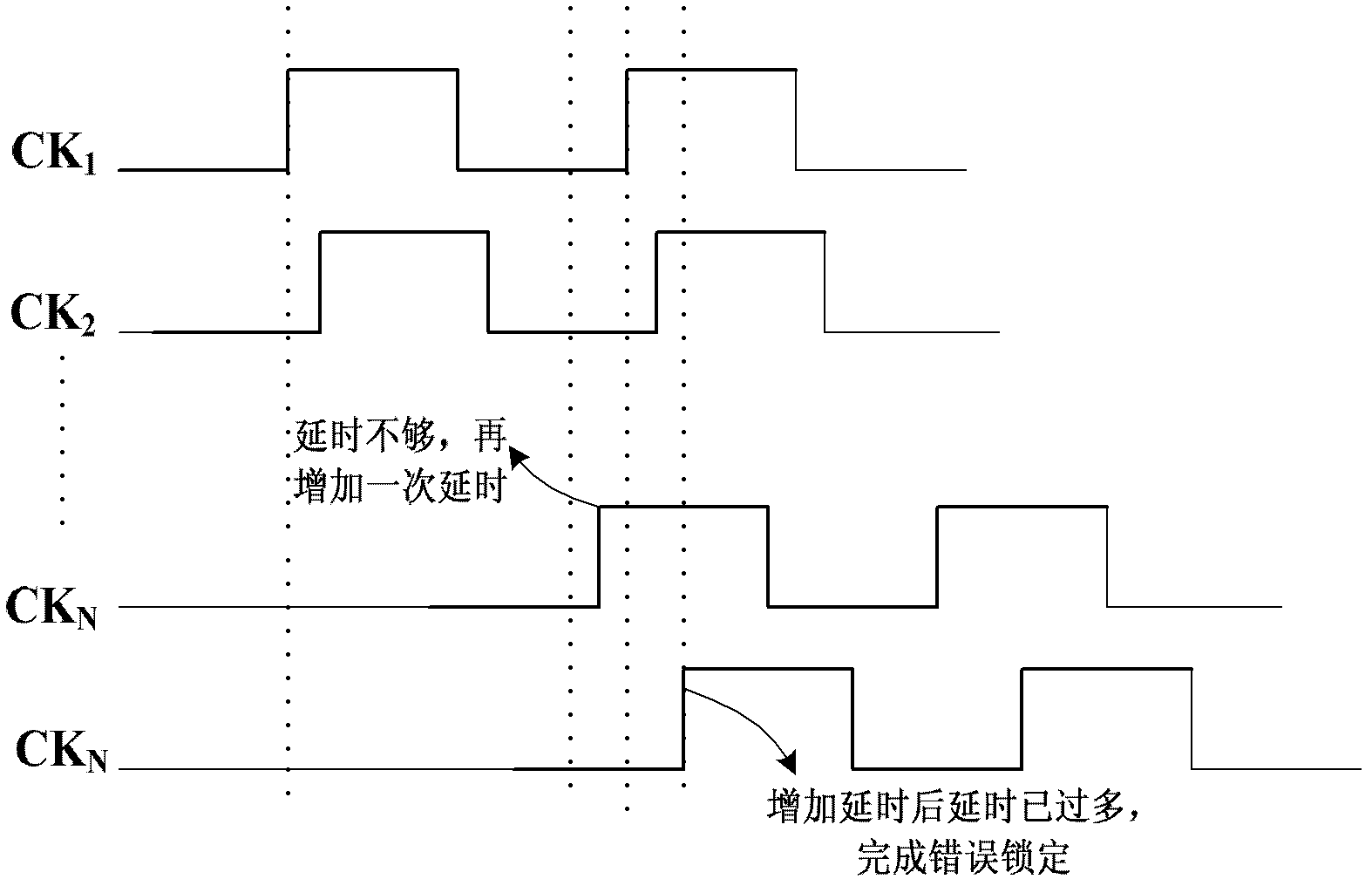

[0028] like image 3 As shown, the structure of the counter-controlled delay-locked loop circuit with an error-locking correction mechanism according to the present invention includes four functional modules: a digital delay line 1, a phase detector 2, an up / down counter 3, and a clock phase operation circuit 4. The digital delay line 1 consists of (n+3) identical delay units, where n is any positive integer, each delay unit is controlled by the output signal of the up / down counter 3, and the phase detector 2 compares the input clock and the delay unit. The phase of the output clock after the time, controls the up / down counter 3 according to the comparison result, and the clock phase operation circuit 4 selects the delay signal output by some delay units...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More