A multi-fpga chip accelerator card

An accelerator card and chip technology, applied in the fields of instruments, electrical digital data processing, etc., can solve the problem of disproportion between power consumption and cost, and achieve the effect of computing acceleration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

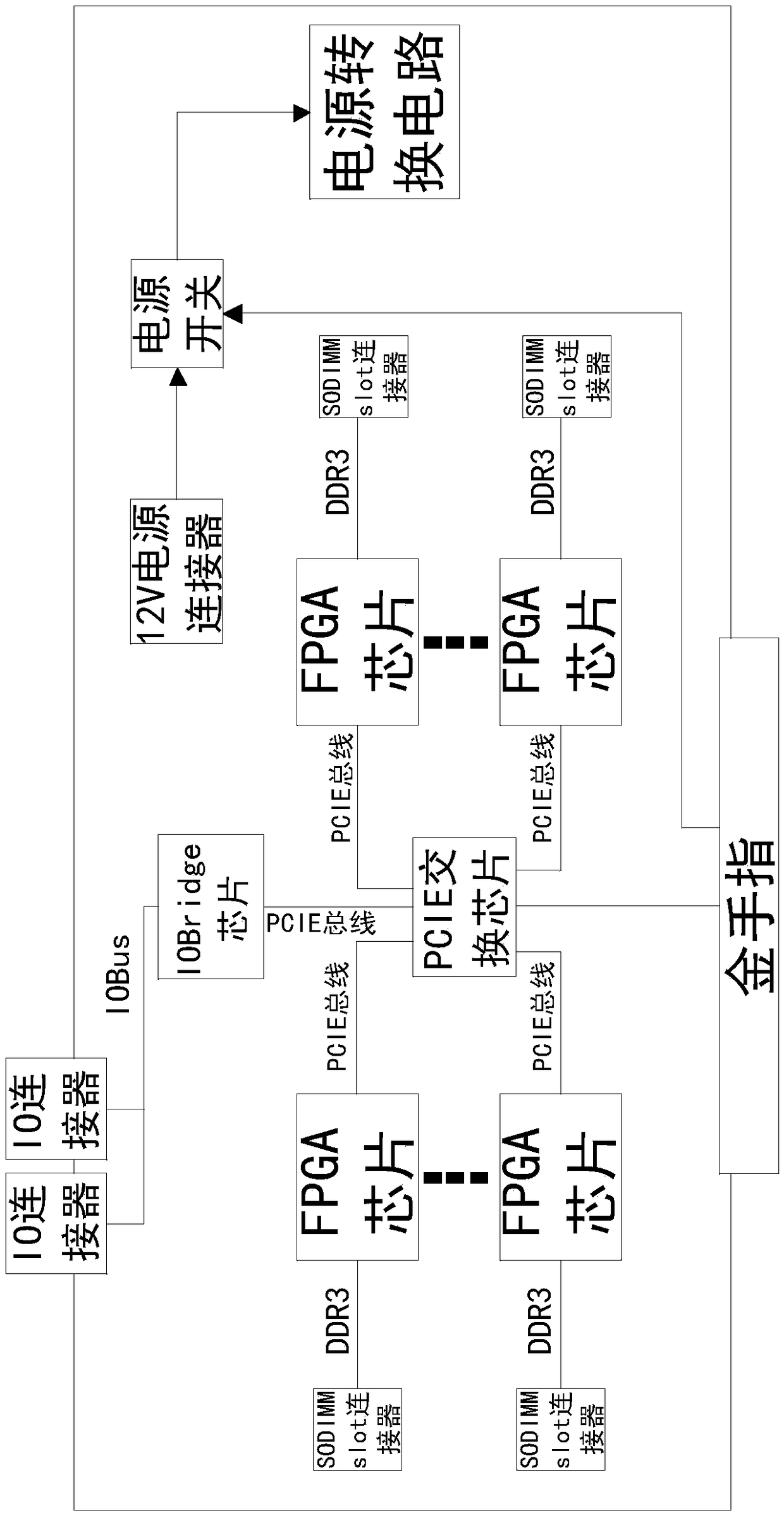

Image

Examples

Embodiment Construction

[0014] In order to make the purpose, technical solution and advantages of the present invention more clear, the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

[0015] The steps shown in the flowcharts of the figures may be performed in a computer system, such as a set of computer-executable instructions. Also, although a logical order is shown in the flowcharts, in some cases the steps shown or described may be performed in an order different from that shown or described herein.

[0016] Aiming at the problem in the existing technology that the increase in computing power in many computing application scenarios is far out of proportion to the increase in power consumption and cost only through the expansion of quantity, the emergenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More