Method for FPGA coarse-grained parallel wiring based on optimal division of netlist position information

A technology of location information and wiring method, applied in the fields of instrumentation, calculation, electrical digital data processing, etc., can solve the problems of wasting time, hindering the use of FPGA, occupying time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

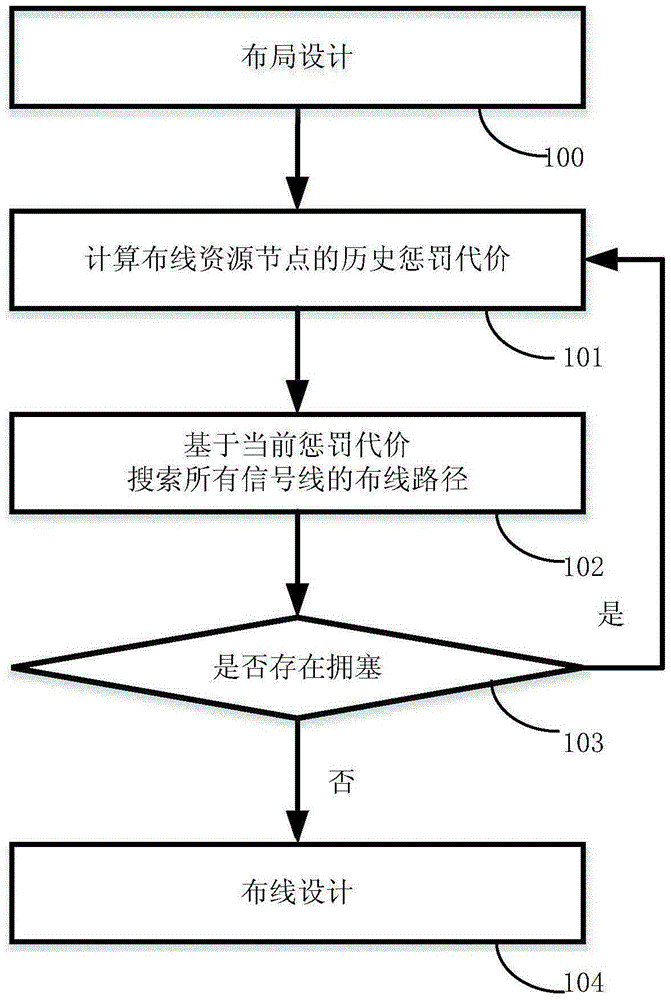

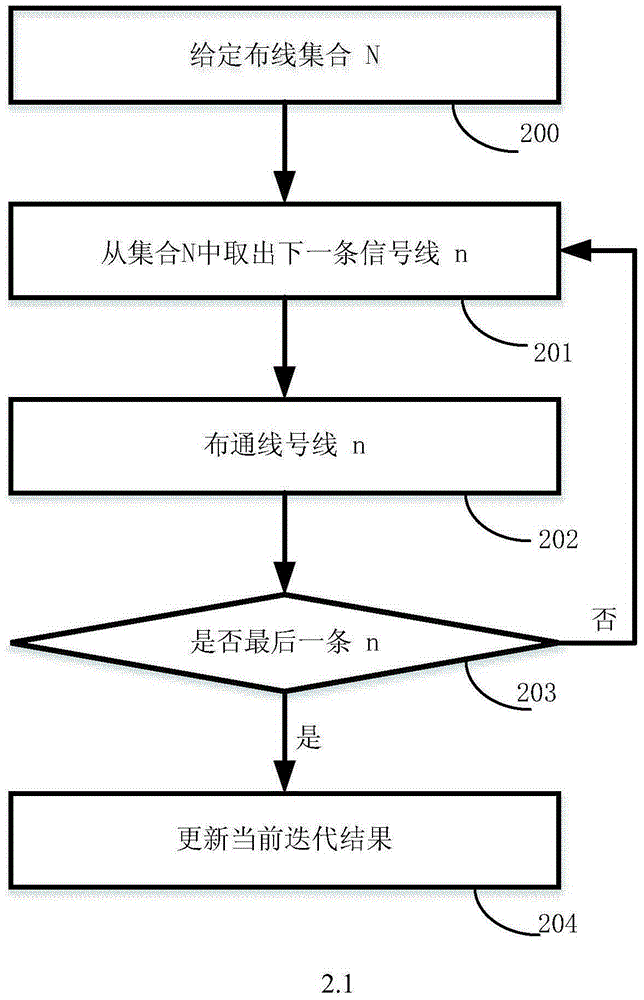

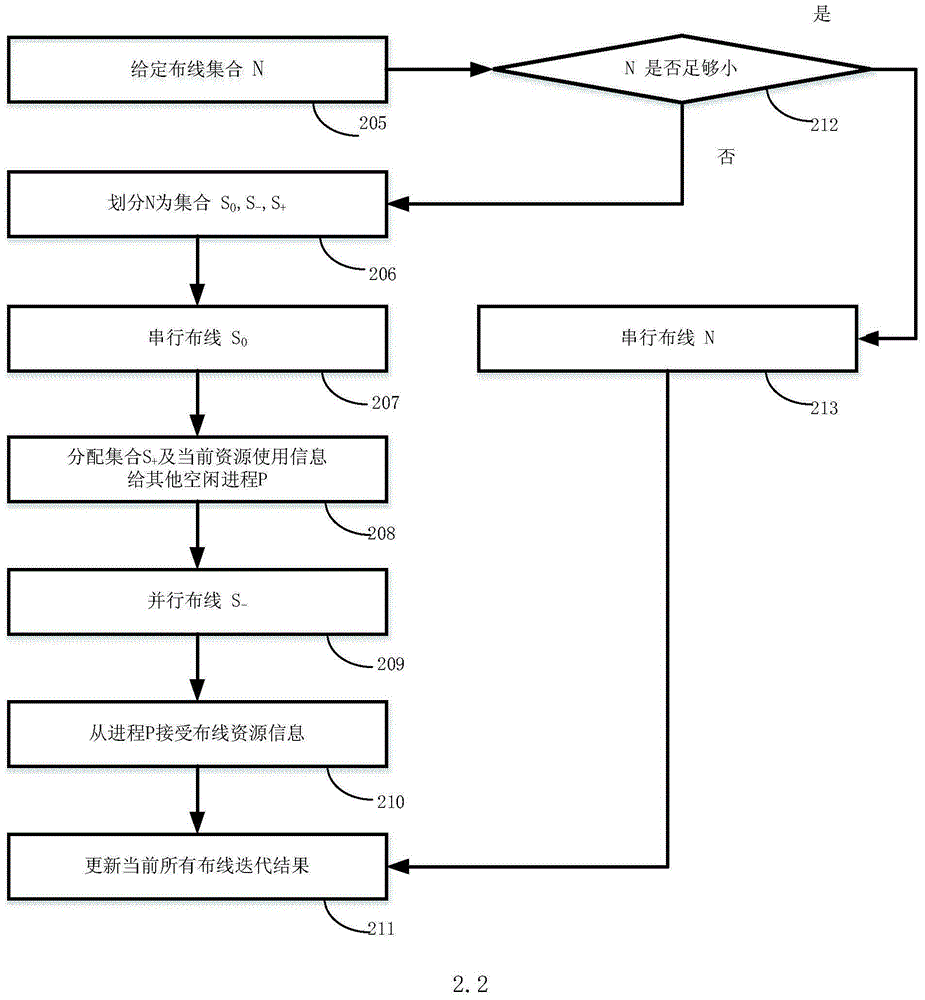

[0056] Below in conjunction with accompanying drawing, further describe the present invention through embodiment, but do not limit the scope of the present invention in any way.

[0057] In the wiring resource diagram abstracted from the wiring resources in the FPGA chip, each signal line that needs to be routed has a source point and one or more sink points; the source point and the sink point are connected by using the wiring resource nodes in the wiring resource diagram point, a routing tree is obtained; all routing work can be completed only when the routing trees of all signal lines are obtained and the routing trees of different signals do not share the same routing resource node. Since the coordinate positions of the source and sink points of such signal lines in the wiring resource diagram are known, the technical solution can classify the signal lines according to the positional relationship between node coordinates and dividing lines.

[0058] Assuming that the divid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More