Flow control type FIFO cache structure and method for uniformly configuring data significant bits

A technology for effective data and configuration registers, applied in electrical digital data processing, instruments, etc., to achieve the effect of reducing auxiliary operation overhead and avoiding overflow errors

Active Publication Date: 2019-08-30

XIAN MICROELECTRONICS TECH INST

View PDF6 Cites 8 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

[0005] The purpose of the present invention is to provide a flow-controlled FIFO cache structure and method in which data valid bits are uniformly configured to solve the problems existing in the existing FIFO structure. The present invention can improve the data transmission efficiency of the host interface and reduce The overhead of data integration, and the design of hardware-managed flow control mode to avoid FIFO overflow

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

[0056] The present invention is applied to the design of I2C serial bus controllers of multiple SoC chips. These SoCs adopt the host control interface of 32-bit SPARC V8 processor, so the FIFO storage bit width in the I2C bus controller is also 32 bits. By using the content of the invention, the data transmission efficiency between the I2C module and the host SPARC V8 processor is obviously improved, and no I2C FIFO overflow error occurs, thereby improving application reliability.

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

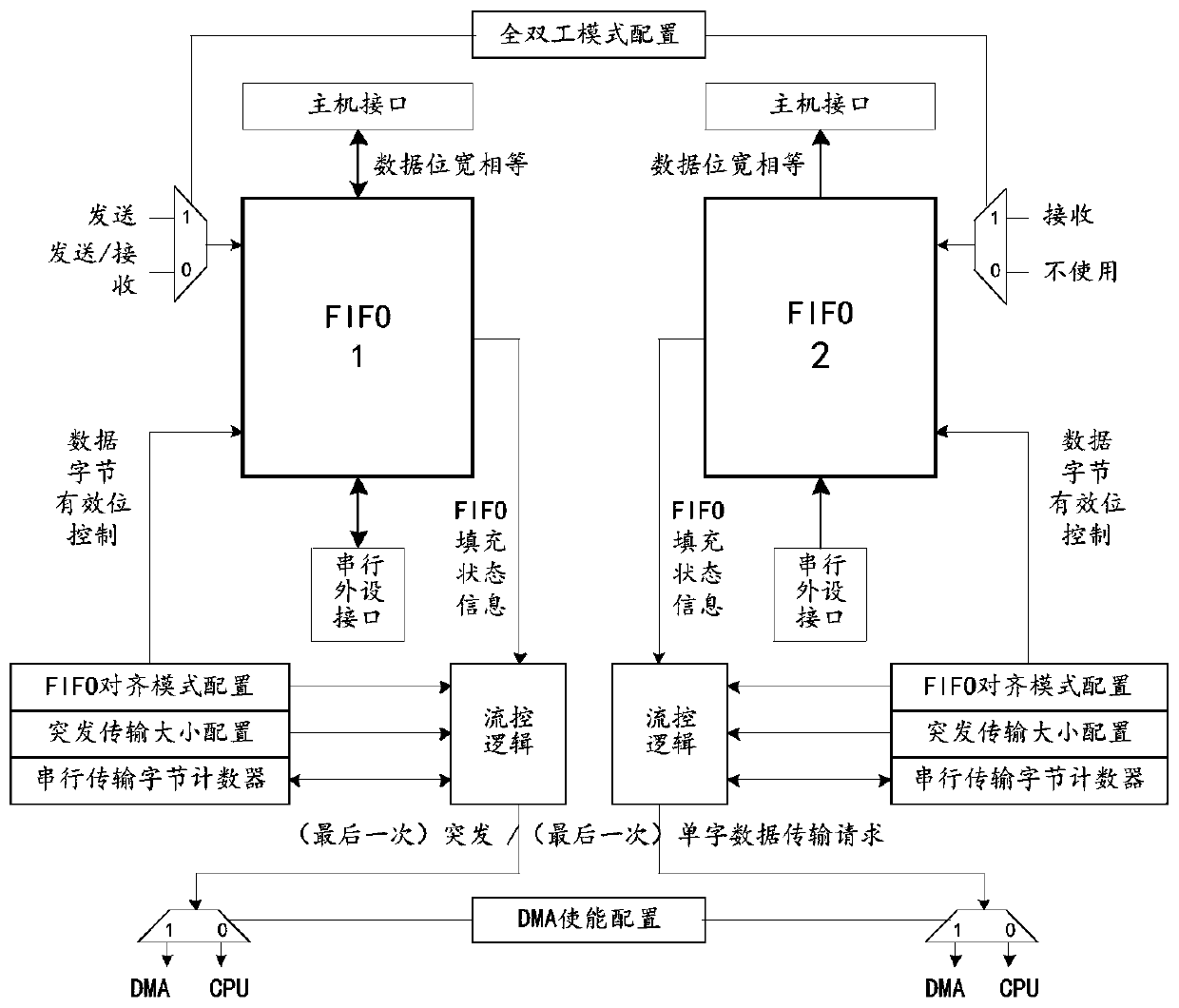

The invention discloses a flow control type FIFO cache structure and method for uniformly configuring the data significant bits, and the structure comprises a first FIFO and a second FIFO, and the first FIFO and the second FIFO are jointly connected to a full-duplex mode configuration register which is used for selecting a full-duplex mode or a half-duplex mode. According to the invention, the data transmission efficiency with a host interface can be improved, the overhead of data integration through software is reduced, and the flow control mode of hardware management is designed, so that theoverflow phenomenon of FIFO is avoided.

Description

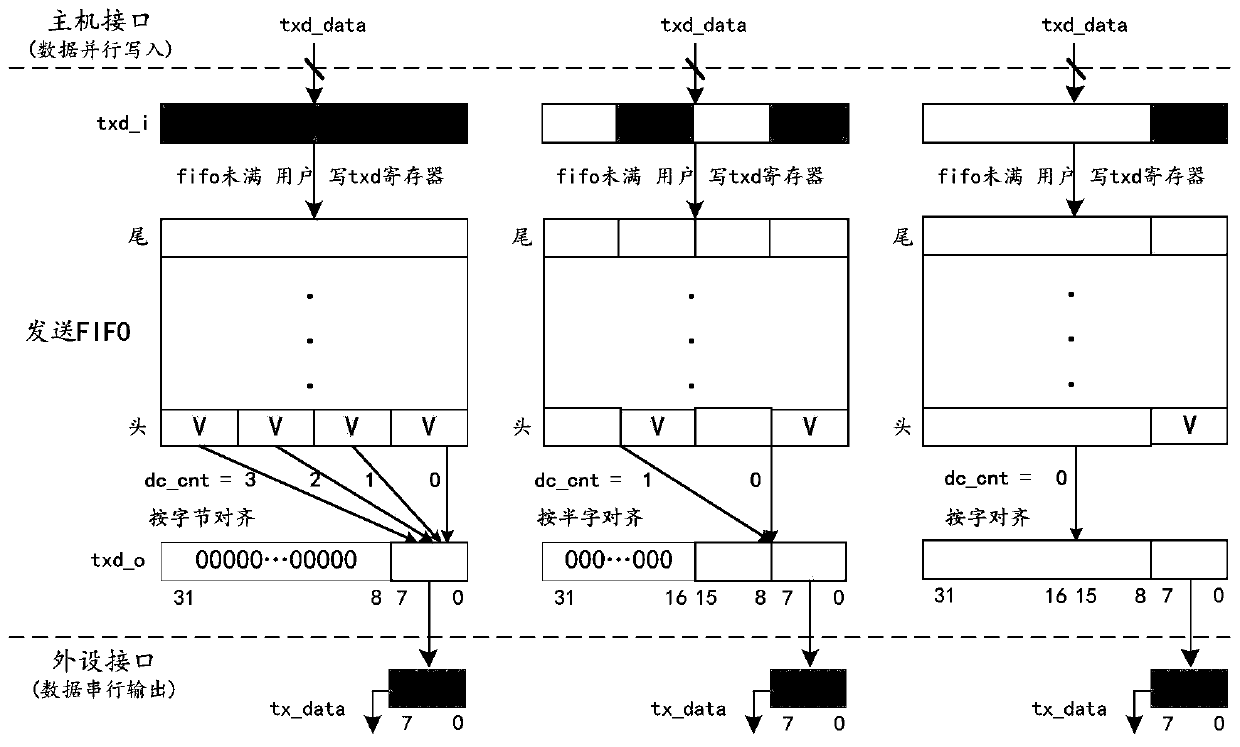

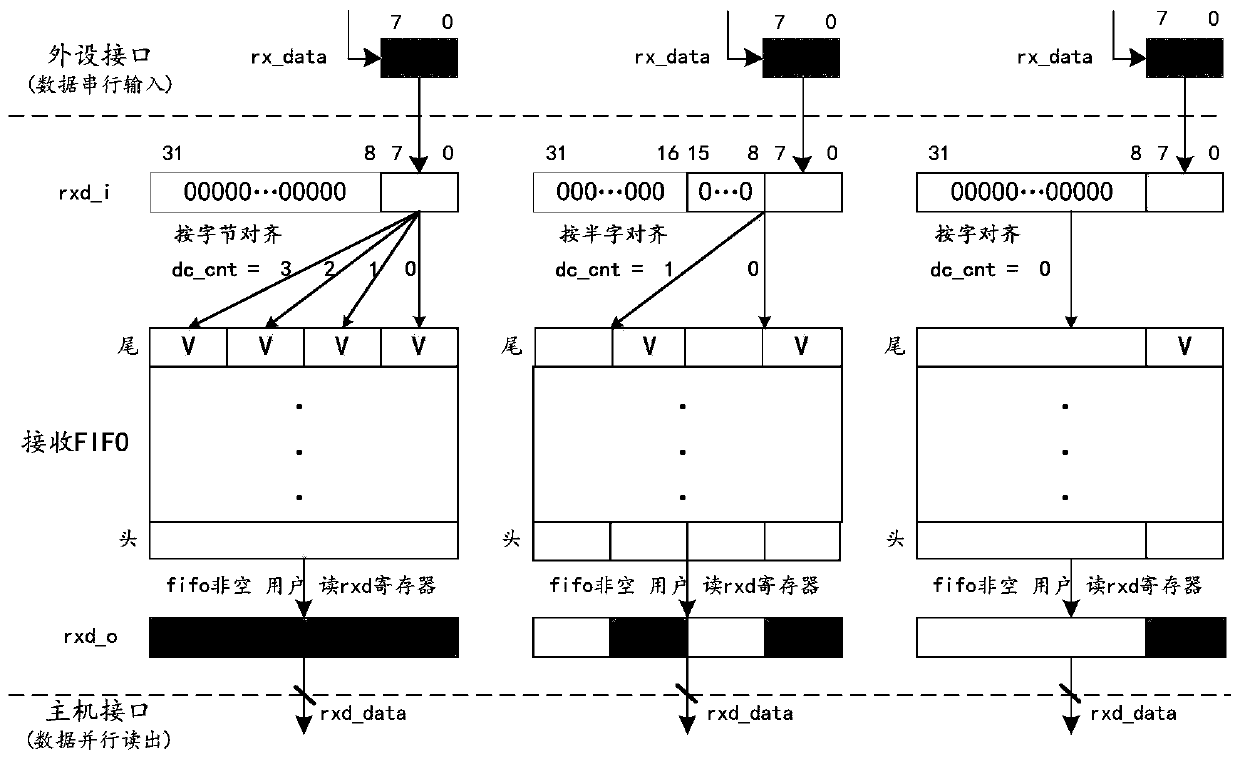

technical field [0001] The invention relates to the field of serial communication control, in particular to a flow control type FIFO buffer structure and method with uniform configuration of valid bits of data. Background technique [0002] In the field of serial communication control, FIFO is a ubiquitous basic structure used to cache parallel data interacted with the host. According to the actual application situation, the current FIFO bit width mainly has two forms: (1) The FIFO storage width is a standard eight-bit data byte. Under this structure, when the host performs a parallel data transmission, only one byte of data is valid, so the data transmission efficiency is low. For example, when the parallel data bit width of the host is 32 bits, only 8 bits of data are associated with the FIFO for each transmission, and the other 24 bits of data are wasted. Even if the host wants to send a 32-bit data, it still needs to perform Four transfers. (2) The FIFO storage width ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G06F13/42G06F13/28G06F13/16

CPCG06F13/1673G06F13/28G06F13/4282

Inventor 肖建青刘思源杨靓张海金贾一鸣

Owner XIAN MICROELECTRONICS TECH INST