Method for suppressing common-mode voltage in SVPWM (Space Vector Pulse Width Modulation) modulation of three-phase two-level inverter

A technology for suppressing common mode and inverters, which is used in motor generator control, control of electromechanical brakes, and AC motor control. High-order harmonics, easy to program, and small computational effort

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

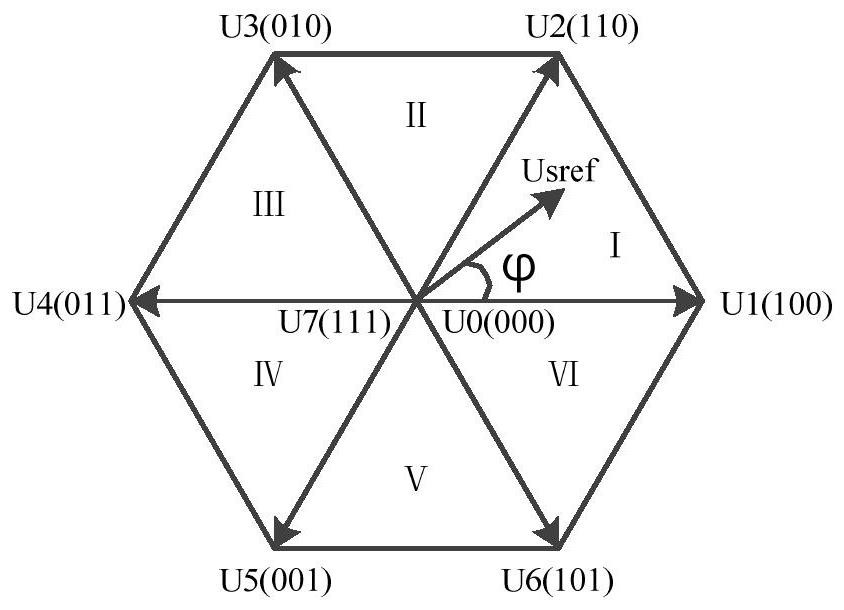

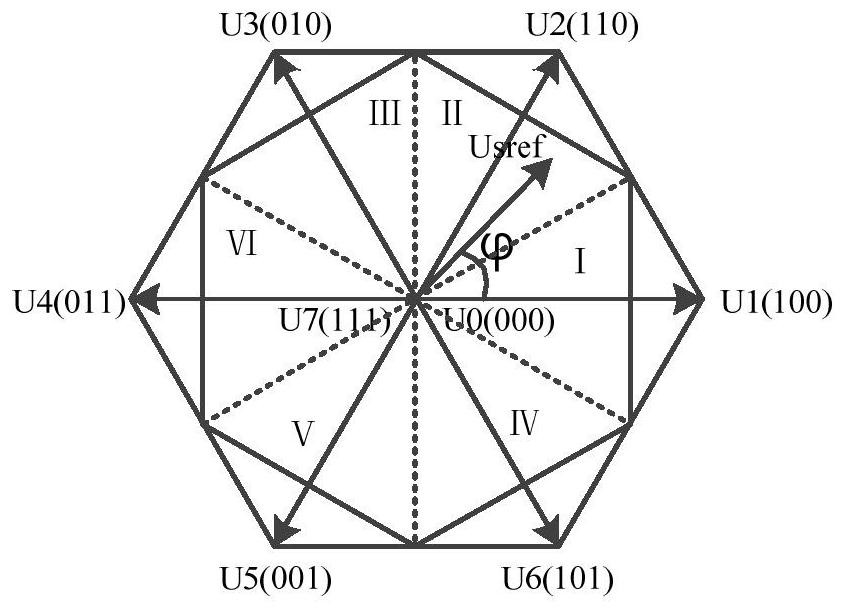

[0037] Such as Figure 1-4 As shown, the method and device for suppressing the common mode voltage in the SVPWM modulation of the three-phase two-level inverter of the present invention include the following steps:

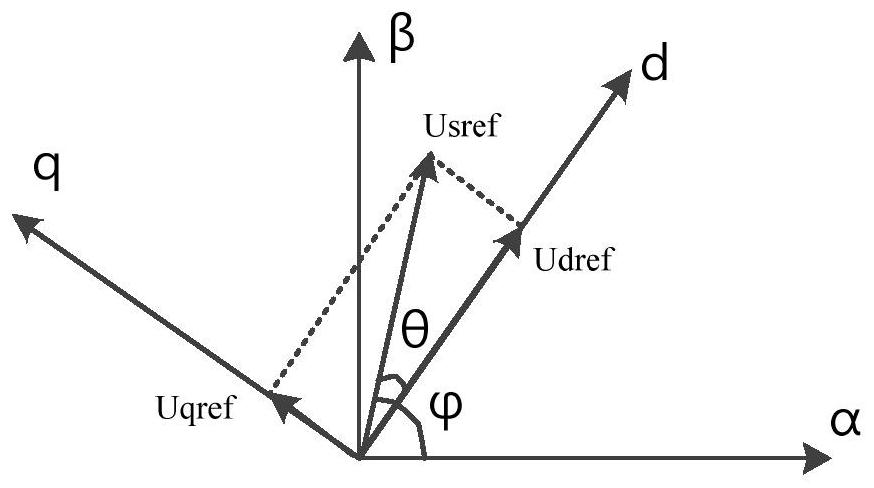

[0038] Step 1. Obtain the desired d-q axis voltage Udref and Uqref through the current loop, and obtain the angle θ between the d-axis and the α-axis through the motor position or speed sensor (this angle can also be achieved through the position sensorless algorithm or the speed sensorless speed get);

[0039] Step 2. Calculate the desired reference voltage vector amplitude Usref, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More