Patents

Literature

30results about How to "Eliminate common mode voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

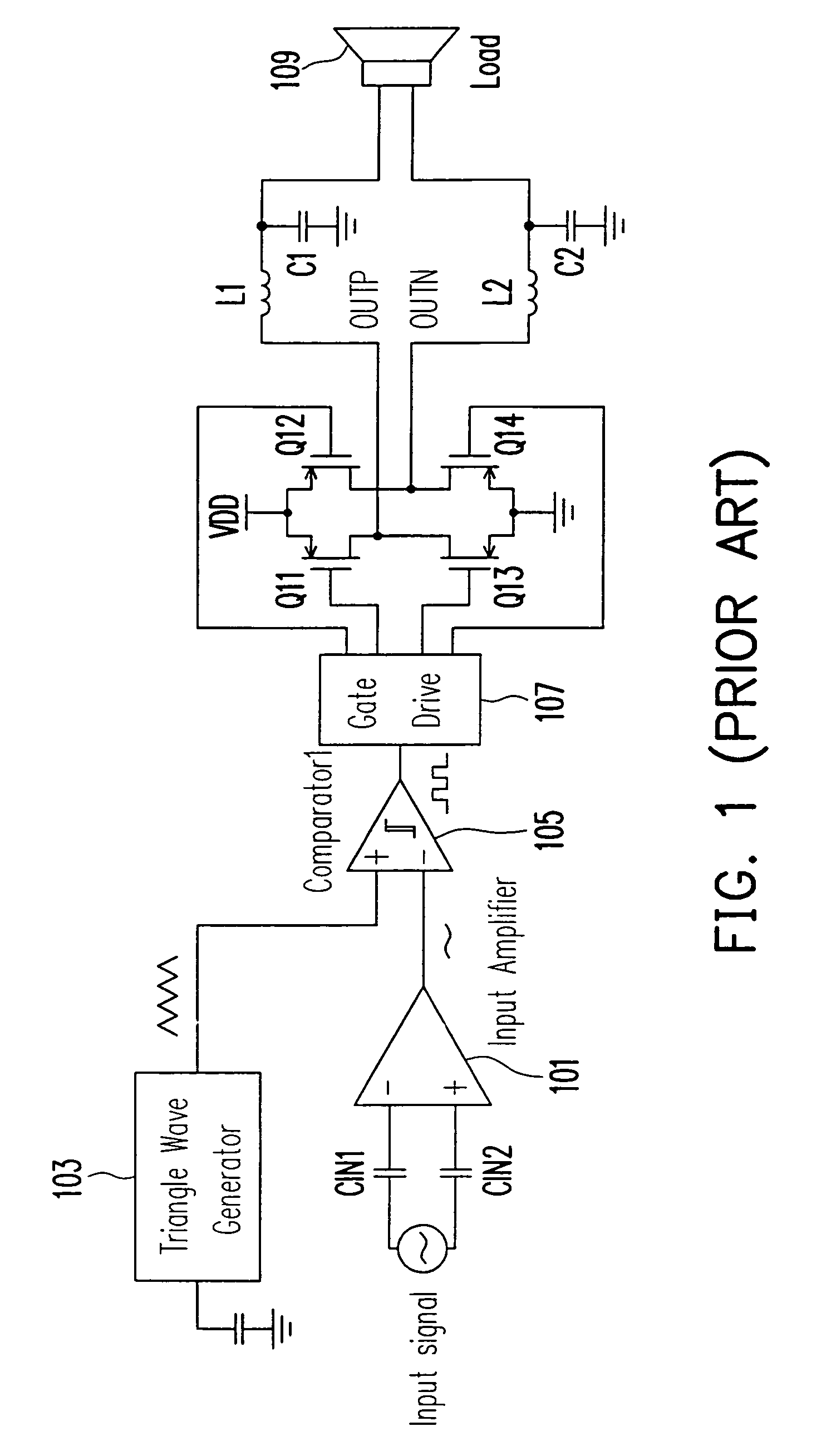

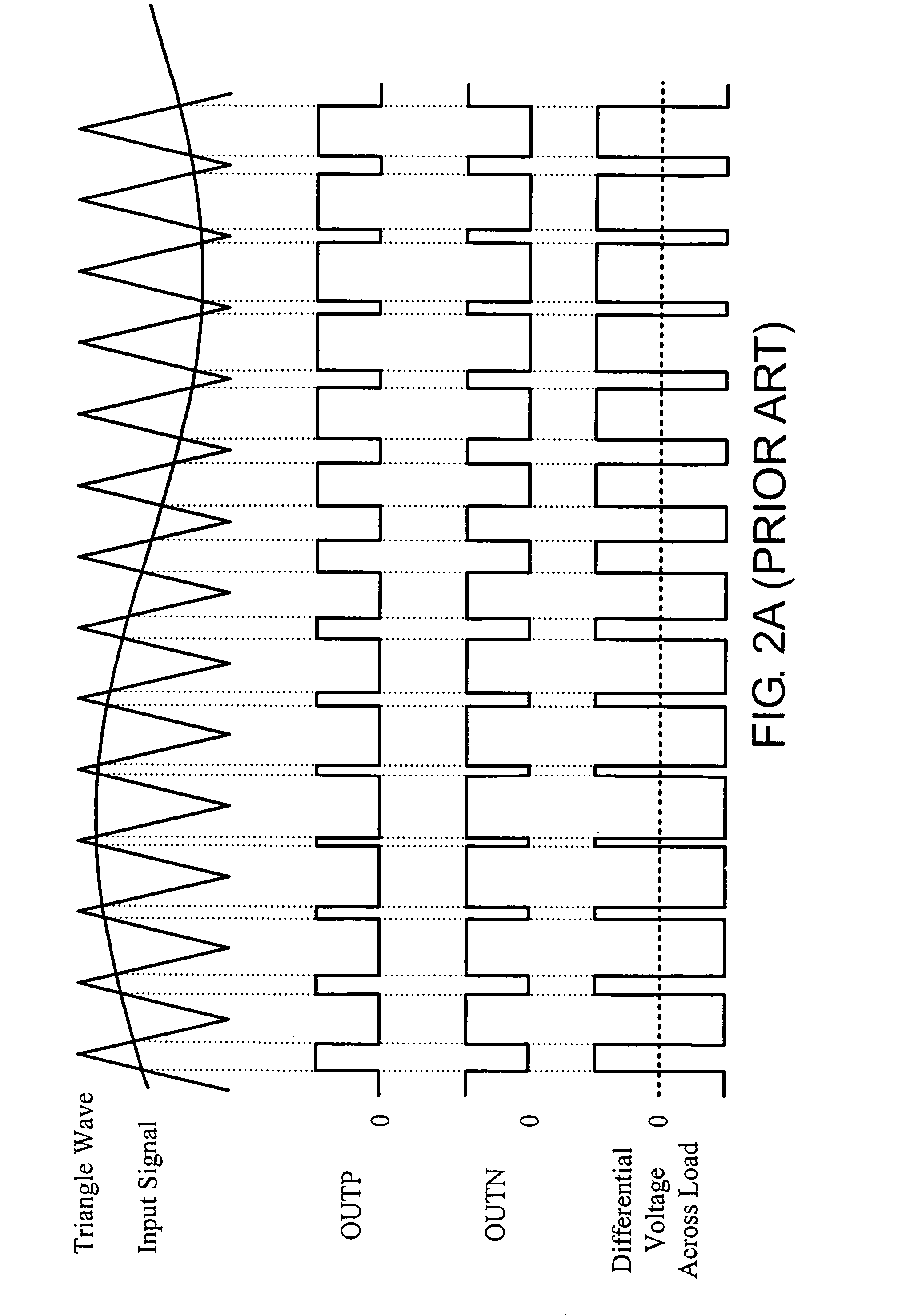

Filterless class D power amplifier

InactiveUS20070146069A1Reduce decreaseEliminate common mode noisePulse duration/width modulationDc amplifiers with modulator-demodulatorAudio power amplifierEngineering

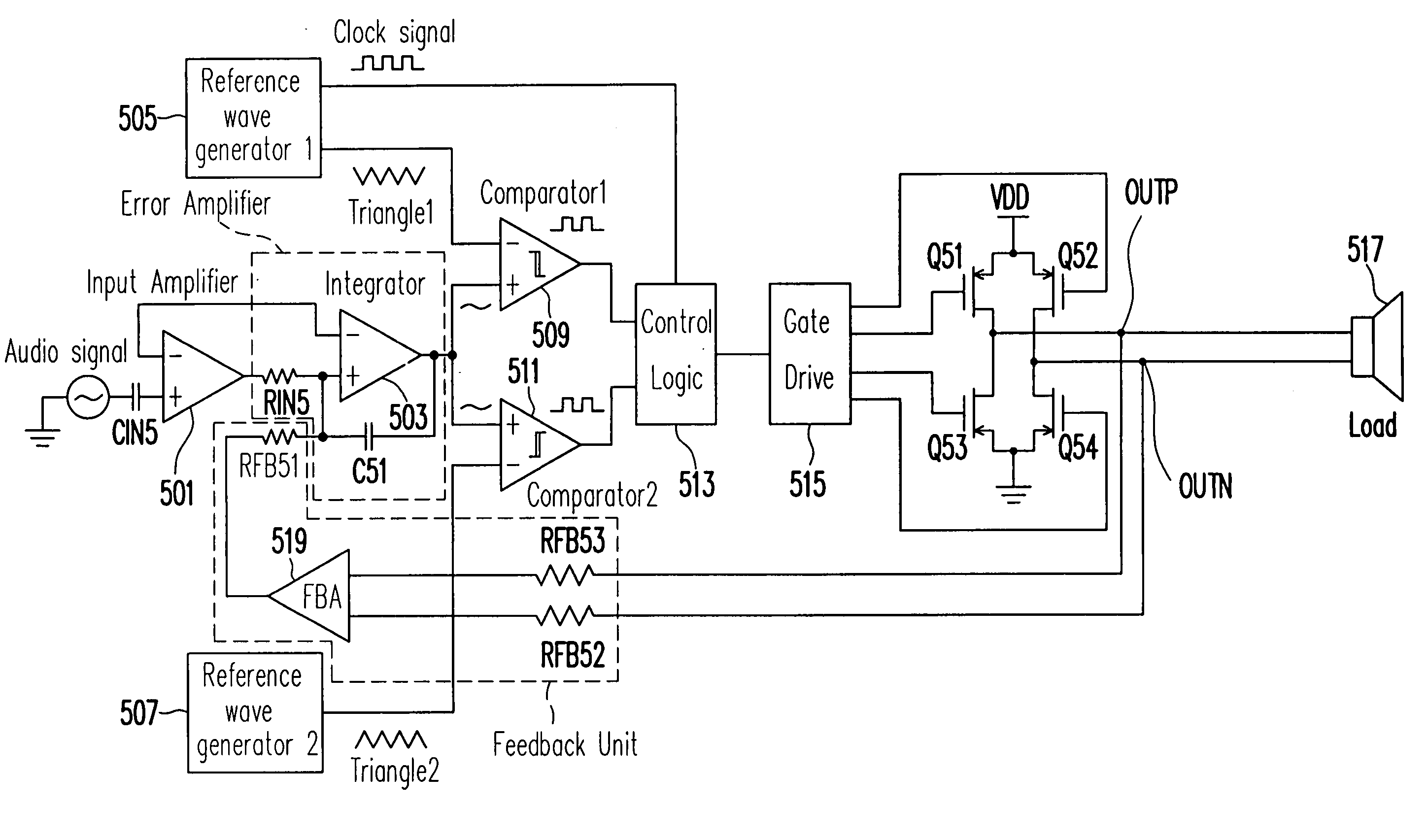

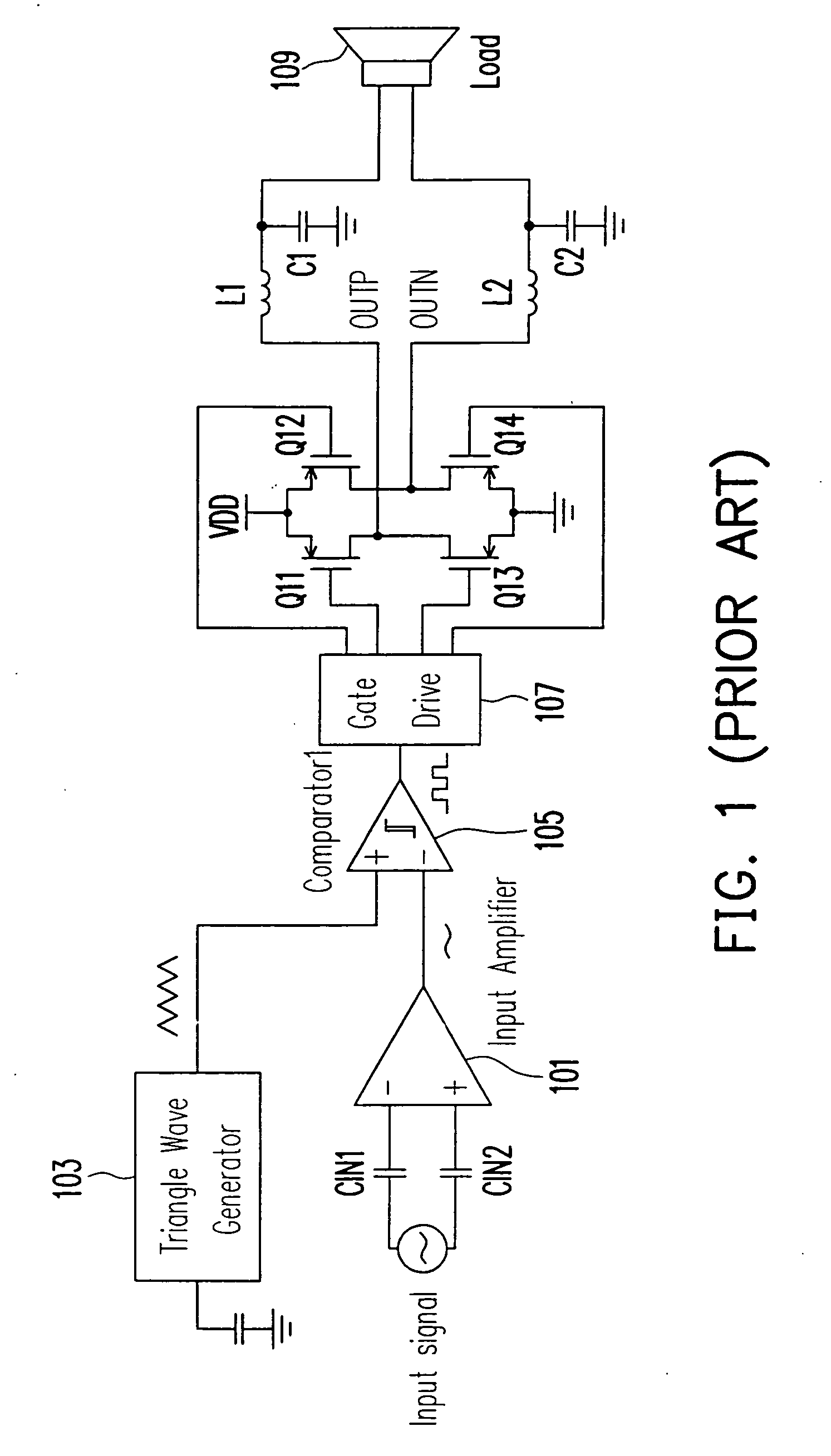

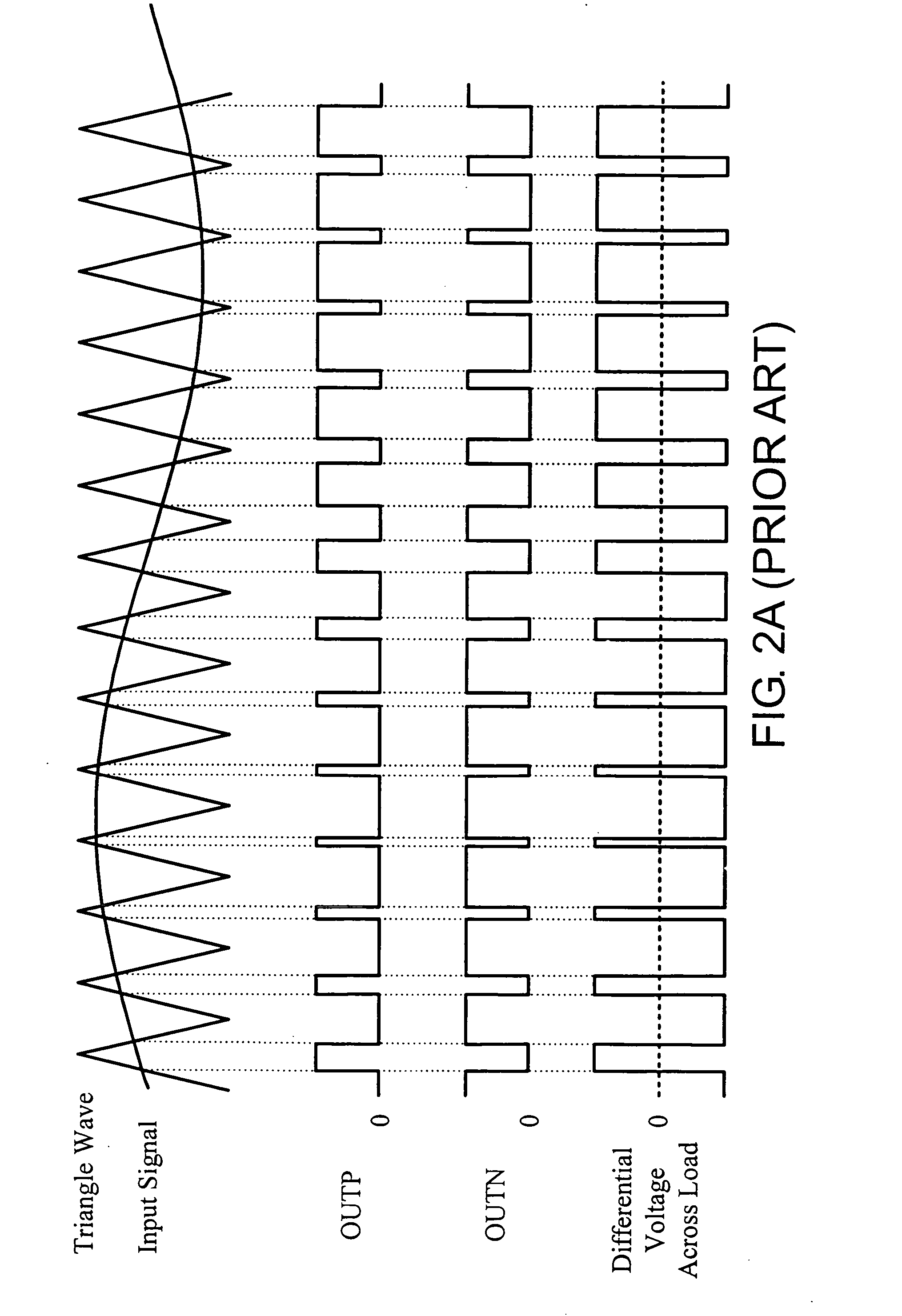

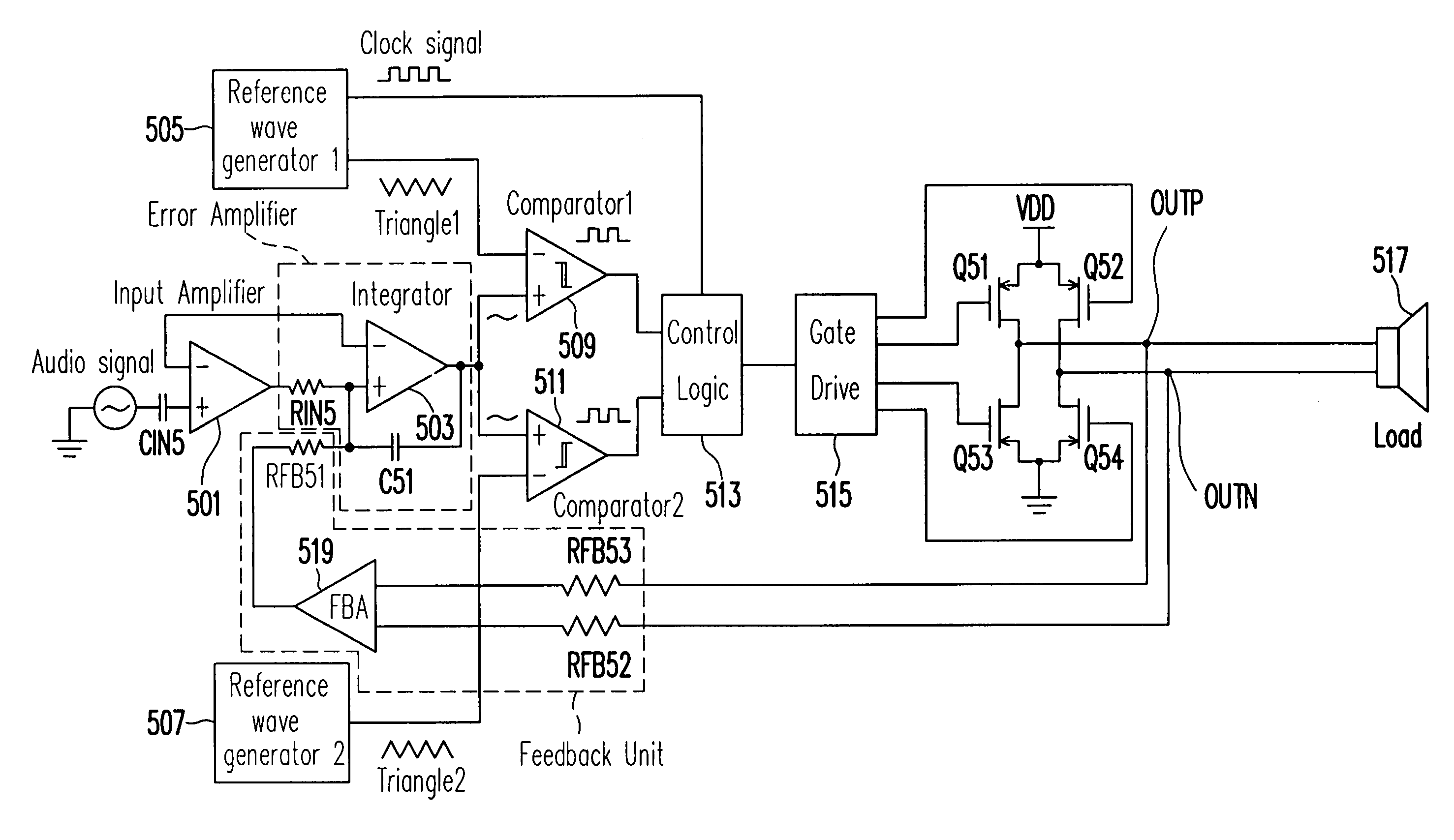

A double reference wave modulation scheme for filterless power amplifiers is disclosed for reducing EMI and common mode voltages. In the filterless power amplifier, differential outputs for driving load impedance are feedback and corrected based on input audio signals. Reference wave generators generate reference waves. A control logic results pulses in the pair of differential outputs in response to a clock signal or a reference voltage and a cross relationship between the input audio signal and the first and second reference waves. Pulses of one of the differential outputs are not overlapped with pulses of the other of the differential outputs for eliminating common mode noises of the power amplifier.

Owner:AMAZION ELECTRONICS NC

Filterless class D power amplifier

InactiveUS7332962B2Improve sound qualityReduce common mode noiseNegative-feedback-circuit arrangementsAmplifier modifications to raise efficiencyAudio power amplifierEngineering

A double reference wave modulation scheme for filterless power amplifiers is disclosed for reducing EMI and common mode voltages. In the filterless power amplifier, differential outputs for driving load impedance are feedback and corrected based on input audio signals. Reference wave generators generate reference waves. A control logic results pulses in the pair of differential outputs in response to a clock signal or a reference voltage and a cross relationship between the input audio signal and the first and second reference waves. Pulses of one of the differential outputs are not overlapped with pulses of the other of the differential outputs for eliminating common mode noises of the power amplifier.

Owner:AMAZION ELECTRONICS NC

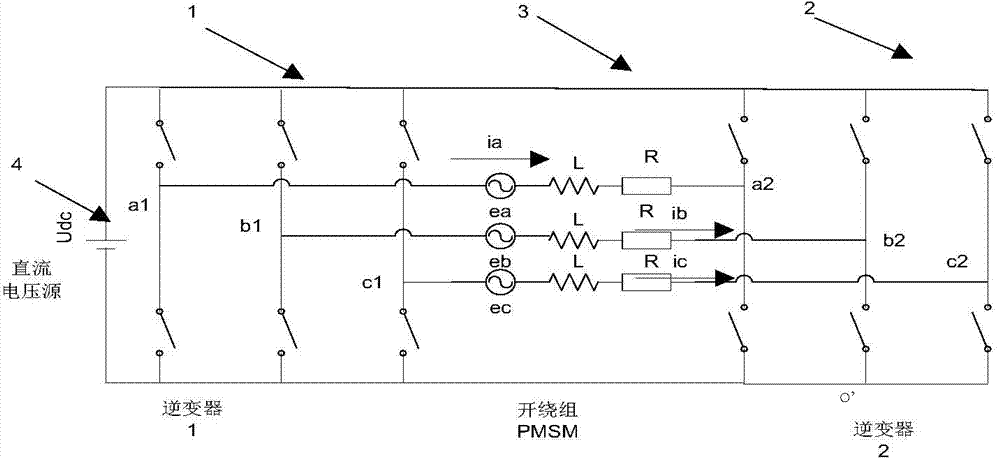

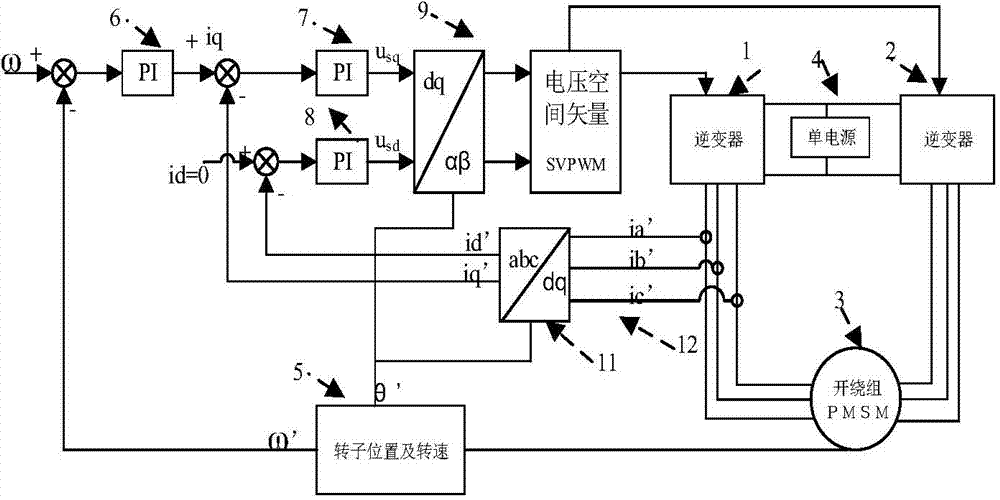

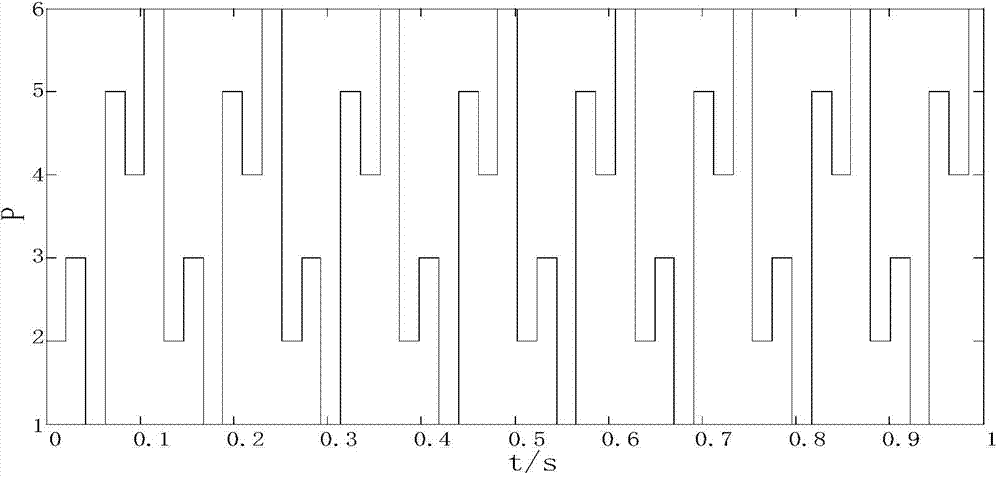

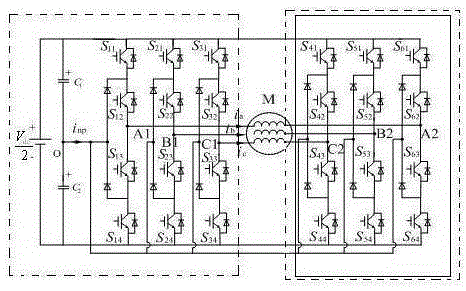

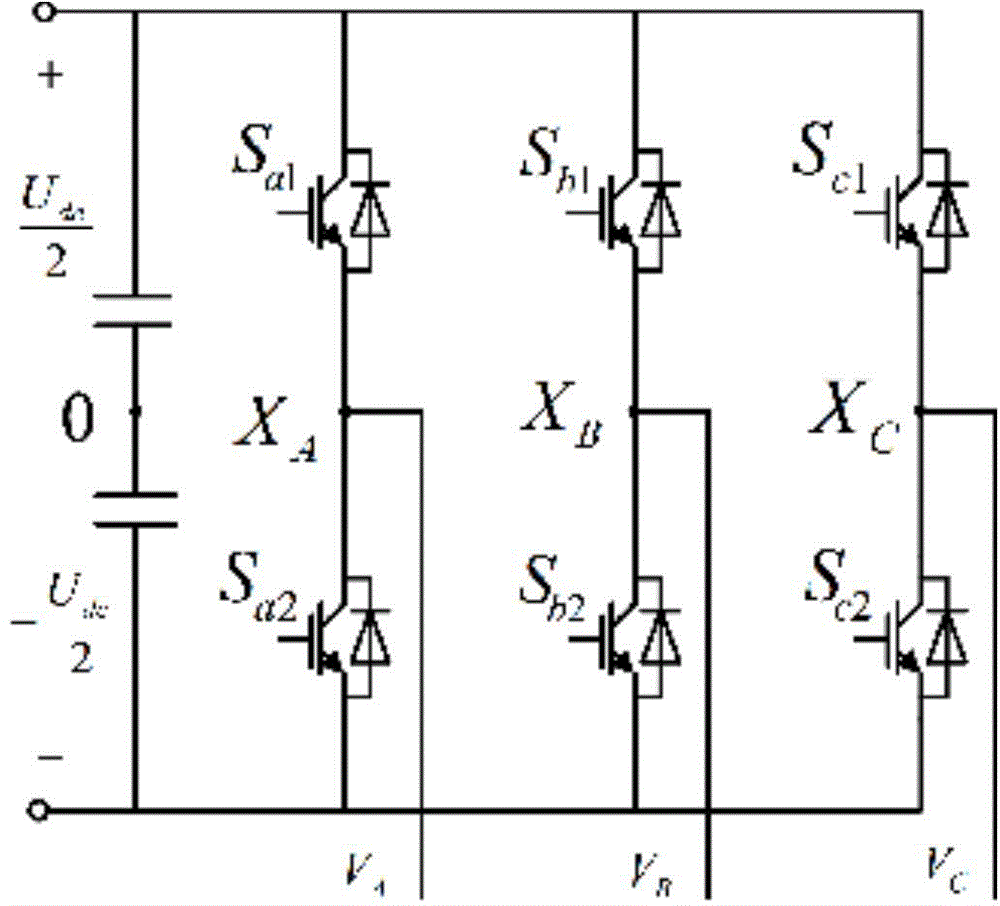

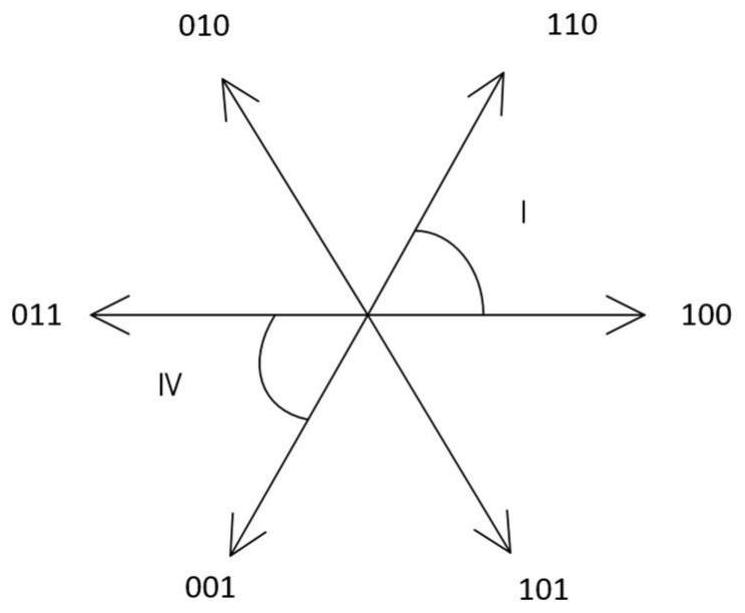

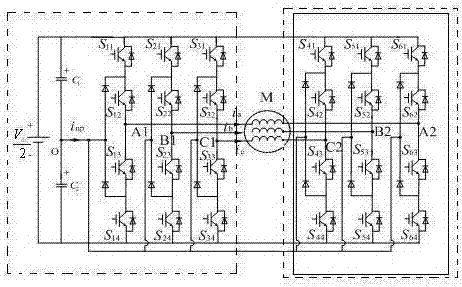

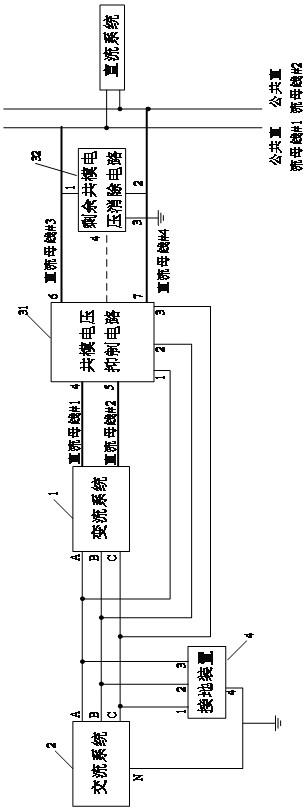

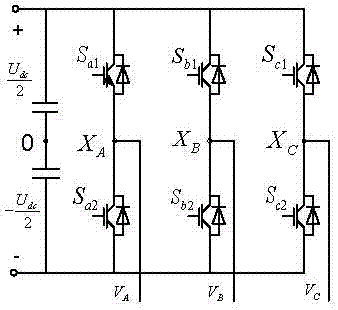

Electromobile driving system vector control method using double inverters

InactiveCN104753430AEasy to controlEliminate common mode voltageElectronic commutation motor controlVector control systemsStator voltageSynchronous motor

The invention discloses an electromobile driving system vector control method using double inverters. The electromobile driving system vector control method includes the following steps: collecting three-phase stator current, rotor position and rotating speed in an unwinding permanent magnetic synchronous motor, wherein the three-phase current is subjected to 3S / 2R conversion to acquire current under a two-phase rotating coordinate system. A system adopts the vector control method with id equal to 0, a stator voltage instruction under the two-phase rotating coordinate system is acquired through double closed-ring control of a rotating speed outer ring and a current inner ring, stator voltage under the two-phase static coordinate system is acquired through 2R / 2S coordinate conversion, control pulse of the double inverters is acquired through a single-power-source double-inverter SVPWM (space vector pulse width modulation) module, and switch devices of the double inverters are triggered to realize vector control of double-inverter SVPWM of the unwinding permanent magnetic synchronous motor. The electromobile driving system vector control method has the advantages that the unwinding permanent magnetic synchronous motor is quick to start, high in overload capability and good in speed adjusting performance; due to the single-power-source double-inverter SVPWM, voltage level of the system is increased, and safety and reliability of the system are guaranteed.

Owner:SOUTHEAST UNIV

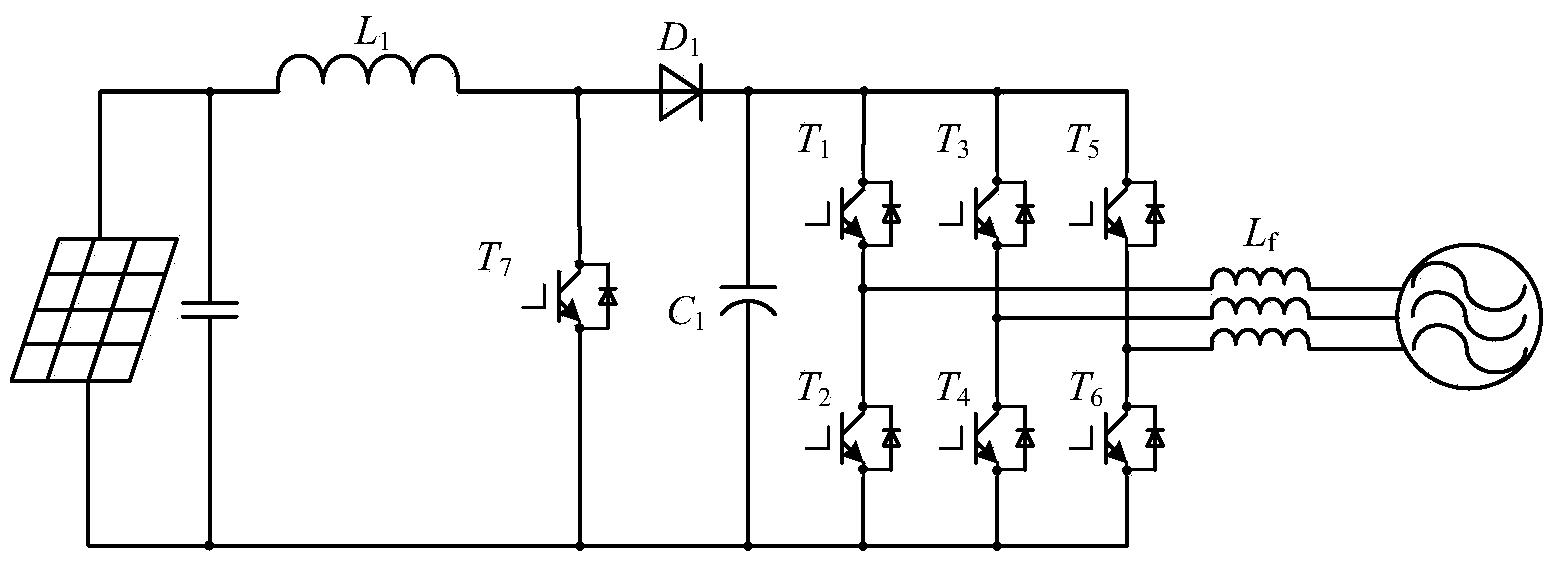

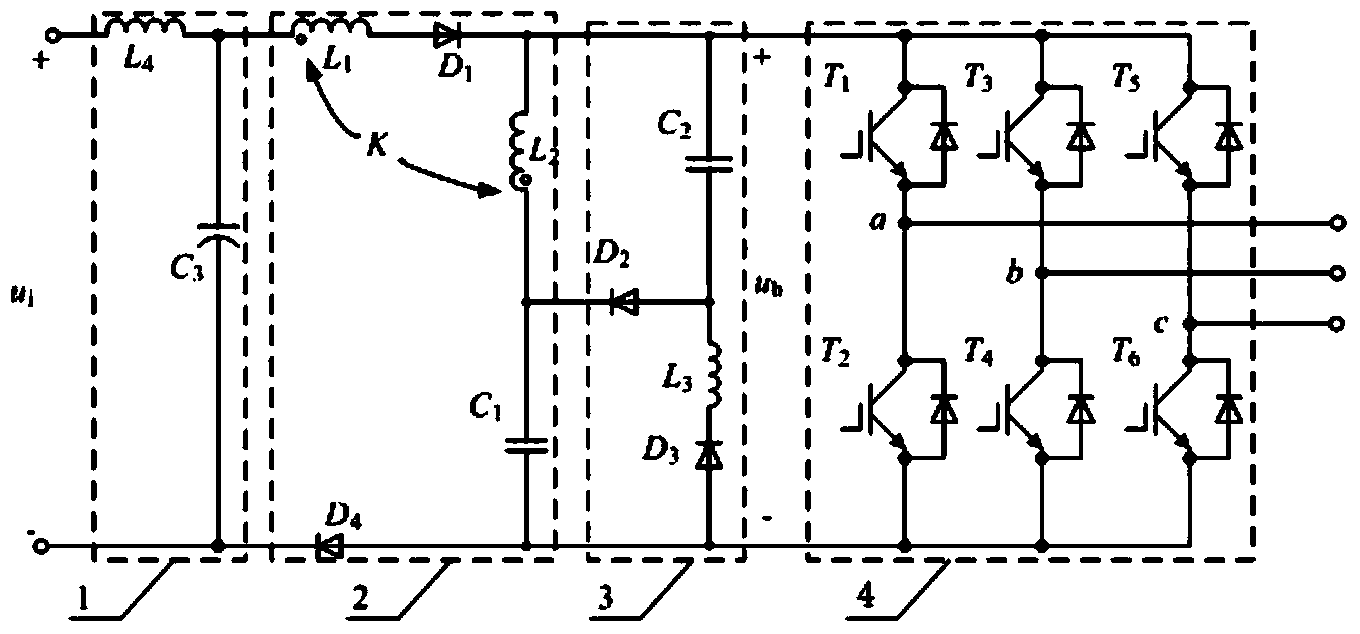

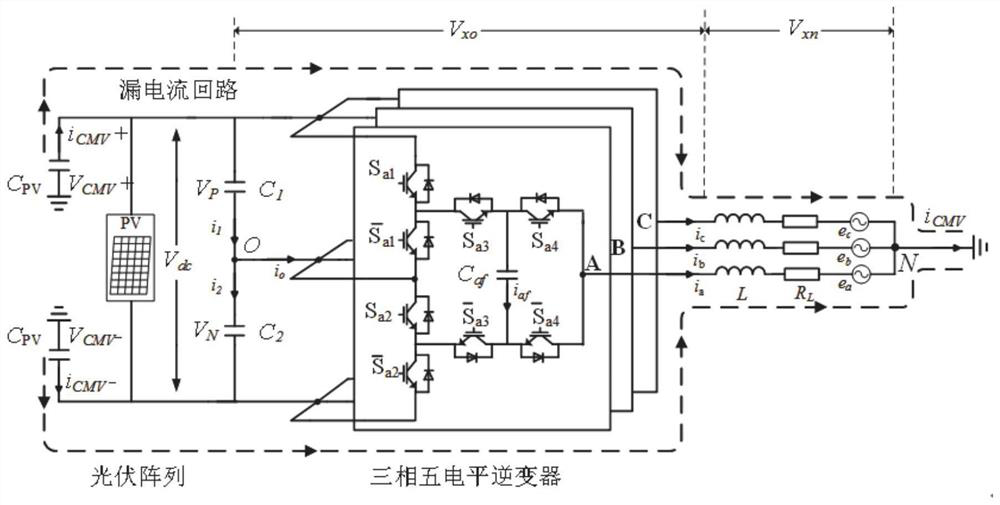

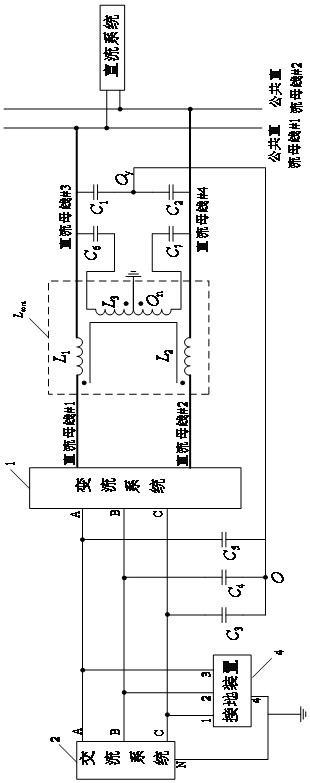

Single-stage booster inverter non-isolated grid-connected photovoltaic power generation system and control method thereof

ActiveCN103779874ARealize the boost functionEliminate common mode voltageAc-dc conversionSingle network parallel feeding arrangementsVoltage amplitudePower inverter

The invention discloses a single-stage booster inverter non-isolated grid-connected photovoltaic power generation system. A coupled inductor passive network is introduced to couple the main circuit of the inverter with a power source, the booster function is realized through primary transformation, and at the same time, a fourth diode is added, the electrical connection between the effective vector and the photovoltaic cell end and the power grid side in the traditional zero vector state can be disconnected, so the common mode voltage generation current circuit in the state can be blocked. The invention further discloses a single-stage booster inverter non-isolated grid-connected photovoltaic power generation system control method, in the control method, the adjacent effective vector synthesis pulse width modulation and direct connection control mode is adopted, and the traditional zero vector does not adopted, so the common mode voltage when the traditional zero vector is switched to other states can be eliminated, and the common mode voltage amplitude of the effective vector can be reduced.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Fault-tolerant modulation method for co-busbar double-end cascade type five-level inverters

Owner:HUAIHAI INST OF TECH

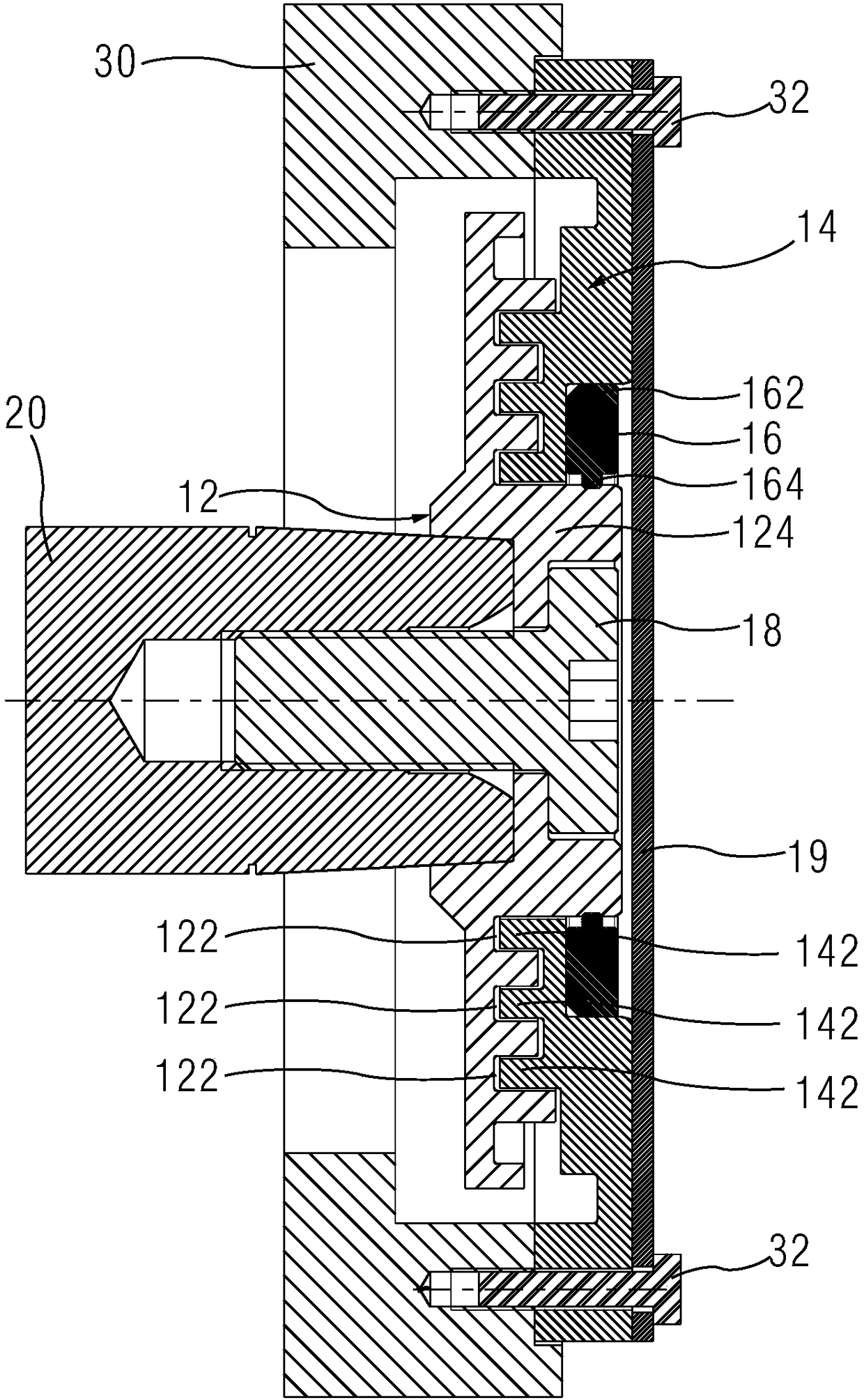

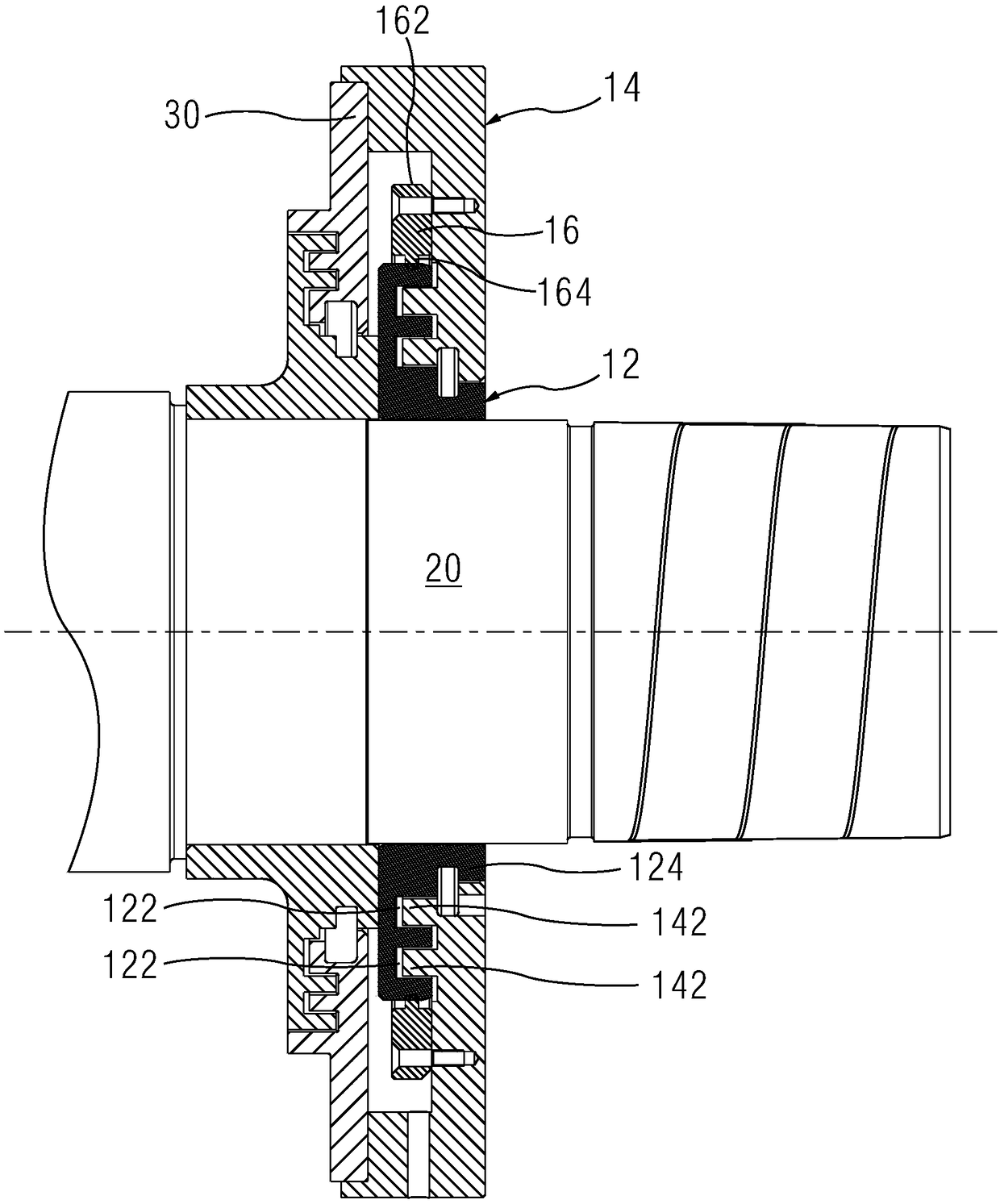

Motor driving shaft grounding device and motor

PendingCN109302003AEliminate common-mode currents and common-mode voltagesPrevent failureAssociation with grounding devicesDynamoelectric machine connectorsMotor driveDrive shaft

Owner:SIEMENS CHINA

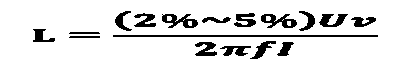

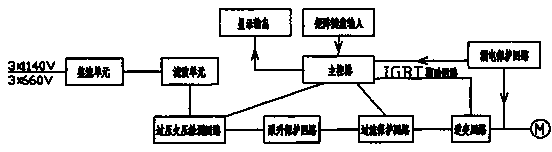

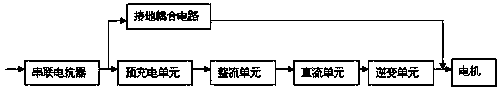

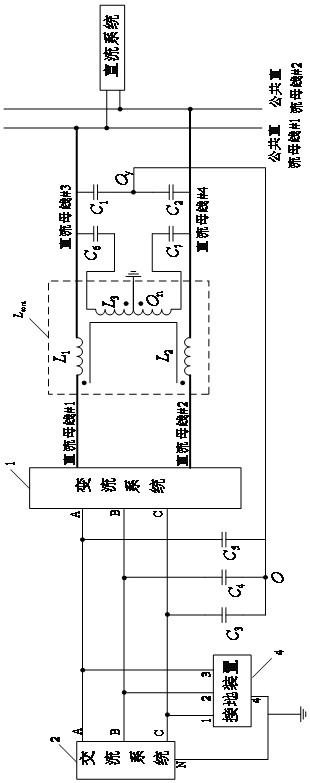

Topology circuit for mining frequency converter

InactiveCN104201872ASuppress release harmonicsHarmonic suppressionPower conversion systemsElectricityCoupling

The invention discloses a topology circuit for a mining frequency converter. The topology circuit comprises a series reactor, a grounding coupling circuit, a pre-charging circuit and a power unit, wherein the output end of the series reactor is connected with the input ends of the grounding coupling circuit and the pre-charging circuit respectively; the output end of the pre-charging circuit is connected with the input end of the power unit; the output ends of the grounding coupling circuit and the power unit are connected with the input end of a motor at the same time. The topology circuit is simple in structure; through the series reactor, the grounding coupling circuit and the pre-charging circuit, the frequency converter can be effectively prevented from releasing harmonic waves into a power grid, and impact on a rectification unit at the moment of electrification is further eliminated; through the grounding coupling circuit, the common-mode voltage can be better eliminated, and the electromagnetic interference is eliminated.

Owner:EXPLOSION PROTECTION ELECTRICAL SYST ENG GRP

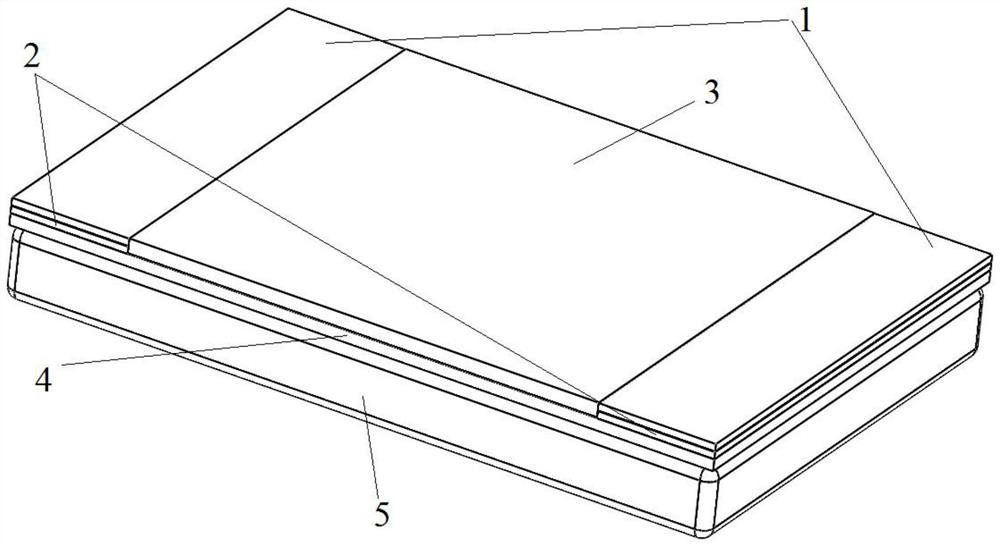

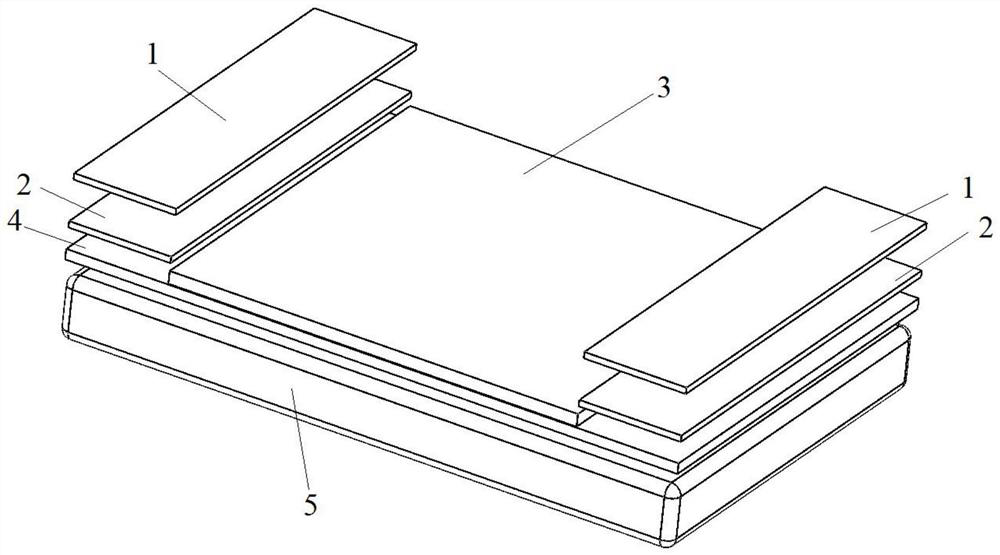

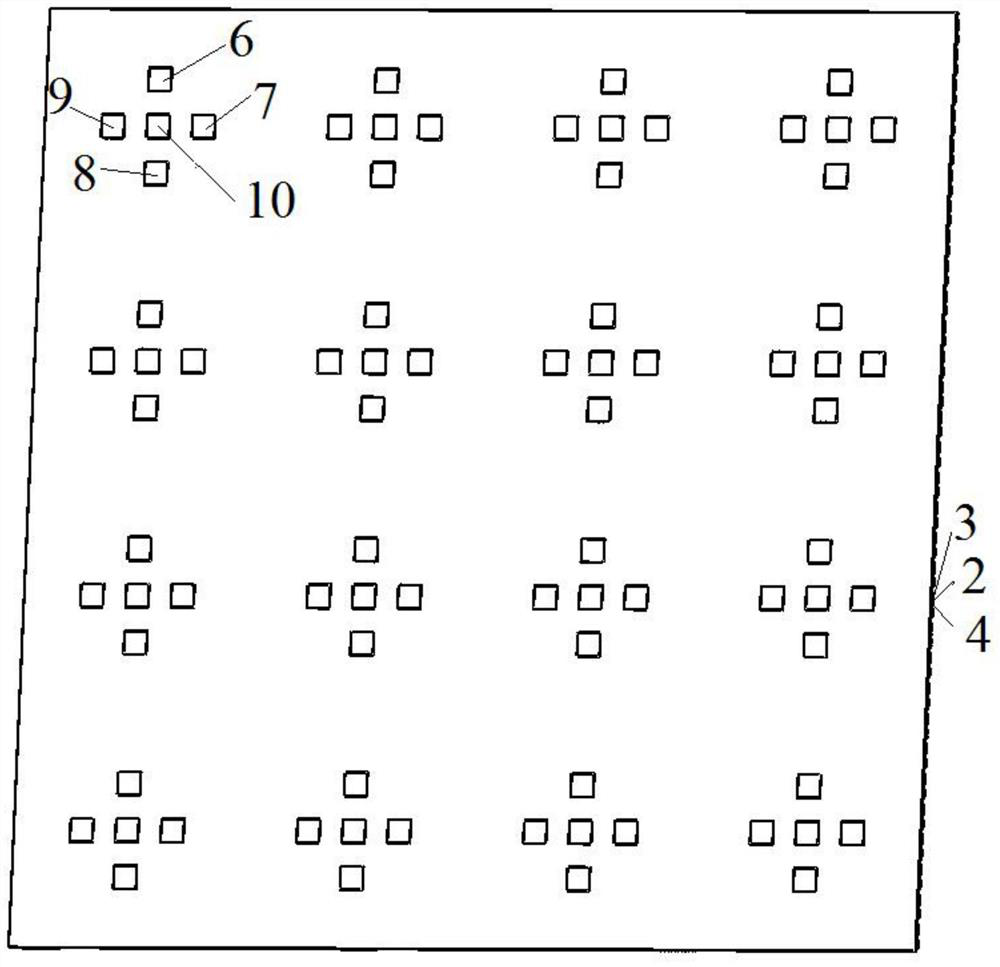

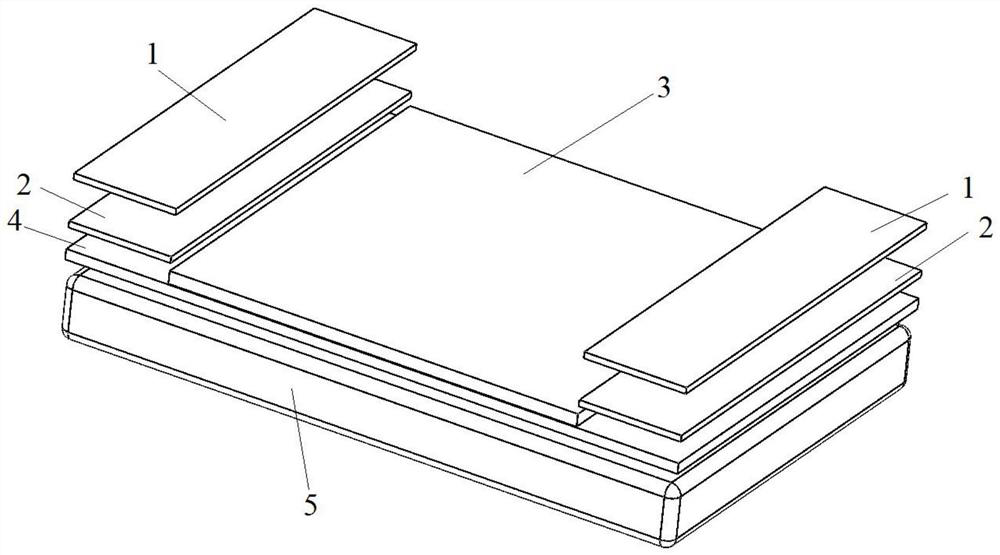

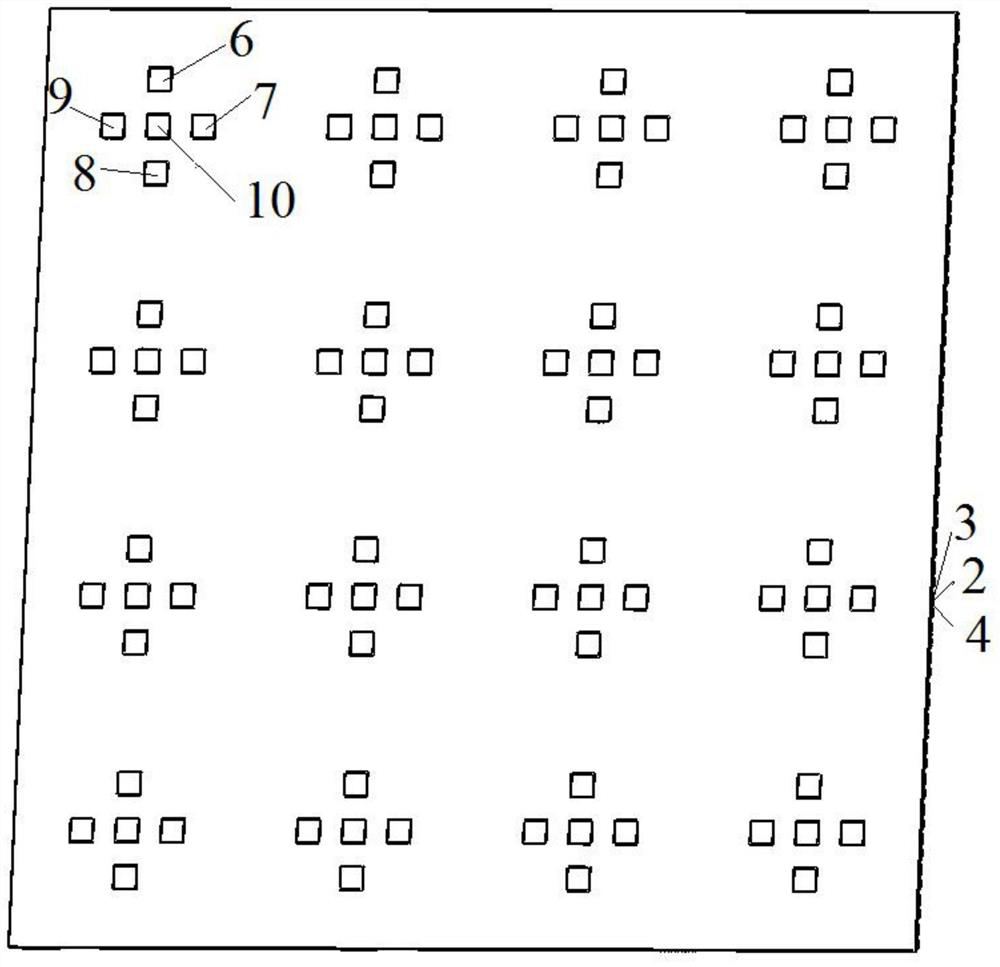

Permanent magnet type surface flow field sensor and sensor array

ActiveCN112684206AWon't breakReduce power consumptionFluid speed measurementSensor arraySurface mounting

The invention relates to a permanent magnet type surface flow field sensor and a sensor array. The sensor comprises an electrode, a conductive substrate, an insulating layer, a substrate and a magnet; the electrode is fixed on the conductive substrate, the conductive substrate is fixed on the first part of the substrate, the insulating layer is fixed on the second part of the substrate, and the magnet is attached to the bottom surface of the substrate. According to the invention, the size of an underwater speedometer can be reduced, and surface mounting is realized.

Owner:BEIHANG UNIV +1

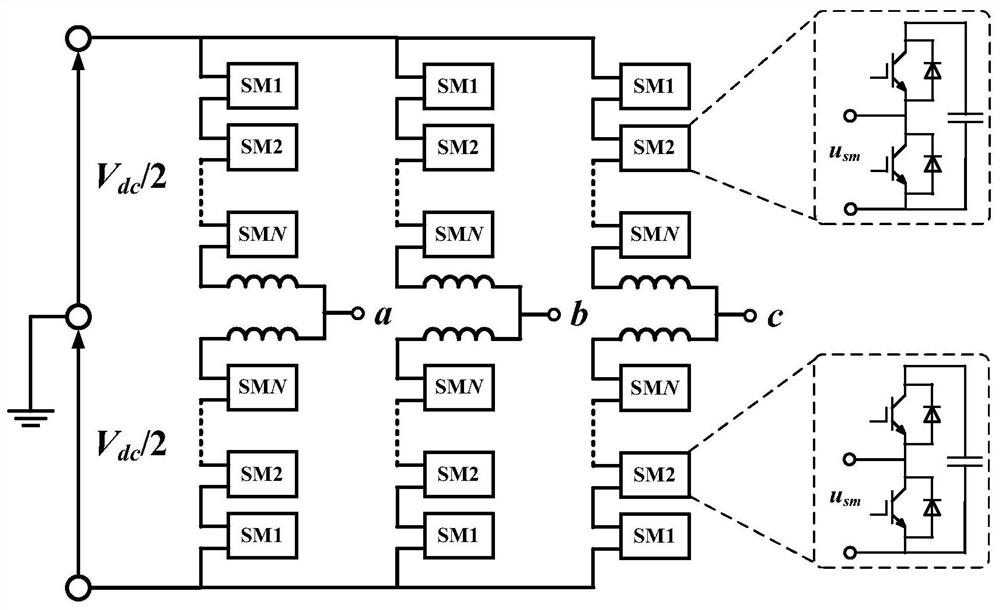

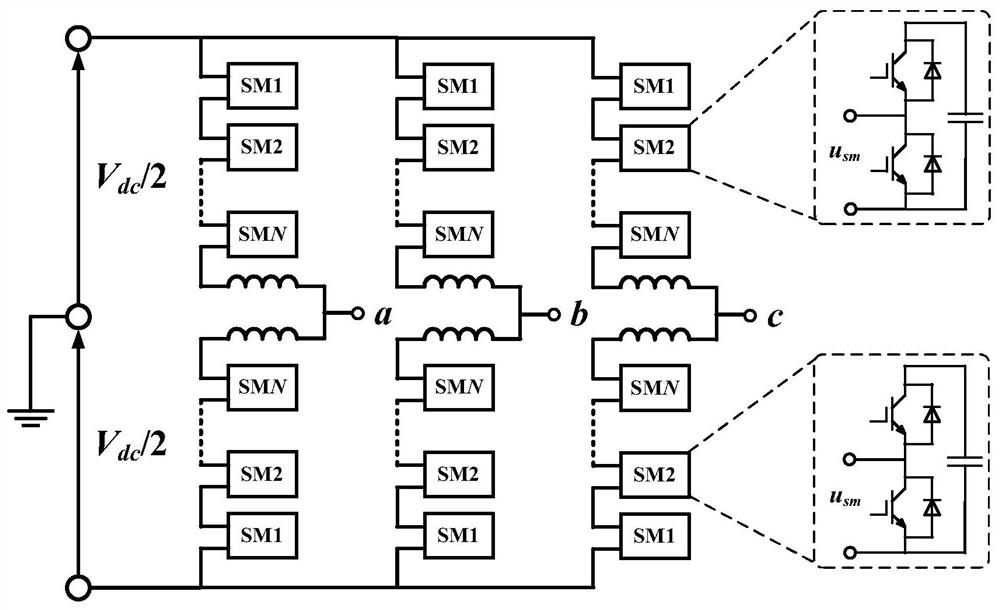

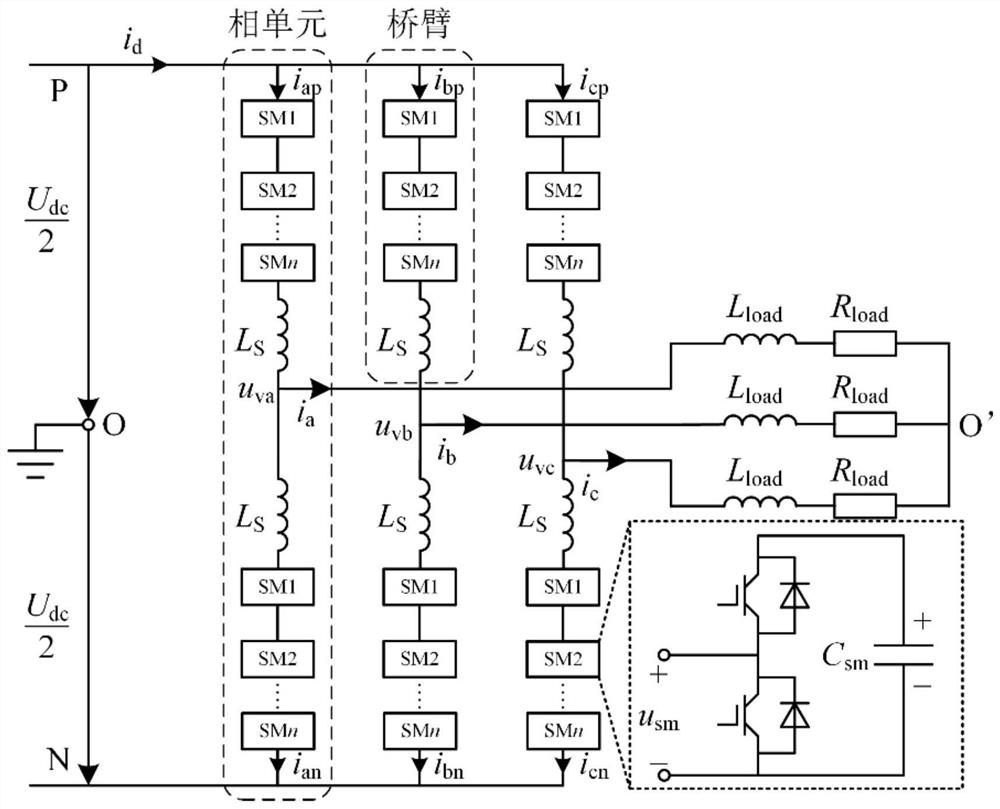

Modulation method and system suitable for MMC suppression common-mode voltage of even number of sub-modules

ActiveCN112039322AAvoid damageReduce common mode voltageAc-dc conversionPhotovoltaicsCapacitanceVoltage vector

The invention discloses a modulation method and system suitable for MMC suppression common-mode voltage of an even number of sub-modules, which belongs to the field of electric power. The method comprises the following steps of converting three-phase reference voltage analog quantity linear operation into three reference line voltage analog quantities injected with zero-sequence components, for the MMC with 2N sub-modules, respectively carrying out carrier comparison on the three reference line voltage analog quantities and N in-phase stacked carriers to obtain three driving signal digital quantities, linearly converting the three driving signal digital quantities into a three-phase reference voltage digital quantity of the MMC, and distributing the three-phase reference voltage digital quantity of the MMC to the sub-modules to control the MMC so as to obtain driving signals of all switching tubes in the MMC. According to the method, the zero common-mode voltage vector is equivalentlytransmitted in a carrier comparison addition and subtraction mode, the common-mode voltage is greatly reduced, the stray capacitance coupled common-mode current is suppressed, the method is easy to implement, and complicated calculation such as reference vector positioning based on a traditional space vector synthesis method is avoided.

Owner:HUAZHONG UNIV OF SCI & TECH

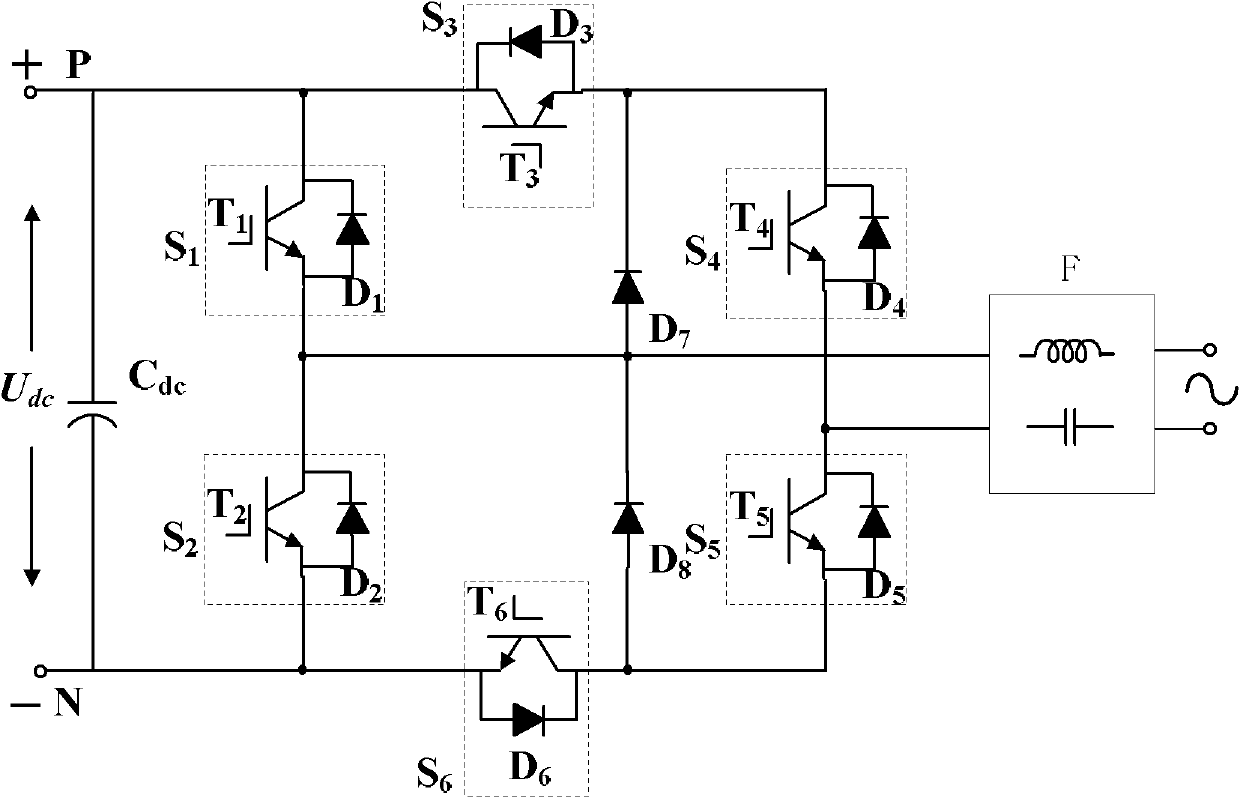

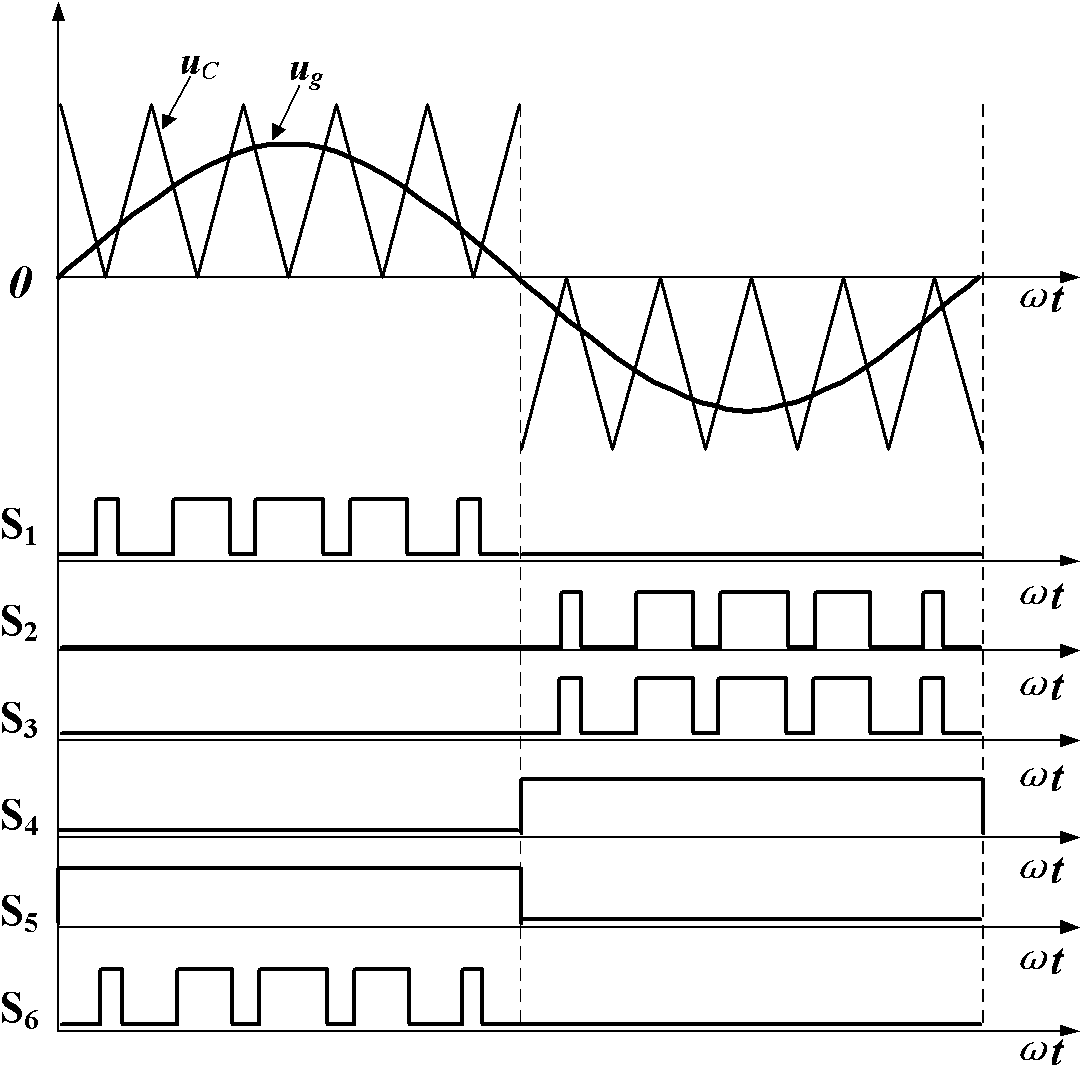

Single-phase three-level inverter

ActiveCN102185514BEliminate common mode voltageImprove output power qualityAc-dc conversionParasitic capacitorPower quality

A single-phase three-level inverter includes an input capacitor (Cdc), six power switches (S1, S2, S3, S4, S5, S6), two free-wheeling diodes (D7, D8) and a single-phase output filter (F). The switching operation is performed by the cooperation of the six power switches and the free-wheeling diodes, so that when the output voltage from the inverter is zero level, the output AC side and the input DC side of the inverter are in a decoupled state, which insures that the common-mode voltage is maintained at a constant while the output voltage from the inverter is performed with three levels, so as to completely eliminate the common-mode current.

Owner:HOYMILES POWER ELECTRONICS INC

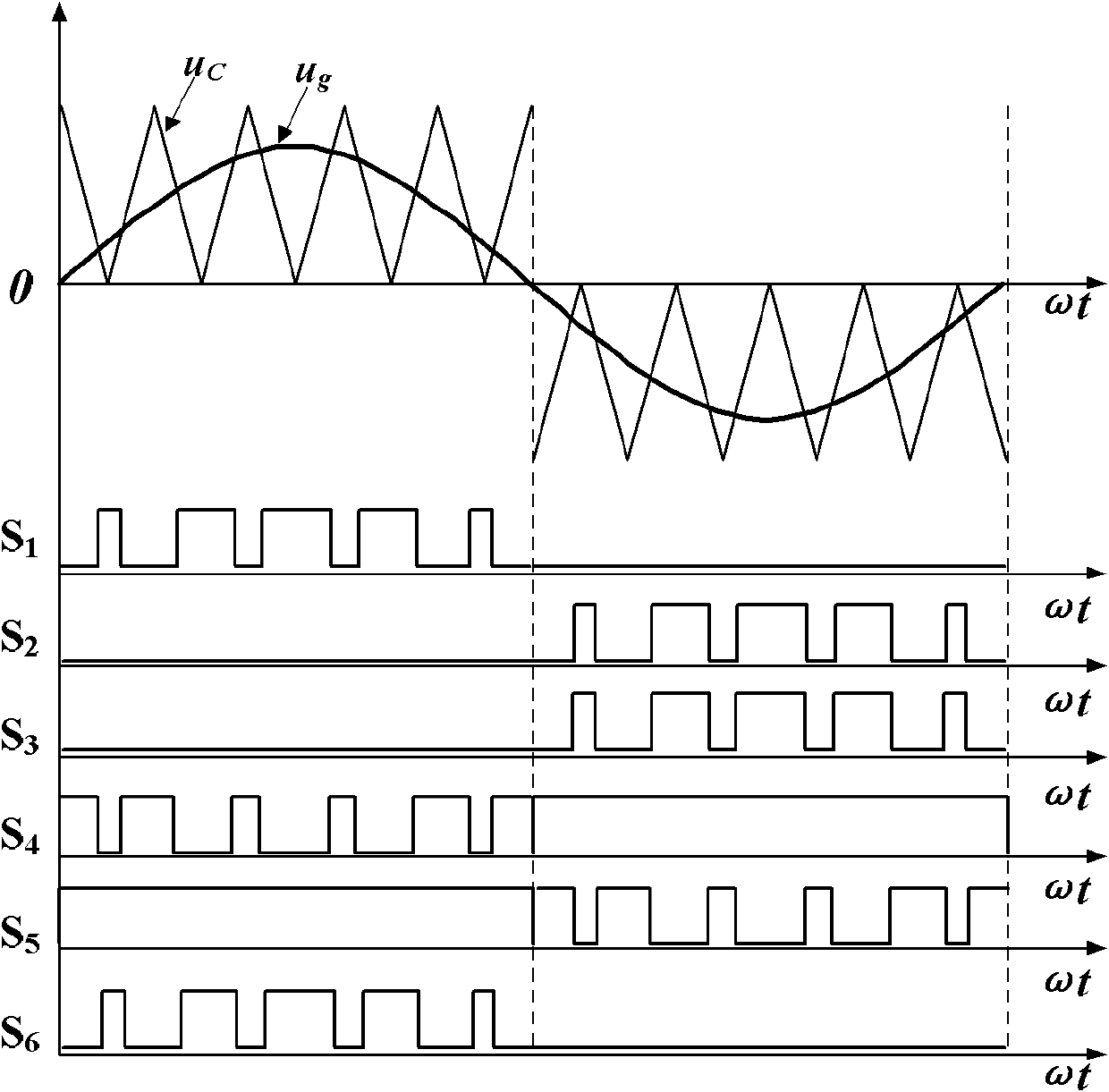

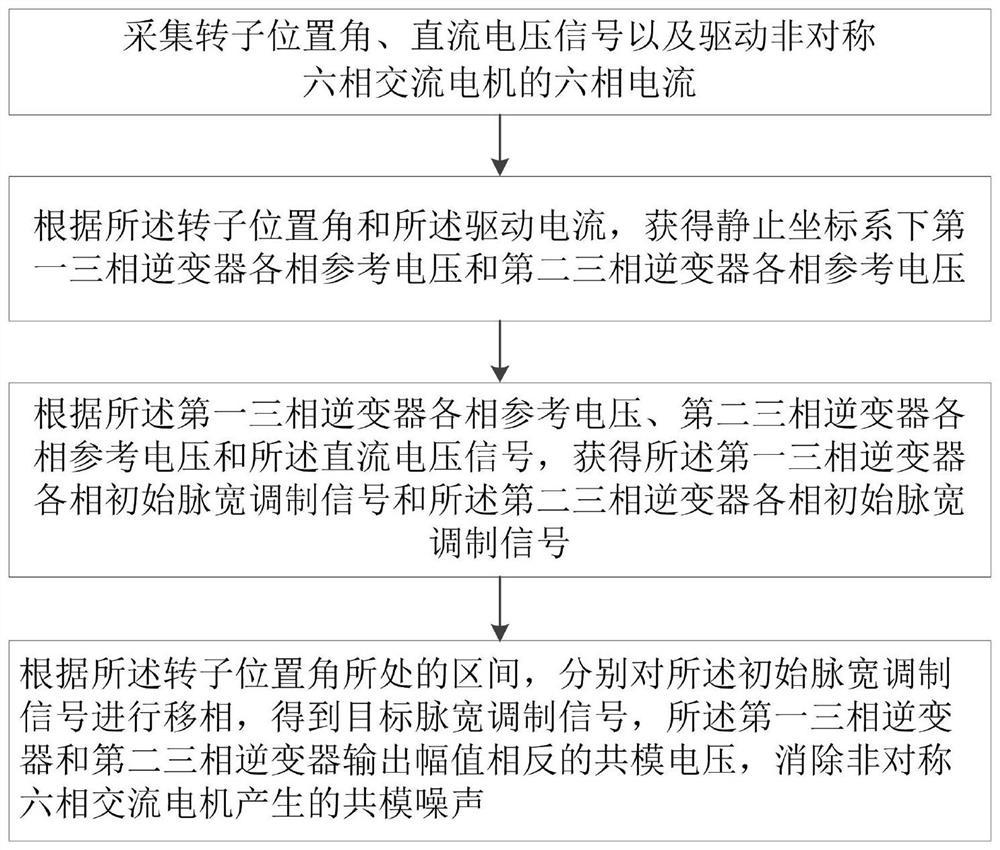

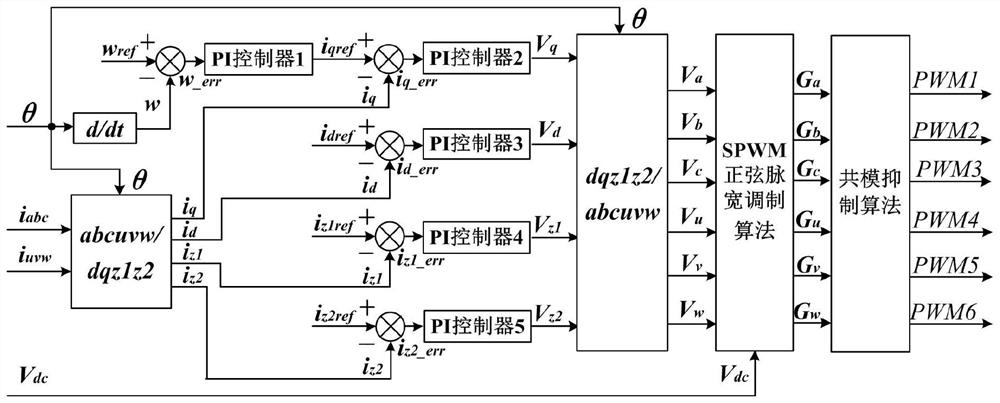

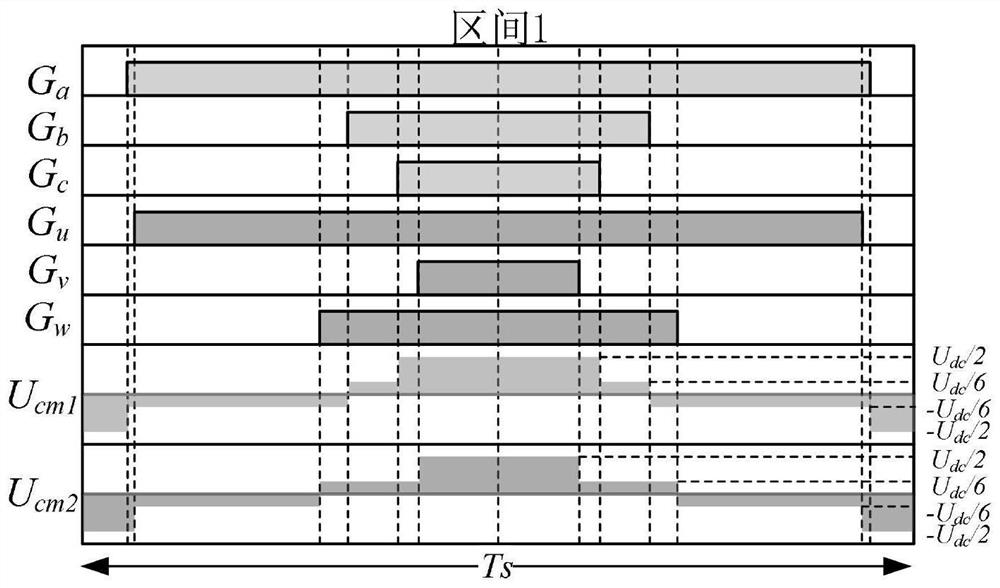

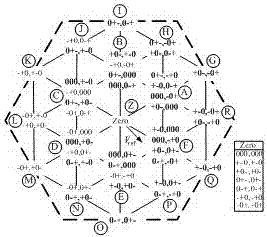

A method and system for suppressing common-mode noise of an asymmetrical six-phase AC motor

ActiveCN110011581BEliminate common mode voltageEliminate common mode noiseElectronic commutation motor controlAC motor controlElectric machineControl engineering

The invention discloses a method and system for suppressing the common mode noise of an asymmetrical six-phase AC motor. Phase, so that the two sets of three-phase inverters driving the asymmetric six-phase AC motor output common-mode voltages with opposite amplitudes, so as to eliminate the total common-mode voltage input from the inverter to the asymmetric six-phase AC motor, thereby suppressing the non-symmetrical six-phase AC motor. Common mode noise generated by symmetrical six-phase motors; at the same time, the control method and system of the present invention do not require additional hardware, and can be realized only by improving software algorithms, have strong versatility, can protect motor bearings, and improve system reliability.

Owner:HUAZHONG UNIV OF SCI & TECH

Three-level zero common-mode voltage modulation method based on DSP (digital signal processor) and CPLD (complex programmable logic device)

InactiveCN102739091BModulation method is simpleEasy to implementAc-dc conversionDigital signal processingThree level

Owner:HEFEI UNIV OF TECH

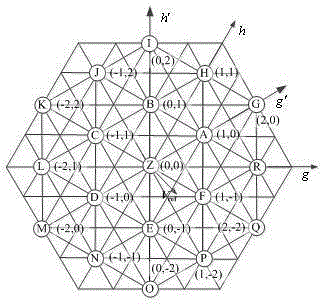

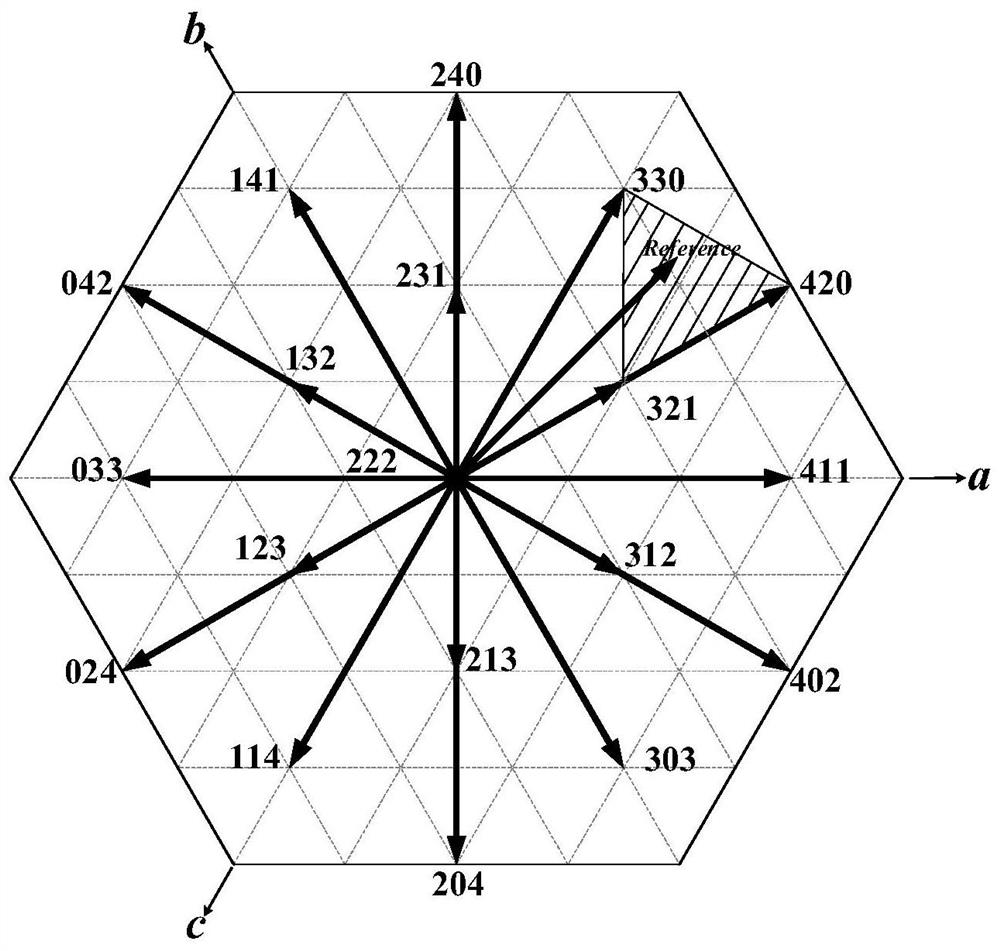

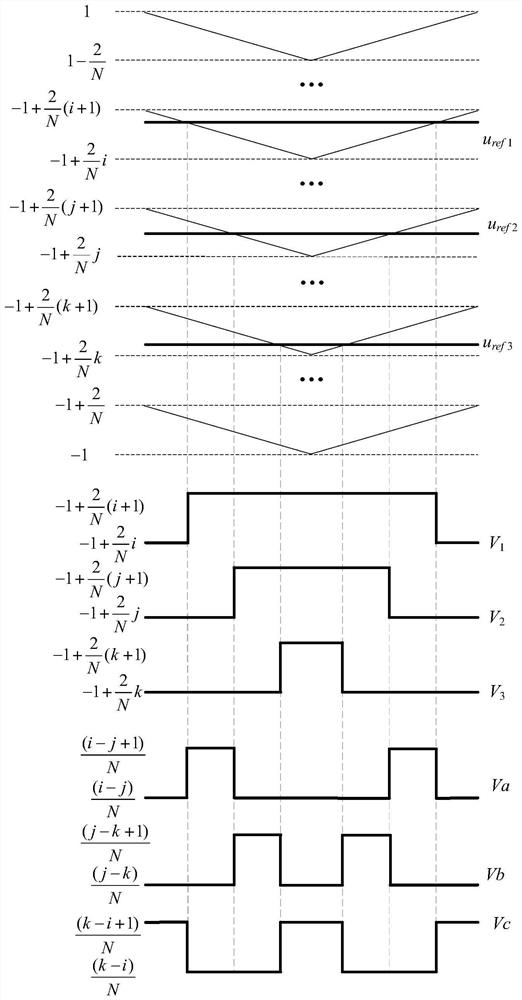

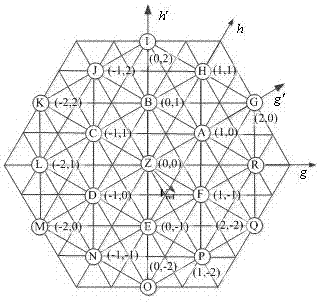

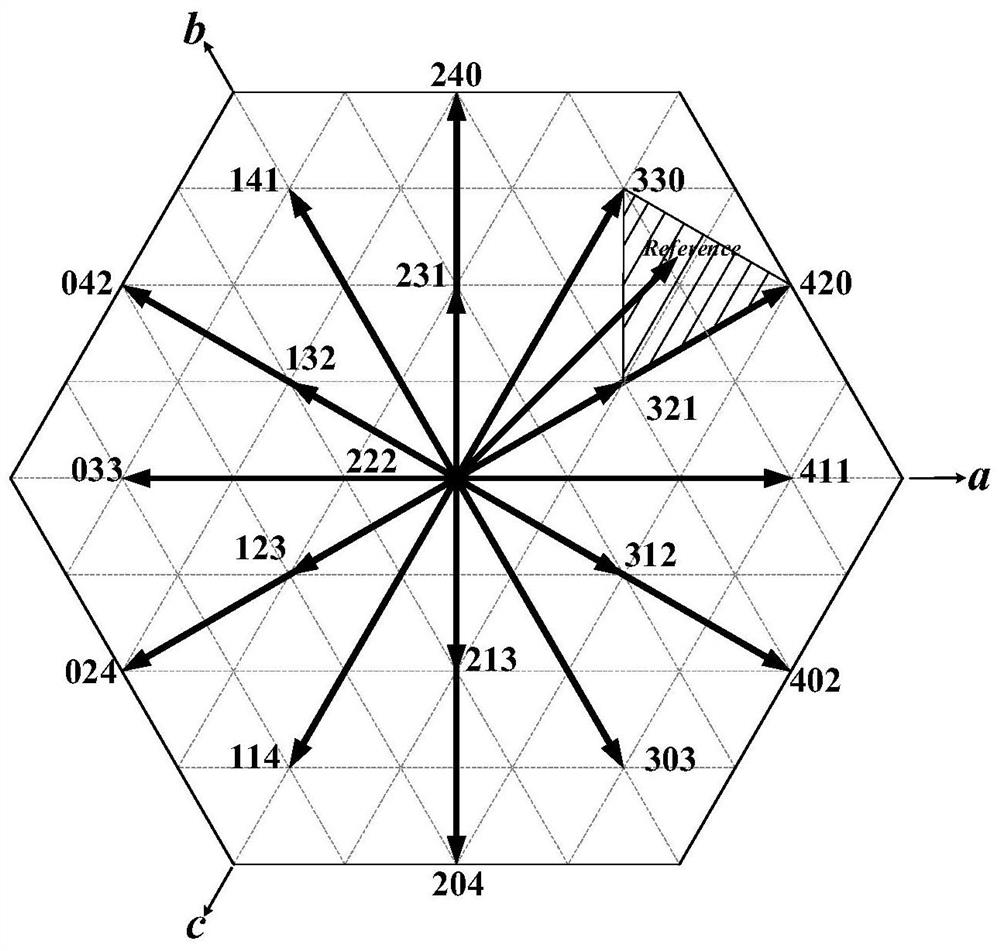

A fast three-phase space vector modulation method in two-dimensional coordinate system

ActiveCN109067224BStable outputReduce switching lossesEfficient power electronics conversionAc-dc conversionSwitching frequencyHarmonics

The invention provides a three-phase space vector rapid modulation method in a two-dimensional coordinate system, which belongs to the technical field of power electronic modulation. This method transforms the traditional three-phase two-dimensional coordinate system into a new two-dimensional rectangular coordinate system, and obtains the remaining two vectors of the modulation triangle by directly checking the vector closest to the origin, which has strong scalability. In addition, this method can provide several controllable factors, and the factor N can be used as an optimization target to weaken the common-mode voltage and select redundant vectors for voltage equalization; the controllable switching sequence produced can ensure the smooth transition of vectors in the modulation triangle and between modulation triangles To reduce the overall switching frequency of the system to reduce switching loss and optimize harmonic performance; adjustable zero-vector duty cycle can also optimize harmonic performance, synthesize a more ideal flux linkage circle to output high-quality sine waves and ensure the same voltage as the factor N balanced. The function of this method reflects its superior application value and good application prospect.

Owner:SOUTHWEST JIAOTONG UNIV

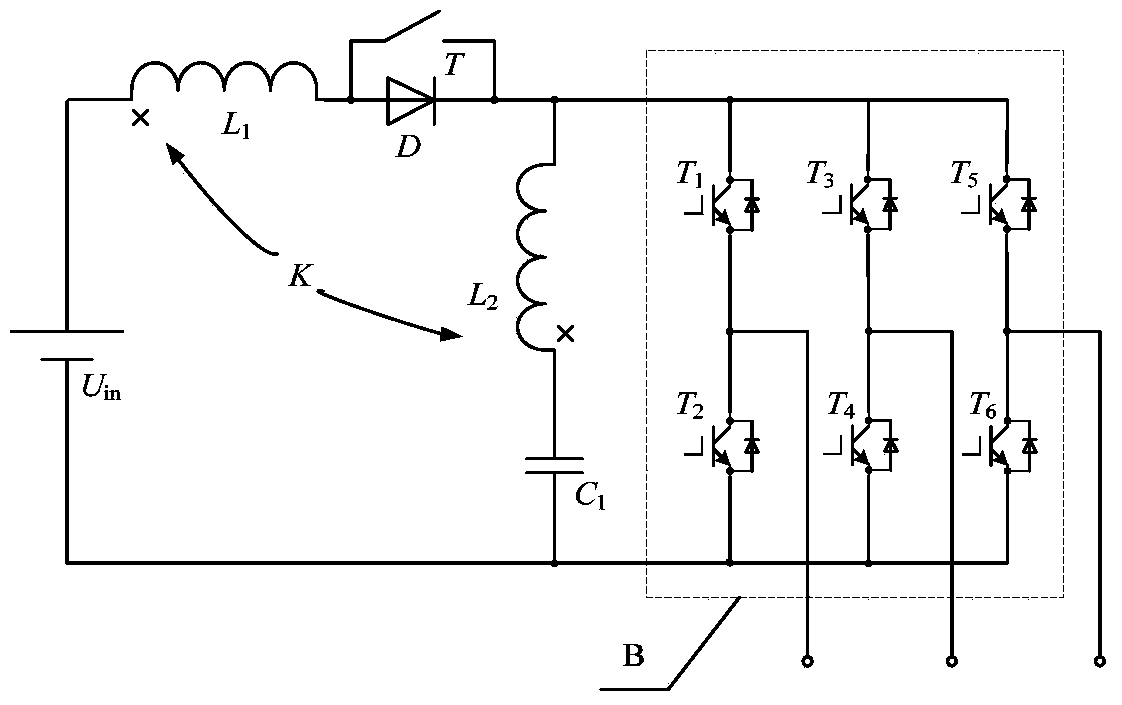

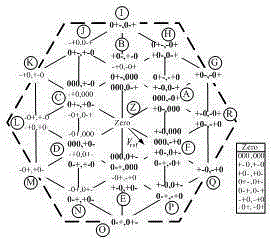

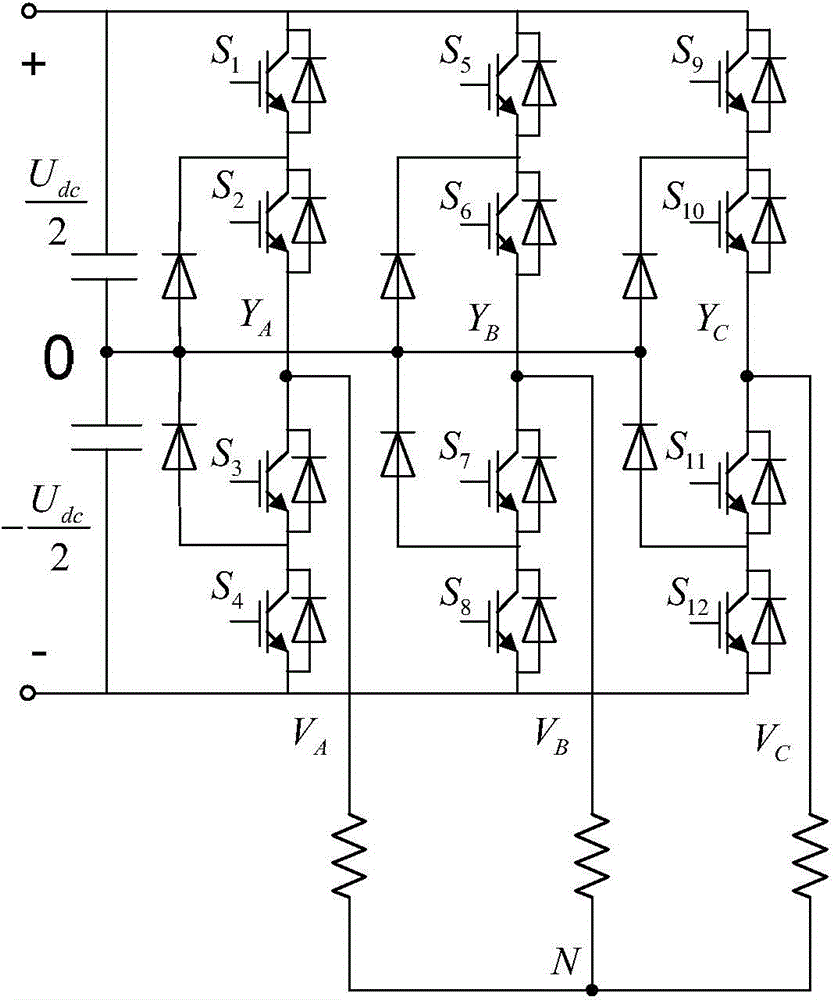

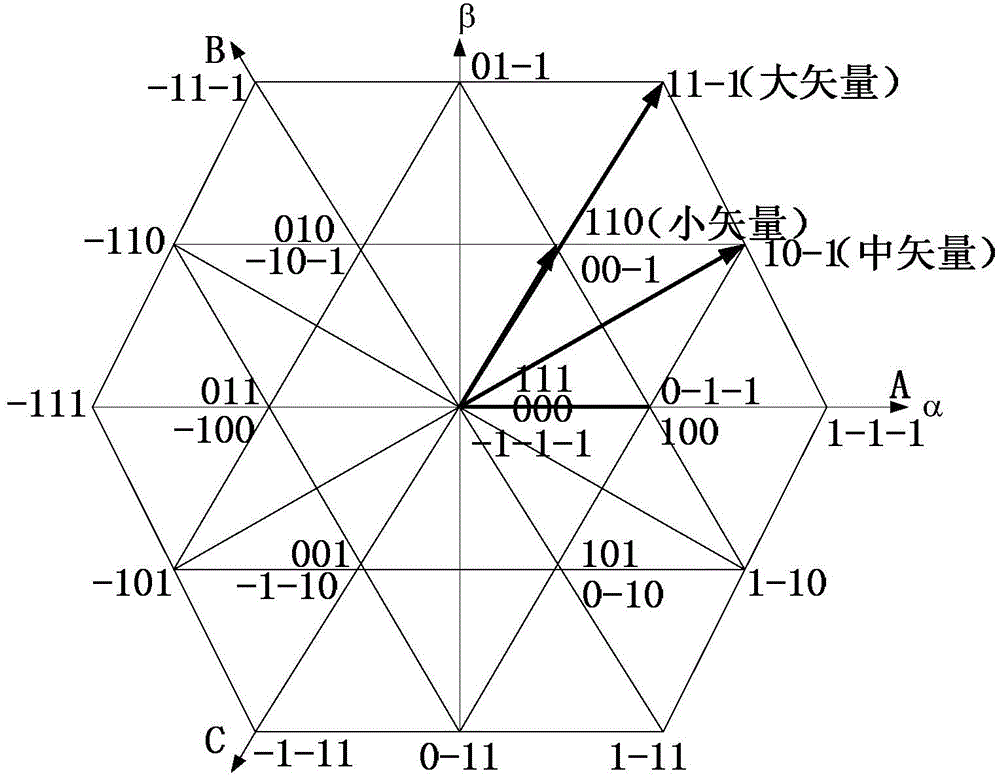

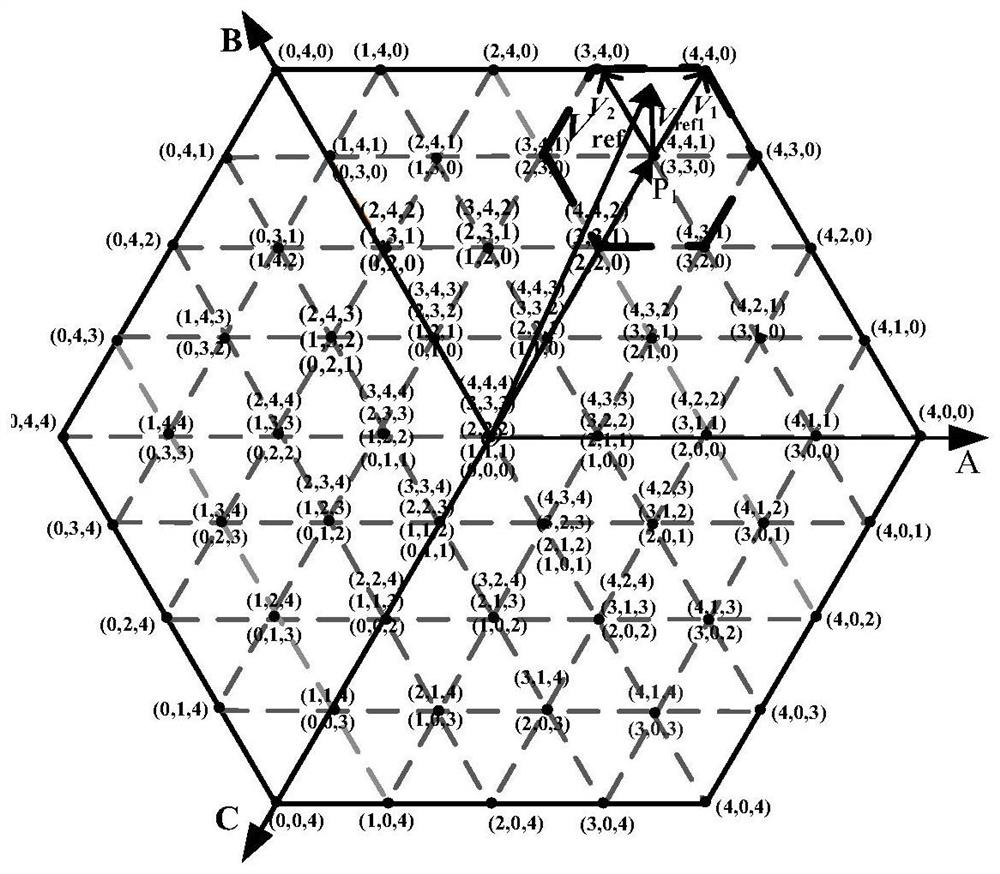

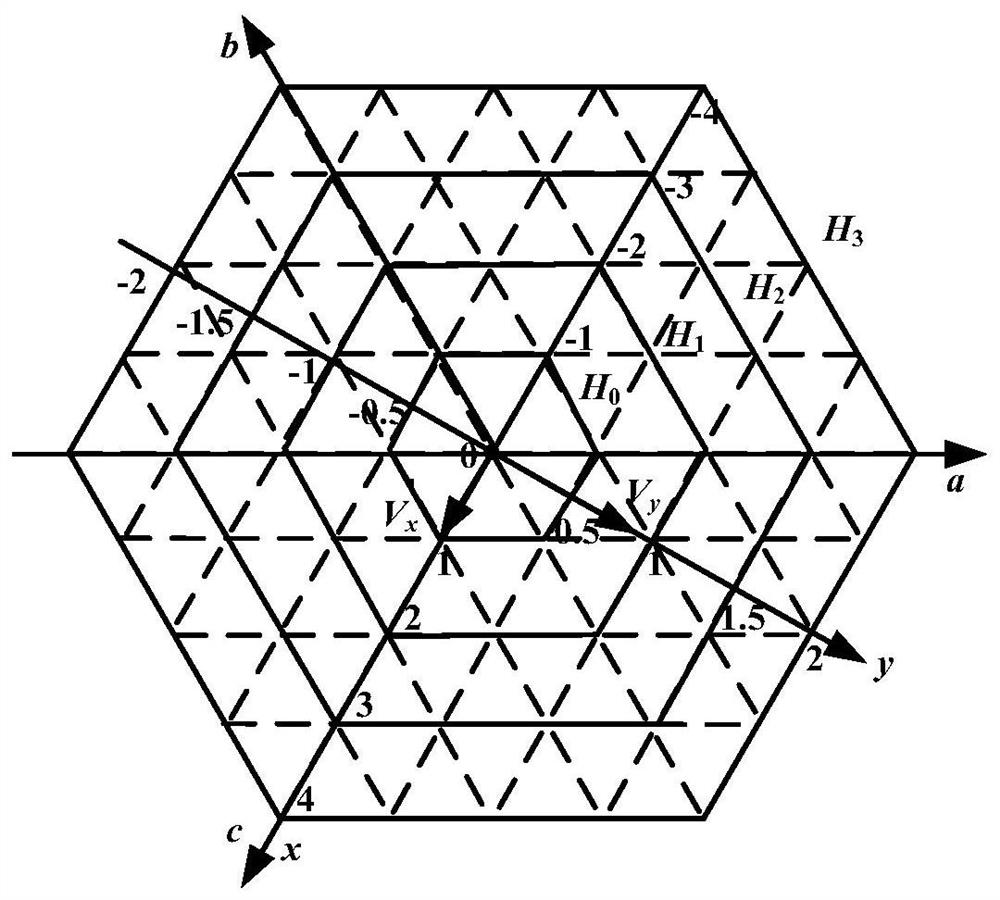

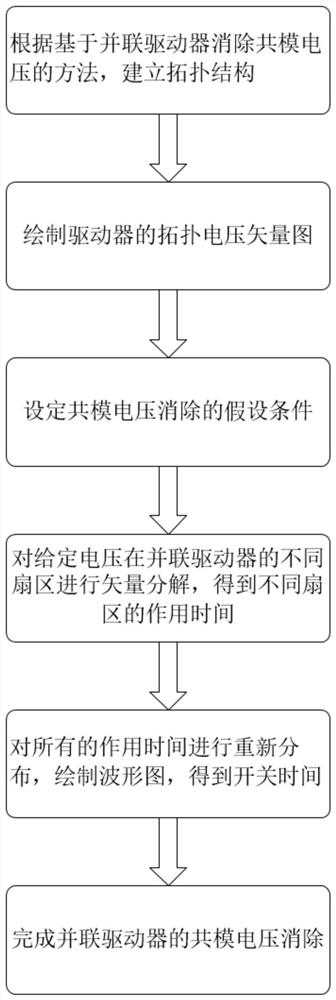

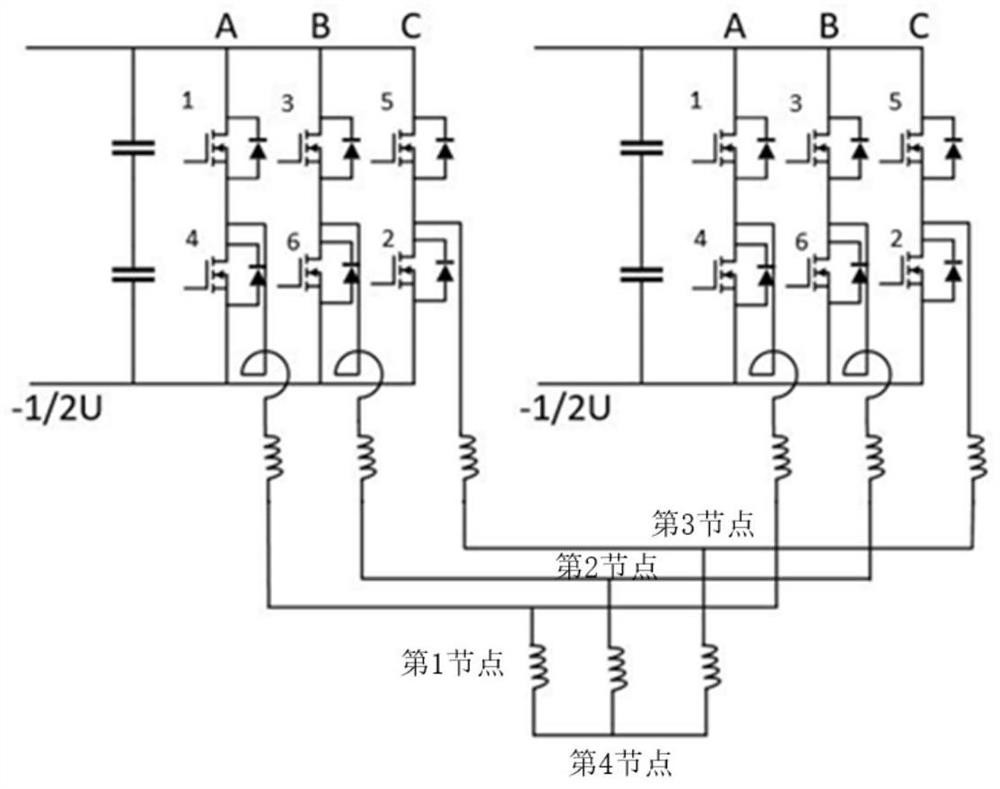

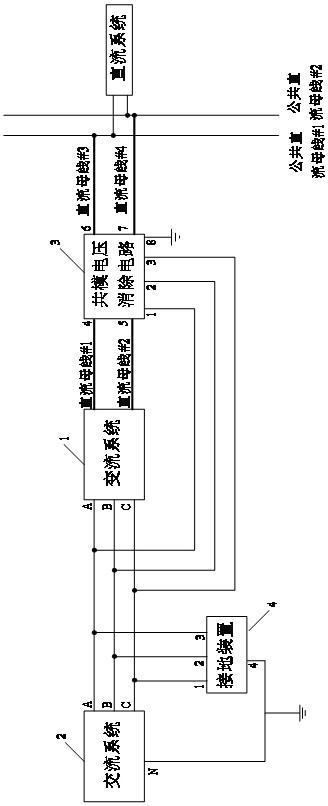

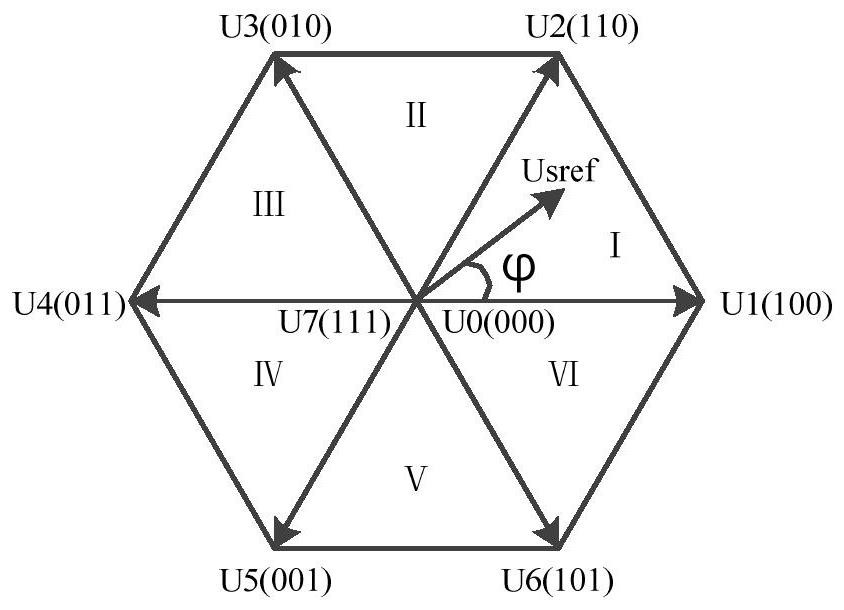

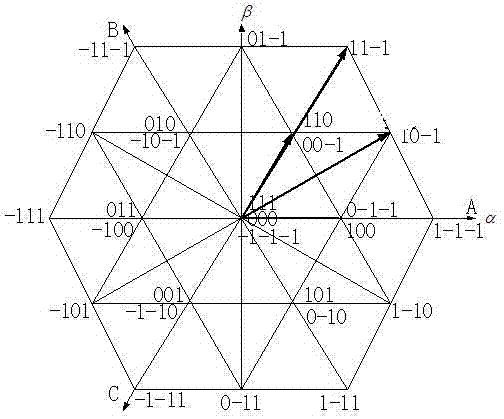

Common-mode voltage elimination method based on parallel driver topological structure

The invention discloses a common-mode voltage elimination method based on a parallel driver topological structure. The common-mode voltage elimination method solves the problem of effectively eliminating common-mode voltage under high and low frequencies. The method comprises the following steps of: establishing a topological structure for eliminating common-mode voltage according to a parallel driver; drawing a topological voltage vector diagram; putting forward assumed conditions of common-mode voltage elimination; performing vector decomposition on different sectors of the given voltage to obtain action time of different sectors; redistributing all action time, drawing an oscillogram, and modulating to obtain switching time; and completing common-mode voltage elimination of the parallel drivers. According to the method, assumed conditions are proposed to generate voltages which are equal in size and opposite in direction in a parallel driver topological structure, and given voltages are subjected to vector decomposition in each sector; and the obtained action time is redistributed and modulated, and the common-mode voltage is eliminated. The topological structure is simple, easy to construct and convenient to understand; and the common-mode voltage can be effectively eliminated without a specific environment. The method is used in the fields of automotive electronics, medical instruments and aerospace.

Owner:XIAN TECH UNIV

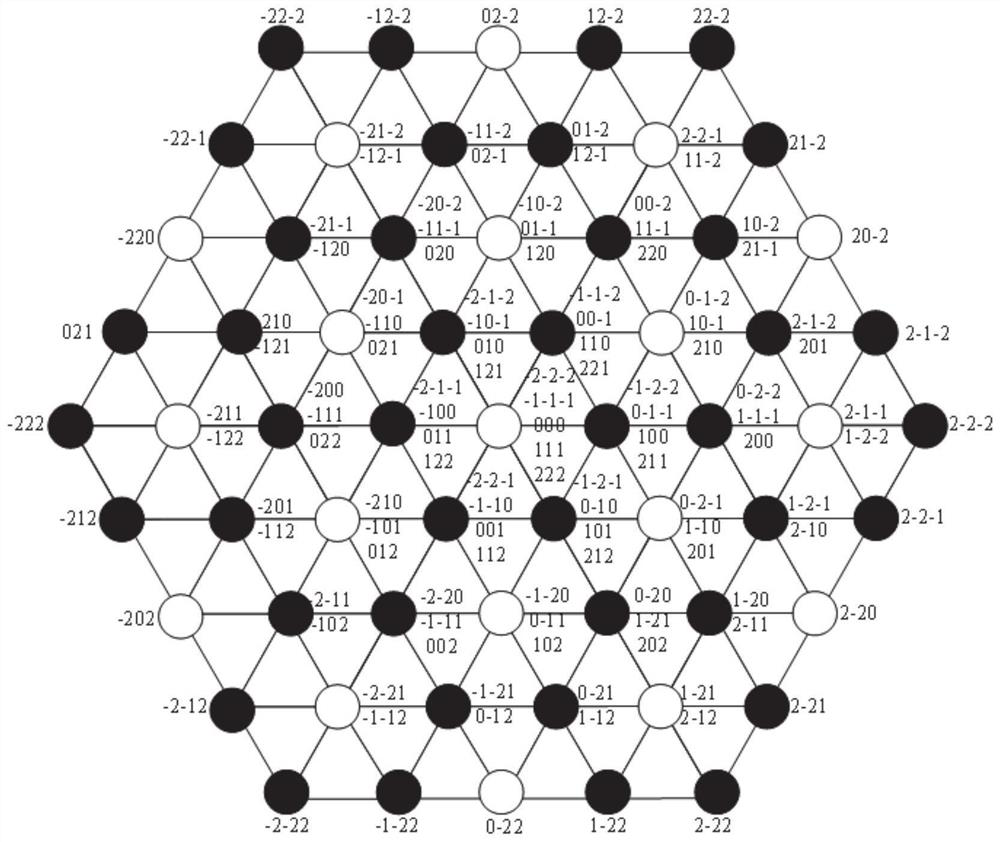

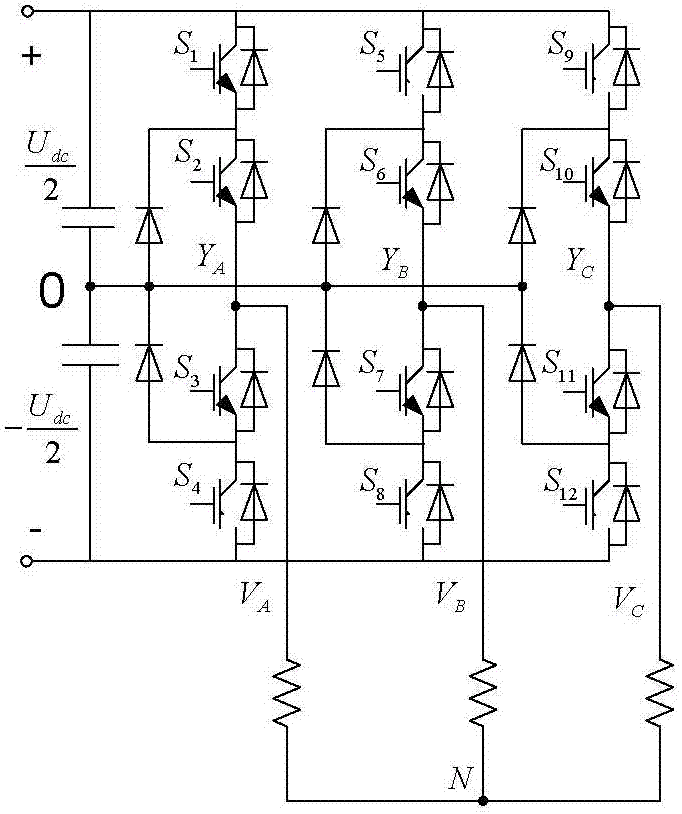

A fault-tolerant modulation method for a common bus double-ended cascaded five-level inverter

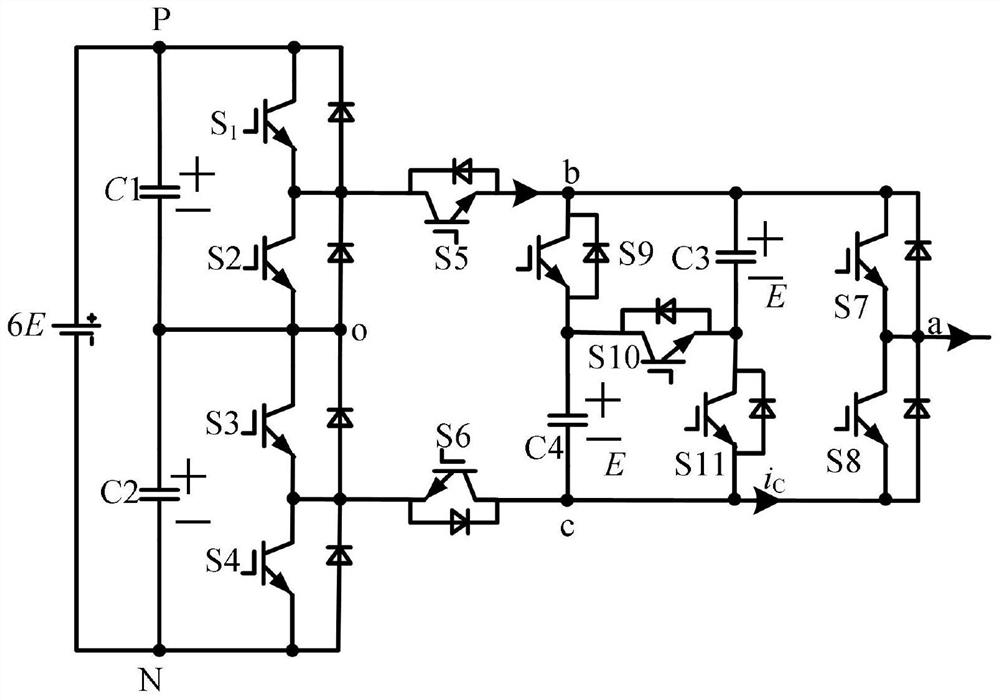

ActiveCN105207508BAchieve balanceEliminate common mode voltageAc-dc conversionVoltage vectorDouble fault

A fault-tolerant modulation method for a double-terminal cascaded five-level inverter with a common bus. The stator winding of the motor is opened, and the two ends of the stator winding are powered by two identical inverters, and the two inverters share a The DC bus is set to form a common bus double-ended cascaded five-level topology; in order to ensure that the reference voltage vector track is a circle, when a short-circuit fault occurs in the switching device, the maximum output voltage of the inverter will drop to half of the original, and only the inner six The polygon can use the switch state to synthesize the reference voltage vector, and use the rotation and per unit of the coordinate system to effectively simplify the five-level modulation method and reduce the hardware requirements of the system control; use the balance factor to ensure the fault-tolerant control, and realize the midpoint potential balance. The present invention is based on the high fault-tolerant characteristics of the double-ended cascaded five-level inverter. When the switching device fails, the fault-tolerant operation of the inverter is realized by reselecting the voltage vector; an optimization method is proposed for the double-ended cascaded system The 60° modulation method.

Owner:HUAIHAI INST OF TECH

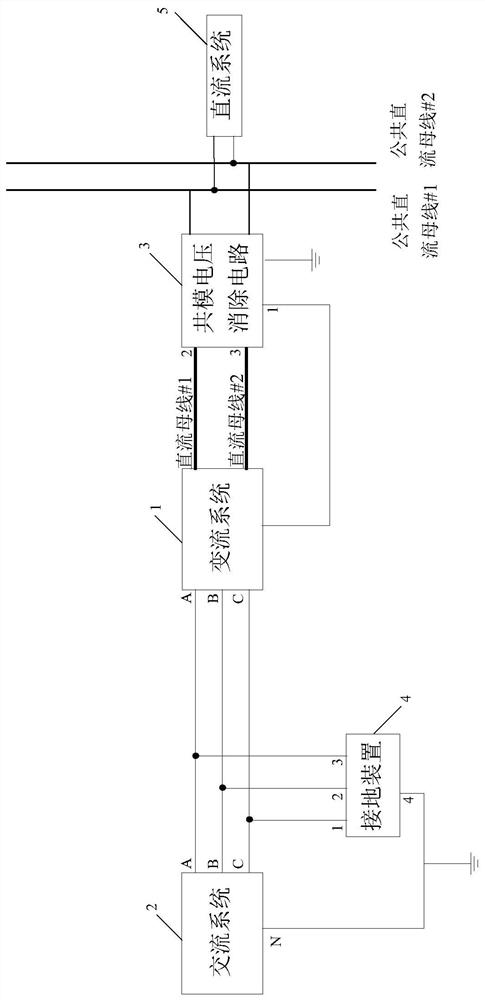

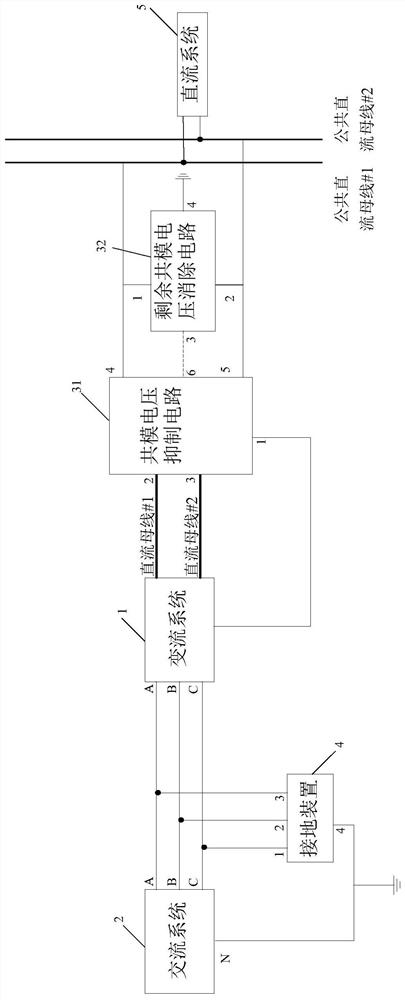

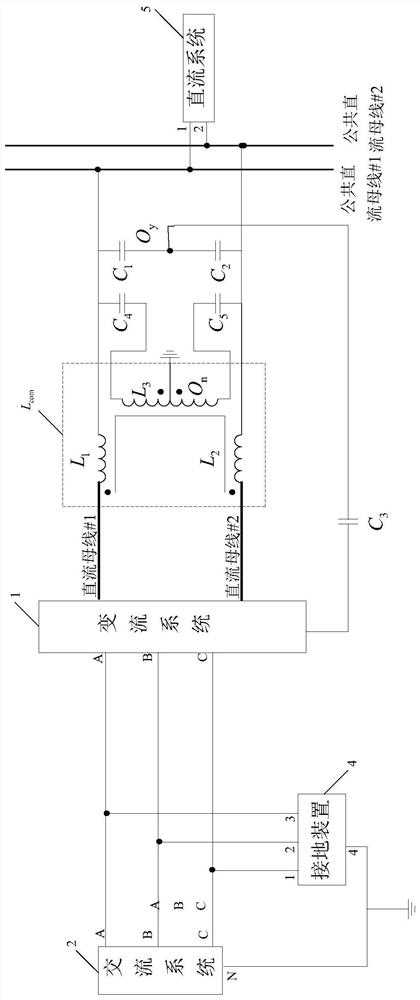

Non-isolated AC/DC power supply system

PendingCN113285498AEliminate common mode voltageImprove the quality of supply voltageAc-dc network circuit arrangementsControl theoryDirect current

The invention provides a non-isolated AC / DC power supply system, which comprises an AC system, a grounding device, a converter system, a common-mode voltage elimination circuit and a DC system, and is characterized in that a three-phase AC line of the AC system is connected with a three-phase AC line of the converter system, and is connected with a first end, a second end and a third end of the grounding device; a fourth end of the grounding device is connected with the zero line of the AC system and is grounded; and the AC system is also connected with the first end of the common-mode voltage elimination circuit; the direct current side of the AC system is correspondingly connected with the second end and the third end of the common-mode voltage elimination circuit through two direct current buses, and the output end of the common-mode voltage elimination circuit is connected with the direct current system through two common direct current buses. By implementing the invention, the common-mode voltage is eliminated, the quality of the power supply voltage is improved, and the power supply reliability is further improved.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

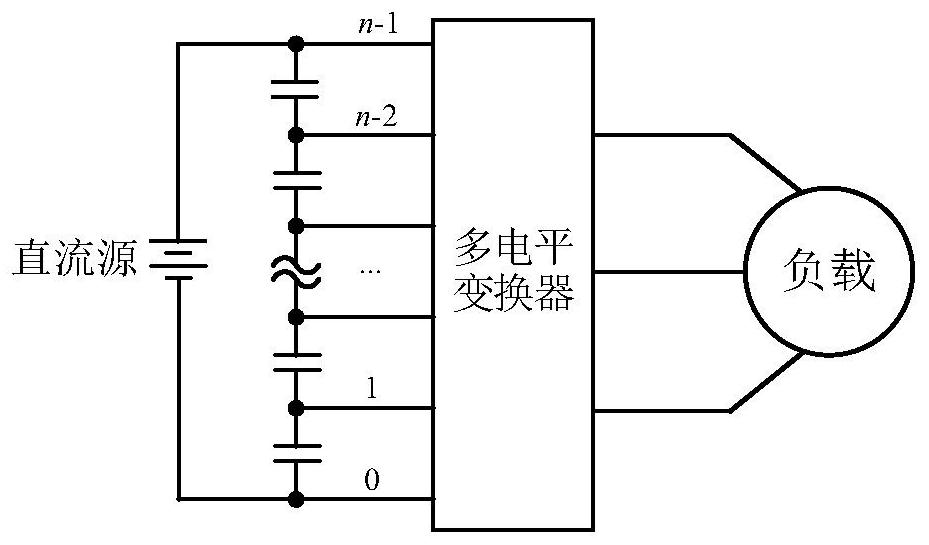

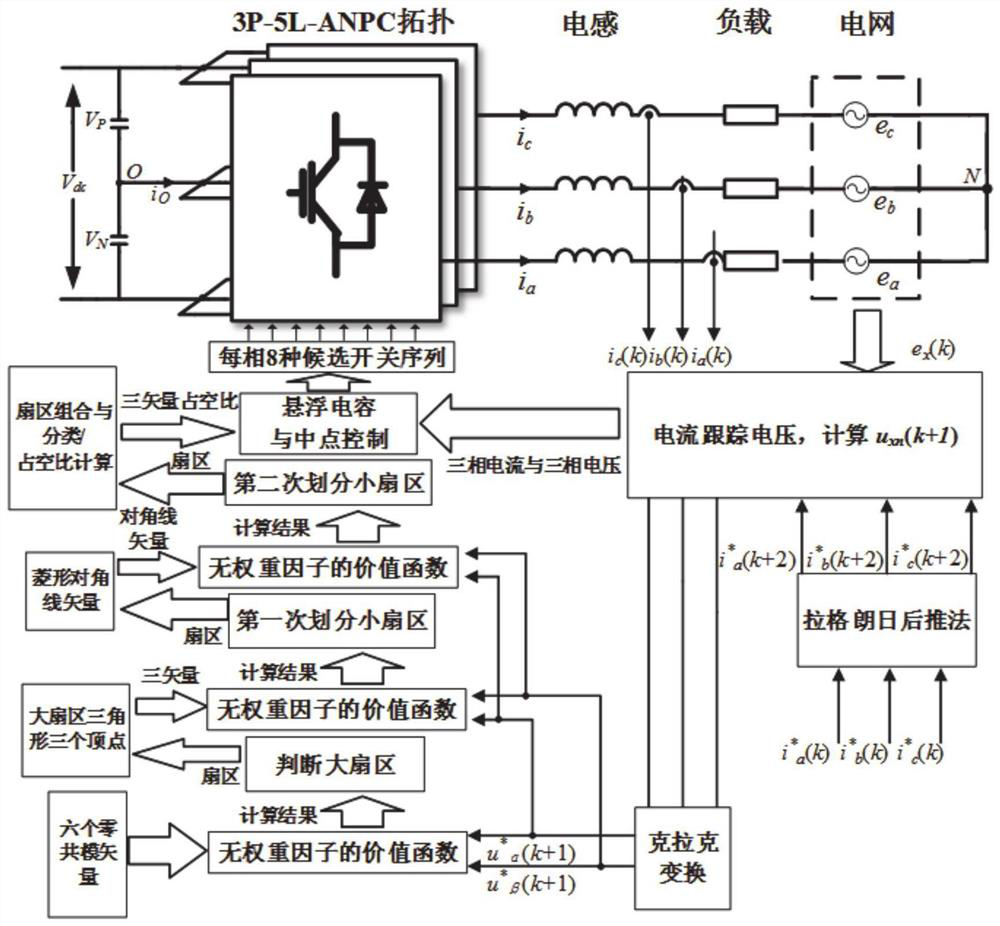

Multi-level inverter model prediction control method and system

PendingCN113904577AAchieve fixationHarmonic reductionAc-dc conversionSingle network parallel feeding arrangementsCapacitanceCapacitor voltage

The invention discloses a multi-level inverter model prediction control method and system. The method comprises the steps of: presetting a control threshold value for controlling a floating capacitor voltage fluctuation range, and determining the balance priority of a midpoint voltage and a floating capacitor voltage; constructing a neutral-point voltage and floating capacitor voltage balance condition, and screening a switch sequence through the balance condition; constructing a value function, constructing a space vector diagram, performing sector division on the space vector diagram according to a vector value function value, and determining a first target sector where the reference voltage is located; carrying out secondary division in the first target sector by taking a virtual vector as a benchmark, carrying out tertiary division on a second target sector according to a rhombic diagonal line, and determining a final position of the space vector diagram where the reference voltage is located; determining a zero common mode vector according to the final position; reordering the vectors according to an inner and outer ring division principle of the space vector diagram to obtain a sequence with reduced switching loss and fixed switching frequency; and obtaining a duty ratio according to the value function so as to control the action of an inverter switching tube.

Owner:SHANDONG UNIV

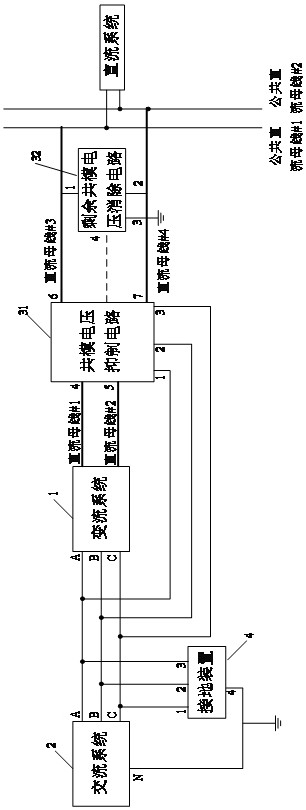

AC/DC power supply system

ActiveCN113258620AImprove the quality of supply voltageReliable power supplyPower conversion systemsPhysicsElectrical and Electronics engineering

The invention discloses an AC / DC power supply system characterized in that a grounding device is additionally arranged between an AC system and a converter system, and the grounding device is also connected with a null line and the ground, so that the null line and a grounding point are provided for the conversion system, and the wiring mode of the conversion system is not limited to a three-phase three-wire system; a common-mode voltage elimination circuit is connected to the alternating current side and the direct current side of the conversion system, and the common-mode voltage elimination circuit is not limited to restraining common-mode voltage between the alternating current side and the direct current side of the conversion system; and meanwhile, reverse common-mode voltage of a corresponding proportion is inducted, and the reverse common-mode voltage is connected into a direct current bus and a ground wire loop in series; therefore, the ground common-mode voltage of the conversion system is eliminated.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

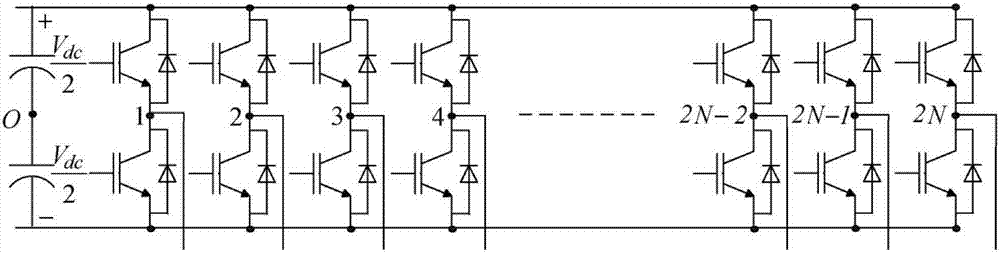

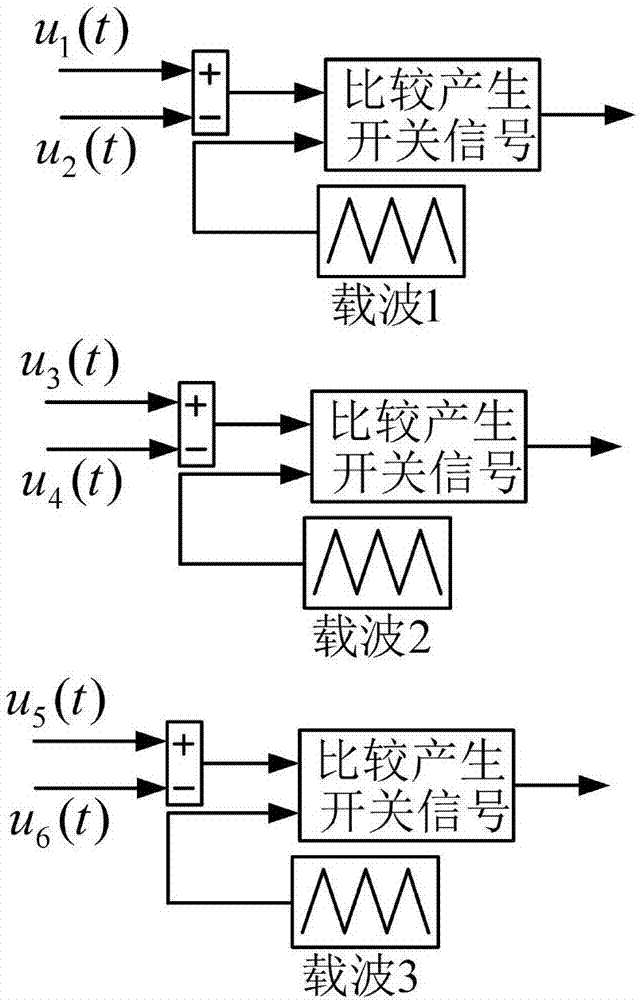

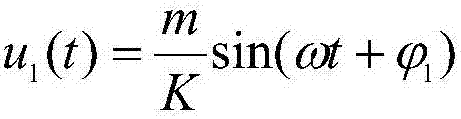

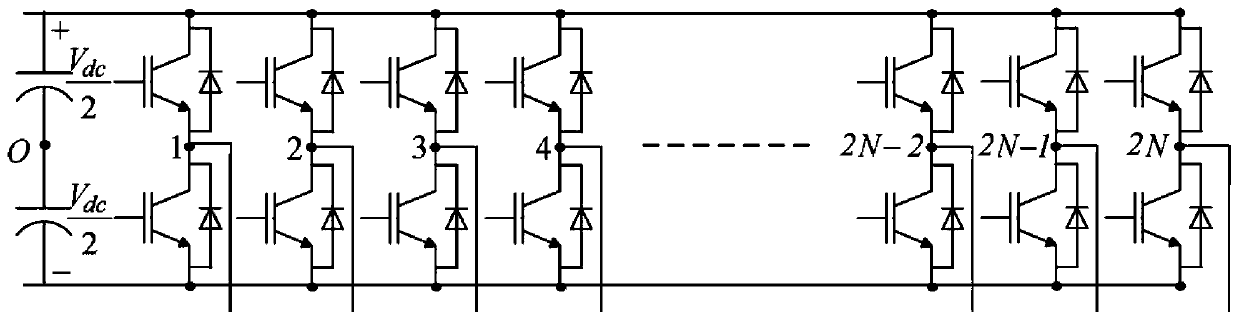

Polyphase motor driver control method

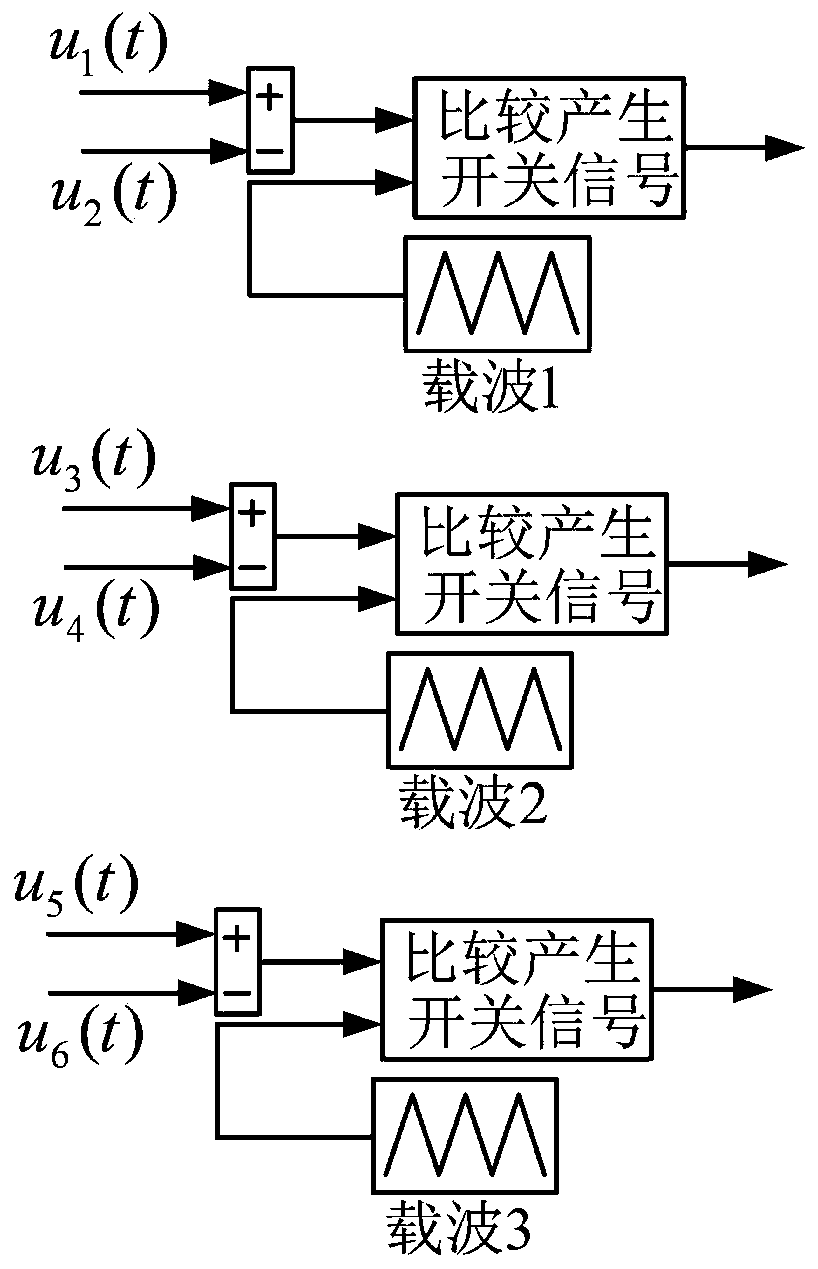

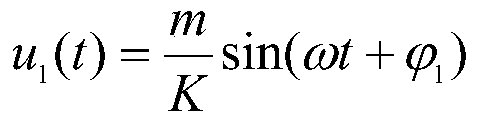

ActiveCN108011563AEliminate common mode voltageAC motor controlAc-dc conversionControl signalCarrier signal

The present invention provides a polyphase motor driver control method. The method comprises the steps that: a polyphase motor driver is formed by 2n-phase inverters, and n is a natural number, wherein a first-phase bridge arm and a second-phase bridge arm are controlled by a first module; a third-phase bridge arm and a fourth-phase bridge arm are controlled by a second module; a (2n-1)th-phase bridge arm and a 2nth-phase bridge arm are controlled by an nth module, and so on; in the control of the first module, a first modulation wave subtracts a second modulation wave, a difference of the first modulation wave and the second modulation wave is compared to a carrier wave to generate control signals of the first module; if the difference of the first modulation wave and the second modulation wave is larger than the first carrier wave 1, a first-phase bridge arm upper switch is conducted with a second-phase bridge arm lower switch, if a first-phase bridge arm current is smaller than 0, the first-phase bridge arm upper switch is switched off, and the second-phase bridge arm lower switch is only switched on; and if a second-phase bridge arm current is larger than 0, the second-phase bridge arm lower switch is switched off, and the first-phase bridge arm upper switch is switched on. Simple modulation wave operation and carrier wave comparison are employed to generate control signalsto eliminate a system common mode voltage.

Owner:YANSHAN UNIV

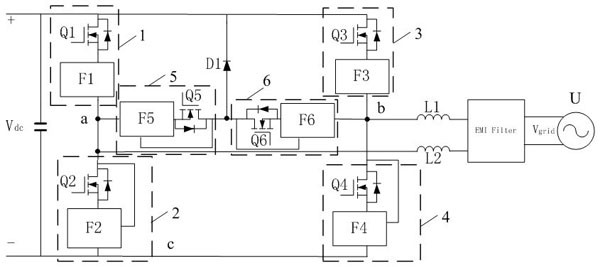

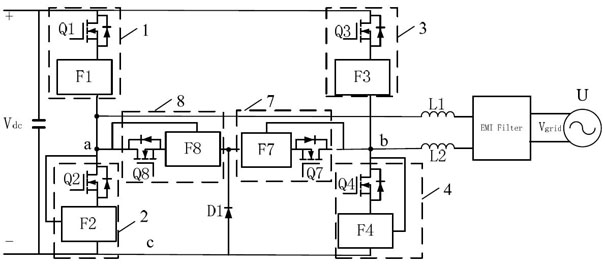

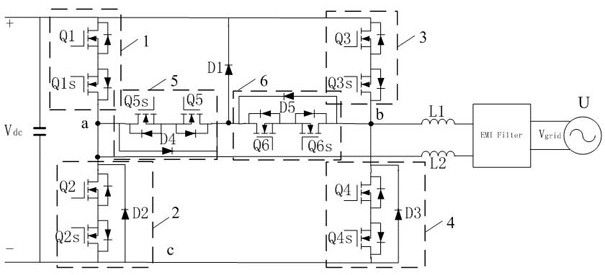

Single-phase three-level inverter circuit

The invention discloses a single-phase three-level inverter circuit which comprises a bus, a first power switch module 1, a second power switch module 2, a third power switch module 3, a fourth power switch module 4, a fifth power switch module 5, a sixth power switch module 6, a first diode D1, a first inductor L1 and a second inductor L2. Or the fifth power switch module 5 and the sixth power switch module 6 are replaced by a seventh power switch module 7 and an eighth power switch module 8. The first power switch module 1 to the eighth power switch module 8 respectively comprise a main power switch and an auxiliary circuit. The auxiliary circuit is unidirectionally conducted when the main power switch is conducted, and reverse current is prevented from flowing through the main power switch. The auxiliary circuit for protecting the main power switch is added, the main power switch is prevented from being attacked by reverse current, the service life of a device is prolonged, the stability of the circuit is improved, soft switching of the main power switch can be achieved, and the working efficiency of the inverter is improved.

Owner:浙江日风电气股份有限公司

A permanent magnet surface flow field sensor and sensor array

ActiveCN112684206BWon't breakReduce power consumptionFluid speed measurementSensor arraySurface mounting

Owner:BEIHANG UNIV +1

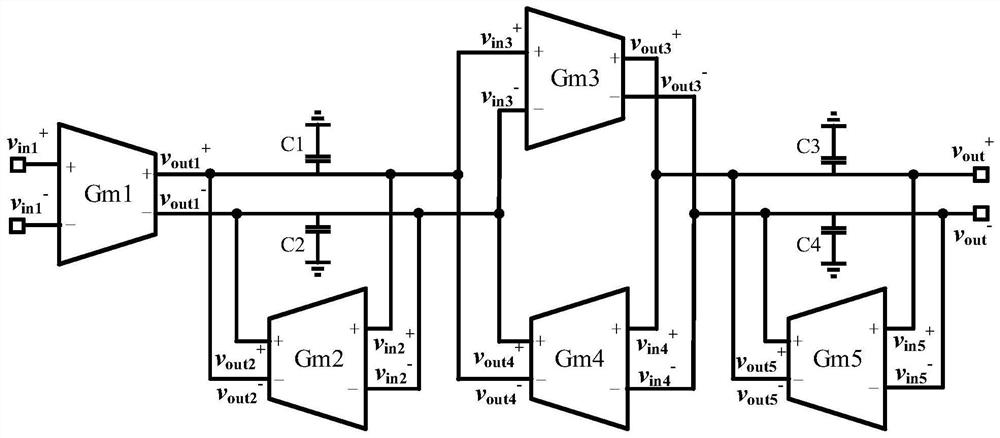

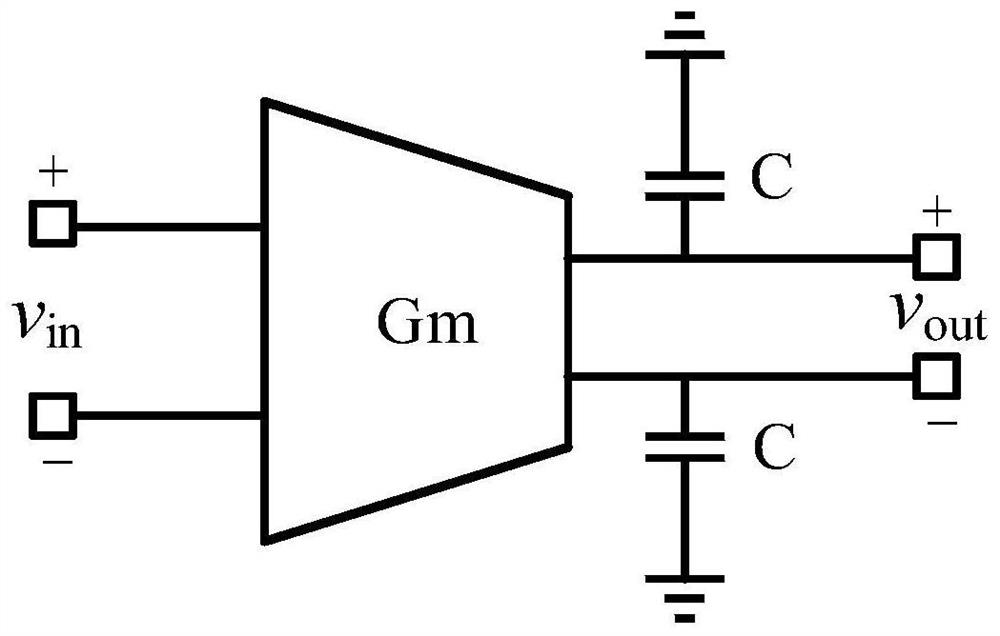

A low frequency fully differential gm-c filter applied to ecg signal acquisition

ActiveCN109787583BEliminate common mode voltageLower limitFrequency selective two-port networksEcg signalCapacitance

The invention relates to a low-frequency fully differential Gm-C filter applied to ECG signal acquisition. And the filter comprises a transconductance unit, a capacitor C1, a capacitor C2, a capacitorC3 and a capacitor C4, and the transconductance unit comprises a fully differential transconductance unit Gm1, a fully differential transconductance unit Gm2, a fully differential transconductance unit Gm3, a fully differential transconductance unit Gm4 and a fully differential transconductance unit Gm5. The improved source electrode negative feedback circuit is adopted, common-mode voltage on aresistor is effectively eliminated, the upper limit of input common-mode voltage is prevented from being reduced, and it is convenient to achieve that the output common-mode voltage is equal to the input common-mode voltage; The pseudo full-differential circuit based on the series-parallel current mirror is adopted, and a common-mode feedback circuit of a traditional full-differential circuit is prevented from being used for determining the output common-mode voltage, so that the complexity of circuit design is reduced, and the power consumption is reduced.

Owner:XIDIAN UNIV

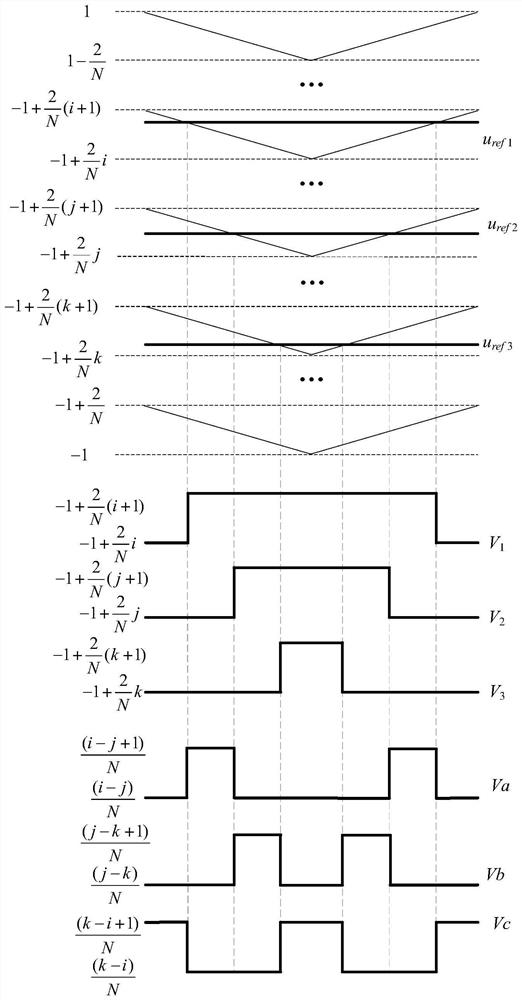

Modulation method of multilevel inverter without common mode voltage

ActiveCN110048627BEliminate the effects ofEliminate common mode voltageAc-dc conversionSingle network parallel feeding arrangementsInverter topologyCarrier signal

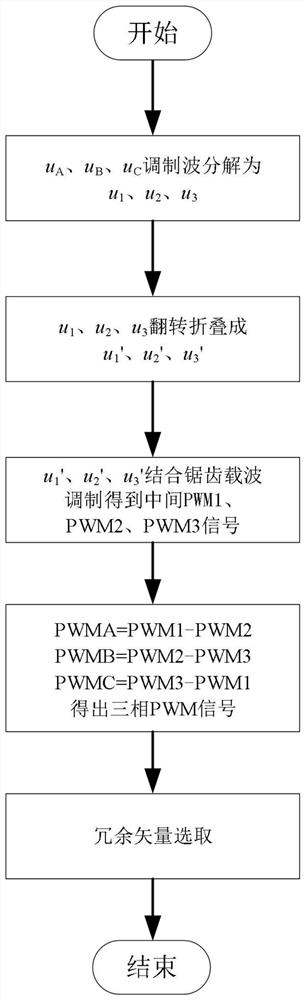

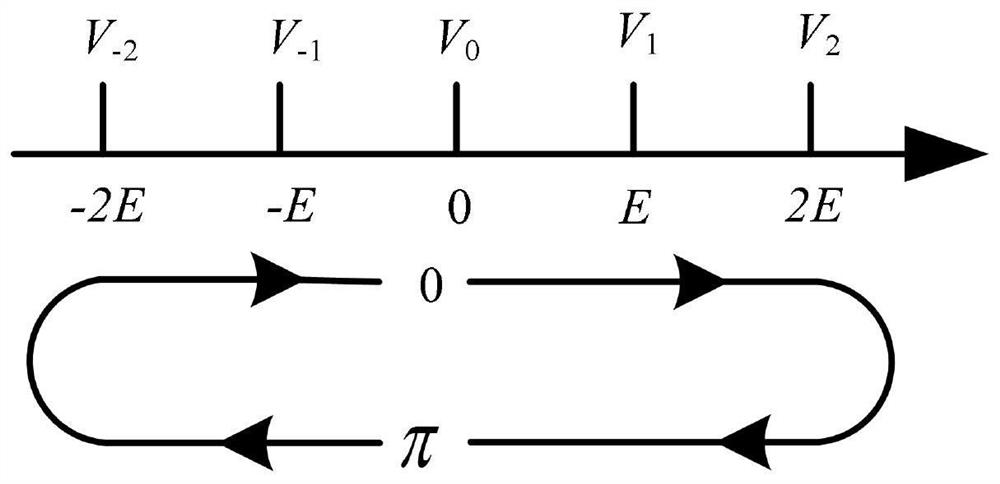

The invention provides a modulation method of a multi-level inverter without common-mode voltage, belonging to the technical field of multi-level inverter modulation. The modulation method comprises the steps that modulating wave is decomposed, and every two phases of the decomposed modulating wave are subtracted from each other to obtain original modulating wave; the decomposed modulating wave issubjected to one-dimensional space vector modulation to obtain the action vector for synthesizing the modulating wave and the corresponding action time of the vector; by being compared with the sawtooth carrier, the vector with small modulus in one carrier period of the positive half period is output first, and the vector with large modulus in the negative half period is output first to obtain intermediate PWM signals; a three-phase PWM signal is obtained by subtracting every two phases of the intermediate PWM signals; and redundant vectors are selected according to the actual needs of different topologies. The modulation method eliminates the common mode voltage, eliminates the influence of the leakage current on the grid-connected current, and improves the waveform quality. Compared with the traditional SVPWM modulation strategy, two-dimensional simplification is changed to one-dimensional simplification, sector judgment and vector action time are simplified, without trigonometric function operation, and the computational effort is small. The method has high versatility for different inverter topologies.

Owner:BEIJING JIAOTONG UNIV

An AC and DC power supply system

ActiveCN113258620BEliminate common mode voltageReliable power supplyPower conversion systemsAC - Alternating currentControl engineering

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

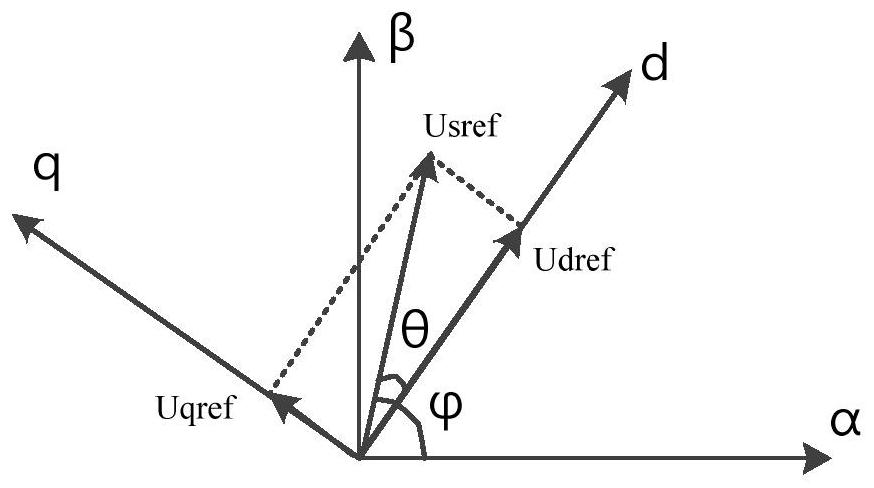

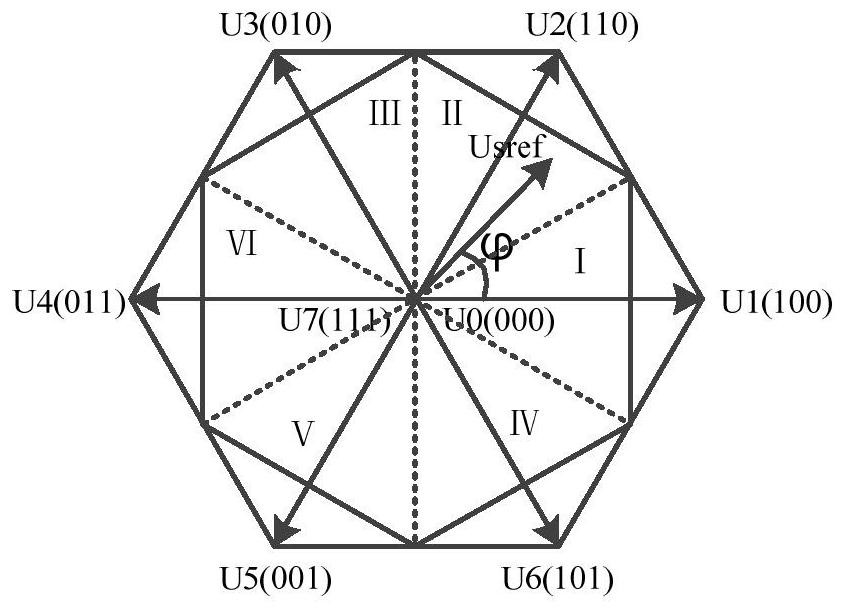

Method for suppressing common-mode voltage in SVPWM (Space Vector Pulse Width Modulation) modulation of three-phase two-level inverter

PendingCN114389473AHarmonic reductionAvoid damageElectronic commutation motor controlAC motor controlPhase currentsVoltage vector

The invention discloses a method for inhibiting common-mode voltage in SVPWM (Space Vector Pulse Width Modulation) modulation of a three-phase two-level inverter, which comprises the following steps of: obtaining expected d-q shafting voltage Udref and Uqref through a current loop, and obtaining an included angle theta between a d axis and an alpha axis through a motor position or a speed sensor; according to the Udref, the Uqref and the theta, calculating to obtain an expected reference voltage vector amplitude Usref and an included angle between the Usref and the alpha axis, judging a sector S where the Usref is located according to the included angle, and looking up a table according to the sector S to obtain three unit vectors Ux, Uy and Uz which need to be used and have a fixed action sequence; according to the volt-second balance principle, the action time Tx, Ty and Tz of the unit vectors Ux, Uy and Uz is obtained through calculation, and Tult is calculated; the part of Ty is eliminated, the part of Tmin is eliminated, Ty is made to be equal to Tmin, and Tmin is dead time; and SVPWM output is carried out by adopting a decreasing symmetric five-section mode. Under the condition that hardware cost is not increased, the problem that + / -Udc / 2 peaks appear in common-mode voltage in PWM modulation can be effectively suppressed, and the problem that a motor bearing is damaged by higher harmonics of three-phase current is obviously solved.

Owner:武汉理工通宇新源动力有限公司

MMC suppression common mode voltage modulation method and system suitable for even number of sub-modules

ActiveCN112039322BAvoid damageReduce common mode voltageAc-dc conversionPhotovoltaicsCapacitanceVoltage vector

The invention discloses a modulation method and a system for suppressing a common-mode voltage by an MMC suitable for an even number of sub-modules, and belongs to the field of electric power. Including: converting the three-phase reference voltage analog linear operation into three reference line voltage analogs injected into the zero-sequence component; for MMC with 2N sub-modules, combining the three reference line voltage analogs with N carrier waves stacked in phase Carrier comparison is performed separately to obtain three driving signal digital quantities; the three driving signal digital quantities are linearly transformed into three-phase reference voltage digital quantities of MMC; the three-phase reference voltage digital quantities of MMC are distributed to sub-modules to control MMC, Get the drive signals of all the switch tubes in the MMC. The present invention equivalently realizes the transmission of zero common-mode voltage vector through the addition and subtraction of carrier comparison, greatly reduces the common-mode voltage, suppresses the common-mode current coupled by stray capacitive coupling, and is simple to implement, avoiding the reference of the traditional method based on space vector synthesis Complicated calculations such as vector positioning.

Owner:HUAZHONG UNIV OF SCI & TECH

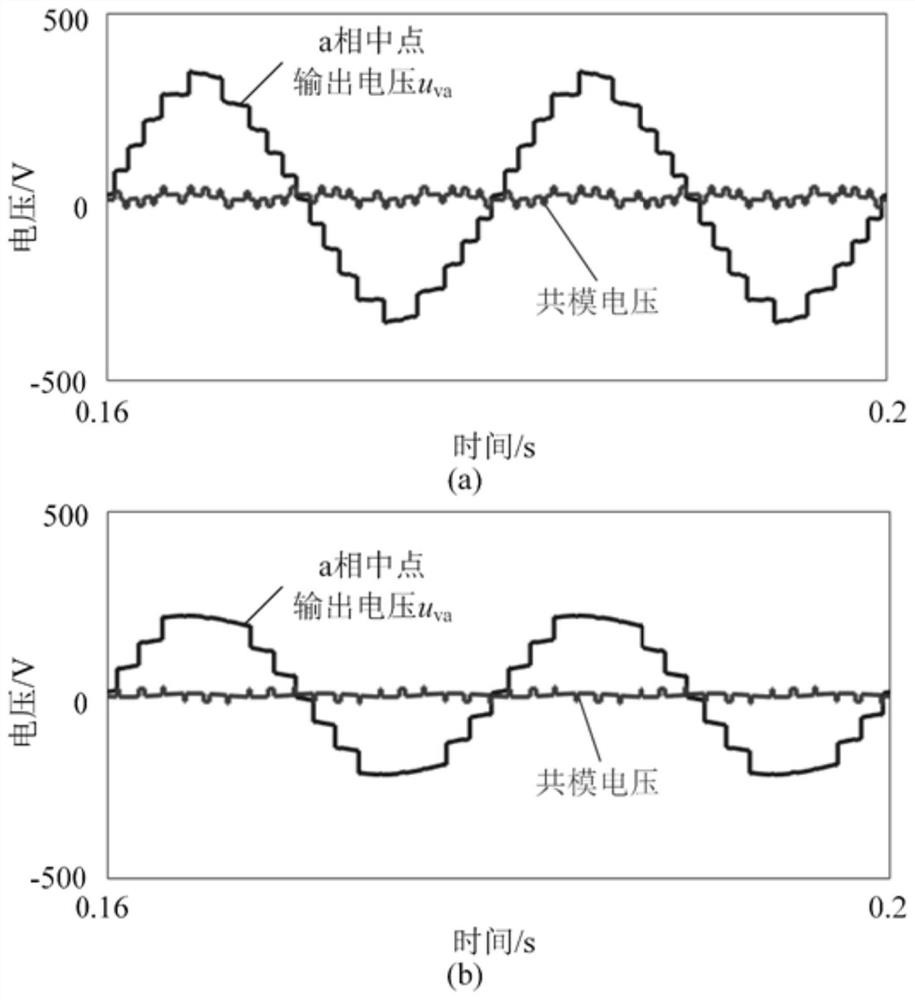

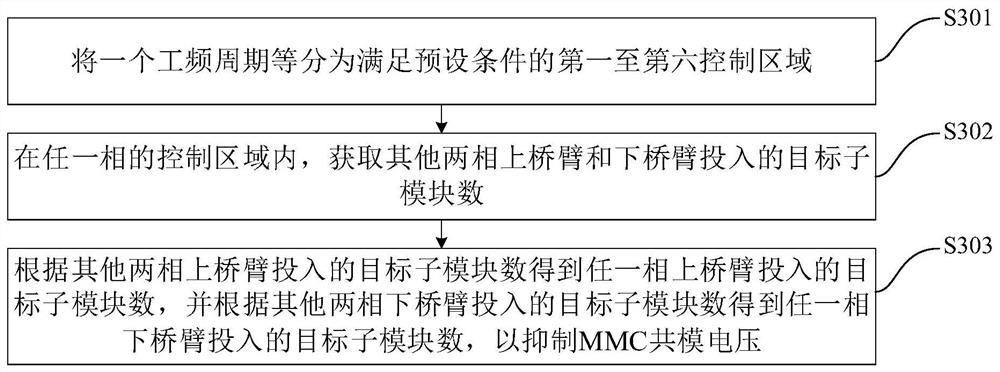

Six-segment nearest level approximation modulation method to eliminate mmc common mode voltage

ActiveCN110739875BEliminate common mode voltageReduce common mode noiseAc-dc conversionCapacitanceCommunications system

The invention discloses a six-segment nearest-level approach modulation method for eliminating the common-mode voltage of an MMC (modularmultilevelconverter, modular multilevel converter), which includes: dividing a power frequency cycle into equal parts that meet preset conditions. The first to sixth control areas; within the control area of any phase, obtain the target number of sub-modules input into the upper bridge arm and the lower bridge arm of the other two phases; obtain any phase The target number of sub-modules put into the upper bridge arm, and the target number of sub-modules put into the lower bridge arm of any phase are obtained according to the target number of sub-modules put into the lower bridge arm of the other two phases, so as to suppress the common mode voltage of the MMC. This method can eliminate common-mode voltage, effectively reduce system leakage current and common-mode noise, and effectively solve the problem of high-frequency common-mode voltage in existing MMCs, which can generate leakage current and common-mode interference through stray capacitance, which endangers motor bearings and communications. system technical issues.

Owner:BEIJING JIAOTONG UNIV

A multi-phase motor driver control method

ActiveCN108011563BEliminate common mode voltageAC motor controlAc-dc conversionControl signalElectric machine

The present invention relates to the field of motor drivers, in particular to a method for controlling a multi-phase motor driver. The multi-phase motor driver is composed of 2n-phase inverters, where n is a natural number, wherein the first and second phase bridge arms are controlled by the first module; 3. The 4-phase bridge arm is controlled by the second module; and so on, the 2n-1, 2n-phase bridge arm is controlled by the nth module; in the control of the first module, the first modulation wave and the second modulation wave are subtracted, and then combined with The first carrier compares to generate the control signal of the first module; when the difference between the first modulation wave and the second modulation wave is greater than the first carrier 1, the upper switch of the first phase bridge arm and the lower switch of the second phase bridge arm are turned on, at this time If the current of the first phase bridge arm is less than 0, the upper switch of the first phase bridge arm is turned off, and only the lower switch of the second phase bridge arm is turned on; at this time, if the current of the second phase bridge arm is greater than 0, the second phase bridge arm The lower switch is turned off, and only the upper switch of the first phase bridge arm is turned on. The present invention can eliminate the system common mode voltage only by modulating wave operation and carrier comparison to generate control signals.

Owner:YANSHAN UNIV

Three-level zero common-mode voltage modulation method based on DSP (digital signal processor) and CPLD (complex programmable logic device)

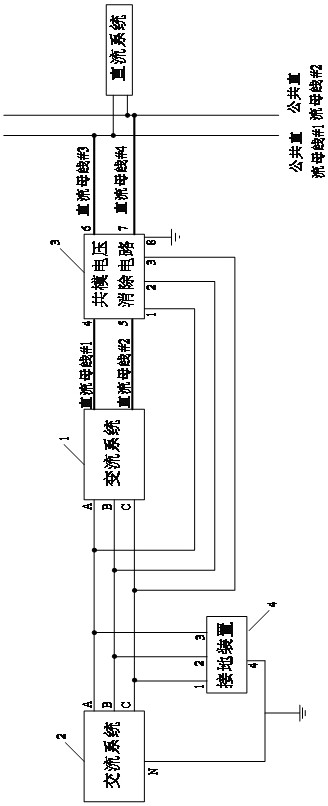

InactiveCN102739091AModulation method is simpleEasy to implementAc-dc conversionDigital signal processingCapacitance

The invention discloses a three-level zero common-mode voltage modulation method based on a DSP (digital signal processor) and a CPLD (complex programmable logic device). PWM (pulse-width modulation) pulse wave modulated by two levels is distributed and adjusted to produce a group of median vector on-off states effective for a three-level inverter, and three-level median vector combination is directly adopted for directly controlling a three-level main circuit to achieve the purpose that the output common-mode voltage is zero. The modulation method is simple and easy to implement without any additional hardware circuits, and applicable to any modulation wave. All output common-mode voltages are zero so as to eliminate leakage current caused by common-mode voltage and drain capacitance, and fundamentally eliminate the common-mode voltage.

Owner:HEFEI UNIV OF TECH

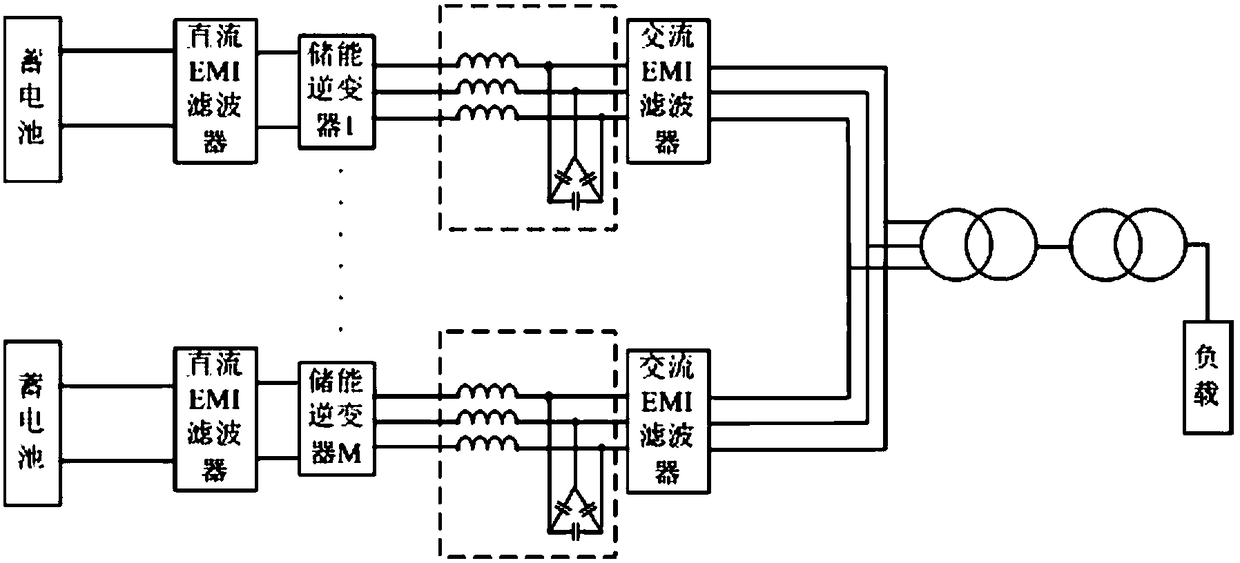

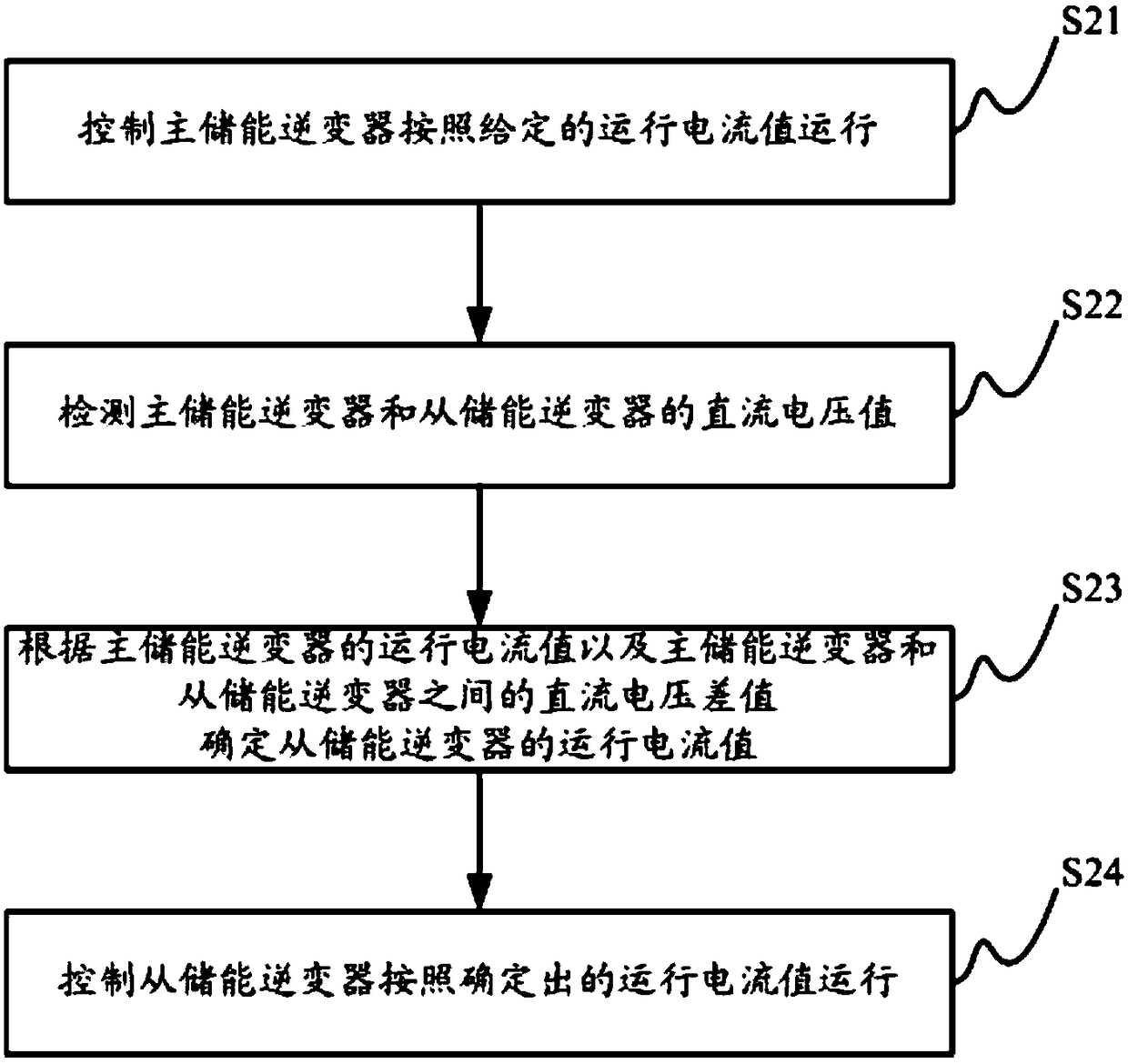

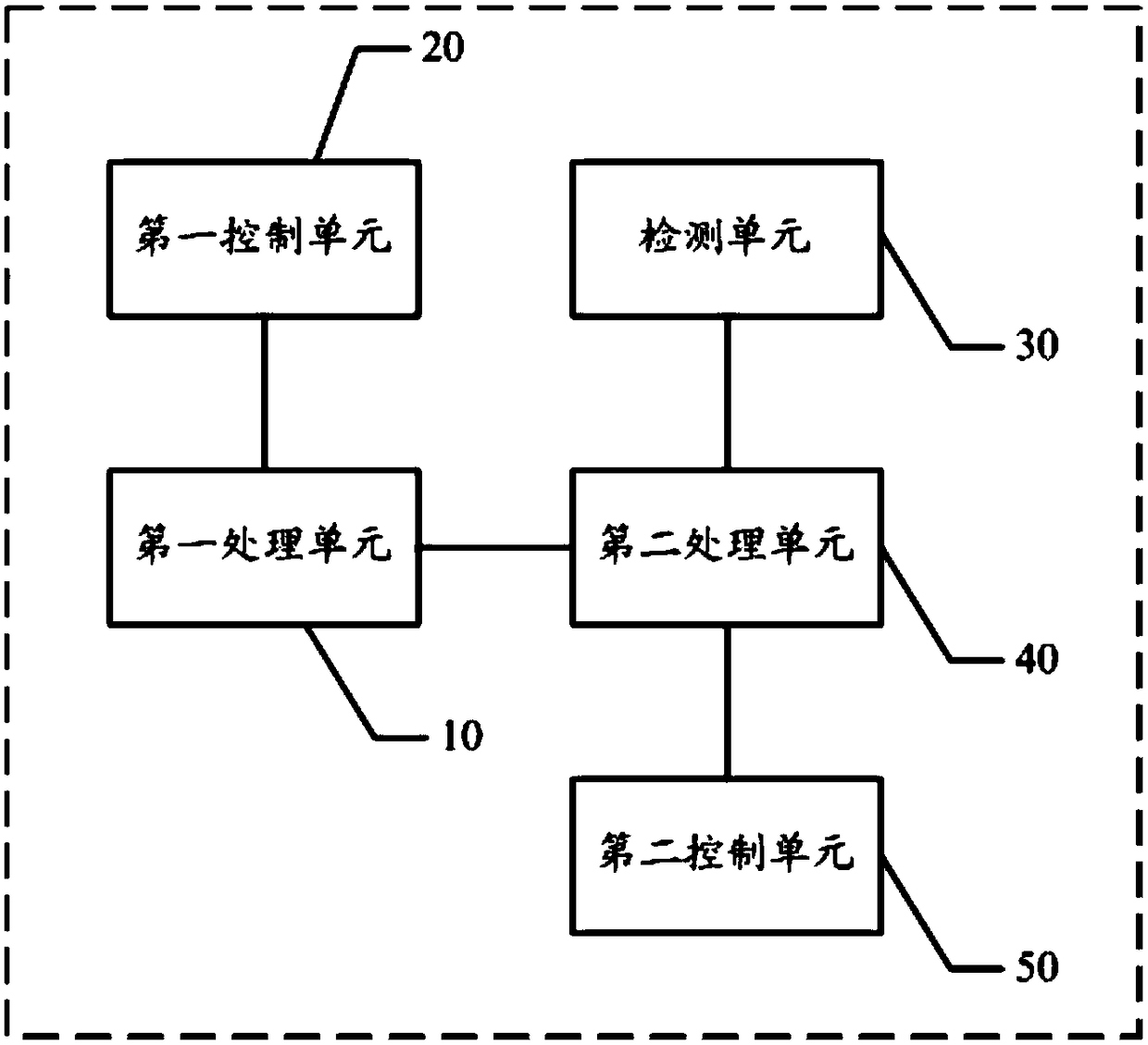

Control method and control device for off-grid parallel system of energy storage inverters

ActiveCN106159935BReduce common mode voltageEliminate common mode voltageDc source parallel operationPower inverterEnergy storage

Owner:SUNGROW POWER SUPPLY CO LTD