Common-mode voltage elimination method based on parallel driver topological structure

A topology and common-mode voltage technology, applied in electrical components, output power conversion devices, AC power input to DC power output, etc., can solve the problem of small switching loss, achieve the elimination of common-mode voltage and reduce damage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] There is a lot of research on common-mode voltage cancellation, but it is only 20 years old, so the technology is not perfect, and there is still a lot to continue to research and learn. Based on the prior art, the present invention proposes innovative assumptions and modulation techniques, further improves the original method for eliminating common-mode voltage, reduces switching loss, and eliminates common-mode voltage.

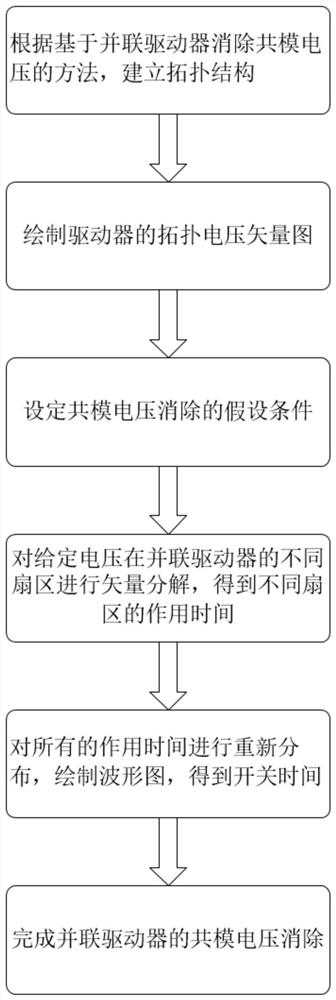

[0028] The present invention is a common-mode voltage elimination method based on parallel driver topology, see figure 1 , including the following steps:

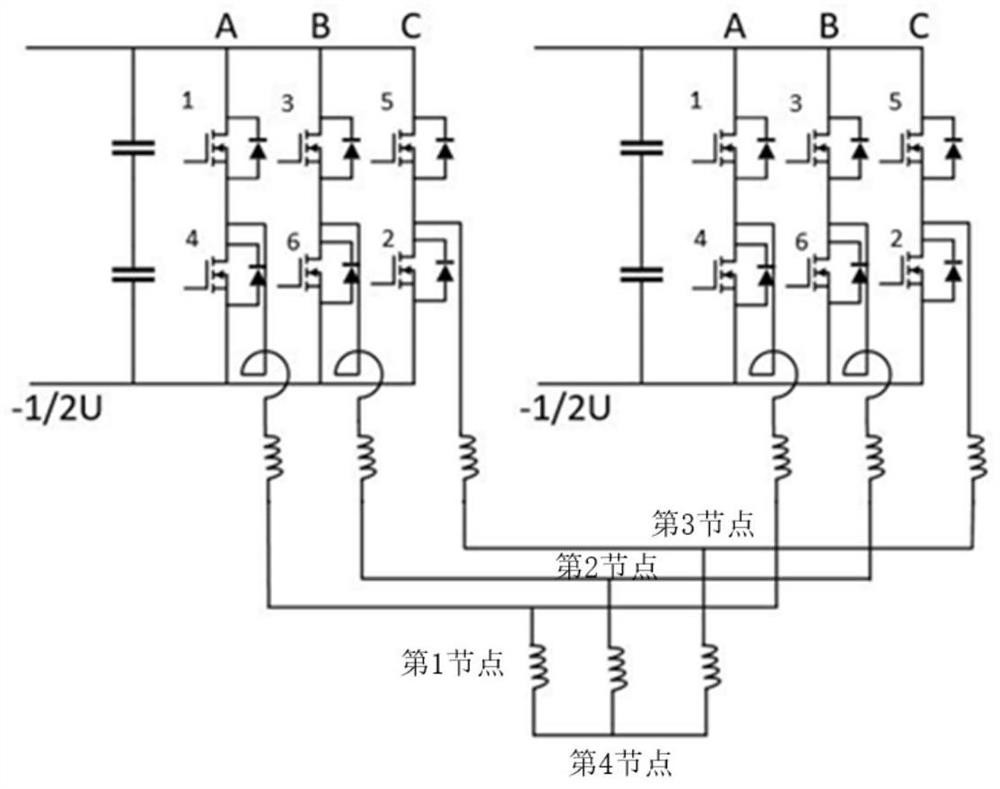

[0029] Step 1: establish topological structure: the topological structure of the present invention originates from two drivers that are formed in parallel, see figure 2 , figure 2is the circuit structure diagram of the parallel driver, figure 2 The voltages generated by the two drivers are equal in magnitude and opposite in direction. Each driver is sequentially connected with three bridge ...

Embodiment 2

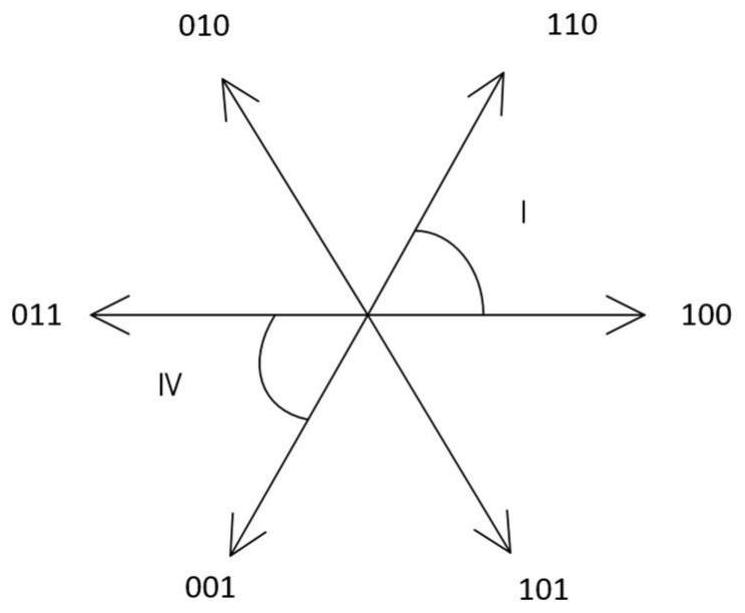

[0041] The common-mode voltage elimination method based on the parallel driver topology is the same as that in Embodiment 1. The vector decomposition of the given voltage in different sectors of the parallel driver described in step 4 of the present invention is to substitute the assumed conditions into the voltage vector decomposition expression decomposition calculation. , to obtain the action time of a given voltage in different sectors, taking the voltage of the first sector as an example, including the following steps:

[0042] (4.1) Decompose the given voltage vector to obtain the decomposition expression: the first sector voltage vector

[0043] The solution expression is:

[0044]

[0045] x 1 +x 3 = 0.5;

[0046] x 2 +x 4 =0.5

[0047] in: For a given voltage, x 1 、x 2 、x 3 、x 4 For the four action times of the given voltage after the decomposition of the first sector, is the voltage vector decomposed by a given voltage in the first sector and the two...

Embodiment 3

[0061] The common-mode voltage elimination method based on the topology of parallel drivers is the same as in embodiment 1-2, redistribute all the action time described in step 5, draw the waveform diagram, and obtain the switching time, which is the given voltage vector obtained in step 4 The decomposed action time is combined with the carrier to obtain the switching time based on the parallel driver topology, and the linear relationship between the given voltage vector and action time obtained in step 4 is substituted into the switching time to obtain the mathematical expression of the given voltage vector and switching time The formula is an innovative modulation technique proposed by the present invention. Taking the first sector as an example, it includes the following steps:

[0062] (5.1) The action time x after decomposing the given voltage vector calculated in step 4 1 、x 2 、x 3 、x 4 Combining with the carrier, draw the ladder diagram, and get the switching time a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More