Three-level zero common-mode voltage modulation method based on DSP (digital signal processor) and CPLD (complex programmable logic device)

A technology of common-mode voltage and modulation method, which is applied in the field of three-level zero-common-mode voltage modulation, and can solve problems such as failure to fundamentally eliminate common-mode voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] Such as Figure 7 Shown, a kind of three-level zero-common-mode voltage modulation method based on DSP and CPLD comprises the following steps:

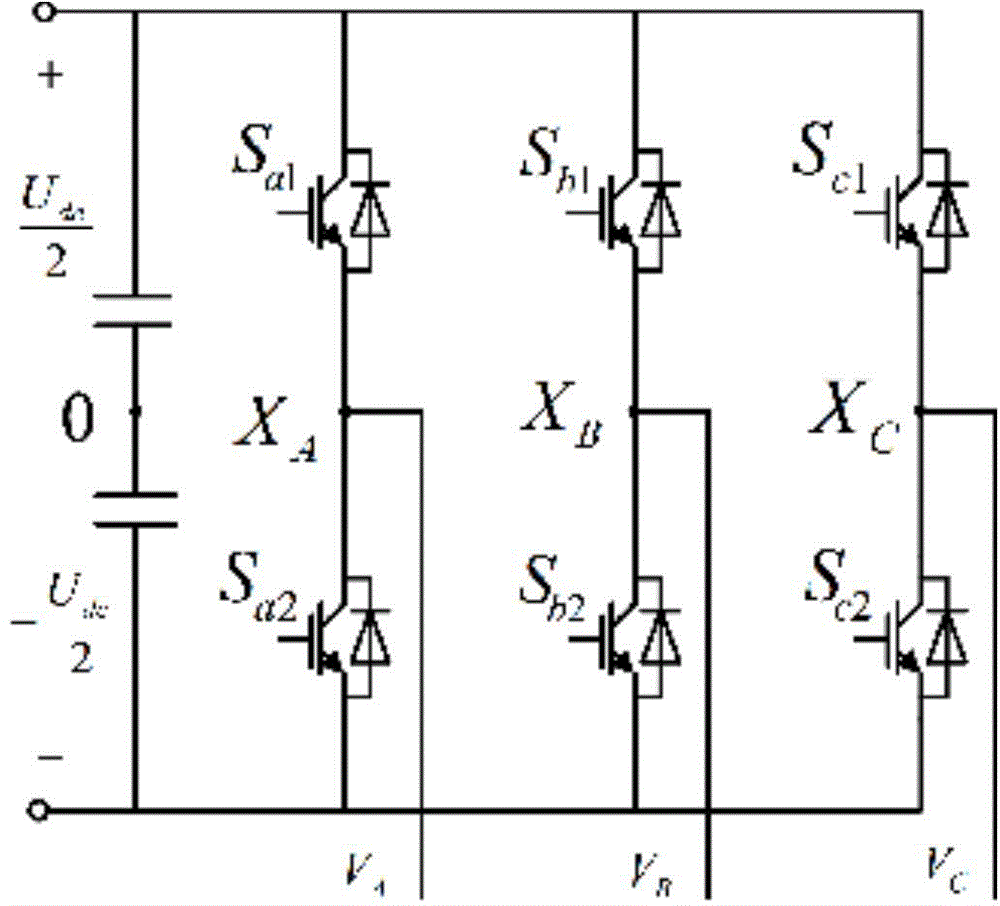

[0067] (1) Use DSP1 to perform two-level modulation to modulate two complementary 6-way two-level PWM signals, and mark the signals as EPWM1 to EPWM6, where EPWM1 and EPWM2 are complementary, EPWM3 and EPWM4 are complementary, and EPWM5 and EPWM6 are complementary;

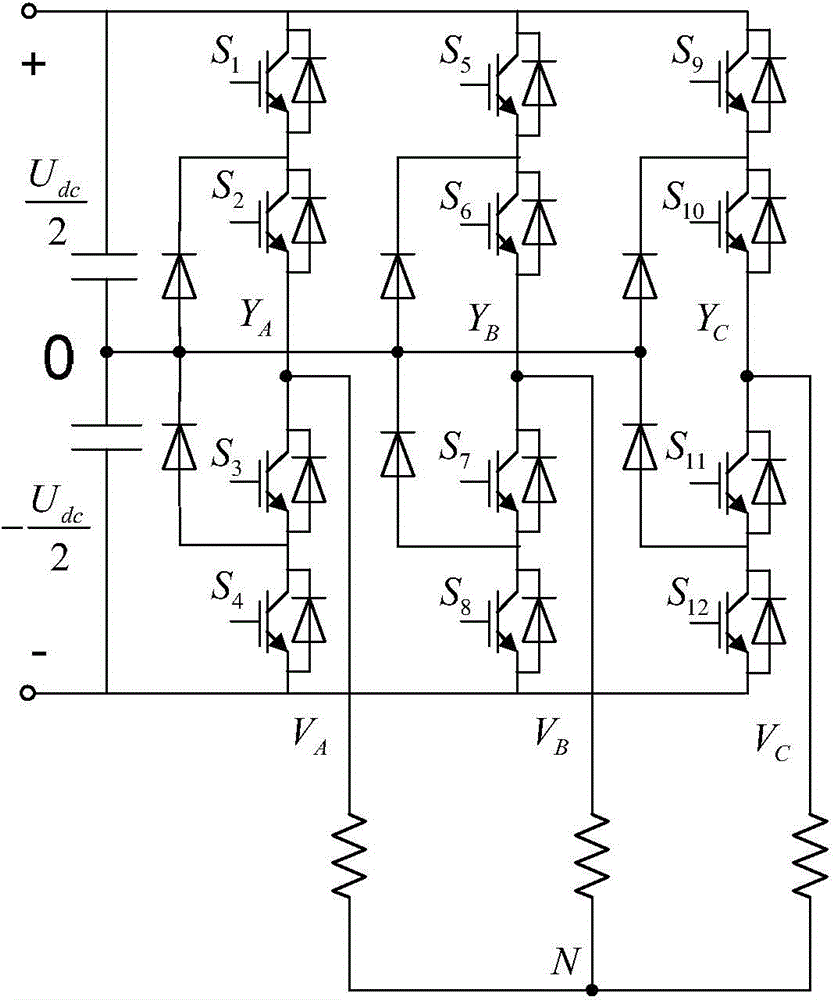

[0068] (2), the 6-way two-level PWM signals generated by DSP1 are passed to CPLD2 through external pins, and CPLD2 adjusts the 6-way two-level PWM signals to generate 12-way PWM signals, and mark the 12-way signals respectively For PWM1 to PWM12;

[0069] Assign values to PWM1-PWM4: When the EPWM1 and EPWM3 signals generated by DSP1 in step (1) are not low at the same time, implement the following distribution method: PWM1 takes the signal of EPWM4, PWM2 takes the signal of EPWM1, and PWM3 takes the signal of EPWM3 Signal, PWM4 takes the signal of EPWM2; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More