A message acceleration method and device for software and hardware coordination

A technology of software-hardware collaboration and hardware acceleration, applied in the field of communication, can solve problems such as high design requirements, high design cost, increased chip power consumption, etc., and achieve the effect of message classification control and unified management

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

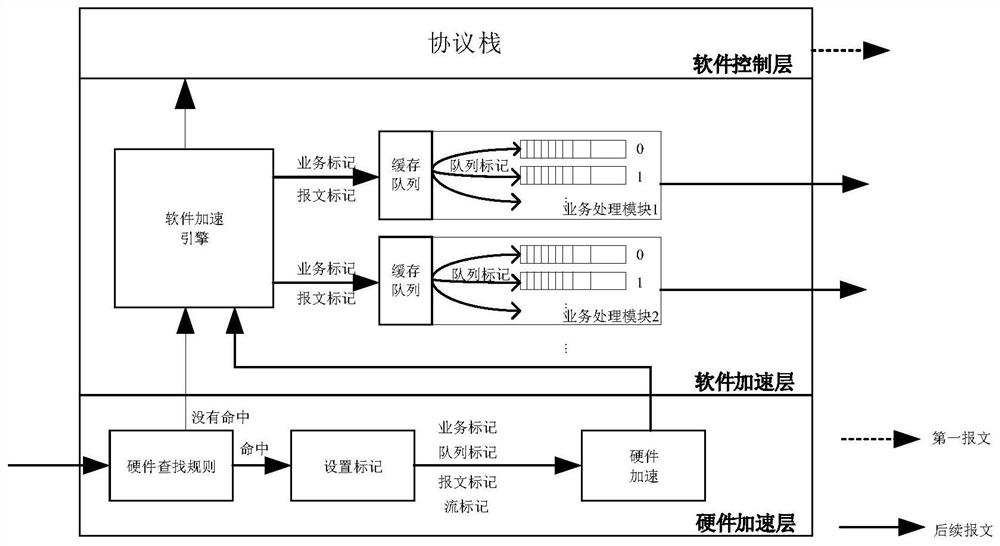

[0068] This implementation provides a software-hardware coordinated message acceleration method. The hardware acceleration layer is responsible for accelerating the L2-L3 layers of the message, and the software acceleration layer is responsible for accelerating the L4-L7 layers of the message. The software acceleration layer and the hardware acceleration layer Cooperate with each other to accelerate the L2-L7 layer of the message, which greatly improves the efficiency of message acceleration.

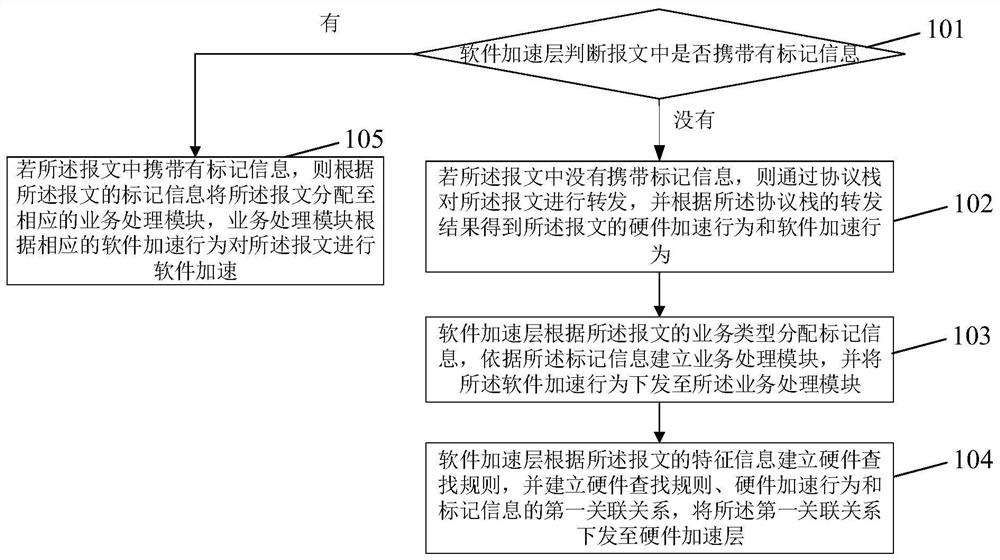

[0069] Combine below figure 1 , specifically illustrating the implementation process of the message acceleration method of this embodiment, the message acceleration method includes the following steps:

[0070] Step 101: The software acceleration layer judges whether the packet carries tag information.

[0071] In this embodiment, according to the order in which the messages are generated, the messages can be divided into two types: the first message and the follow-up message, wherein ...

Embodiment 2

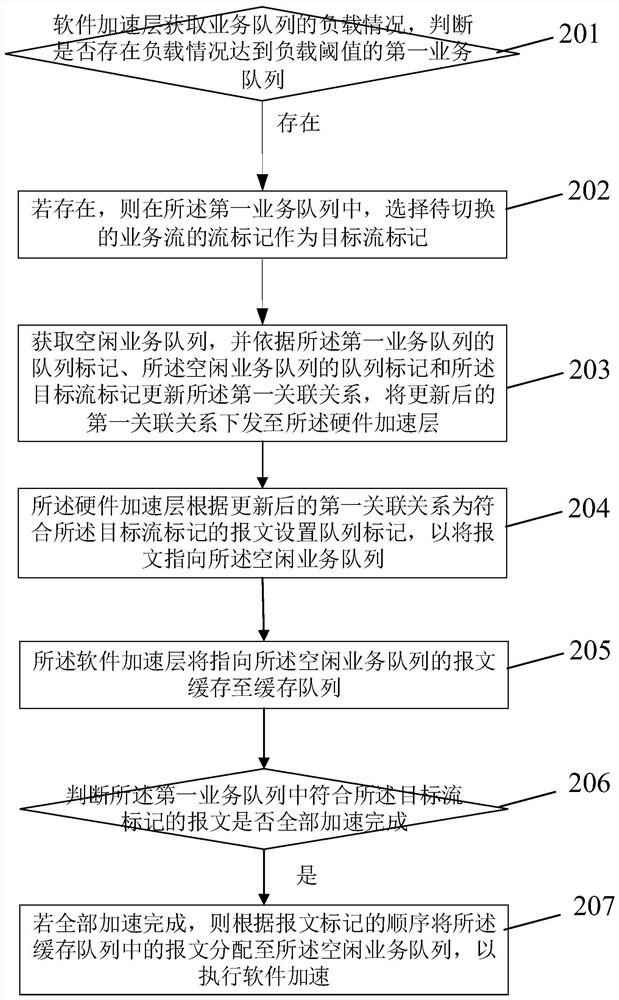

[0101] In practical application scenarios, in order to ensure load balance between service queues, when a service queue is overloaded, the service flow needs to be switched to an idle service queue, and out-of-sequence problems are prone to occur in the process of switching queues.

[0102] In order to solve the out-of-sequence problem during service switching, this embodiment provides another packet acceleration method in combination with the foregoing embodiment 1. In this embodiment, the label information also includes a flow label, and the flow label is used to distinguish different service flows, wherein the packets conforming to the same hardware search rule belong to the same service flow and have the same flow label . The hardware acceleration layer also sets a message mark for the message, wherein, in the same service flow, the message mark is unique and is used to mark different messages.

[0103] In practical application scenarios, the service processing module is ...

Embodiment 3

[0119] see Figure 4 , Figure 4 It is a schematic structural diagram of a message acceleration device provided by an embodiment of the present invention. The packet acceleration device in this embodiment includes one or more processors 41 and a memory 42 . in, Figure 4 A processor 41 is taken as an example.

[0120] Processor 41 and memory 42 can be connected by bus or other means, Figure 4 Take connection via bus as an example.

[0121] The memory 42, as a non-volatile computer-readable storage medium based on the attack message acceleration method, can be used to store non-volatile software programs, non-volatile computer-executable programs and modules, the methods and corresponding program instructions. The processor 41 executes various functional applications and data processing by running non-volatile software programs, instructions and modules stored in the memory 42 to implement the methods of the foregoing embodiments.

[0122]Wherein, the memory 42 may incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More