AXI bus based convenient configurable frame data access control system

An access control and bus control technology, which is applied in electrical digital data processing, instruments, etc., can solve the problems of complex operation and low overall system performance, and achieves the improvement of data transmission rate, simplification of multiple handshake operations, and convenient access methods. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

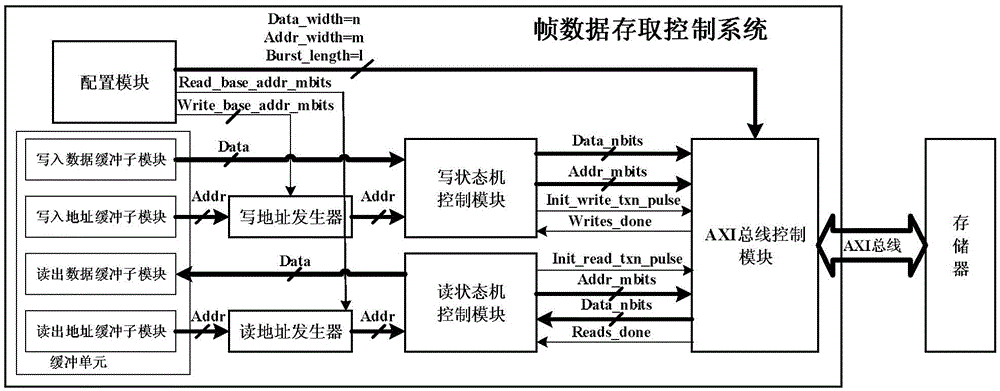

[0032] Specific embodiment one: the configuration module of this embodiment, buffer module namely FIFO module, write address generator module, read address generator module, read state machine control module, write state machine control module and AXI bus control module;

[0033] Wherein, the configuration module is input by the user to configure the parameters of the write address generator module, the read address generator module and the AXI bus control module;

[0034] The parameters are:

[0035] The data bit width data_width is n, the address bit width addr_width is m, and the number of transmission rounds burst_length is l;

[0036] The data bit width n determines the data width transmitted by the AXI bus;

[0037] The address bit width m determines the storage depth of the memory as 2 m bits;

[0038] The configurable range of l is: 1, 2, 4, 8, 16, 32, 64, 128 and 256. This parameter indicates the number of data continuously transmitted without interval during each ...

specific Embodiment approach 2

[0050] Specific embodiment two: the difference between this embodiment and specific embodiment one is: described configuration module is connected with write address generator module, read address generator module and AXI bus control module, carries out read and write address and AXI bus transmission parameter configuration ;

[0051] The buffer module is connected with the write state machine control module and the read state machine control module, and buffers the read and write data and addresses;

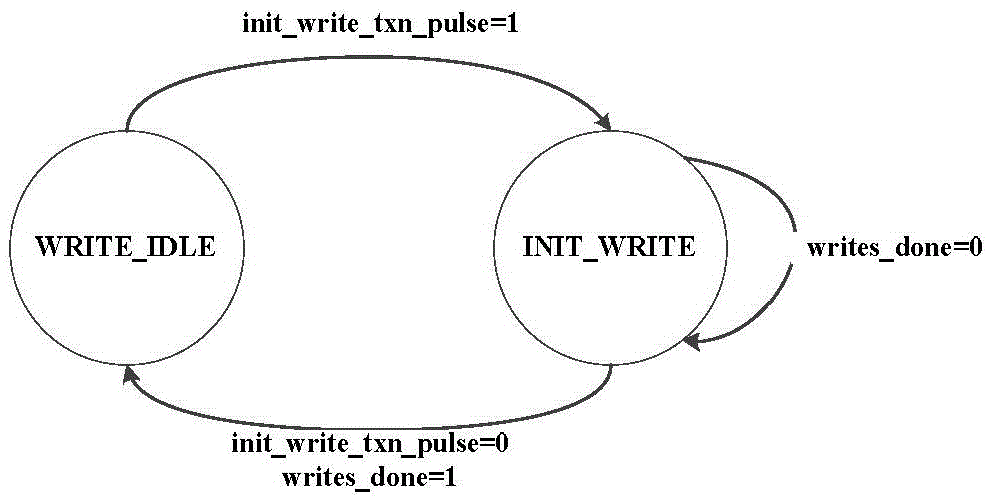

[0052] The write state machine control module and the read state machine control module are connected with the AXI bus control module to realize the interaction of data, address and other handshake signals with the AXI bus;

[0053] The entire system access control system is connected with the external memory through the AXI bus to realize the high-speed data access buffer function.

[0054] Other steps and parameters are the same as those in Embodiment 1.

specific Embodiment approach 3

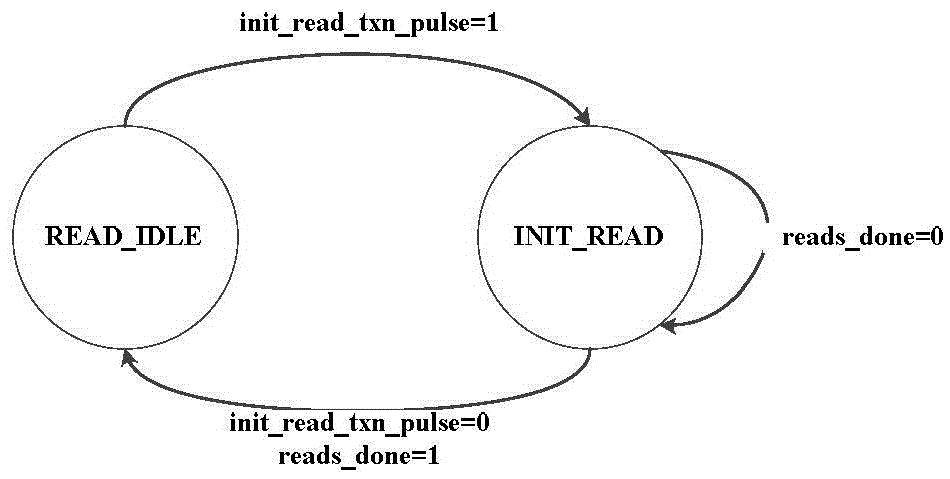

[0055] Specific implementation mode three: the difference between this implementation mode and specific implementation mode one or two is that: the reading sequence of the AXI bus burst transmission controlled by the read state machine control module is specifically:

[0056] The reading sequence of the read state machine control module controlling AXI bus burst transmission is specifically:

[0057] The read state machine control module starts the "read" state when it is not empty, writes the address in the read address buffer submodule to the AXI bus, and reads the data on the corresponding address in the memory to the read data buffer submodule Among them, the data transmission adopts the AXI bus burst transmission, that is, it does not need to take the address from the read address buffer submodule again, but uses the method of automatically adding 1 to the address to read l data at a time;

[0058] The read state machine control module contains two states: READ_IDLE and I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More