System and method used for field-programmable gate array chip file loading

A file loading and gate array technology, applied in the communication field, can solve problems such as complex implementation process, low file loading rate, and inability to dynamically continue, and achieve the effect of simple process and improved loading efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

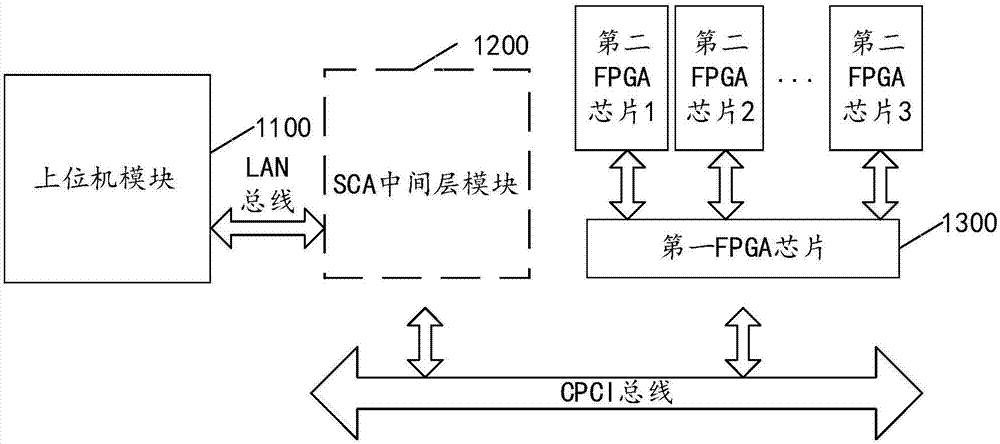

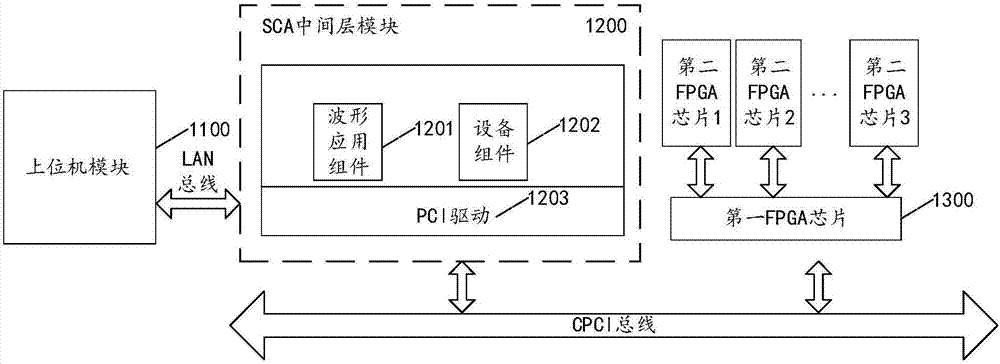

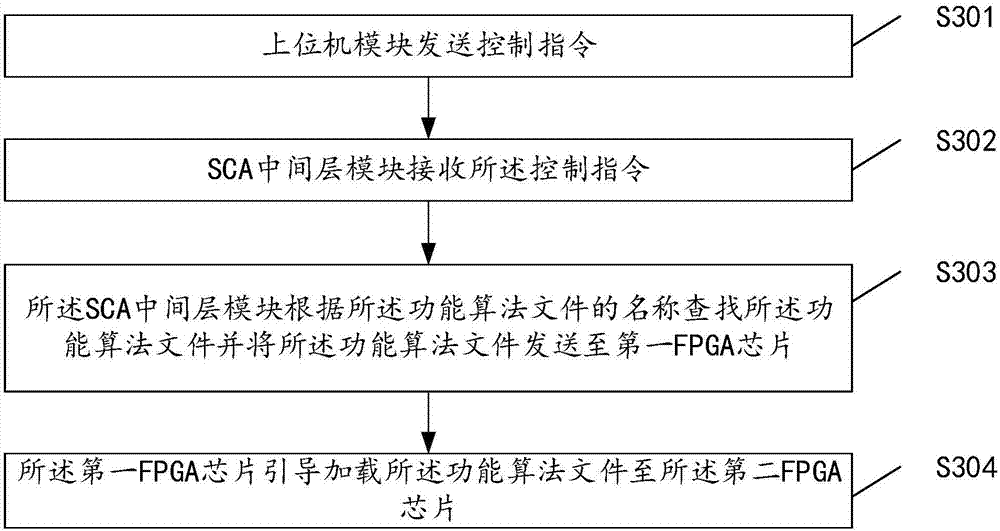

[0023] The following description and drawings illustrate specific embodiments of the invention sufficiently to enable those skilled in the art to practice them. The examples merely represent possible variations. Individual components and functions are optional unless explicitly required, and the order of operations may vary. Portions and features of some embodiments may be included in or substituted for those of other embodiments. The scope of embodiments of the present invention includes the full scope of the claims, and all available equivalents of the claims. Herein, various embodiments may be referred to individually or collectively by the term "invention", which is for convenience only and is not intended to automatically limit the scope of this application if in fact more than one invention is disclosed. A single invention or inventive concept. Herein, relational terms such as first and second etc. are used only to distinguish one entity or operation from another with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More