A cake-type integrated circuit layout method and system for chips

A technology of integrated circuits and layout methods, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve the problems of increasing the difficulty of chip area reduction, affecting the aesthetics of chip layout, and increasing the difficulty of integrated circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

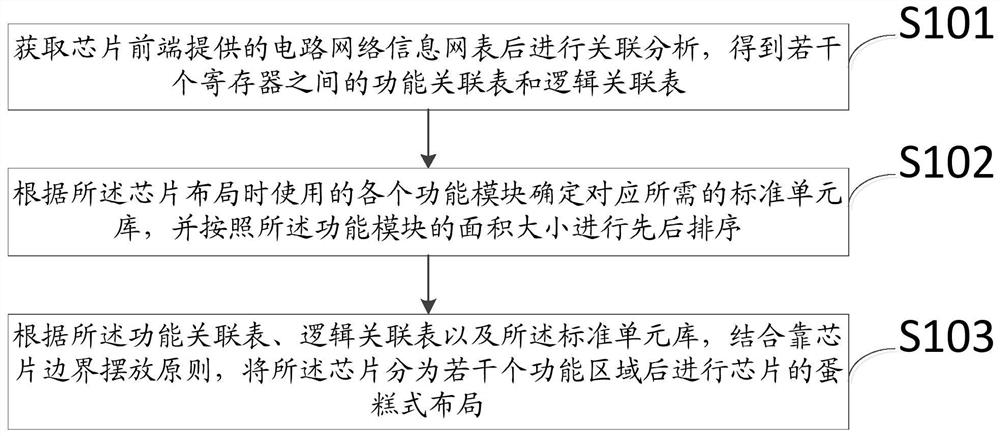

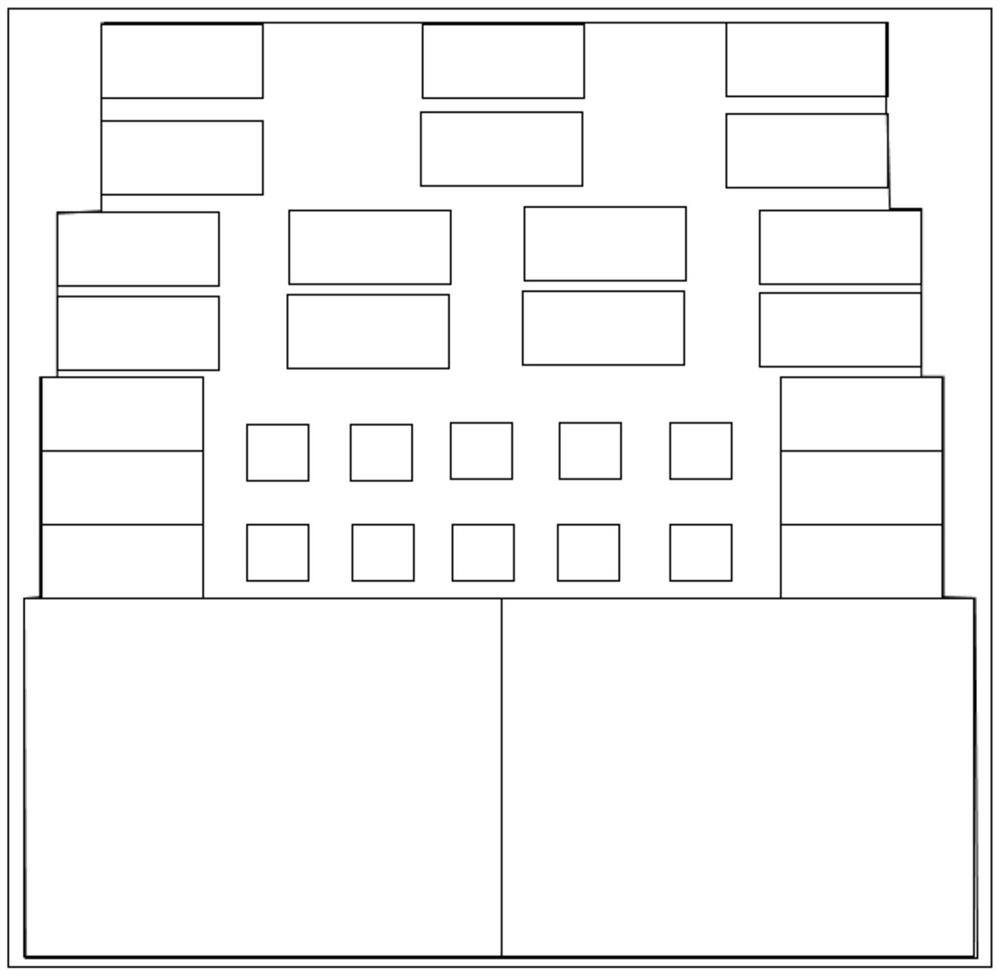

[0044] see Figure 1-3 .

[0045] like figure 1 As shown, this embodiment provides a cake-type integrated circuit layout method for chips, which at least includes the following steps:

[0046] S101. After obtaining the circuit network information netlist provided by the chip front end, perform correlation analysis, and obtain a function correlation table and a logical correlation table among several registers.

[0047]Specifically, for step S101, the netlist netlist provided by the front end is obtained, wherein the netlist netlist is the circuit network information, including the cell (unit) information used in the circuit and the connection relationship between them, which also conforms to the Verilog syntax, from The function description of each module in the netlist netlist analyzes the logical relationship of each module (or register), and further determines the correlation between functions or logic of each module (register), such as the input terminal input of each mo...

no. 2 example

[0068] see Figure 4 .

[0069] like Figure 4 As shown, this embodiment provides a cake-type integrated circuit layout system for chips, including:

[0070] The correlation analysis module 100 is used for obtaining the circuit network information netlist provided by the chip front end and performing correlation analysis to obtain a function correlation table and a logical correlation table among several registers.

[0071] Specifically, for the association analysis module 100, the netlist netlist provided by the front end is obtained, wherein the netlist netlist is the circuit network information, including the cell (unit) information used in the circuit and the connection relationship between them, which also conforms to Verilog syntax , analyze the logical relationship of each module (or register) from the functional description of each module in the netlist netlist, and further determine the correlation between functions or logic of each module (register), such as the in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More